## HIGH VOLTAGE HIGH-SIDE DRIVER

- V<sub>H.V.</sub> UP TO 600 V

- SUPPLY VOLTAGE UP TO 17 V

- DRIVER CURRENT CAPABILITY: SINK CURRENT = 200 mA SOURCE CURRENT = 100 mA

- UNDER VOLTAGE LOCKOUT WITH HYSTERESIS

- CMOS/LSTTL COMPATIBLE INVERTING IN-PUT

- dV/dt IMMUNITY ± 50 V/nS IN FULL TEM-PERATURE RANGE

- CURRENT MODE CONTROL REFERENCE INPUT

- CURRENT/VOLTAGE MODE OPERATION (L6380)

- VOLTAGE MODE OPERATION (L6381)

- 8 PINS PACKAGE

#### **DESCRIPTION**

The L6380/L6381 is a high-voltage device with a

driving stage floating up to 600V.

It can be used to drive N-channel power MOSFET and IGBT, in high-side and low-side configurations.

The device has a logic input (CMOS and LSTTL compatible) and two comparator inputs compatible to ground.

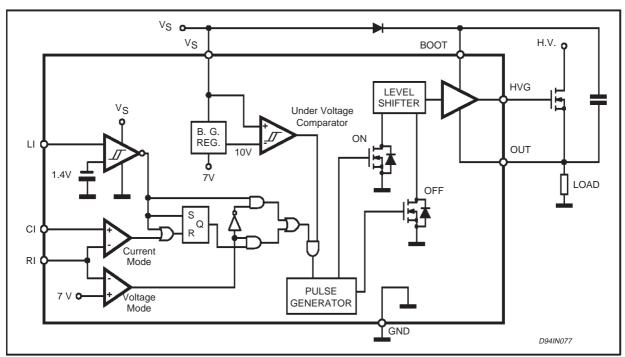

#### L6380 BLOCK DIAGRAM

January 1999 1/9

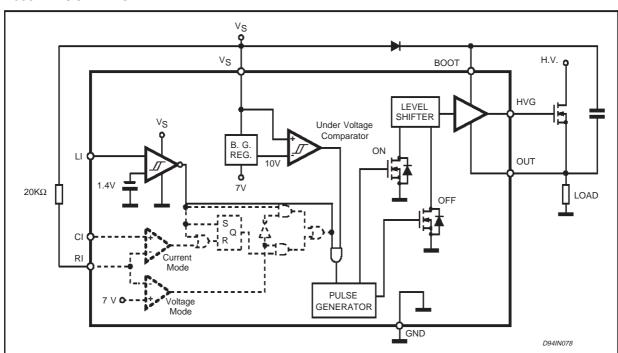

To drive the external power device the signal coming from input logic is fed into a pulse generator that in turns drives the level shifting sructure (that include two High Voltage DMOS) designed to ensure low power dissipation and high noise immunity. The output buffer (in Totem Pole arrangement) is able to sink from or source to the gate of the external device the current needed to switch it ON or OFF.

The falling edge of the signal coming from the input logic will turn ON while the rising edge will turn OFF the driven power device. This operation will ensure low current sinking from the HV rail during commutations.

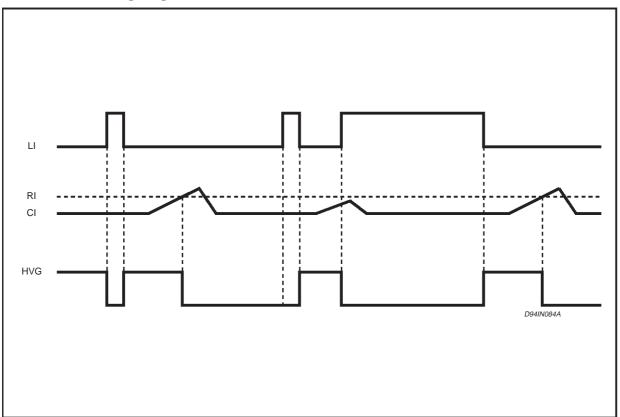

#### **Current / Voltage Mode Operation**

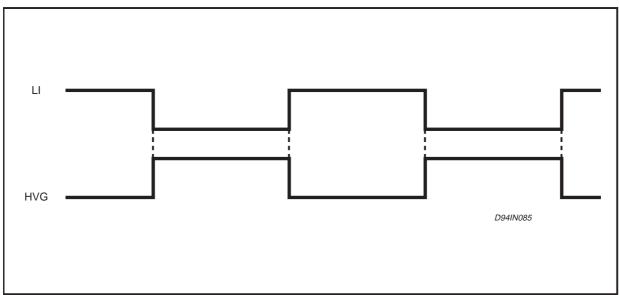

To select the Voltage Mode Operation the user have to set on the RI pin a voltage higher than the internal reference (7V). In this way the IC will function as an inverting buffer driven by the LI input pin (see Voltage Mode Timing Diagram).

If the voltage on RI input pin is lower than 7V the Current Mode Operation will be enabled. In this configuration the RI input will set the reference

voltage to the non inverting input of the Current Mode Comparator (see block diagram), whose inverting input, the CI input pin, in allowable to close a current control loop with a voltage drop coming from a sense resistor. To summarise (see Current Mode Timing Diagrams):

The output of the Current Mode Comparator will mask the LI input whenever the CI voltage is higher than the RI input (and the RI voltage is below 7V).

#### **Under Voltage Lockout**

The output buffer if switched off whenever Vs decrease below Vth OFF.

The IC will remail in this shut down status until Vs has risen above VthON, the hysteresis will provide a good noise immunity.

#### **Applications**

The L6380/L6381 can be used in motor control applications (AC, DC and switched reluctance), electronic ballasts, heating and welding, switching power supplies and UPS.

#### L6381 BLOCK DIAGRAM

7/

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                               | Parameter                                                                 | Value              | Unit |

|--------------------------------------|---------------------------------------------------------------------------|--------------------|------|

| V <sub>BOOT</sub>                    | Supply voltage of bootstrapped section                                    | 600+V <sub>S</sub> | V    |

| $V_{HVG}$                            | Gate voltage of upper driver                                              | 600+V <sub>S</sub> | V    |

| V <sub>OUT</sub>                     | Output voltage                                                            | 600                | V    |

| V <sub>BOOT</sub> - V <sub>OUT</sub> | Difference between boot voltage and output voltage                        | 18                 | V    |

| V <sub>HVG</sub> - V <sub>OUT</sub>  | Difference between gate voltage of upper gate and output voltage          | 18                 | V    |

| Vs                                   | Supply voltage                                                            | 18                 | V    |

| V <sub>IN</sub>                      | Input voltage                                                             | V <sub>S</sub> -2V | V    |

| dV <sub>OUT</sub> /dt                | Transient offset supply voltage                                           | ±50                | V/ns |

| V <sub>OUT</sub> - V <sub>GND</sub>  | Difference between output voltage and ground ( $t_p \le 100 \text{ ns}$ ) | -10                | V    |

| T <sub>amb</sub>                     | Ambient Temperature Range (operative)                                     | -25 to +85         | °C   |

| TJ                                   | Junction temperature                                                      | 150                | °C   |

| T <sub>ST</sub>                      | Storage temperature                                                       | -40 to +150        | °C   |

| P <sub>tot</sub>                     | Total Power Dissipation (at $T_j = 85^{\circ}C$ )                         | 650                | mW   |

Note: ESD immunity for pins 1, 2 and 3 is guaranteed up to 900V (Human Body Model)

#### **THERMAL DATA**

| Symbol                | Parameter                                | MINIDIP | SO8 | Unit |      |

|-----------------------|------------------------------------------|---------|-----|------|------|

| R <sub>th j-amb</sub> | Thermal Resistance, Junction Ambient Max | .       | 100 | 150  | °C/W |

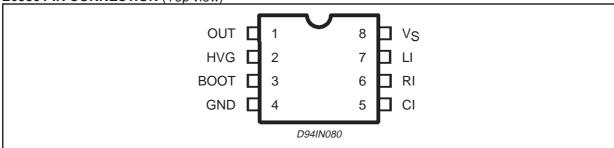

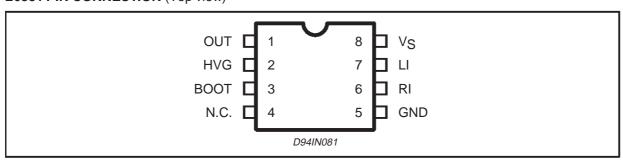

#### L6381 PIN CONNECTION (Top view)

5

#### **ELECTRICAL CHARACTERISTICS**

**DC OPERATION** ( $V_S = 15V$ ;  $T_j = 25$ °C; unless otherwise specified.)

| Symbol               | Pin    | Parameter                                    | Test Condition                                                                          | Min. | Тур. | Max. | Unit |

|----------------------|--------|----------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| Vs                   |        | Supply Voltage (operative)                   |                                                                                         |      |      | 17   | V    |

| $V_{thON}$           |        | UV Turn-On Theshold                          |                                                                                         | 10   | 10.5 | 11   | V    |

| $V_{thOFF}$          | 8      | UV Turn-Off Theshold                         |                                                                                         | 9    | 9.5  | 10   | V    |

| $V_{Shys}$           | ľ      | UV Hysteresis                                |                                                                                         | 0.5  | 0.75 | 1    | V    |

| Iq                   |        | Quiescent Current Before<br>Start-Up         | V <sub>S</sub> ≤8V                                                                      |      | 300  | 700  | mA   |

| $I_{qs}$             |        | Quiescent Supply Current                     |                                                                                         |      | 2    | 3    | mA   |

| Vil                  | 7      | Logic Input Low Level                        |                                                                                         |      |      | 0.8  | V    |

| $V_{ih}$             | ,      | Logic Input High Level                       |                                                                                         | 2    |      |      | V    |

| $V_{co}$             | 6 vs 5 | Input Comparator Offset                      |                                                                                         |      |      | 100  | mV   |

| $V_{thRI}$           | 6      | Mode Selection Internal<br>Threshold Voltage |                                                                                         | 6.5  | 7    | 7.5  | V    |

| I <sub>so</sub>      | 2      | Source Current                               | $V_{BOOT}$ - $V_{OUT}$ =12 $V$ ;<br>$V_{HVG}$ - $V_{OUT}$ =0 $V$ ;<br>$t_p$ ≤10 $\mu$ s | 130  |      | 230  | mA   |

| I <sub>si</sub>      | 2      | Sink Current                                 | $V_{BOOT}$ - $V_{OUT}$ =12 $V$ ;<br>$V_{HVG}$ - $V_{OUT}$ =6 $V$ ;<br>$t_p$ ≤10 $\mu$ s | -320 |      | -180 | mA   |

| I <sub>qBOOT</sub>   | 3      | Boot Supply Quiescent<br>Current             | $V_{HVG} = V_{BOOT}$                                                                    |      | 70   |      | μΑ   |

| I <sub>lkgBOOT</sub> |        | Boot Leakage Current                         | V <sub>BOOT</sub> =500V                                                                 |      |      | 10   | μА   |

| I <sub>IkgHVG</sub>  | 2      | Gate Driver Leakage Current                  | V <sub>HVG</sub> =500V                                                                  |      |      | 10   | μΑ   |

| I <sub>IkgOUT</sub>  | 1      | Output Leakage Current                       | V <sub>OUT</sub> =500V                                                                  |      |      | 10   | μΑ   |

| l.                   | 5, 6   | Input Bias Current                           |                                                                                         |      |      | 2    | μΑ   |

| I <sub>bias</sub>    | 7      | присыаз очненс                               |                                                                                         |      |      | 30   | μΑ   |

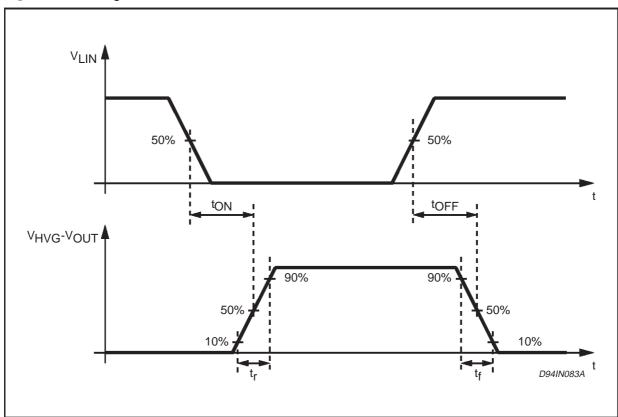

## **AC OPERATION** ( $V_S = 15V$ ; $T_j = 25$ °C; unless otherwise specified.)

| Symbol           | Parameter             | Test Condition                 | Min. | Тур. | Max. | Unit |

|------------------|-----------------------|--------------------------------|------|------|------|------|

| t <sub>r</sub>   | Gate Driver Rise Time |                                |      | 70   | 100  | ns   |

| t <sub>f</sub>   | Gate Driver Fall Time | C <sub>L</sub> (HVG, OUT)=1nF; |      | 50   | 100  | ns   |

| t <sub>ON</sub>  | Turn-On Delay         | V <sub>OUT</sub> =0 to 500V    |      |      | 400  | ns   |

| t <sub>OFF</sub> | Turn-Off Delay        |                                |      |      | 400  | ns   |

4/9

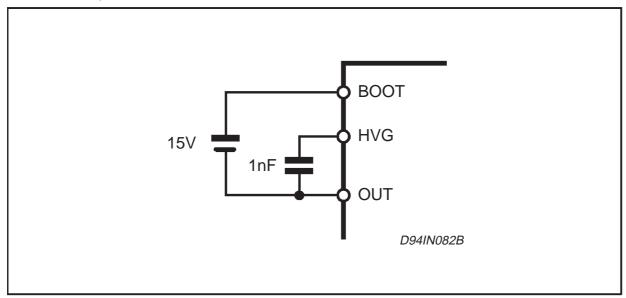

Figure 1: AC Operation Test Circuit

Figure 2: Switching Waveforms

## **Voltage Mode Timing Diagrams**

## **Current Mode Timing Diagrams**

6/9

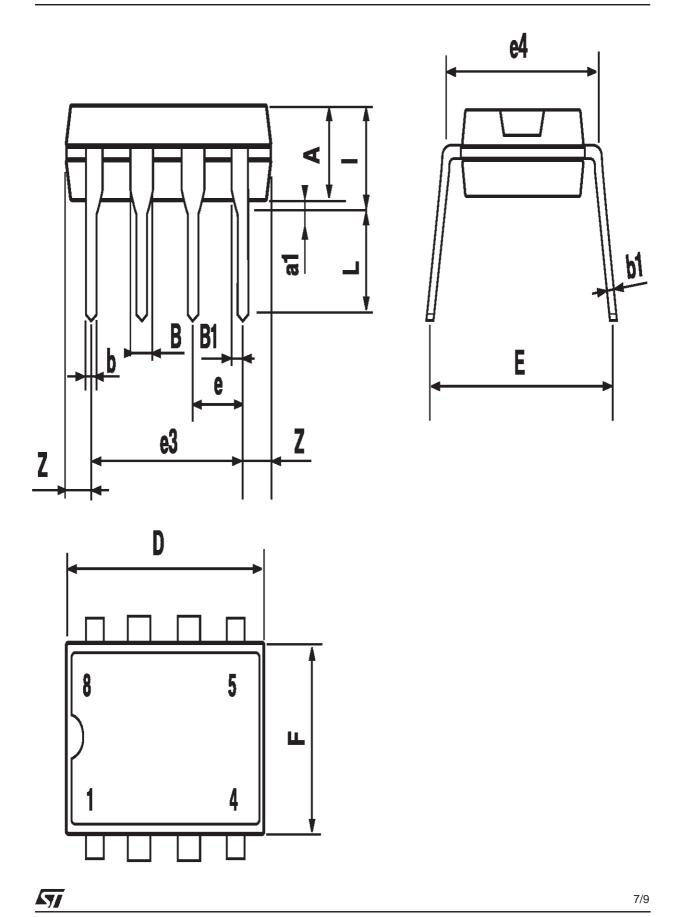

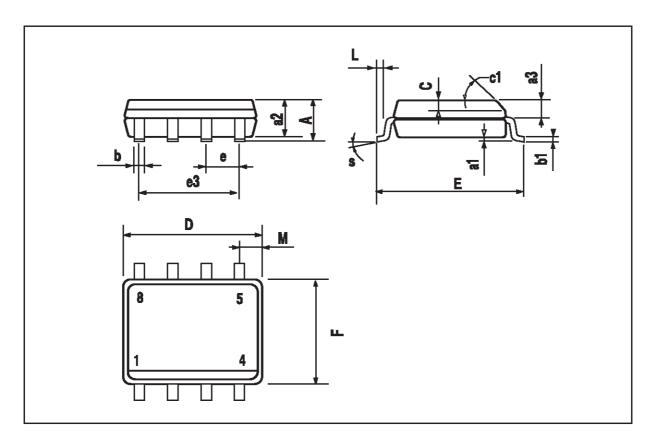

| DIM.  |           | mm   |       |        | inch  |       |  |  |

|-------|-----------|------|-------|--------|-------|-------|--|--|

| DIWI. | MIN.      | TYP. | MAX.  | MIN.   | TYP.  | MAX.  |  |  |

| Α     |           |      | 1.75  |        |       | 0.069 |  |  |

| a1    | 0.1       |      | 0.25  | 0.004  |       | 0.010 |  |  |

| a2    |           |      | 1.65  |        |       | 0.065 |  |  |

| аЗ    | 0.65      |      | 0.85  | 0.026  |       | 0.033 |  |  |

| b     | 0.35      |      | 0.48  | 0.014  |       | 0.019 |  |  |

| b1    | 0.19      |      | 0.25  | 0.007  |       | 0.010 |  |  |

| С     | 0.25      |      | 0.5   | 0.010  |       | 0.020 |  |  |

| c1    |           |      | 45° ( | (typ.) |       |       |  |  |

| D (1) | 4.8       |      | 5.0   | 0.189  |       | 0.197 |  |  |

| Е     | 5.8       |      | 6.2   | 0.228  |       | 0.244 |  |  |

| е     |           | 1.27 |       |        | 0.050 |       |  |  |

| e3    |           | 3.81 |       |        | 0.150 |       |  |  |

| F (1) | 3.8       |      | 4.0   | 0.15   |       | 0.157 |  |  |

| L     | 0.4       |      | 1.27  | 0.016  |       | 0.050 |  |  |

| М     |           |      | 0.6   |        |       | 0.024 |  |  |

| S     | 8° (max.) |      |       |        |       |       |  |  |

## (1) D and F do not include mold flash or protrusions. Mold flash or potrusions shall not exceed 0.15mm (.006inch).

# OUTLINE AND MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

$\ \, \odot$  1999 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com