# L5380/53C80 SCSI Bus Controller

### FEATURES

- Asynchronous Transfer Rate Up to 4 Mbytes/sec

- Low Power CMOS Technology

- Replaces NCR 5380/53C80/ 53C80-40 and AMD Am5380/ 53C80

- On-Chip SCSI Bus Drivers

- Supports Arbitration, Selection/ Reselection, Initiator or Target Roles

- Programmed or DMA I/O, Handshake or Wait State DMA Interlock

- DECC SMD No. 5962-90548 — L53C80

- Package Styles Available:

- 40/48-pin Plastic DIP

- 48-pin Sidebraze, Hermetic DIP

- 44-pin Plastic LCC, J-Lead

### DESCRIPTION

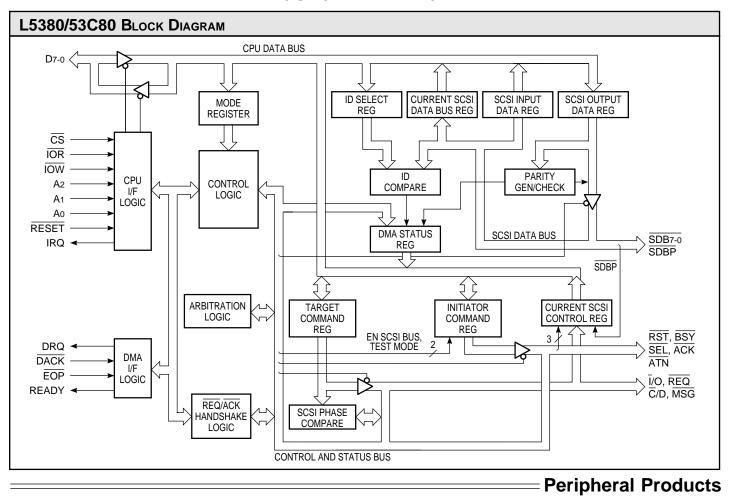

The L5380/53C80 are high performance SCSI bus controllers which support the physical layer of the SCSI (Small Computer System Interface) bus as defined by the ANSI X3T9.2 committee. It is pin and functionally compatible with the NMOS NCR5380, while offering up to a 2.5x performance improvement, 10x power reduction, and lower cost. Replacement of the NMOS 5380 by the LOGIC Devices L5380/53C80 will result in an immediate transfer rate improvement due to REQ/ACK and DRQ/DACK handshake response times up to 5 times faster than previous devices. While remaining firmware compatible with the NCR5380, the L5380/53C80 provides bug fixes and state machine enhancements allowing even larger throughput gains for new designs.

The L5380/53C80 supports asynchronous data transfer between initiator and target at up to 4 Mbytes/sec. It operates in either initiator or target roles and offers a choice of programmed I/O (direct microprocessor manipulation of handshake) or any of several DMA modes (autonomous handshake and data transfer operations). The L5380/53C80 has internal hardware to support arbitration and can monitor and generate interrupts for a variety of error conditions. It provides extensive bus status monitoring features and includes buffers capable of directly driving a terminated SCSI bus for a compact implementation.

#### **PIN DEFINITIONS**

#### A. SCSI Bus

SDB7-0 — SCSI DATA BUS 7-0

Bidirectional/Active low. The 8-bit SCSI data bus is defined by these pins. SDB7 is the most significant bit. During arbitration phase, these lines contain the SCSI ID numbers of all initiators arbitrating for the SCSI bus; SDB7 represents the initiator with the highest priority. During the selection/reselection phase, these lines contain the ID number of the device that won the arbitration along with the ID number of the device to be selected/reselected.

#### <u>SDBP</u> — SCSI DATA BUS PARITY

Bidirectional/Active low. SDBP is the parity bit of the SCSI data bus. Odd parity is used, meaning that the total number of ones on the bus, including the parity bit, is odd. Parity is always generated when sending information, however checking for parity errors when receiving information is a user option. Parity is not valid during arbitration phase.

#### $\overline{SEL}$ — SELECT

Bidirectional/Active low.  $\overline{\text{SEL}}$  is asserted by the initiator to select a target. It is also asserted by the target when reselecting it as an initiator.

#### $\overline{BSY} - BUSY$

Bidirectional/Active low.  $\overline{\text{BSY}}$  is asserted to indicate that the SCSI bus is active.

#### $\overline{ACK}$ — ACKNOWLEDGE

Bidirectional/Active low. ACK is asserted by the initiator during any information transfer phase in response to assertion of  $\overline{\text{REQ}}$  by the target. Similarly,  $\overline{\text{ACK}}$  is deasserted after  $\overline{\text{REQ}}$  becomes inactive. These two signals form the data transfer handshake between the initiator and target. Data is latched by the target on the lowgoing edge of ACK for target receive operations.

#### $\overline{ATN} - ATTENTION$

Bidirectional/Active low. ATN is asserted by the initiator after successful selection of a target, to indicate an intention to send a message to the target. The target responds to ATN by entering the MESSAGE OUT phase.

#### RST — SCSI BUS RESET

Bidirectional/Active low. RST when active indicates a SCSI bus reset condition.

#### $\overline{I}$ /O — INPUT/OUTPUT

Bidirectional/Active low.  $\overline{I}$ /O is controlled by the target and specifies the direction of information transfer. When  $\overline{I}$ /O is asserted, the direction of transfer is to the initiator.  $\overline{I}$ /O is also asserted by the target during RESE-LECTION phase to distinguish it from SELECTION phase.

#### $\overline{C}/D$ — CONTROL/DATA

Bidirectional/Active low.  $\overline{C}/D$  is controlled by the target and when asserted, indicates CONTROL (command or status) information is on the SCSI data bus. DATA is specified when  $\overline{C}/D$  is deasserted.

#### $\overline{MSG}$ — MESSAGE

Bidirectional/Active low.  $\overline{\text{MSG}}$  is controlled by the target, and when asserted indicates MESSAGE phase.

#### $\overline{REQ}$ — REQUEST

Bidirectional/Active low.  $\overline{\text{REQ}}$  is asserted by the target to begin the handshake associated with transfer of a byte over the SCSI data bus.  $\overline{\text{REQ}}$  is deasserted upon receipt of  $\overline{\text{ACK}}$  from the initiator. Data is latched by the initiator on the lowgoing edge of  $\overline{\text{REQ}}$ for initiator receive operations.

### SCSI Bus Controller

L5380/53C80

#### B. Microprocessor Bus

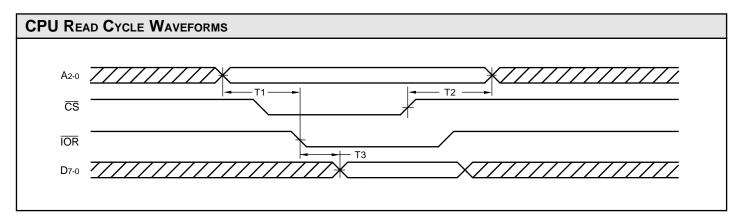

$\overline{CS}$  — CHIP SELECT

Input/Active low. This signal enables reading or writing of the internal registers by the microprocessor, using memory mapped I/O. An alternate method for reading selected registers is available for DMA.

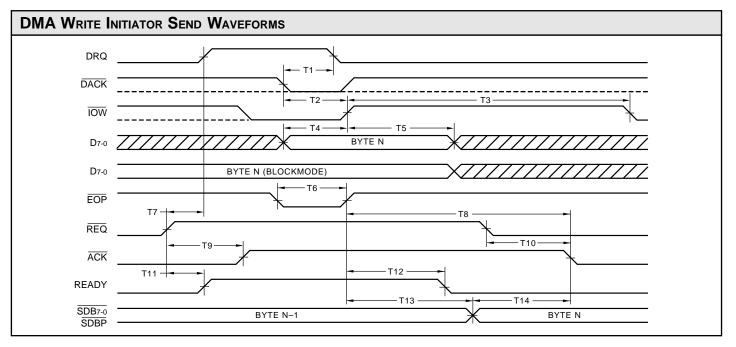

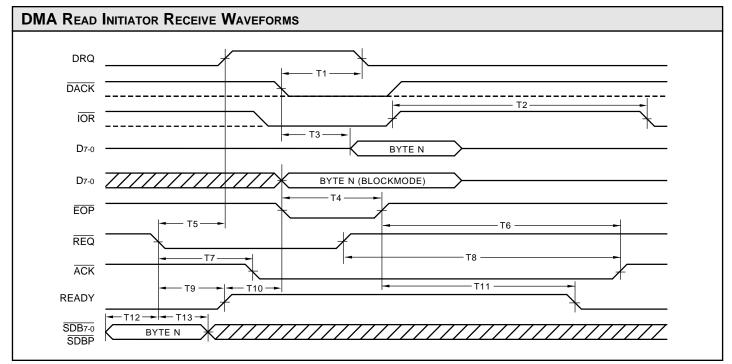

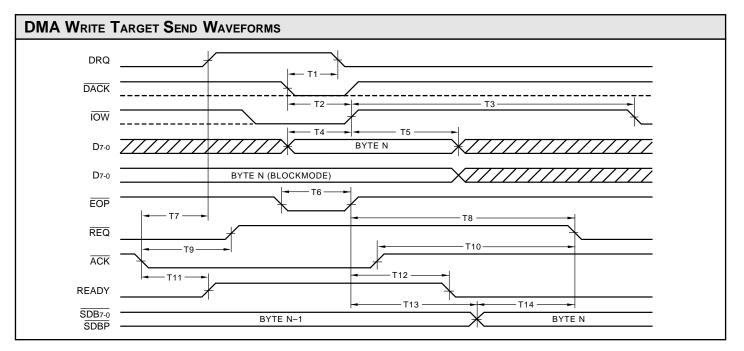

#### DRQ — DMA REQUEST

Output/Active high. This signal is used to indicate that the L5380/53C80 is ready to execute the next cycle of a DMA transfer on the microprocessor bus. For send operations, it indicates that the output data register is ready to receive the next byte from the DMA controller or CPU. For receive operations, it indicates that the input data register contains the next byte to be read by the DMA controller or CPU.

#### IRQ — INTERRUPT REQUEST

Output/Active high. The L5380/ 53C80 asserts this signal to indicate to the microprocessor that one of the several interrupt conditions have been met. These include SCSI bus fault conditions as well as other events requiring microprocessor intervention. Most interrupt types are individually maskable.

#### $\overline{\textit{IOR}}$ — I/O READ

Input/Active low.  $\overline{IOR}$  is used in conjunction with  $\overline{CS}$  and A2–0 to execute a memory mapped read of a L5380/ 53C80 internal register. It is also used in conjunction with  $\overline{DACK}$  to execute a DMA read of the SCSI Input Data Register.

#### READY - READY

Output/Active high. Ready is used rather than DRQ as an alternate method for controlling DMA data transfer. This DMA type is termed blockmode DMA and must be specifically enabled by the CPU. In block-

mode DMA, data is throttled by treating the L5380/53C80 as wait state memory. I/O (DMA) cycles are initiated at the maximum rate sustainable by the DMA controller/memory subsystem, but all cycles are extended (wait-states inserted) until READY is asserted by the L5380/53C80. This is generally the fastest DMA method since memory subsystem addressing can be overlapped with SCSI operations (flyby mode).

#### $\overline{DACK}$ — DMA ACKNOWLEDGE

Input/Active low.  $\overline{DACK}$  is used in conjunction with  $\overline{IOR}$  or  $\overline{IOW}$  to enable reading or writing of the SCSI Input and Output Data Registers when in DMA mode.  $\overline{DACK}$  resets DRQ and must not occur simultaneously with  $\overline{CS}$ .

#### $\overline{EOP}$ — END OF PROCESS

Input/Active low. This input is used to indicate to the L5380/53C80 that a DMA transfer is to be concluded. The L5380/53C80 can automatically generate an interrupt in response to receiving  $\overline{\text{EOP}}$  from the DMA controller.

#### RESET — CPU BUS RESET

Input/Active low. This input clears all internal registers and state machines. It does not result in assertion of the RST signal on the SCSI bus and therefore affects only the local L5380/ 53C80 and not other devices on the bus.

#### *ĪOW* — *Ι/Ο* WRITE

Input/Active low.  $\overline{IOW}$  is used in conjunction with  $\overline{CS}$  and A2–0 to execute a memory mapped write of a L5380/53C80 internal register. It is also used in conjunction with  $\overline{DACK}$ to execute a DMA write of the SCSI Output Data Register.

#### $A_{2-0} - ADDRESS 2-0$

Inputs/Active high. These signals, in conjunction with  $\overline{CS}$ ,  $\overline{IOR}$ , and  $\overline{IOW}$ , address the L5380/53C80 internal registers for CPU read/write operations.

#### D7-0 — DATA 7-0

Bidirectional/Active high. These signals are the microprocessor data bus. D7 is the most significant bit.

#### L5380/53C80 INTERNAL REGISTERS

#### Overview

The L5380/53C80 contains registers that are directly addressed by the microprocessor. These registers allow for monitoring of SCSI bus activity, controlling the operation of the L5380/53C80, and determining the cause of interrupts. In many cases, a read-only and a write-only register are mapped to the same address. Some addresses are dummy registers which are used to implement a control operation but do not correspond to a physical register. The state of the CPU data bus when writing or reading these dummy registers is 'don't care'. Tables 1 and 3 show the address and name of each register as well as bit definitions.

#### **Register Descriptions**

#### A. Write Operations

The following paragraphs give detailed descriptions of the function of each bit in the L5380/53C80 internal registers for write operations as shown in Table 1.

#### WRITE ADDRESS 0 Output Data Register

The Output Data Register is a writeonly register used for sending information to the SCSI data bus. During arbitration, the arbitrating SCSI device

### **SCSI Bus Controller**

L5380/53C80

asserts its ID via this register. The device which wins arbitration also asserts the "OR" of its ID and the ID of the target/initiator to be selected/ reselected. In programmed I/O mode this register is written using  $\overline{CS}$  and  $\overline{IOW}$  with A2-0 = 000. In DMA mode, it is written when  $\overline{IOW}$  and  $\overline{DACK}$  are simultaneously active, irrespective of the state of the address lines. Note that a "1" written to the Output Data Register becomes a low state when asserted on the active-low SCSI bus.

#### WRITE ADDRESS 1 Initiator Command Register

The Initiator Command Register is a read/write register which allows CPU control of the SCSI signals asserted by the initiator. Some bits in this register are not readable, and these positions are mapped to status bits useful in monitoring the progress of arbitration. These, along with the initiation of system-wide reset and test functions, may also be of use to the target.

#### R1 Bit 7 — Assert $\overline{RST}$

When this bit is set, the L5380/53C80 asserts the RST line on the SCSI bus, initializing all devices on the bus to the reset condition. All logic and internal registers of the L5380/53C80 are reset, except for the Assert RST bit itself, the Testmode bit (R1 bit 6) and the IRQ (interrupt request) latch. The IRQ pin becomes active indicating a SCSI bus reset interrupt. This interrupt is not maskable.

#### R1 Bit 6 — Testmode

When this bit is set, the L5380/53C80 places all outputs, including both SCSI and CPU signals, in a high impedance state. This effectively removes the device from the system as an aid to system diagnostics. Note that internal registers may still be written to while in Testmode. The L5380/53C80 returns to normal operation when Testmode is reset. The Testmode bit is reset by either writing a "0" to R1 bit 6

or via the  $\overline{\text{RESET}}$  (CPU reset) pin. Testmode is not affected by the  $\overline{\text{RST}}$ (SCSI bus reset) signal, or by the Assert  $\overline{\text{RST}}$  bit in the Initiator Command Register (R1 bit 7).

#### R1 Bit 5 — Not Used

R1 Bit 4 — Assert ACK

When this bit is set,  $\overline{ACK}$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{ACK}$ . Note that  $\overline{ACK}$  will be asserted only if the Targetmode bit (R2 bit 6) is reset, indicating that the L5380/53C80 is acting as an initiator.

#### R1 Bit 3 — Assert $\overline{BSY}$

When this bit is set,  $\overline{BSY}$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{BSY}$ .  $\overline{BSY}$  is asserted to indicate that the device has been selected or reselected, and deasserting  $\overline{BSY}$  causes a bus free condition.

R1 Bit 2 — Assert  $\overline{SEL}$

When this bit is set,  $\overline{SEL}$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{SEL}$ .  $\overline{SEL}$  is normally asserted after a successful arbitration.

R1 Bit 1 — Assert  $\overline{ATN}$

When this bit is set, ATN is asserted on the SCSI bus. Resetting this bit deasserts ATN. ATN is asserted by the initiator to request message out phase. Note that ATN will be asserted only if the Targetmode bit (R2 bit 6) is reset, indicating that the L5380/53C80 is acting as an initiator.

#### R1 Bit 0 — Assert Data Bus

When this bit is set, the open drain SCSI data bus and parity drivers are enabled and the contents of the Output Data Register are driven onto the SCSI data lines. In addition to the Assert Data Bus bit, enabling of the SCSI bus drivers requires one of the following two sets of conditions:

When the L5380/53C80 is operating as an initiator, the Targetmode bit (R2 bit 6) must be reset, the  $\overline{I}$ /O pin must be negated (initiator to target transfer) and no phase mismatch condition can exist. A phase mismatch occurs when the  $\overline{MSG}$ ,  $\overline{C}/D$ , and  $\overline{I}/O$  bits of the Target Command Register (R3) do not match the corresponding SCSI control lines.

When the L5380/L53C80 is operating as a target, the Targetmode bit will be set, and in this case Assert Data Bus will enable the outputs unconditionally.

The Assert Data Bus bit need not be set for arbitration to occur; when the Arbitrate bit (R2 bit 0) is set, and a bus free condition is detected, the data bus will be enabled for arbitration regardless of the state of the Assert Data Bus bit.

Finally, note that the Testmode bit (R1 bit 6) overrides all other controls, including Assert Data Bus and Arbitrate, and disables all outputs.

#### WRITE ADDRESS 2 Mode Register

The Mode register is a read/write register which provides control over several aspects of L5380/53C80 operation. Programmed I/O or two different types of DMA transfer may be selected, initiator or target device operation is accommodated, and parity checking and interrupts may be enabled via this register. The function of each individual bit is described as follows:

R2 Bit 7 — Blockmode

This bit must be used in conjunction with DMA Mode (R2 bit 1). It is used to select the type of handshake desired between the L5380/53C80 and the external DMA controller. See "L5380/53C80 Data Transfers" for a complete discussion of the transfer types supported.

#### R2 Bit 6 — Targetmode

When this bit is set, the L5380/53C80 will operate as a SCSI target device. This enables the SCSI signals  $\overline{I}/O$ ,  $\overline{C}/D$ ,  $\overline{MSG}$ , and  $\overline{REQ}$  to be asserted.

### **SCSI Bus Controller**

When Targetmode is reset, the device will operate as an initiator. This enables the SCSI signals ATN and ACK to be asserted. Targetmode also affects state machine operation for DMA transfers and the conditions necessary for enabling the SCSI Data bus drivers. (See Assert Databus, R1 bit 0).

#### R2 Bit 5 — Enable Parity Check

When this bit is set, information received on the SCSI data bus is checked for odd parity. The Parity Error latch will be set whenever data is received under DMA control or the Current SCSI Data Register (Read Register 0) is read by the CPU. The state of the Parity Error latch can be determined by reading R5 bit 5, and it can be reset by a read to Address 7. Note that ENABLE PARITY CHECK must be set if parity error interrupts are to be generated. This interrupt can be separately masked by the Enable Parity Interrupt bit (R2 bit 4) while retaining the state of the Parity Error latch for later examination by the CPU.

#### R2 Bit 4 — Enable Parity Interrupt

When this bit is set, the L5380/53C80 will set the interrupt request latch, and assert IRQ (interrupt request) if it detects a parity error. Enable Parity Check (R2 bit 5) must also be set if parity error interrupts are desired.

#### R2 Bit 3 — Enable End Of DMA Interrupt

When this bit is set, the L5380/53C80 will set the interrupt request latch, and assert IRQ (interrupt request) if it detects a valid  $\overline{\text{EOP}}$  (End of Process) signal.  $\overline{\text{EOP}}$  is normally generated by a DMA controller to indicate the end of a DMA transfer.  $\overline{\text{EOP}}$  is valid only when coincident with  $\overline{\text{IOR}}$  or  $\overline{\text{IOW}}$  and  $\overline{\text{DACK}}$ .

SCSI Bus Controller

#### R2 Bit 2 — Monitor Busy

When this bit is set, the L5380/53C80 continuously monitors the state of the  $\overline{\text{BSY}}$  signal. Absence of  $\overline{\text{BSY}}$  for a period longer than 400 ns (but less than 1200 ns) will cause the L5380/53C80 to set the BSYERR and IRQ (interrupt request) latches. In addition, the six least significant bits of the Initiator Command Register are reset, and all SCSI data and control outputs are disabled until the BSYERR latch is reset. This effectively disconnects the L5380/ 53C80 from the SCSI bus in response to an unexpected disconnect by another device. It also allows the CPU to be interrupted when the SCSI bus becomes free in systems where arbitration is not used and an  $\overline{\text{EOP}}$  signal is not available.

#### R2 Bit 1 — DMA Mode

When this bit is set, the L5380/53C80's internal state machines automatically control the SCSI signals  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$ (as appropriate for initiator or target operation) and the CPU signals DRQ and READY. DMA Mode must be set prior to starting a DMA transfer in either direction. The DMA Mode bit is reset whenever a bus free condition is detected ( $\overline{BSY}$  is not active). This aborts DMA operations when a loss of  $\overline{BSY}$ occurs, regardless of the state of the Monitor Busy bit (R2 bit 2.) The DMA Mode bit is not reset when  $\overline{\text{EOP}}$  is received, but must be specifically reset by the CPU. EOP does, however, inhibit additional DMA cycles from occurring.

#### R2 Bit 0 — Arbitrate

This bit is set to indicate a desire to arbitrate for use of the SCSI bus. Before setting the Arbitrate bit, the SCSI Output Data Register (Write Register 0) must be written with the SCSI ID assigned to the arbitrating SCSI device. The bit position of register R0 which is set represents the priority number of the SCSI device, with bit 7 the highest priority. See the section on "Arbitration" for a full discussion of the L5380/ 53C80 arbitration procedure.

#### WRITE REGISTERS TABLE 1. Address 0 — Output Data Register 6 3 2 1 7 5 4 0 SDB7 SDB6 SDB5 SDB<sub>4</sub> SDB3 SDB<sub>2</sub> SDB1 SDB<sub>0</sub> Address 1 — Initiator Command Register 6 5 4 3 7 2 1 0 ASSERT TEST ASSERT ASSERT ASSERT ASSERT ASSERT MODE RST ACK BSY SEL ATN DATA BUS Address 2 — Mode Register 7 6 5 4 3 2 1 0 BLOCK TARGET ENABLE ENABLE MONI-DMA ARBI-ENABLE MODE MODE PARITY PARITY EODMA TOR MODE TRATE CHECK INT'RPT INT'RPT BUSY Address 3 — Target Command Register 7 6 5 4 3 2 1 0 LAST ASSERT ASSERT ASSERT ASSERT BYTE REQ MSG C/D I/O SENT Address 4 — ID Select Register 6 2 5 4 3 1 0 7 SDB7 SDB6 SDB5 SDB4 SDB<sub>3</sub> SDB<sub>2</sub> SDB1 SDB0 Address 5 — Start DMA Send 7 6 5 4 3 2 1 0 Address 6 — Start DMA Target Receive 6 5 7 4 3 2 1 0 Address 7 — Start DMA Initiator Receive 6 5 7 4 3 2 1 0

#### WRITE ADDRESS 3 Target Command Register

The Target Command Register is a read/write register which allows CPU control of the SCSI signals asserted by the target. In addition, this register contains a read-only status flag useful in unambiguously determining when the last byte of a DMA transfer has actually been sent over the SCSI bus.

When operating as an initiator with DMA mode set, the Assert  $\overline{\text{MSG}}$ , Assert  $\overline{C}/D$ , and Assert  $\overline{I}/O$  bits are used as a template to compare against the corresponding SCSI control signals provided by the target. A phase mismatch interrupt will be generated on the falling edge of the  $\overline{\text{REQ}}$  input if the template does not match the state of the signals. Therefore the CPU should initialize these bits to the phase of the expected data transfer. An interrupt, then, will signal an intent by the target to change to a new phase. The SCSI information transfer phases and their associated direction of data transfer are given in Table 2.

R3 Bits 7-4 — Not Used

R3 Bit 3 — Assert  $\overline{REQ}$

When this bit is set,  $\overline{\text{REQ}}$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{\text{REQ}}$ . Note that  $\overline{\text{REQ}}$  will be asserted only if the Targetmode bit (R2 bit 6) is set, indicating that the L5380/53C80 is acting as a target.

R3 Bit 2 — Assert  $\overline{MSG}$

When this bit is set,  $\overline{\text{MSG}}$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{\text{MSG}}$ . Note that  $\overline{\text{MSG}}$  will be asserted only if the Targetmode bit (R2 bit 6) is set, indicating that the L5380/53C80 is acting as a target. When operating as an initiator, this bit is compared against the  $\overline{\text{MSG}}$  input, and an interrupt is generated if they differ at the falling edge of  $\overline{\text{REQ}}$ . R3 Bit 1 — Assert  $\overline{C}/D$

When this bit is set,  $\overline{C}/D$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{C}/D$ . Note that  $\overline{C}/D$  will be asserted only if the Targetmode bit (R2 bit 6) is set, indicating that the L5380/53C80 is acting as a target. When operating as an initiator, this bit is compared against the  $\overline{C}/D$  input, and an interrupt is generated if they differ at the falling edge of  $\overline{REQ}$ .

#### R3 Bit 0 — Assert Ī/O

When this bit is set,  $\overline{I}/O$  is asserted on the SCSI bus. Resetting this bit deasserts  $\overline{I}/O$ . Note that  $\overline{I}/O$  will be asserted only if the Targetmode bit (R2 bit 6) is set, indicating that the L5380/53C80 is acting as a target. When operating as an initiator, this bit is compared against the  $\overline{I}/O$  input, and an interrupt is generated if they differ at the falling edge of  $\overline{REQ}$ .

#### WRITE ADDRESS 4 ID Select Register

The ID Select Register is a write-only register which is used to monitor selection or reselection attempts to the L5380/53C80. In arbitrating systems, an ID number is assigned to each SCSI device by setting a single bit position of the ID Select Register. Each SCSI data pin is inverted and compared with the corresponding bit in the ID Select Register. If any matches are found while a bus free condition exists

### **SCSI Bus Controller**

and  $\overline{\text{SEL}}$  is active, the L5380/53C80 will generate an interrupt to indicate a selection or reselection. During selection or reselection, parity checking may be enabled by setting the Enable Parity Check bit (R2 bit 5). This interrupt may be masked by resetting all bits in this register.

#### WRITE ADDRESS 5 Start DMA Send

This is a dummy register. Writes to this location are detected and cause the L5380/53C80 internal state machine to execute a DMA send operation. This location is used for either initiator or target DMA send. The DMAMODE bit (R2 bit 1) must be set prior to writing this location.

#### WRITE ADDRESS 6 Start DMA Target Receive

This is a dummy register. Writes to this location are detected and cause the L5380/53C80 internal state machine to execute a target DMA receive operation. The DMAMODE bit (R2 bit 1) and the Targetmode bit (R2 bit 6) must be set prior to writing this location.

#### WRITE ADDRESS 7 Start DMA Initiator Receive

This is a dummy register. Writes to this location are detected and cause the L5380/53C80 internal state machine to execute an initiator DMA

| TABL | е <b>2.</b> | SC  | SI INFORMATION | TRANSFER  | Рназ          | ES        |

|------|-------------|-----|----------------|-----------|---------------|-----------|

| MSG  | <u></u> C/D | Ī/O | Phase          | Direction |               |           |

| 0    | 0           | 0   | Message In     | Target    | +             | Initiator |

| 0    | 0           | 1   | Message Out    | Initiator | $\rightarrow$ | Target    |

| 0    | 1           | 0   | Unused         |           |               |           |

| 0    | 1           | 1   | Unused         |           |               |           |

| 1    | 0           | 0   | Status In      | Target    | $\rightarrow$ | Initiator |

| 1    | 0           | 1   | Command        | Initiator | $\rightarrow$ | Target    |

| 1    | 1           | 0   | Data In        | Target    | $\rightarrow$ | Initiator |

| 1    | 1           | 1   | Data Out       | Initiator | $\rightarrow$ | Target    |

03/11/97-LDS.5380-I

receive operation. The DMAMODE bit (R2 bit 1) must be set and the Targetmode bit (R2 bit 6) must be reset prior to writing this location.

#### **B. READ OPERATIONS**

The following paragraphs give detailed descriptions of the function of each bit in the L5380/53C80 internal registers for read operations as shown in Table 3.

#### READ ADDRESS 0 Current SCSI Data Bus

The Current SCSI Data Bus Register allows the microprocessor to monitor the SCSI data bus at any time, by asserting  $\overline{CS}$  and  $\overline{IOR}$  with address lines  $A_{2-0} = 000$ . The SCSI data lines are not actually registered, but gated directly onto the CPU bus whenever Address 000 is read by the CPU. Therefore, reads of this location should only be done when the SCSI data lines are guaranteed to be stable by the SCSI protocol. For systems which implement SCSI bus arbitration, this location is read to determine whether devices having higher priorities are also arbitrating. Programmed I/O data transfer uses this location for reading data transferred on the SCSI data bus. With parity checking enabled, SCSI data bus parity checking is done at the beginning of the read cycle for fast error detection. Note that the SCSI data bus is inverted to become active high when presented to the CPU.

#### **READ ADDRESS 1** Initiator Command Register

Reading bit 7 or bits 4–0 of the Initiator Command Register simply reflects the status of the corresponding bit in the register. Bits 6 and 5 are mapped to other signals as discussed below:

#### R1 Bit 6 — Arbitration In Progress

For this bit to be active, the Arbitrate bit (R2 bit 0) must be set. When ARBITRATION IN PROGRESS is set, it indicates that the L5380/53C80 has detected a bus free condition and is currently arbitrating for control of the bus. See the section on "Arbitration" for a complete discussion of the L5380/53C80 arbitration mechanism. Resetting the Arbitrate bit will reset ARBITRATION IN PROGRESS.

#### R1 Bit 5 — Lost Arbitration

For this bit to be active, the Arbitrate bit (R2 bit 0) must be set. When LOST ARBITRATION is set, it indicates that the L5380/53C80 has arbitrated for the SCSI bus (see R1 bit 6 above) and has detected the assertion of SEL by another (higher priority) device. The L5380/53C80 responds to loss of arbitration by immediately discontinuing the arbitration attempt. Resetting the Arbitrate bit will reset LOST ARBITRATION.

#### READ ADDRESS 2 Mode Register

Reading the Mode Register simply reflects the status of the bits in that register.

#### READ ADDRESS 3 Target Command Register

Reading the Target Command Register simply reflects the status of the bits in that register, except for bit 7, LAST BYTE SENT.

#### R3 bit 7 — Last Byte Sent

This read only bit indicates that the last byte of data loaded into the L5380/53C80 during a DMA send operation has actually been transferred over the SCSI bus. Note that the end of process flag and the corresponding interrupt occur when this byte is loaded into the L5380/53C80, but do not reflect whether it has actually been sent. This bit is not present in the NCR5380, but is present in the NCR53C80. Last Byte Sent is reset when the DMAMODE bit (R2 bit 1) is reset.

### **SCSI Bus Controller**

#### READ ADDRESS 4 Current SCSI Control Register

The Current SCSI Control Register provides a means for the CPU to directly monitor the state of the SCSI bus control signals. The SCSI control lines are not actually registered, but gated directly onto the CPU bus whenever Address 100 is read by the CPU. The value of each bit position represents the complement of the corresponding (low true) SCSI Signal Pin.

#### READ ADDRESS 5 DMA Status Register

The DMA Status Register provides a means for the CPU to determine the status of a DMA transfer and to determine the cause of an interrupt. It also makes available the final two SCSI bus signals which are not included in the Current SCSI Control Register. The function of each individual bit is defined as follows:

#### R5 Bit 7 — End of DMA

When this bit is set, it indicates that a valid  $\overline{EOP}$  has been received during a DMA transfer. A valid  $\overline{EOP}$  occurs when  $\overline{EOP}$ , DACK, and either  $\overline{IOR}$  or  $\overline{IOW}$  are simultaneously active for the minimum specified time. End of DMA is reset when the DMAMODE bit (R2 bit 1) is reset.

Note that for DMA send operations, an END OF DMA status indicates only that the last byte of the transfer is loaded into the Output Data Register of the sending device, not that it has actually been transferred over the SCSI bus. For this reason, the L5380/ 53C80 provides an additional status bit; Last Byte Sent (R3 bit 7) which indicates that this final byte has been transferred to the receiving end. This bit is not present in the NCR5380.

Also, note that the DMAMODE bit is reset automatically whenever a loss of busy condition is detected, which in turn resets END OF DMA. Therefore

the DMA Status Register should be read prior to resetting the Assert  $\overrightarrow{\text{BSY}}$ bit (R1 bit 3) at the conclusion of a DMA transfer.

R5 Bit 6 — DMA Request

This bit reflects the state of the DRQ (DMA Request) signal. In programmed I/O, this bit can be polled by the CPU to determine whether there is a pending request for byte transfer. For DMA send operations, DMA REQUEST is reset when DACK and IOW are simultaneously asserted. For DMA receive operations, simultaneous DACK and IOR will reset DMA REQUEST. DMA REQUEST is reset unconditionally when the DMAMODE bit (R2 bit 1) is reset.

#### R5 Bit 5 — Parity Error

This bit can only be set if Enable Parity Check (R2 bit 5) is set. When enabled, the Parity Error bit is set if incoming SCSI data in either initiator or target mode, or during selection phase, does not correctly reflect odd parity. PARITY ERROR can be reset by a read to the Reset Error/Interrupt Register (Register 7).

#### R5 Bit 4 — Interrupt Request

This bit reflects the state of the IRQ signal. The L5380/53C80 asserts IRQ to generate an interrupt to the CPU. See the section on "Interrupts" for further information on the possible sources of interrupts in the L5380/53C80. INTERRUPT REQUEST can be reset by a read to the Reset Error/Interrupt Register (Register 7).

#### R5 Bit 3 — Phase Match

When this bit is set, it indicates that the  $\overline{\text{MSG}}$ ,  $\overline{\text{C}}/\text{D}$ , and  $\overline{\text{I}}/\text{O}$  lines match the state of the Assert  $\overline{\text{MSG}}$ , Assert  $\overline{\text{C}}/\text{D}$ , and Assert  $\overline{\text{I}}/\text{O}$  bits in the Target Command Register. PHASEMATCH is not actually registered, but represents a continuous comparison of these three phase bits to the corresponding internal register locations. This bit is intended for use by the

|                                                                      | . Read                                                           | REGISTE                                                                | RS                                                                          |                                                                                                |                                  |                      |                       |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------|----------------------|-----------------------|--|--|--|

| Address                                                              | Address 0 — Current SCSI Data Bus                                |                                                                        |                                                                             |                                                                                                |                                  |                      |                       |  |  |  |

| 7                                                                    | 6                                                                | 5                                                                      | 4                                                                           | 3                                                                                              | 2                                | 1                    | 0                     |  |  |  |

| SDB7                                                                 | SDB6                                                             | SDB5                                                                   | SDB4                                                                        | SDB3                                                                                           | SDB2                             | SDB1                 | SDB0                  |  |  |  |

|                                                                      | Address 1 — Initiator Command Register                           |                                                                        |                                                                             |                                                                                                |                                  |                      |                       |  |  |  |

| 7                                                                    | 6                                                                | 5                                                                      | 4                                                                           | 3                                                                                              | 2                                | 1                    |                       |  |  |  |

| ASSERT<br>RST                                                        | ARB. IN<br>PRO-<br>GRESS                                         | LOST<br>ARB.                                                           | ASSERT                                                                      | ASSERT<br>BSY                                                                                  | ASSERT<br>SEL                    | ASSERT<br>ATN        | ASSERT<br>DATA<br>BUS |  |  |  |

| Address                                                              | 2 — Mod                                                          | e Registe                                                              | er                                                                          |                                                                                                |                                  |                      |                       |  |  |  |

| 7                                                                    | 6                                                                | 5                                                                      | 4                                                                           | 3                                                                                              | 2                                | 1                    | 0                     |  |  |  |

| BLOCK<br>MODE                                                        | TARGET<br>MODE                                                   | ENABLE<br>PARITY<br>CHECK                                              |                                                                             | ENABLE<br>EODMA<br>INT'RPT                                                                     | MONI-<br>TOR<br>BUSY             | DMA<br>MODE          | ARBI-<br>TRATE        |  |  |  |

| Address                                                              | 3 — Targ                                                         | jet Comm                                                               | and Reg                                                                     | ister                                                                                          |                                  |                      |                       |  |  |  |

| 7                                                                    | 6                                                                | 5                                                                      | 4                                                                           | 3                                                                                              | 2                                | 1                    | 0                     |  |  |  |

| LAST<br>BYTE<br>SENT                                                 |                                                                  |                                                                        |                                                                             | ASSERT<br>REQ                                                                                  | ASSERT<br>MSG                    | ASSERT<br>C/D        | ASSERT<br>Ī/O         |  |  |  |

| Address                                                              | Address 4 — Current SCSI Control Register                        |                                                                        |                                                                             |                                                                                                |                                  |                      |                       |  |  |  |

| Addic33                                                              | 4 — Curr                                                         | ent SCSI                                                               | Control                                                                     | Register                                                                                       |                                  |                      |                       |  |  |  |

| 7                                                                    | 4 — Curr<br>6                                                    | ent SCSI<br>5                                                          | Control                                                                     | Register<br>3                                                                                  | 2                                | 1                    | 0                     |  |  |  |

|                                                                      |                                                                  |                                                                        |                                                                             | -                                                                                              | <b>2</b><br>ī/O                  | 1<br>SEL             | 0<br>Parity           |  |  |  |

| 7<br>RST                                                             | 6                                                                | 5<br>REQ                                                               | 4<br>MSG                                                                    | 3                                                                                              |                                  | _                    |                       |  |  |  |

| 7<br>RST                                                             | 6<br>BSY                                                         | 5<br>REQ                                                               | 4<br>MSG                                                                    | 3                                                                                              |                                  | _                    |                       |  |  |  |

| 7<br>RST<br>Address                                                  | 6<br>BSY<br>5 — DMA                                              | 5<br>REQ<br>Status F                                                   | 4<br>MSG<br>Register<br>4                                                   | 3<br><u> </u> <u> </u> | Ī/O                              | SEL                  | PARITY                |  |  |  |

| 7<br>RST<br>Address<br>7<br>END<br>OF<br>DMA                         | 6<br>BSY<br>5 — DMA<br>6<br>DMA                                  | 5<br>REQ<br>Status F<br>5<br>PARITY<br>ERROR                           | 4<br>MSG<br>Register<br>4<br>INTER-<br>RUPT<br>REQ.                         | 3<br>C/D<br>3<br>PHASE                                                                         | ī/O<br><b>2</b><br>BUSY          | SEL                  | PARITY                |  |  |  |

| 7<br>RST<br>Address<br>7<br>END<br>OF<br>DMA                         | 6<br>BSY<br>5 — DMA<br>6<br>DMA<br>REQ.                          | 5<br>REQ<br>Status F<br>5<br>PARITY<br>ERROR                           | 4<br>MSG<br>Register<br>4<br>INTER-<br>RUPT<br>REQ.                         | 3<br>C/D<br>3<br>PHASE                                                                         | ī/O<br><b>2</b><br>BUSY          | SEL                  | PARITY                |  |  |  |

| 7<br>RST<br>Address<br>7<br>END<br>OF<br>DMA<br>Address              | 6<br>BSY<br>5 — DMA<br>6<br>DMA<br>REQ.<br>6 — Inpu              | 5<br>REQ<br>Status F<br>5<br>PARITY<br>ERROR                           | 4<br>MSG<br>Register<br>4<br>INTER-<br>RUPT<br>REQ.                         | 3<br>C/D<br>3<br>PHASE<br>MATCH                                                                | Ī/O<br><b>2</b><br>BUSY<br>ERROR | SEL<br>1<br>ATN      | PARITY<br>0<br>ACK    |  |  |  |

| 7<br>RST<br>Address<br>7<br>END<br>OF<br>DMA<br>Address<br>7<br>SDB7 | 6<br>BSY<br>5 — DMA<br>6<br>DMA<br>REQ.<br>6 — Inpu<br>6         | 5<br>REQ<br>Status F<br>5<br>PARITY<br>ERROR<br>t Data Re<br>5<br>SDB5 | 4<br>MSG<br>Register<br>4<br>INTER-<br>RUPT<br>REQ.<br>egister<br>4<br>SDB4 | 3<br>$\overline{C}/D$<br>3<br>PHASE<br>MATCH<br>3<br>SDB3                                      | Ī/O<br>2<br>BUSY<br>ERROR<br>2   | SEL<br>1<br>ATN<br>1 | PARITY<br>0<br>ACK    |  |  |  |

| 7<br>RST<br>Address<br>7<br>END<br>OF<br>DMA<br>Address<br>7<br>SDB7 | 6<br>BSY<br>5 — DMA<br>6<br>DMA<br>REQ.<br>6 — Inpu<br>6<br>SDB6 | 5<br>REQ<br>Status F<br>5<br>PARITY<br>ERROR<br>t Data Re<br>5<br>SDB5 | 4<br>MSG<br>Register<br>4<br>INTER-<br>RUPT<br>REQ.<br>egister<br>4<br>SDB4 | 3<br>$\overline{C}/D$<br>3<br>PHASE<br>MATCH<br>3<br>SDB3                                      | Ī/O<br>2<br>BUSY<br>ERROR<br>2   | SEL<br>1<br>ATN<br>1 | PARITY<br>0<br>ACK    |  |  |  |

initiator to detect that the target device has changed to a different information transfer phase. When the L5380/53C80 detects a phase mismatch, PHASEMATCH is reset, and information transfer to or from the SCSI bus is inhibited.

#### R5 Bit 2 — Busy Error

This bit can only be set if the Monitor Busy bit (R2 bit 2) is set. When set, Busy Error indicates that the BSY pin has been false for a period at least equal to a bus settle delay (400 ns). When the Busy Error condition is detected, all SCSI signal pins are disabled, and the DMAMODE bit (R2 bit 1) and bits 5-0 of the Initiator Command Register are reset. Busy Error can be reset by a read to the Reset Error/Interrupt Register (Register 7).

#### R5 Bits 1, 0 — $\overline{ATN}$ , $\overline{ACK}$

Like the Current SCSI Control Register, these bits provide a means for the CPU to directly monitor the state of the SCSI bus control signals. The SCSI control lines are not actually registered, but gated directly onto the CPU bus whenever Address 5 is read by the CPU. The value of each bit position represents the complement of the corresponding (low true) SCSI Signal Pin.

#### READ ADDRESS 6 Input Data Register

This register acts as a temporary holding register for information received from the SCSI data bus during DMA transfers (DMAMODE bit, R2 bit 1 is set). In the initiator mode, the L5380/53C80 latches the SCSI data when  $\overline{\text{REQ}}$  goes active. In the target mode, data is latched when ACK goes active. The contents of this register represent the negation of the low-true SCSI data. The contents of the SCSI Input Data Register are gated onto the CPU data bus when DACK and IOR are simultaneously true, or by a CPU read of location 6. Note that DACK and CS must never be active simultaneously in order to prevent conflicting read operations. Parity may optionally be checked on the data as it is loaded into this register.

#### READ ADDRESS 7 Reset Error/Interrupt Register

This is a dummy register. Reads to this location are detected and used to reset the Interrupt Request Latch (IRQ signal) and the PARITY ERROR, INTERRUPT REQUEST, and BUSY ERROR latches (visible as bits 5, 4, and 2 of Register 5).

#### INTERRUPTS

The L5380/53C80 generates interrupts to the CPU by setting the Interrupt Request Latch, which directly drives the IRQ (Interrupt Request) line. The IRQ output will reflect the state of the Interrupt Request Latch under all conditions except when Testmode (R1 bit 6) is active, when it is in a high impedance state. The Interrupt Request Latch may be reset by reading Address 7, the Reset Error/Interrupt Register. A read of this location also resets several error condition latches as discussed in the section on "Internal Registers".

Interrupts may be caused by any of six conditions, most of which may be masked by resetting enable bits in the appropriate registers. The following sections describe each interrupt type, its cause, and how it may be reset. Upon receiving an interrupt, the CPU may read the Current SCSI Control Register (R4) and the DMA Status Register (R5) to determine the cause of the interrupt. While the following discussions indicate the expected values of these registers following an interrupt, it is recommended that bits in these registers which are not germane to determining the cause of an interrupt be masked off in firmware prior to implementing a comparison. A typical operational sequence for an interrupt service routine is given at the end of this section.

### **SCSI Bus Controller**

#### SCSI Bus Reset Interrupt

A SCSI Bus Reset Interrupt occurs when the SCSI  $\overline{\text{RST}}$  signal becomes active. This may be due to another SCSI device driving the  $\overline{\text{RST}}$  line, or because the Assert  $\overline{\text{RST}}$  bit (R1 bit 7) has been set, causing the L5380/53C80 to drive the SCSI RST line. The value of the SCSI  $\overline{\text{RST}}$  line is visible as R4 bit 7; however, this line is not latched and therefore may have changed state by the time the CPU responds to the interrupt and polls this location. For this reason, a SCSI Bus Reset Interrupt should be assumed if no other interrupt condition is active when reading Registers 4 and 5.

The SCSI Bus Reset Interrupt is nonmaskable. The expected read values for the Current SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

#### Selection/Reselection Interrupt

A Selection/Reselection Interrupt occurs when the SCSI SEL signal becomes active, the SCSI bus matches the bit set in the ID Select Register, and  $\overline{BSY}$  has been false for at least a bus settle delay. When the  $\overline{I}/O$  pin is asserted, the interrupt should be interpreted as a reselection. The Selection/Reselection Interrupt may be masked by resetting all bits in the ID Select Register. The expected read values for the Current SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

#### Loss of Busy Interrupt

A Loss of Busy Interrupt occurs when the SCSI BSY signal has been inactive for at least a bus settle delay (400 ns). The Loss of Busy Interrupt may be masked by resetting the Monitor Busy bit (R2 bit 2). Resetting Monitor Busy also prevents the Busy Error latch (Read R5 bit 2) from being set. The expected read values for the Current

SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

#### **Phase Mismatch Interrupt**

A Phase Mismatch Interrupt occurs when the DMAMODE bit (R2 bit 1) is set,  $\overline{\text{REQ}}$  is active on the SCSI bus, and the SCSI phase signals  $\overline{\text{MSG}}$ ,  $\overline{\text{C}}/\text{D}$ , and  $\overline{I}/O$  do not match the corresponding bits in the Target Command Register. This interrupt is intended for use by the initiator to detect a change of phase by the target during a DMA transfer. When operating as a target, the SCSI phase lines will normally be asserted via the Target Command Register, so no phase mismatch will be generated unless another SCSI device is erroneously driving the phase lines to an unintended state.

The result of the continuous comparison of the SCSI phase lines to the Target Command Register contents is visible as the Phase Match bit (Read R5 bit 3). This flag operates irrespective of the state of DMAMODE and REQ. As long as a phase mismatch condition persists, the L5380/53C80 is prevented from recognizing active REQ inputs, and SCSI output data drivers are disabled.

The Phase Mismatch Interrupt is nonmaskable, however it will only occur when operating in DMAMODE. The expected read values for the Current SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

#### **Parity Error Interrupt**

A Parity Error Interrupt occurs when incorrect parity is detected during a read of the SCSI bus. Parity checking occurs under the following conditions: Parity is checked during a programmed I/O read of the Current SCSI Data Register (Read R0), when  $\overline{\text{CS}}$  and  $\overline{\text{IOR}}$  are active and the A2-0 lines are 000. Parity is also checked during DMA read operations (DMAMODE bit, R2 bit 1 is set) when  $\overline{ACK}$  is active for target receive, or  $\overline{REQ}$  is active for initiator receive.

The Parity Error latch is set when parity error checking is enabled and one of the above parity error conditions is encountered. This latch is

### TABLE 4. INTERRUPT READ VALUES

| Read Address 4 — Current SCSI Control Register |            |            |         |     |         |     |        |  |

|------------------------------------------------|------------|------------|---------|-----|---------|-----|--------|--|

| 7                                              | 6          | 5          | 4       | 3   | 2       | 1   | 0      |  |

| RST                                            | BSY        | REQ        | MSG     | C/D | Ī/O     | SEL | PARITY |  |

| SCSI B                                         | us Reset   | Interrup   | t       |     |         |     |        |  |

| Х                                              | 0          | 0          | 0       | 0   | 0       | 0   | 0      |  |

| Selecti                                        | on/Resel   | ection In  | terrupt |     |         |     |        |  |

| 0                                              | 0          | 0          | Х       | Х   | 1=RESEL | 1   | Х      |  |

| Loss o                                         | f Busy In  | terrupt    |         |     |         |     |        |  |

| 0                                              | 0          | 0          | 0       | 0   | 0       | 0   | 0      |  |

| Phase                                          | Mismatcl   | h Interrup | ot      |     |         |     |        |  |

| 0                                              | 1          | 1          | Х       | Х   | X       | 0   | Х      |  |

| Parity                                         | Error Inte | errupt     |         |     |         |     |        |  |

| 0                                              | Х          | Х          | Х       | Х   | Х       | Х   | Х      |  |

| End of                                         | DMA Inte   | errupt     |         |     |         |     |        |  |

| 0                                              | 1          | Х          | Х       | Х   | Х       | 0   | Х      |  |

#### Read Address 5 — DMA Status Register

| 7                | 6          | 5               | 4                     | 3              | 2             | 1   | 0   |

|------------------|------------|-----------------|-----------------------|----------------|---------------|-----|-----|

| END<br>OF<br>DMA | DMA<br>REQ | PARITY<br>ERROR | INTER-<br>RUPT<br>REQ | PHASE<br>MATCH | BUSY<br>ERROR | ATN | ACK |

| SCSI B           | us Reset   | Interrup        | t                     |                |               |     |     |

| 0                | 0          | 0               | 1                     | 1              | 0             | 0   | 0   |

| Selecti          | on/Resel   | ection In       | terrupt               |                |               |     |     |

| 0                | 0          | 0               | 1                     | Х              | 0             | Х   | 0   |

| Loss o           | f Busy In  | terrupt         |                       |                |               |     |     |

| 0                | 0          | 0               | 1                     | Х              | 1             | 0   | 0   |

| Phase            | Mismatc    | h Interrup      | ot                    |                |               |     |     |

| 0                | 0          | 0               | 1                     | 0              | Х             | Х   | 0   |

| Parity           | Error Inte | errupt          |                       |                |               |     |     |

| Х                | Х          | 1               | 1                     | Х              | Х             | Х   | Х   |

| End of           | DMA Inte   | errupt          |                       |                |               |     |     |

| 1                | 0          | 0               | 1                     | Х              | 0             | 0   | Х   |

|                  |            |                 |                       | I              | I             |     |     |

visible as bit 5 of the DMA Status Register (Read R5). The Parity Error Interrupt may be masked and setting of the Parity Error latch prevented by resetting the Enable Parity Check bit (Write R2 bit 5). The Parity Error latch can be reset by reading the Reset Error/Interrupt Register (Read R7). The expected read values for the Current SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

#### **End of DMA Interrupt**

An End of DMA Interrupt occurs when a valid EOP (End of Process) signal is detected during a DMA transfer. EOP is valid when EOP, DACK, and either IOR or IOW are simultaneously asserted for the minimum specified time. EOP inputs not occurring during I/O read or write operations are ignored.

The End of DMA latch is set whenever the DMAMODE bit (R2 bit 1) is set and a valid  $\overline{\text{EOP}}$  is received. This latch is visible as bit 7 of the DMA Status Register (Read R5). The End of DMA Interrupt may be masked by resetting the Enable EODMA Interrupt bit (Write R2 bit 3). This bit does not affect the End of DMA latch, however. The End of DMA latch can be reset by resetting the DMAMODE bit in the Mode Register. The expected read values for the Current SCSI Control Register and the DMA Status Register upon encountering this interrupt are given in Table 4.

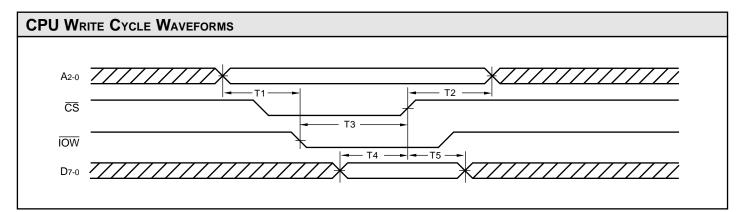

#### DATA TRANSFERS

The L5380/53C80 supports programmed I/O under CPU control or DMA transfer via a DMA controller when transferring information to and from the SCSI data bus. Programmed I/O can be implemented entirely in firmware or using minimum external logic for accessing the appropriate registers. Under DMA control, the L5380/53C80's DMA interface logic and internal state machines provide the necessary control of the  $\overline{\text{REQ}}$ - $\overline{\text{ACK}}$  handshake. Each type of transfer is fully described in the following sections.

#### Programmed I/O

Two forms of programmed I/O are supported by the L5380/53C80. For normal programmed I/O, the SCSI handshake is accomplished by setting bits in the Initiator or Target Command registers to assert SCSI control lines, and polling the Current SCSI Control and DMA Control registers for the appropriate responses. Since for this method the control is contained in firmware, the cycle times are relatively slow. It is most appropriate **SCSI Bus Controller**

for transferring small blocks of data such as SCSI command blocks or messages, where the overhead of setting up a DMA controller could be significant.

#### Pseudo DMA

An alternate method of programmed I/O allows the state machines of the L5380/53C80 to handle the SCSI handshake, thereby improving performance in systems which do not employ a hardware DMA controller. To implement Pseudo DMA, the DMAMODE bit is set. The CPU polls the DRQ bit in the DMA Control Register to determine when a byte should be written to or read from the

| TABLE 5.   TYPICAL INTERRUPT                         | Service Routine Polling Service                                        |

|------------------------------------------------------|------------------------------------------------------------------------|

| Read Address 5 > TEMP                                | : Read DMA Status Reg to variable TEMP                                 |

| IF TEMP "AND" HEX (10) = 0<br>THEN GO TO NEXT DEVICE | : IRQ not active, so L5380/L53C80 was not the source of this interrupt |

| TEMP "AND" HEX (AC) → TEMP                           | : Mask off irrevelant bits                                             |

| IF TEMP > HEX (7F) THEN<br>GO TO EODMA               | : End of DMA Interrupt                                                 |

| IF TEMP > HEX (1F) THEN<br>GO TO PARERR              | : Parity Error Interrupt                                               |

| IF TEMP > HEX (03) THEN<br>GO TO BYSERR              | : Loss of Busy Interrupt                                               |

| IF TEMP = HEX (00) THEN<br>GO TO PHASERR             | : Phase Mismatch Interrupt                                             |

| Read Address 4 → TEMP                                | : Read Current SCSI Control Reg<br>to variable TEMP                    |

| TEMP "AND" HEX (06) → TEMP                           | : Mask off irrevelant bits                                             |

| IF TEMP = HEX (06) THEN<br>GO TO RESEL               | : Reselection Interrupt                                                |

| IF TEMP = HEX (02) THEN<br>GO TO SEL                 | : Selection Interrupt                                                  |

| IF TEMP = HEX (00) THEN<br>GO TO RESET               | : SCSI Bus Reset Interrupt                                             |

L5380/53C80. When reading or writing, external logic must be used to decode the L5380/53C80 location and produce  $\overline{DACK}$ , since it is used by the internal state machines. Also,  $\overline{CS}$  must be suppressed since it may not be asserted simultaneously with  $\overline{DACK}$ .

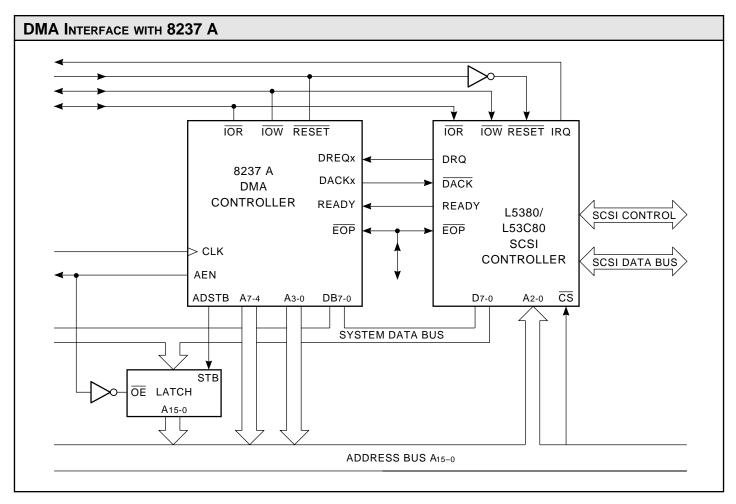

#### Normal DMA Mode

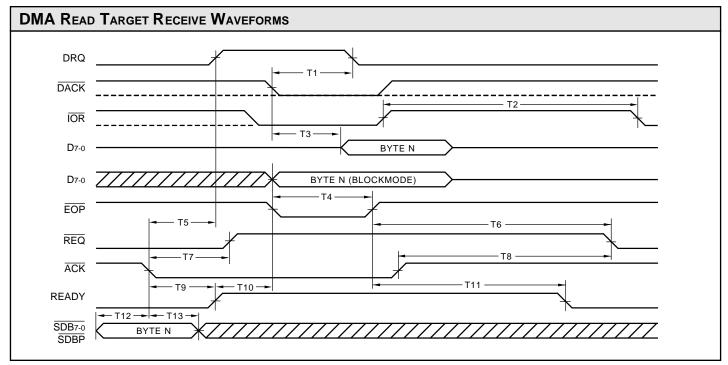

Normal DMA mode is obtained when the DMAMODE bit is set but the Blockmode bit is reset. The DMA process is started by writing to the Start DMA Send, Start DMA Initiator Receive, or Start DMA Target Receive locations as appropriate. Once started, the internal state machines of the L5380/53C80 manage the REQ -ACK handshake protocol, as well as the DRQ-DACK handshake with the DMA controller.

The L5380/53C80 will assert DRQ whenever it is ready to transfer a byte to or from the DMA controller. In response to DRQ, the controller asserts  $\overline{DACK}$  and  $\overline{IOR}$  to read the byte, or  $\overline{DACK}$  and  $\overline{IOW}$  to write a byte to the L5380/53C80. For write operations, the byte is latched at the rising edge of the logical AND of  $\overline{DACK}$  and  $\overline{IOW}$ . The transfer can be terminated by asserting  $\overline{EOP}$  during a read or write operation, or by resetting the DMAMODE bit.

#### **Block DMA Mode**

When the Blockmode bit is set, the DMA handshake is no longer dependent on interlocked DRQ-DACK cycles. Instead, the DMA controller may be allowed to free-run, with data flow throttled by inserting "wait-states" in the DMA transfer to or from the L5380/53C80. Wait-states, which are idle clock cycles inserted during the I/O read or write operation, are inserted by the DMA controller until the READY output of the L5380/ 53C80 goes true, allowing the bus cycle to conclude. The READY output will be deasserted under the following conditions: For send operations, READY will be false whenever the Output Data Register contains a byte which has not been transferred over the SCSI bus. This allows the DMA controller to access RAM to fetch the next byte, but postpones the end of the CPU bus cycle until the previous byte has been transferred, freeing the Output Data Register to receive it.

For receive operations, READY will be false whenever the Input Data Register is empty. This allows the DMA controller to address the RAM for a write operation, but postpones the end of the CPU bus cycle until the incoming byte is stored in the Input Data Register and is available on the CPU bus.

Note that when blockmode is employed, DACK may optionally remain asserted throughout the DMA transfer, since it is not used in an interlocked DMA handshake (Its interlock function is replaced by  $\overline{IOR}$ or  $\overline{IOW}$ ). Also, DRQ will be asserted in the normal way when operating in blockmode. To gain the abovementioned performance benefits, it should be used only to initiate the first byte transfer, with READY used to throttle succeeding transfers. This methodology is compatible with DMA controllers such as the Intel 8237 and AMD Am9516/9517.

In summary, blockmode operation offers the potential for improved transfer rates by overlapping the DMA memory access with the SCSI transfer. This is of particular value when used with DMA controllers capable of "flyby" operation, where the data is transferred directly from memory to the peripheral, and does not pass through the DMA controller itself. This transfer rate gain is achieved at the expense of locking up the CPU bus for a time equal to the SCSI transit time of the entire block.

### **SCSI Bus Controller**

This may be strongly preferable in some systems where net disk access time is a crucial performance factor. Also, the time required to arbitrate for the CPU bus on a byte-by-byte basis may well be longer than the cycles wasted waiting for SCSI transfers to take place, especially with fast peripherals which operate from a high speed sector buffer.

#### **Terminating DMA Transfers**

DMA transfers, either normal or blockmode, may be terminated in a number of ways. The following sections describe these methods, along with providing information about correct sequencing of various signals to effect a clean exit from a DMA process.

#### **EOP** Signal

The  $\overline{\text{EOP}}$  signal is usually generated by a DMA controller to indicate that its transfer counter has decremented to zero. In order to be recognized by the L5380/53C80, it should be asserted simultaneously with the DACK and IOR or IOW signals corresponding to the last byte in the transfer. Note that in the case of send operations, asserting  $\overline{\text{EOP}}$  indicates to the L5380/53C80 that SCSI transfers should cease after transmission of the byte loaded while EOP is asserted. In order to determine when this last byte has actually been sent, the Last Byte Sent flag in the Target Command Register may be examined. This flag is not present in the NCR implementation of the 5380, but is available in the 53C80, a nonpin-compatible variant. The  $\overline{\text{EOP}}$ input does not reset the DMAMODE bit, but after transmission of the last byte causes the internal state machine to return to an idle condition, so that no further SCSI handshaking will occur until another transmission is explicitly initiated. Note that the NCR version of the 5380, upon receiving an EOP, will stop asserting DRQ, but will continue to issue  $\overline{ACK}$ in response to additional  $\overline{\text{REQ}}$  inputs,

potentially causing data loss if the target initiates another data transmission without an intervening phase change. The L5380/53C80 prevents this spurious DMA handshake from occurring.

#### DMA Mode Bit

Resetting the DMAMODE bit in the Mode Register causes a hard reset of the internal DMA state machines, and thus an effective termination of a DMA transfer. Since unlike the EOP case the state machine is not allowed to exit gracefully, care must be taken in the timing of DMAMODE reset.

For receive operations, the DMAMODE bit should be reset after the last DRQ is received, but prior to asserting DACK to prevent an additional  $\overline{\text{REQ}}$  or  $\overline{\text{ACK}}$  from occurring. For normal DMA mode, resetting this bit will cause DRQ to go inactive. However, the last byte received remains in the SCSI Input Data Register and may be read either by the normal  $\overline{\text{DACK}}$  and  $\overline{\text{IOR}}$  DMA read or using a CPU read of Address 6. For blockmode DMA, READY will remain asserted when DMAMODE is reset, allowing the DMA controller to retrieve the last byte in the normal fashion. The NCR version of the 5380 fails to keep READY asserted when DMAMODE is reset, potentially causing deadlock on the CPU bus.

#### **Bus Phase Mismatch**

When operating in DMAMODE as an initiator, a bus phase mismatch can be used to terminate a data transfer. If the  $\overline{C}/D$ ,  $\overline{I}/O$ , and  $\overline{MSG}$  lines fail to match the corresponding bits in the Target Command Register, it will prevent recognition of  $\overline{REQ}$ , and will disable the SCSI data and parity output drivers. Also, when  $\overline{REQ}$  becomes active, an interrupt will be generated. Because  $\overline{REQ}$  is not recognized, the effect is to stop the DMA transfer, although the state machine does not return to idle until either DMAMODE is reset or a valid  $\overline{EOP}$  is received.

One caution should be observed when using phase changes to end DMA transfers: While this method does not require the initiator to keep a transfer counter, it depends on the target causing a phase change between any two consecutive information transfer phases. Since this is not required by the protocol, it must be guaranteed by the target software. Otherwise the target may begin a new information transfer without the initiator recognizing the boundary between the two.

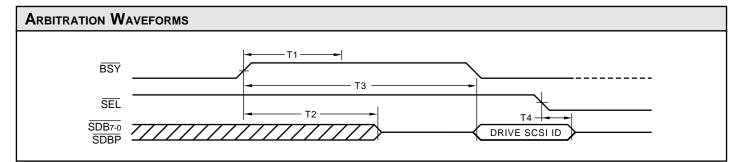

#### ARBITRATION

The L5380/53C80 contains on-chip hardware to assist in arbitrating for the SCSI bus. This arbitration logic cooperates with the host firmware to effect SCSI arbitration, as described in the following paragraphs:

The SCSI arbitration timeline begins with detection of a bus free condition at time to. Bus free is defined as  $\overline{BSY}$ and SEL inactive for at least a bus settle delay (400 ns). Following the bus settle delay, the SCSI device must wait an additional bus free delay of 800 ns, for a total of 1200 ns after to, prior to driving any signal. Thus a minimum of 1200 ns must elapse from initial deassertion of  $\overline{BSY}$  to the beginning of an arbitration attempt. A final constraint is that arbitration may not begin if more than a bus set delay (1800 ns) has elapsed since  $\overline{BSY}$ became active (arbitration began), corresponding to 2200 ns after to.

The CPU indicates a desire to arbitrate by setting the Arbitrate bit (R2 bit 0). When Arbitrate is set, the L5380/53C80 will monitor the state of BSY and SEL to detect a bus free condition. The actual implementation uses an internal delay line to provide a time reference for detection of a bus free condition. This delay is nominally 800 ns during which BSY and SEL must be inactive. This time represents the center of the window between the Bus Settle Delay (400 ns)

### **SCSI Bus Controller**

and the Bus Free Delay (400 + 800 = 1200 ns). When Bus Free is detected, the L5380/53C80 waits for an additional time of nominally 900 ns (1700 ns nominal since to) and asserts  $\overline{\text{BSY}}$  and the contents of the Output Data Register. This time represents the center of the 1200 ns–2200 ns window between the earliest and latest legal arbitration attempt. Since the actual delays are process and temperature dependent, they will vary in practice, but will always remain well within the specified limits.

Once arbitration has begun (BSY and the Output Data Register asserted,) the Arbitration In Progress bit (R1 bit 6) will be set, allowing the CPU to detect the fact that arbitration has begun. The CPU should then wait one arbitration delay (2.2 µs) before reading the bus to determine whether arbitration has been won or lost. The Lost Arbitration bit (R2 bit 7) will be active if the L5380/53C80 has detected SEL active on the SCSI bus, indicating that another SCSI device has declared itself the winner of the arbitration. **SEL** active also disables the SCSI output drivers, allowing the winning arbitrator to proceed with its transfer.

#### **BUG FIXES/ENHANCMENTS**

The NCR5380 and the Am5380 have some architectural bugs, both published and unpublished. The **LOGIC Devices L5380/53C80** was designed to eliminate these bugs while maintaining pin and architectural compatibility. A list of these errors along with solutions implemented in the L5380/ 53C80 is itemized below.

1. When executing blockmode DMA send operations, the READY signal is intended to insert memory wait states as a mechanism to throttle data transfer, with the DMA controller in a free-running loop. The NCR/ Am5380 erroneously allows the contents of the Output Data Register to be overwritten by subsequent bytes prior to acknowledgment of the

current byte by the SCSI receiver. This causes loss of data when operating in blockmode if the sender's DMA cycle is faster than the receiver's.

2. Assertion of EOP during blockmode DMA transfers fails to cause assertion of READY in the NCR/Am5380. This may prevent the CPU from becoming bus master and can result in lockup of the CPU bus in a not-ready state. In block DMA send mode when EOP is received, the L5380/53C80 reasserts READY immediately after transmitting the final byte. For receive mode, READY is asserted immediately.

3. When a valid EOP is detected, the NCR/Am5380 prevents assertion of additional DRQ's, but continues to respond to SCSI handshakes. This means that additional data transmitted without phase change may be lost. The L5380/53C80, like the NCR/Am5380 remains in DMAMODE after an EOP. However, the internal state machine returns to an idle condition and does not respond to additional SCSI handshake attempts until another data transfer is explicitly initiated.

4. When operating as an initiator in DMAMODE, the NCR/Am5380 leaves ACK asserted after receipt of a valid EOP, requiring the CPU to deassert it. When a valid EOP is detected, the L5380/53C80 deasserts ACK properly.

5. If the NCR/Am5380 is not terminated on the SCSI side, the floating  $\overline{\text{RST}}$ pin will cause spurious interrupts. The L5380/53C80 contains internal high value pullups to set unterminated SCSI pins to the inactive state.

6. During DMA send operations, when a valid  $\overrightarrow{EOP}$  signal is received by the NCR/Am5380, no convenient indication exists to indicate that the last byte of data (loaded simultaneously with  $\overrightarrow{EOP}$ ) has in fact been successfully transmitted. The L5380/53C80 provides Last Byte status bit mapped to bit 7 of the Target Command Register. This bit will be set after a valid  $\overrightarrow{EOP}$  has occurred, and the final byte has been transmitted successfully.

7. During the reselection phase, the NCR/AM5380 may reset the reselection interrupt if the contents of the Target Command Register do not match the current SCSI bus phase. The L5380/53C80 does not spuriously reset this interrupt.

### **SCSI Bus Controller**

8. In the NCR/Am5380, the phase mismatch interrupt is captured in an edge triggered fashion on the active edge of REQ. During reselection, this interrupt might not be generated even though a phase change has occurred. The reason for this is as follows:

- The initiator DMAMODE bit must be set in order to receive a phase-match interrupt.

- However, the DMAMODE bit cannot be set unless BSY is active.

- BSY will be driven active by the target only after the relesection has occurred.

- Once BSY has been asserted by the target, it may then assert REQ before the initiator has set the DMAMODE bit, and the initiator will then fail to generate an interrupt.

The L5380/53C80 interrupt latch will be set if a phase mismatch condition exists when the later of  $\overline{\text{REQ}}$  or DMAMODE become active. In this way, the mismatch will always be detected, even if the target asserts  $\overline{\text{REQ}}$  before the initiator sets DMAMODE.

#### MAXIMUM RATINGS Above which useful life may be impaired

| Storage temperature                        | –65°C to +150°C      |

|--------------------------------------------|----------------------|

| Vcc supply voltage with respect to ground  |                      |

| Output voltage                             | 0.0 V to <b>V</b> cc |

| Input voltage                              | 0.0 V to +5.5 V      |

| IoL Low Level Output Current (SCSI Bus)    | 48 mA                |

| IoL Low Level Output Current (other pins)  | 8 mA                 |

| IOH High Level Output Current (other pins) | –4 mA                |

| <b>OPERATING CONDITIONS</b> To meet specified electrical and switching characteristics |                             |                                                               |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|--|--|--|--|--|

| Mode                                                                                   | Temperature Range (Ambient) | Supply Voltage                                                |  |  |  |  |  |

| Active Operation, Commercial                                                           | 0°C to +70°C                | $4.75 \text{ V} \leq \textbf{V}\text{CC} \leq 5.25 \text{ V}$ |  |  |  |  |  |

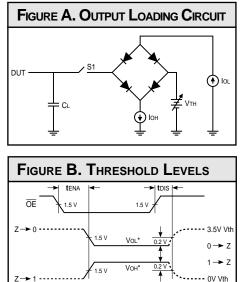

| ELECTRI     | ELECTRICAL CHARACTERISTICS Over Operating Conditions |                                                                             |     |     |     |      |  |  |

|-------------|------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol      | Parameter                                            | Test Condition                                                              | Min | Тур | Max | Unit |  |  |

| Vı∟         | Input Low Voltage                                    |                                                                             | 0.0 |     | 0.8 | V    |  |  |

| <b>V</b> IH | Input High Voltage                                   |                                                                             | 2.0 |     | Vcc | V    |  |  |

| VOL         | Output Low Voltage<br>(SCSI bus)                     | <b>V</b> CC = Min, <b>I</b> OL = 48 mA                                      |     |     | 0.5 | V    |  |  |

| VOL         | Output Low Voltage<br>(other pins)                   | VCC = Min, IOL = 8 mA                                                       |     |     | 0.5 | V    |  |  |

| <b>V</b> он | Output High Voltage<br>(other pins)                  | <b>V</b> CC = Min, <b>I</b> OH = -4 mA                                      | 3.5 |     |     | V    |  |  |

| lin         | Input Current*                                       | $V_{CC} = Max, V_{IN} = 0 - V_{CC} (SCSI bus)$                              |     |     | 65  | μA   |  |  |