# **LXT902**

# Ethernet Twisted-Pair Media Attachment Unit

## **General Description**

The LXT902 twisted-pair Media Attachment Unit (TP-MAU) is designed to allow Ethernet connections to use the existing twisted-pair wiring plant through an Ethernet Attachment Unit Interface (AUI). The LXT902 provides the electrical interface between the AUI and the twisted-pair wire.

LXT902 functions include level-shifted data pass-through from one transmission media to another, collision detection, Signal Quality Error (SQE) testing and automatic correction of polarity reversal on the twisted-pair input. It also includes LED drivers for transmit, receive, jabber, collision, reversed polarity detect and link functions. The LXT902 is an advanced CMOS device and requires only a single 5-volt power supply.

## **Applications**

- · Computer/workstation interface boards

- · LAN repeater

- External 10BASE-T transceiver (MAU)

#### **Features**

- Meets or exceeds IEEE 802.3 standards for AUI and 10BASE-T interface

- Direct interface to AUI and RJ-45 connectors

- Automatic AUI/RJ-45 selection

- Internal pre-distortion generation

- Internal common mode voltage generation

- · Jabber function

- Selectable link test, SQE test disable

- Twisted-pair receive polarity reverse detection and selectable polarity correction

- LED driver for transmit, receive, jabber, collision, link and reversed polarity indicators or for flashing status indicator

- Single 5 V supply, CMOS technology

- Available in 28-pin PLCC

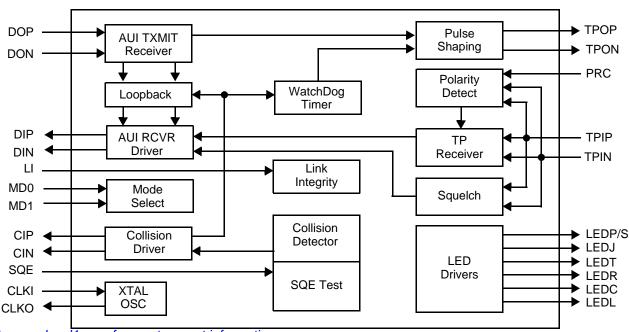

# LXT902 Block Diagram

Refer to www.level1.com for most current information.

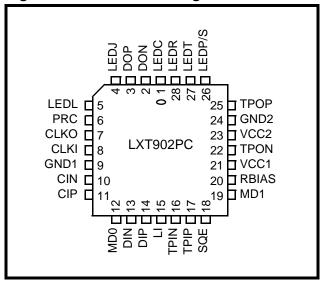

# PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

Figure 1: LXT902 Pin Assignments

Table 1: LXT902 Signal Descriptions

| Table 1: | LX 1902 Signal Descriptions |     |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------|-----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PLCC     | Symbol                      | I/O | Description                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2        | DON                         | I   | Data Out Negative and Data Out Positive. Differential input pair from the AUI                                                                                                                                                                                                                                                   |  |  |  |

| 3        | DOP                         | I   | transceiver DO circuit.                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4        | LEDJ                        | I/O | <b>Jabber LED Driver.</b> Active Low, open drain driver for the Jabber indicator LED. Output goes active when watchdog timer begins jab, and stays active until end of the unjab wait period (491 - 525 ms). When tied to ground, causes LEDP/S to act as a multi-function blinking status indicator.                           |  |  |  |

| 5        | LEDL                        | О   | <b>Link LED Driver.</b> Active Low, open drain driver for the Link indicator LED. Output is active except during Link Fail or when Link Integrity Test is disabled.                                                                                                                                                             |  |  |  |

| 6        | PRC                         | I/O | <b>Polarity Reverse Correction.</b> The LXT902 automatically corrects reversed polarity at TPI when PRC is tied High. In Test mode, this pin is a 10 MHz output.                                                                                                                                                                |  |  |  |

| 7        | CLKO                        | О   | Crystal Oscillator. The LXT902 requires either a 20 MHz crystal                                                                                                                                                                                                                                                                 |  |  |  |

| 8        | CLKI                        | I   | (or ceramic resonator) connected across these pins, or a 20 MHz external clock applied at CLKI with CLKO left unconnected.                                                                                                                                                                                                      |  |  |  |

| 9        | GND1                        | _   | Ground 1. Ground                                                                                                                                                                                                                                                                                                                |  |  |  |

| 10       | CIN                         | 0   | Collision Negative and Collision Positive. Differential driver output pair tied to the                                                                                                                                                                                                                                          |  |  |  |

| 11       | CIP                         | О   | collision presence pair of the Ethernet transceiver AUI cable. The collision presence signal is a 10 MHz square wave. This output is activated when a collision is detected on the network, during self-test by the SQE sequence, or after the watchdog timer has expired to indicate the transmit wire pair has been disabled. |  |  |  |

Table 1: LXT902 Signal Descriptions - continued

| Table 1: LX1902 Signal Descriptions – continued |        |     |                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------------------------------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PLCC                                            | Symbol | I/O | Description                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 12                                              | MD0    | I   | <b>Mode Select 0.</b> Selects operating modes in conjunction with MD1. See Table 2 for mode select options.                                                                                                                                                                                                                           |  |  |  |

| 13                                              | DIN    | О   | Data In Negative and Data In Positive. Differential driver pair connected to the                                                                                                                                                                                                                                                      |  |  |  |

| 14                                              | DIP    | О   | AUI transceiver DI circuit.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 15                                              | LI     | I   | <b>Link Integrity Test Enable.</b> Link integrity testing is enabled when this pin is tied High. With link test enabled, the LXT902 sends the link integrity signal in the absence of transmit traffic. It also recognizes received link test pulses, indicating the receive wire pair is present in the absence of transmit traffic. |  |  |  |

| 16                                              | TPIN   | I   | <b>Twisted-Pair Receive Inputs.</b> Differential receive inputs from the twisted-pair input                                                                                                                                                                                                                                           |  |  |  |

| 17                                              | TPIP   | I   | filter.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 18                                              | SQE    | I/O | <b>Signal Quality Error Test Enable.</b> SQE is enabled when this pin is tied High. When enabled, the LXT902 sends the signal quality error test sequence to the CI of the AUI cable after every successful transmission to the media. In Test mode, SQE becomes a 20 MHz output.                                                     |  |  |  |

| 19                                              | MD1    | I   | Mode Select 1. Selects operating modes in conjunction with MD0. (See Table 2.) MD1 clock input between 2.0 and 2.5 MHz enables Test mode.                                                                                                                                                                                             |  |  |  |

| 20                                              | RBIAS  | _   | <b>Resistor Bias Control.</b> Bias control pin for the operating circuit. Bias set from external resistor to ground. External resistor value = $12.4 \text{ k}\Omega \ (\pm 1\%)$ .                                                                                                                                                   |  |  |  |

| 21                                              | VCC1   | I   | <b>Power Supply 1.</b> +5 V power supply.                                                                                                                                                                                                                                                                                             |  |  |  |

| 22                                              | TPON   | О   | Twisted-Pair Transmit Outputs. Transmit drivers to the twisted-pair                                                                                                                                                                                                                                                                   |  |  |  |

| 25                                              | TPOP   | О   | output filter. The output is Manchester encoded and pre-distorted to meet the 10BASE-T template.                                                                                                                                                                                                                                      |  |  |  |

| 23                                              | VCC2   | I   | <b>Power Supply 2.</b> +5 V power supply.                                                                                                                                                                                                                                                                                             |  |  |  |

| 24                                              | GND2   | -   | Ground 2. Ground.                                                                                                                                                                                                                                                                                                                     |  |  |  |

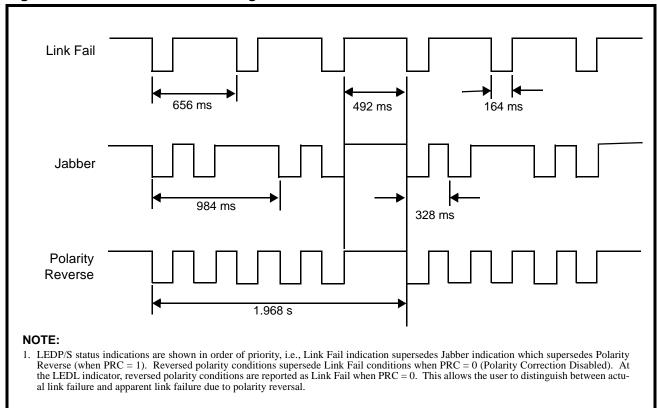

| 26                                              | LEDP/S | O   | Polarity/Status LED Driver. Active Low, open drain LED driver. In normal mode, LEDP/S is active when reversed polarity is detected. If LEDJ is tied to ground, LEDP/S indicates multiple status conditions as shown in Figure 11: On solid = Normal, 1 Blink = Link Down, 2 Blinks = Jabber, 5 Blinks = Polarity Reversed.            |  |  |  |

| 27                                              | LEDT   | О   | <b>Transmit LED Driver.</b> Active Low, open drain driver for the Transmit indicator LED. Output is active during transmit.                                                                                                                                                                                                           |  |  |  |

| 28                                              | LEDR   | О   | <b>Receive LED Driver.</b> Active Low, open drain driver for the Receive indicator LED. Output is active during receive.                                                                                                                                                                                                              |  |  |  |

| 1                                               | LEDC   | О   | Collision LED Driver. Active Low, open drain driver for the Collision indicator LED. Output is active when a collision occurs.                                                                                                                                                                                                        |  |  |  |

## **FUNCTIONAL DESCRIPTION**

## Introduction

The LXT902 Media Attachment Unit (MAU) interfaces the Attachment Unit Interface (AUI) to the unshielded twisted-pair cables, transferring data in both directions between the two. The AUI side of the interface comprises three circuits: Data Output (DO), Data Input (DI) and Control Interface (CI). The twisted-pair network side of the interface comprises two circuits: Twisted-Pair Input (TPI) and Twisted-Pair Output (TPO). In addition to these five basic circuits, the LXT902 also contains: crystal oscillator circuitry, separate power and ground pins for analog and digital circuits, mode selection logic (see Table 2) and six LED drivers for status indications.

Table 2: Mode Select Options

| MD1  | MD0   | Mode                       |

|------|-------|----------------------------|

| Low  | Low   | 10BASE-T compliant MAU     |

| Low  | High  | Reduced squelch level      |

| High | Low   | Half current AUI driver    |

| High | High  | DO, DI & CI ports disabled |

| High | Clock | Test Mode, Jabber on       |

| Low  | Clock | Test mode, Jabber disabled |

Functions are defined from the AUI side of the interface. The LXT902 Transmit function refers to data transmitted by the Data Terminal Equipment (DTE) through the AUI and MAU to the twisted-pair network. The LXT902 Receive function refers to data received by the DTE through the MAU and AUI from the twisted-pair network. In addition to basic transmit and receive functions, the LXT902 performs all required functions defined by the IEEE 802.3 10BASE-T MAU specification such as collision detection, link integrity testing, Signal Quality Error (SQE), jabber control and loopback.

# **Transmit Function**

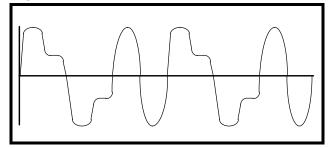

The LXT902 transfers Manchester encoded data from the AUI port of the DTE (the DO circuit) to the twisted-pair network (the TPO circuit). The output signal on TPON and TPOP is pre-distorted to meet the 10 BASE-T jitter template, and filtered to meet FCC requirements. The output waveform (after the transmit filter) is shown in Figure 2. If the differential inputs at the DO circuit fall

below 75% of the threshold level for 8 bit times (typical), the LXT902 transmit function will enter the idle state. During idle periods, the LXT902 transmits link integrity test pulses on the TPO circuit.

Figure 2: LXT902 TPO Output Waveform

# Receive Function

The LXT902 receive function transfers serial data from the twisted-pair network (the TPI circuit) to the DTE (over the DI circuit of the AUI). An internal squelch function discriminates noise from link test pulses and valid data streams. Only valid data streams activate the receive function. If the differential inputs at the TPI circuit fall below 75% of the threshold level (unsquelched) for 8 bit times (typical), the LXT902 receive function will enter the idle state. The TPI threshold can be reduced by approximately 3 dB to allow for longer loops in low-noise environments. The reduced threshold is selected when MD1 = Low and MD0 = High.

# Polarity Reverse Function

The LXT902 polarity reverse function uses both link pulses and end-of-frame data to determine polarity of the received signal. A reversed polarity condition is detected when eight opposite receive link pulses are detected without receipt of a link pulse with the expected polarity. Reversed polarity is also detected if four frames are received with a reversed start-of-idle. Whenever polarity is reversed, these two counters are reset to zero. If the LXT902 enters the link fail state, and no data or link pulses are received within 96 to 128 ms, the polarity is reset to the default non-flipped condition. If Link Integrity is disabled, polarity detection is based only on received data pulses.

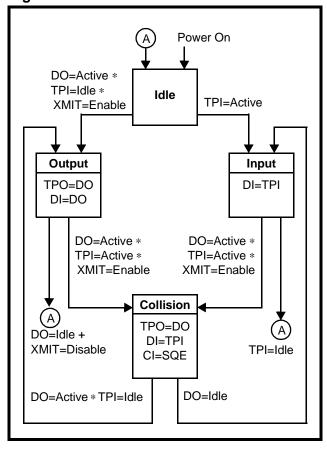

# Collision Detection Function

The collision detection function operates on the twisted-pair side of the interface. A collision is defined as the simultaneous presence of valid signals on both the TPI circuit and the TPO circuit. The LXT902 reports collisions to the AUI by sending a 10 MHz signal over the CI circuit. The collision report signal is output no more than 9 bit times (BT) after the chip detects a collision. If the TPI circuit becomes active while there is activity on the TPO circuit, the TPI data is passed to the DTE over the DI circuit, disabling the loopback. Figure 3 is a state diagram of the LXT902 collision detection function (refer to IEEE 802.3 10BASE-T specification).

Figure 3: Collision Detection Function

# **Loopback Function**

The LXT902 loopback function operates in conjunction with the transmit function. Data transmitted by the DTE is internally looped back within the LXT902 from the DO pins to the DI pins and returned to the DTE. The loopback function is disabled when a data collision occurs, clearing the DI circuit for the TPI data. Loopback is also disabled during link fail and jabber states.

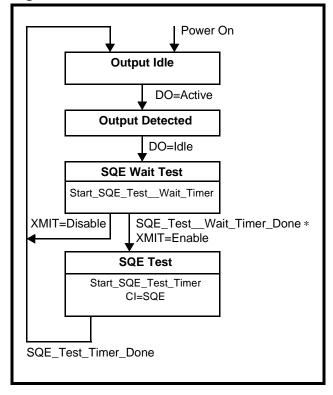

# SQE Test Function

Figure 4 is a state diagram of the SQE Test function. The SQE test function is enabled when the SQE pin is tied High. When enabled, the SQE test sequence is transmitted to the controller after every successful transmission on the 10BASE-T network. When a successful transmission is completed, the LXT902 transmits the SQE signal to the AUI over the CI circuit for 10 BT  $\pm$  5 BT. The SQE function can be disabled for hub applications by tying the SQE pin to ground.

Figure 4: SQE Function

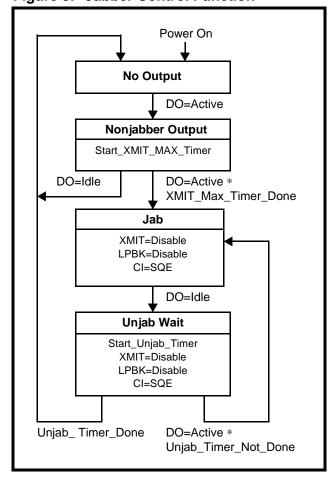

# **Jabber Control Function**

Figure 5 is a state diagram of the LXT902 Jabber control function. The LXT902 on-chip watchdog timer prevents the DTE from locking into a continuous transmit mode. When a transmission exceeds the time limit, the Watchdog timer disables the transmit and loopback functions, and sends the SQE signal to the DTE over the CI circuit. Once the LXT902 is in the jabber state, the DO circuit must remain idle for a period of 491 to 525 ms before it will exit the jabber state.

Figure 5: Jabber Control Function

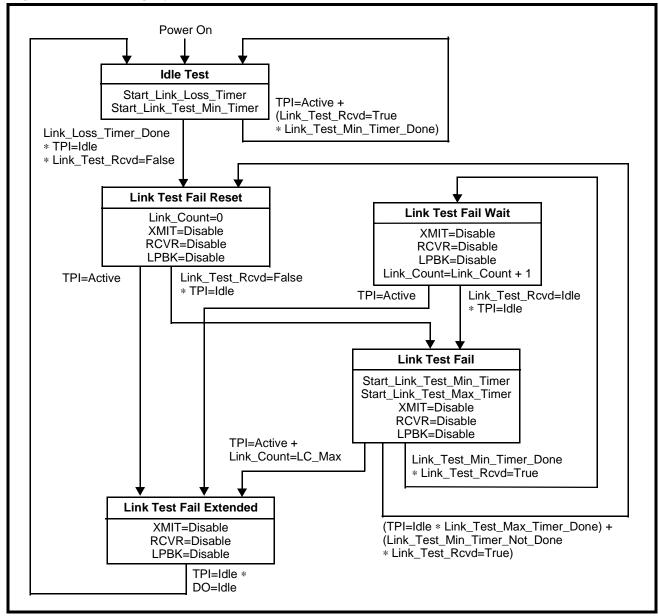

# Link Integrity Test Function

Figure 6 is a state diagram of the LXT902 Link Integrity Test Function. The Link Integrity Test is used to determine the status of the receive side twisted-pair cable. The link integrity test is enabled when the LI pin is tied High. When enabled, the receiver recognizes link integrity pulses which are transmitted in the absence of receive traffic. If no serial data stream or link integrity pulses are detected within 50 - 150 ms, the chip enters a link fail state and disables the transmit and loopback functions. The LXT902 ignores any link integrity pulse with interval less than 2 - 7 ms. The LXT902 will remain in the link fail state until it detects either a serial data packet or two or more link integrity pulses.

# Test Mode

The LXT902 Test mode is selected when a 2 - 2.5 MHz clock is input on the MD0 mode select pin. Test mode sets the internal counter chains to run at 1024 times their normal speed. The maximum transmit time, unjab time, Link Integrity timing and LED timing are reduced by a factor of 1024. During test operation, 10 MHz and 20 MHz signals are output on the PRC and SQE pins, respectively. When Test mode is selected, the SQE function cannot be disabled. In Test mode the PRC function can be disabled by the LI pin. Jabber can be disabled by setting MD1 Low.

Figure 6: Link Integrity Test Function

## **APPLICATION INFORMATION**

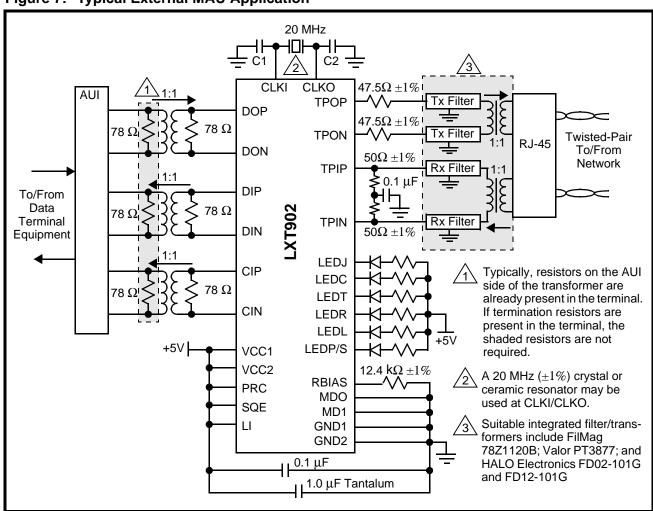

# External MAU

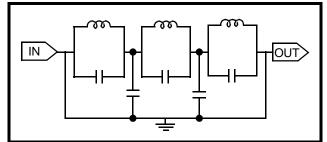

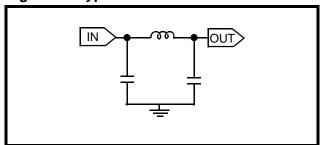

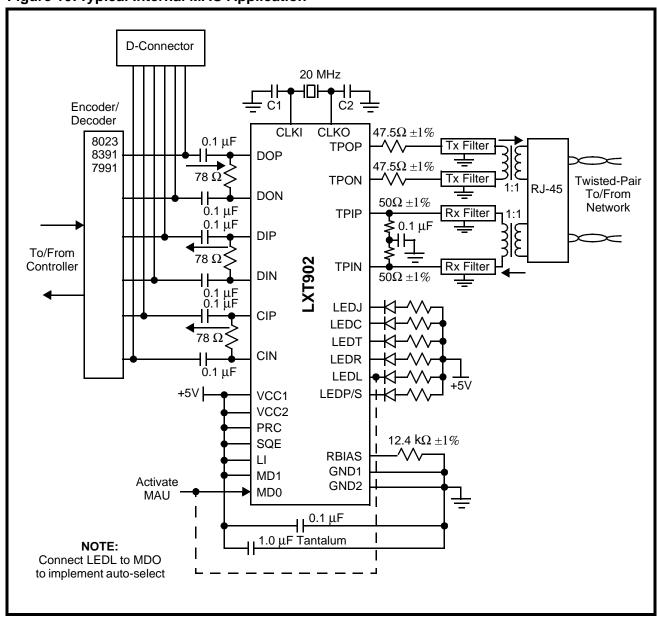

Figure 7 shows the LXT902 in a typical external MAU application, interfacing between an AUI and the RJ-45 connectors of the twisted-pair network. A 20 MHz crystal (or ceramic resonator) connected across CLKI and CLKO provides the required clock signal. Transmit and receive filters are required in the TPO and TPI circuits. Details of the transmit and receive filters are shown in Figures 8 and 9, respectively. (Differential filters are also recommended.)

## Internal MAU

Figure 10 shows an internal MAU application which takes advantage of the LXT902's unique AUI/10BASE-T switching feature to select either the D-connector (AUI) or the RJ-45 connector (10BASE-T). No termination resistors are used on the LXT902 side of the AUI interface

to prevent impedance mismatch with the drop cable. The half current drive mode is used to maintain the same voltage levels in the absence of termination resistors. This application uses capacitive coupling instead of transformer coupling. MD1 is tied High so MD0 functions as the mode control switch.

When MD0 is Low, the half current drive mode is selected. When MD0 is High, the LXT902 is effectively removed from the circuit. The 902 AUI ports (DO, DI and CI) are disabled isolating the LXT902 from the AUI. The LXT902 DI and CI ports go to a high impedance state and the DO port is ignored. To implement an auto-select function, LEDL can be tied to MD0. This activates the 902/AUI interface when the TP link is active (data or link integrity pulses) and disables it when the link is inactive.

Figure 7: Typical External MAU Application

Figure 8: Typical Transmit Filter

Figure 9: Typical Receive Filter

Figure 10: Typical Internal MAU Application

# **TEST SPECIFICATIONS**

#### **NOTE**

The minimum and maximum values in Tables 3 through 9 and Figure 11 represent the performance specifications of the LXT902 and are guaranteed by test, except where noted by design. Minimum and maximum values in Tables 5 through 9 apply over the recommended operating conditions specified in Table 4.

**Table 3: Absolute Maximum Values**

| Parameter                     | Symbol | Min  | Max  | Units |

|-------------------------------|--------|------|------|-------|

| Supply voltage                | Vcc    | -0.3 | 6    | V     |

| Ambient operating temperature | TA     | 0    | 70   | °C    |

| Storage temperature           | Tstg   | -65  | +150 | °C    |

#### **CAUTION**

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Table 4: Recommended Operating Conditions**

| Parameter                                 | Symbol | Min  | Тур | Max  | Units | Test Conditions |

|-------------------------------------------|--------|------|-----|------|-------|-----------------|

| Recommended supply voltage <sup>1,2</sup> | Vcc    | 4.75 | 5.0 | 5.25 | V     | _               |

| Recommended operating temperature         | Тор    | 0    | _   | 70   | °C    | -               |

<sup>1.</sup> Voltages with respect to ground unless otherwise specified.

Table 5: I/O Electrical Characteristics

| Parameter                                     | Sym  | Min | Typ <sup>1</sup> | Max | Units | Test Conditions                       |

|-----------------------------------------------|------|-----|------------------|-----|-------|---------------------------------------|

| Input Low voltage <sup>2</sup>                | VIL  | _   | _                | 0.8 | V     | _                                     |

| Input High voltage <sup>2</sup>               | Vih  | 2.0 | _                | _   | V     | _                                     |

| Output Low voltage<br>(Open drain LED driver) | Voll | _   | -                | 0.7 | V     | IOLL = 10 mA                          |

| Supply Current                                | ICC  | -   | 60               | 70  | mA    | Line Idle                             |

| (Vcc1=Vcc2=5.25 V)                            |      | _   | 125              | 140 | mA    | Line Active,<br>transmitting all ones |

| Input Leakage Current <sup>3</sup>            | ILL  | _   | ±1               | ±10 | μΑ    | Input between VCC and GND             |

| Three state leakage current (high Z)          | ITS  | _   | ±1               | ±10 | μА    | Output between VCC and GND            |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> Maximum voltage differential between VCC1 and VCC2 must not exceed 0.3 V.

$<sup>2. \ \</sup> MD0, MD1, SQE, PRC, and \ LI \ pins. \ MD0 \ clock \ (test \ mode) \ must \ be \ CMOS \ level \ input.$

<sup>3.</sup> Not including TPIN, TPIP, DOP, or DON.

**Table 6: AUI Electrical Characteristics**

| Parameter                      | Symbol | Min  | Typ <sup>1</sup> | Max   | Units | Test Conditions     |

|--------------------------------|--------|------|------------------|-------|-------|---------------------|

| Input Low current              | IIL    | _    | _                | -700  | μA    | _                   |

| Input High current             | Іін    | _    | _                | 500   | μΑ    | -                   |

| Differential output voltage    | Vod    | ±550 | _                | ±1200 | mV    | -                   |

| Differential squelch threshold | VDS    | _    | 220              | _     | mV    | -                   |

| Receive input impedance        | Rz     |      | 20               | 1     | kΩ    | Between DOP and DON |

<sup>1.</sup> Typical values are at 25  $^{\circ}$ C and are for design aid only; not guaranteed and not subject to production testing.

**Table 7: Transmit Characteristics**

| Parameter                                    | Sym  | Minimum | Typical <sup>1</sup> | Maximum | Units | Test Conditions                                                     |

|----------------------------------------------|------|---------|----------------------|---------|-------|---------------------------------------------------------------------|

| Transmit output impedance                    | Zout | _       | 5                    | ı       | Ω     | _                                                                   |

| Transmit timing jitter addition <sup>2</sup> | -    | -       | -                    | ±8      | ns    | After Tx filter,<br>0 line length                                   |

| Transmit timing jitter addition <sup>2</sup> | _    | -       | -                    | ±3.5    | ns    | After Tx filter and line model specified by IEEE 802.3 for 10BASE-T |

<sup>1.</sup> Typical values are at 25° C and are for design aid only; not guaranteed and not subject to production testing.

**Table 8: Receive Characteristics**

| Parameter                                   | Sym  | Minimum | Typical <sup>1</sup> | Maximum | Units | Test Conditions   |

|---------------------------------------------|------|---------|----------------------|---------|-------|-------------------|

| Receive input impedance                     | ZIN  | _       | 20                   | _       | kΩ    | Between TPIP/TPIN |

| Differential squelch threshold              | VDS  | _       | 420                  | _       | mV    | -                 |

| Reduced squelch threshold                   | Vdsr | _       | 300                  | _       | mV    | -                 |

| Receive timing jitter addition <sup>2</sup> | _    | _       | _                    | 1.5     | ns    | -                 |

<sup>1.</sup> Typical values are at  $25^{\circ}$  C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> Parameter is guaranteed by design; not subject to production testing.

<sup>2.</sup> Parameter is guaranteed by design; not subject to production testing.

**Table 9: Switching Characteristics**

|                       | Parameter                                                     | Min  | Typ <sup>1</sup> | Max  | Units |

|-----------------------|---------------------------------------------------------------|------|------------------|------|-------|

| Jabber Timing         | Maximum transmit time <sup>2</sup>                            | 98.5 | -                | 131  | ms    |

|                       | Unjab time <sup>2</sup>                                       | 491  | _                | 525  | ms    |

|                       | Time from Jabber to CS0 on CIP/CIN <sup>3</sup>               | 0    | _                | 900  | ns    |

| Link Integrity Timing | Time link loss <sup>2</sup>                                   | 65   | _                | 66   | ms    |

|                       | Time between Link Integrity Pulses <sup>2</sup>               | 9    | _                | 11   | ms    |

|                       | Interval for valid receive Link Integrity Pulses <sup>2</sup> | 4.1  | _                | 65   | ms    |

| Collision Timing      | Simultaneous TPI/TPO to CSO state on CIN/CIP                  | 0    | _                | 900  | ns    |

|                       | DO loopback to TPI on DI <sup>3</sup>                         | 300  | _                | 900  | ns    |

|                       | CS0 state delay after TPI/DO idle                             | _    | -                | 900  | ns    |

|                       | CS0 High pulse width                                          | 40   | -                | 60   | ns    |

|                       | CS0 Low pulse width                                           | 40   | _                | 60   | ns    |

|                       | CS0 frequency                                                 | -    | 10               | _    | MHz   |

| SQE Timing            | SQE signal duration                                           | 500  | _                | 1500 | ns    |

|                       | Delay after last positive transition of DO                    | 0.6  | -                | 1.6  | μs    |

| LED Timing            | LEDC, LEDT, LEDR on time <sup>2</sup>                         | 100  | _                | _    | ms    |

|                       | LEDP/S on time <sup>2</sup> (See Figure 11)                   | _    | 164              | _    | ms    |

|                       | LEDP/S period <sup>2</sup> (Figure 11)                        | _    | 328              | _    | ms    |

| General               | Receive start-up delay                                        | 0    | _                | 500  | ns    |

|                       | Transmit start-up delay                                       | 0    | _                | 200  | ns    |

|                       | Loopback start-up delay                                       | 0    | _                | 500  | ns    |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> Switching times reduced by a factor of 1024 during Test mode.

<sup>3.</sup> Parameter is guaranteed by design; not subject to production testing.

Figure 11: LEDP/S Indication Timing

# **MECHANICAL SPECIFICATIONS**

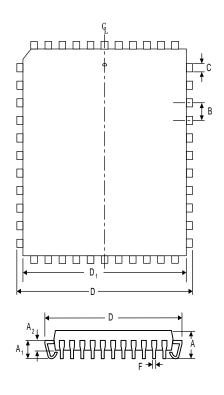

Figure 12: LXT902PC Package Specifications

#### 28-Pin Plastic Leaded Chip Carrier

- Part Number LXT902PC

- Commercial Temperature Range (0°C to 70°C)

| D:  | Inc   | hes   | Millimeters |        |  |

|-----|-------|-------|-------------|--------|--|

| Dim | Min   | Max   | Min         | Max    |  |

| A   | 0.165 | 0.180 | 4.191       | 4.572  |  |

| A1  | 0.090 | 0.120 | 2.286       | 3.048  |  |

| A2  | 0.062 | 0.083 | 1.575       | 2.108  |  |

| В   | 0.050 | _     | 1.270       | _      |  |

| С   | 0.026 | 0.032 | 0.660       | 0.813  |  |

| D   | 0.485 | 0.495 | 12.319      | 12.573 |  |

| D1  | 0.450 | 0.456 | 11.430      | 11.582 |  |

| F   | 0.013 | 0.021 | 0.330       | 0.533  |  |

# **NOTES**

Table 10: Changes from Revision 2.1 to Revision 2.2 (10/11/99)

| Section                      | Page  | Change | Text                                                                                                                                       |

|------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Features                     | Front | Modify | Delete reference to DIP.                                                                                                                   |

| Figure 1                     | 2     | Modify | Delete DIP pin assignment.                                                                                                                 |

| Pin Assignments              |       |        |                                                                                                                                            |

| Table 1                      | 2     | Modify | Delete DIP signal descriptions.                                                                                                            |

| Signal Descriptions          |       |        |                                                                                                                                            |

| Test Specifications          | 10    | Modify | Add text to NOTE, "Minimum and maximum values in Tables 5 through 9 apply over the recommended operating conditions specified in Table 4". |

|                              | 10-12 | Modify | Remove "Over Recommended Range" from headings in Tables 5 through 9.                                                                       |

| Mechanical<br>Specifications | 14    | Delete | Remove LXT902NC Package Specification (was Figure 12) and renumber subsequent figure.                                                      |

## **Corporate Headquarters**

9750 Goethe Road

Sacramento, California 95827 Telephone: (916) 855-5000

Fax: (916) 854-1102 Web: www.level1.com

# International

# **The Americas**

#### Eastern Area Headquarters & Western Area **Northeastern Regional Office**

**EAST**

234 Littleton Road, Unit 1A Westford, MA 01886

USA

Tel: (978) 692-1193 Fax: (978) 692-1124

# **Headquarters**

3375 Scott Blvd., #110 Santa Clara, CA 95054

**WEST**

USA

Tel: (408) 496-1950 Fax: (408) 496-1955

#### ASIA/PACIFIC

#### Asia / Pacific Area **Headquarters**

101 Thomson Road United Square #08-01 Singapore 307591

Singapore

Tel: +65 353 6722 Fax: +65 353 6711

#### **EUROPE**

#### European Area Headquarters & **Southern Regional Office**

Parc Technopolis-Bat. Zeta 3, avenue du Canada -Z.A. de Courtaboeuf Les Ulis Cedex 91974

France

Tel: +33 1 64 86 2828 Fax: +33 1 60 92 0608

#### **North Central Regional Office**

One Pierce Place Suite 500E Itasca, IL 60143

Tel: (630) 250-6044 Fax: (630) 250-6045

#### **South Central Regional Office**

800 East Campbell Road Suite 199

Richardson, TX 75081 **USA**

Tel: (972) 680-5207 Fax: (972) 680-5236

#### Central Asia/Pacific **Regional Office**

12F-1, No. 128, Section3, Ming Sheng East Road Taipei, Taiwan,

R.O.C.

Tel: +886 2 2547 5227 Fax: +886 2 2547 5228

#### Central Europe **Regional Office**

Lilienthalstr. 25 D-85399 Hallbergmoos

Germany

Tel: +49 81 16 006 817 Fax: +49 81 16 006 815

#### Southeastern **Regional Office**

4020 WestChase Blvd Suite 100

Raleigh, NC 27607

**USA**

**USA**

Tel: (919) 836-9798 Fax: (919) 836-9818

#### Southwestern **Regional Office**

28203 Cabot Road Suite 300

Laguna Niguel, CA 92677

**USA**

Tel: (949) 365-5655 Fax: (949) 365-5653

#### Northern Asia/Pacific **Regional Office**

Nishi-Shinjuku, Mizuma **Building 8F**

3-3-13, Nishi-Shinjuku, Shinjuku-Ku

Tokyo, 160-0023 Japan Tel: +81 3 3347-8630 Fax: +81 3 3347-8635

#### **Northern Europe Regional Office**

Torshamnsgatan 35 164/40 Kista/Stockholm,

Sweden

Tel: +46 8 750 3980 Fax: +46 8 750 3982

#### Latin/South America

9750 Goethe Road Sacramento, CA 95827

USA

Tel: (916) 855-5000 Fax: (916) 854-1102

# Israel

#### **Regional Office**

Regus Instant Offices-Harel House 3 Abba Hillel Silver Street Ramat Gan, 52522 Israel

Tel: +972-3-754-1130 Fax: +972-3-754-1100

| <u>Revision</u> | <u>Date</u> | <u>Status</u>                                             |

|-----------------|-------------|-----------------------------------------------------------|

| 2.2             | 11/99       | Take out references to DIP package on pages 1, 2, and 14. |

| 2.1             | 04/97       | Minor format changes for website posting.                 |

| 2.0             | 04/96       | Major re-format to separate Test Specifications.          |

The products listed in this publication are covered by one or more of the following patents. Additional patents pending. 5,008,637;5,028,888;5,057,794;5,059,924;5,068,628;5,077,529;5,084,866;5,148,427;5,153,875;5,157,690;5,159,291;5,162,746;5,166,635;5,181,228;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,162,746;5,165,204,880; 5,249,183; 5,257,286; 5,267,269; 5,267,746; 5,461,661; 5,493,243; 5,534,863; 5,574,726; 5,581,585; 5,608,341; 5,671,249; 5,666,129; 5,701,099