# LR38539

# PLL Frequency Synthesizer 1.2 GHz/500 MHz

(Model No.: LR38539)

Issue Date: April 7, 1998

# CONTENTS

|    | 1. Description                                                                             |    |   | • | • | • | • | • | • | • | • | • | • | • | • | •   | 2 |

|----|--------------------------------------------------------------------------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|

|    | 2. Features                                                                                |    |   | • | • | • | • | • | • | • | • |   | • | • | • |     | 2 |

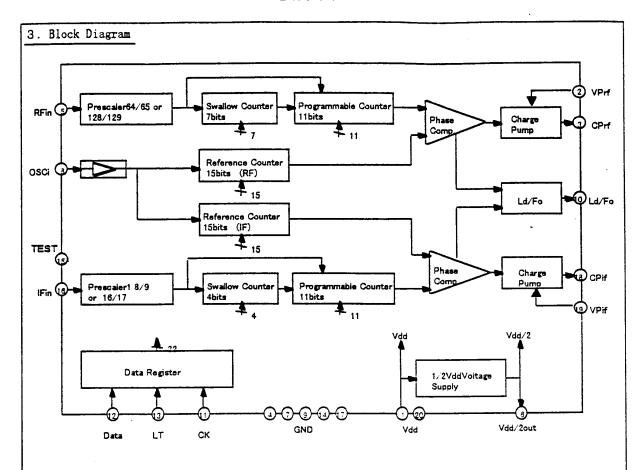

|    | 3. Block Diagram                                                                           |    |   | • | • | • | • | • | • | • |   | • | • | • | • | •   | 3 |

| 4. | Pin Connections 4-1 Pin Table 4-2 Pin Diagram                                              | •  | • | • | ٠ | • | • | ٠ | • | • | • | • | • | • |   | 3   |   |

| 5. | Pin Description                                                                            | •  | • | • |   | • | • | • | • | • | • | • | • | • |   | 5   |   |

| ŝ. | Functional Description                                                                     |    |   |   | • | • | • |   |   | • | • | • |   |   |   | 5   |   |

| 7. | Absolute Maximum Ratings                                                                   | •  |   | • | • | • | • | • |   | • | • |   |   | • |   | 8   |   |

| 8. | Electrical Characteristics $8-1$ Recommended Operating Con $8-2$ Electrical Characteristic | di |   |   |   | • | • | • | • | • | • | • | • | • |   | 9   |   |

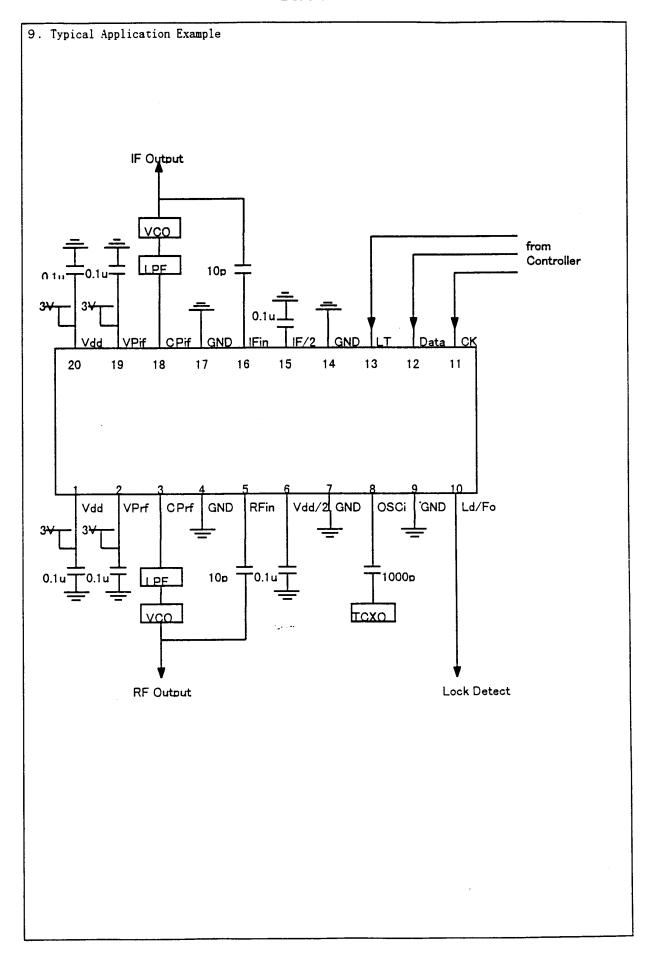

| 9  | Typical Application Example                                                                |    |   |   |   |   |   |   | • |   |   |   |   |   |   | 1 0 |   |

#### 1. Description

This IC of monolithic, a low power Phase Locked Loop (PLL) Frequency Synthesizers, is designed to be used as a local oscillator for the RF and the IF of a dual conversion transceiver. It is fabricated using Sharp's CMOS process.

This Chip is integrated two dual modulus prescalers. One is a 64/65 or a 128/129 prescaler for the RF synthesizer, and Another one is a 8/9 or a 16/17 prescaler for the IF synthesizer. The RF synthesizers have 7bits A (IF synthesizers have 4bits) and 11bits N pulse swallow counters. The Reference counter is 15bits Programmable counter. It contains two digital phase comparator, for the RF and IF, with charge pump. PLL synthesizer is controlled by serial data. That is transferred into this IC via a three wire interface (Data, LT, CK). This IC is very low current consumption; 2.8mA at 3V. This is available in a 20-pin SSOP surface mount plastic package.

#### 2. Features

Process(structure) CMOS

Chip Material Silicon

Wafer substrate type SOI

Package Type 2 O pin TSSOP

Package Material Plastic

Maximum Operating Frequency RF-PLL 1.2GHz

IF-PLL 500MHz

Current Consumption 2. 8 mA (Type) Operating Voltage Range 2.  $70 \sim 3.30 \text{ V}$

Not designed or rated as radiation hardened.

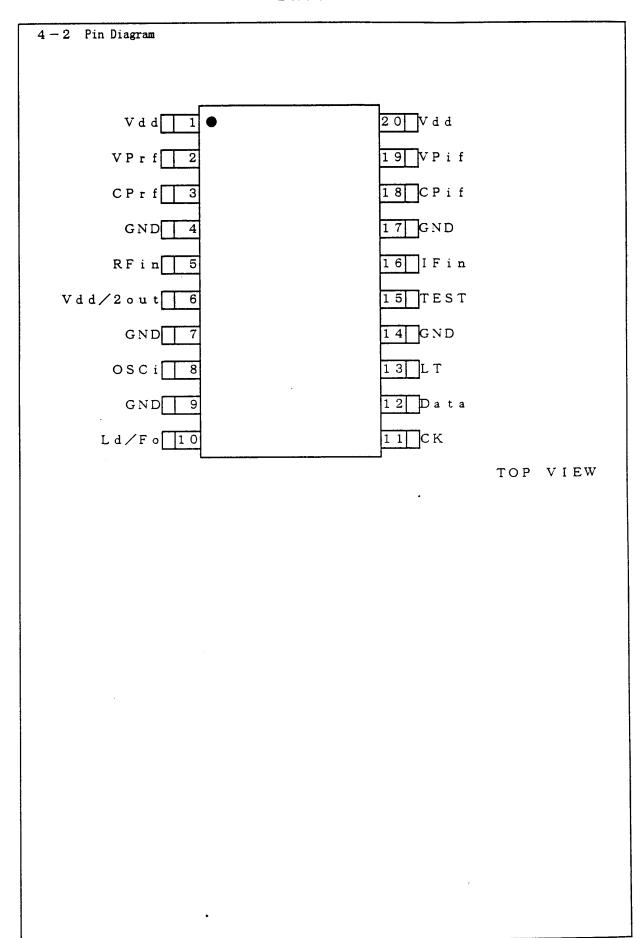

# 4. Pin Connections

4-1 Pin Table

| PinNo. | I/0 | Pin Name | PinNo. | 1/0 | Pin Name |

|--------|-----|----------|--------|-----|----------|

| 1      | _   | Vdd      | 1 1    | I   | CK       |

| 2      | _   | VPrf     | 1 2    | I   | Data     |

| 3      |     | CPrf     | 1 3    | I   | LT       |

| 4      | _   | GND      | 1 4    | _   | GND      |

| 5      | _   | RFin     | 15     | I   | TEST     |

| 6      | _   | Vdd/2out | 1 6    | I   | IFin     |

| 7      | -   | GND      | 1 7    | _   | GND      |

| 8      | I   | OSCi     | 18     | 0   | CPif     |

| 9      | _   | GND      | 1 9    | -   | VPif     |

| 10     | 0   | Ld/Fo    | 2 0    | -   | Vdd      |

#### 5. Pin Description

| PinNo. | Pin Name | 1/0 | Description                                              |

|--------|----------|-----|----------------------------------------------------------|

| 1      | Vdd      | _   | Power Supply Voltage Input. Bypass capacitors should be  |

|        |          |     | placed as close as possible to this pin and be connected |

|        |          |     | directly to the ground plane.                            |

| 2      | VPr f    |     | Power Supply Input for RF Charge pump.                   |

| 3      | CPrf     | 0   | RF Charge pump output. Constant current output.          |

| 4      | GND      | _   | Ground.                                                  |

| 5      | RFin     | I   | RF prescaler input from the RF VCO.                      |

| 6      | Vdd/2out | 0   | Vdd/2 Voltage supply output. Bypass capacitors should be |

|        |          |     | placed as close as possible to this pin and be connected |

|        |          |     | directly to the ground plane.                            |

| 7      | GND      | 1   | Ground.                                                  |

| 8      | OSCi     | I   | Reference Oscillator input.                              |

| 9      | GND      | _   | Ground.                                                  |

| 1 0    | Ld/Fo    | 0   | Multiplexed output to the RF/IF Lock detect and RF/IF or |

|        |          |     | reference dividers.                                      |

| 1 1    | CK       | I   | Serial clock input.                                      |

| 1 2    | Data     | I   | Serial data input.                                       |

| 1 3    | LT       | I   | Serial strobe input.                                     |

| 1 4    | GND      |     | Ground.                                                  |

| 15     | TEST     | I   | TEST pin. Connected to ground with 0.1uF capacitor.      |

| 1 6    | IFin     | I   | IF prescaler input from the IF VCO.                      |

| 1 7    | GND      |     | Ground.                                                  |

| 1 8    | CPif     | 0   | IF Charge pump output. Constant current output.          |

| 1 9    | VPif     | _   | Power Supply Input for IF Charge pump.                   |

| 2 0    | Vdd      | -   | Power Supply Voltage Input. Bypass capacitors should be  |

|        |          |     | placed as close as possible to this pin and be connected |

|        |          |     | directly to the ground plane.                            |

#### 6. Functional Description

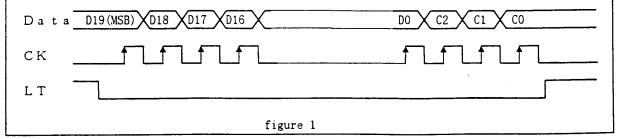

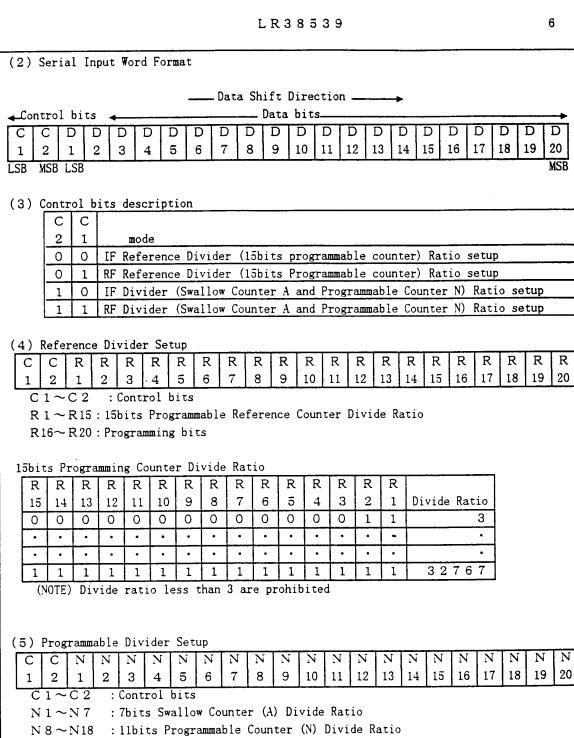

#### (1) Serial Input Programming

The serial input is a 3-wire input (Data, CK, LT) to program all counter ratios, polarity of the phase detector, and other function of this IC. The programming data is structured into 22bit words. Figure 1 shows the timing diagram of the serial input. When the LT= 'L', the CK driver is enabled and Data shifted into register on the CK rising edge. Register data stored into each counter or function register LT rising edge.

(NOTE) Data is shifted in MSB first.

#### SERIAL DATA INPUT TIMING

R

| С | С | N | Z | N | Z | Z | 1.4 | Z |   |   | 1 ' ' | И  |    |    |    | Ν  | N  | N  | '' | 1 1 | l * |

|---|---|---|---|---|---|---|-----|---|---|---|-------|----|----|----|----|----|----|----|----|-----|-----|

| 1 | 2 | 1 | 2 | 3 | 4 | 5 | 6   | 7 | 8 | 9 | 10    | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19  | 20  |

N19~N20 :Programming bits

#### 7bits Swallow Counter Divide Ratio

| (A C          | ount | er) |   | (RI | • ) |   |       |

|---------------|------|-----|---|-----|-----|---|-------|

| N             | N    | N   | N | N   | N   | Z |       |

| 7             | 6    | 5   | 4 | 3   | 2   | 1 | Ratio |

| 0             | 0    | 0   | 0 | 0   | 0   | 0 | 0     |

| 0             | 0    | Ó   | 0 | 0   | 0   | 1 | 1     |

| $\overline{}$ | •    | •   | • | •   | •   | • | •     |

| ·             | ·    | •   | • | •   | •   | • | •     |

| 1             | 1    | 1   | 1 | 1   | 1   | 1 | 127   |

|               |      |     |   |     |     |   |       |

| (A C | ount | er) |   | ( | I | F | ) |  |

|------|------|-----|---|---|---|---|---|--|

| T.   | N:   | 1   | 1 |   | 7 | Т | ╮ |  |

| N | N           | N                                     | N                                | N                                        | N                                                  |                                       |

|---|-------------|---------------------------------------|----------------------------------|------------------------------------------|----------------------------------------------------|---------------------------------------|

| 6 | 5           | 4                                     | 3                                | 2                                        | 1                                                  | Ratio                                 |

| × | ×           | 0                                     | 0                                | 0                                        | 0                                                  | 0                                     |

| × | ×           | 0                                     | 0                                | 0                                        | 1                                                  | 1                                     |

| • | •           | •                                     | •                                | •                                        | •                                                  | •                                     |

| • | •           | •                                     | •                                | •                                        | •                                                  | •                                     |

| × | ×           | 1                                     | 1                                | 1                                        | 1                                                  | 15                                    |

|   | ×<br>×<br>· | X   X   X   X   X   X   X   X   X   X | 6 5 4<br>× × 0<br>× × 0<br>· · · | 6 5 4 3<br>× × 0 0<br>× × 0 0<br>· · · · | 6 5 4 3 2<br>× × 0 0 0<br>× × 0 0 0<br>· · · · · · | 6 5 4 3 2 1  x x 0 0 0 0  x x 0 0 0 1 |

(Note)  $\times$ : (N7, N6, N5) = (0, 0, 0) or (1, 1, 1) Normal Operation.

Other conditions are prohibited.

# 11bits Programmable Counter Divide Ratio

| (N | Counter) |

|----|----------|

| (N | Counter, |

| <u> </u> | Carro | <del>/</del> |    |    |    |    |     |    |   |   |       |

|----------|-------|--------------|----|----|----|----|-----|----|---|---|-------|

| Z        | Z     | Z            | Z  | Ζ  | Ν  | N  | N   | Ν  | Ν | Ν |       |

| 18       | 17    | 16           | 15 | 14 | 13 | 12 | 11_ | 10 | 9 | 8 | Ratio |

| 0        | 0     | 0            | 0  | 0  | 0  | 0  | 0   | 0  | 1 | 1 | 3     |

| 0        | 0     | 0            | 0  | 0  | 0  | 0  | 0   | 1  | 0 | 0 | 4     |

| •        | •     | •            | •  | •  | •  |    | •   | •  | • | ٠ | •     |

| 1        | 1     | 1            | 1  | 1  | 1  | 1  | 1   | 1  | 1 | 1 | 2047  |

(Note) Divide ratio less than 3 are prohibited.

#### (6) Programmable Mode Control Setup

Following mode controlled by R16~R20, N19~N20bits

| С | С | R                 | R              | R              | R       | R       |

|---|---|-------------------|----------------|----------------|---------|---------|

| 1 | 2 | 16                | 17             | 18             | 19      | 20      |

| 0 | 0 | IF Phase Detector | IF Charge Pump | IF Charge Pump | MD3     | MD1     |

|   |   | polarity          | Output Current | Hi-Z           | (IF-Ld) | (IF-Fo) |

| 0 | 1 | RF Phase Detector | RF Charge Pump | RF Charge Pump | MD4     | MD 2    |

|   |   | polarity          | Output Current | Hi-Z           | (RF-Ld) | (RF-Fo) |

| С | С  | N                  | N               |

|---|----|--------------------|-----------------|

| 1 | 2_ | 19                 | 20              |

| 1 | 0  | IF Prescaler Ratio | IF Power ON/OFF |

| 1 | 1  | RF Prescaler Ratio | RF Power ON/OFF |

#### Mode Control Table

|   | Phase Detector | Charge Pump  | Charge Pump      | IF        | RF        | Power ON/OFF |

|---|----------------|--------------|------------------|-----------|-----------|--------------|

| ļ | Polarity       | Current      | Hi-Z             | Prescaler | Prescaler |              |

| 0 | Negative       | 1/4×High     | Normal Operation | 8/9       | 64/65     | Power ON     |

| 1 | Positive       | High Current | Hi-Z             | 16/17     | 128/129   | Power OFF    |

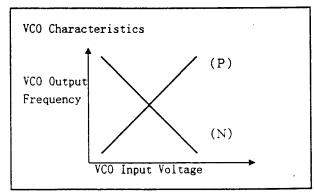

(Note) Phase Detector Polarity

Depending upon VCO characteristics.

When VCO characteristics are positive like(P):R16=1

When VCO characteristics are negative like(N):R16=0

VCO Characteristics Positive: (P)

VCO Characteristics Negative: (N)

| Ld/Fo ( | utput Mo | de Selec | t Contro | ol                                                     |  |  |

|---------|----------|----------|----------|--------------------------------------------------------|--|--|

| MD4     | MD3      | MD2      | MD1      | Ld/Fo Output State                                     |  |  |

| 0       | 0        | 0        | 0        | Disabled (It is actively pulled to a Low logic state.) |  |  |

| 0       | 1        | 0        | 0        | IF Lock Detect Signal output                           |  |  |

| 1       | 0        | 0        | 0        | RF Lock Detect Signal output                           |  |  |

| 1       | 1        | 0        | 0        | RF/IF Lock Detect Signal output                        |  |  |

| ×       | 0        | 0        | 1        | IF Reference Divider output                            |  |  |

| ×       | 0        | 1        | 0        | RF Reference Divider output                            |  |  |

| ×       | 1        | 0        | 1        | IF Programmable Divider output                         |  |  |

| ×       | 1        | 1        | 0        | RF Programmable Divider output                         |  |  |

| 0       | 0        | 1        | 1        | It is actively pulled to a Low logic state.            |  |  |

| 0       | 1        | 1        | 1        | IF counter reset. (IF charge pump output is Hi-Z)      |  |  |

| 1       | 0        | 1        | 1        | RF counter reset. (RF charge pump output is Hi-Z)      |  |  |

× : DON'T CARE condition

Expect the above-mentioned states are prohibited.

#### TEST Mode Control

(IF)

| / I I |   |   |                  |

|-------|---|---|------------------|

| N     | Z | Z |                  |

| 7     | 6 | 5 | operation state  |

| 0     | 0 | 0 | Normal operation |

| 0     | 0 | 1 | Normal operation |

| 0     | 1 | 0 | Normal operation |

| 0     | 1 | 1 | TEST Mode        |

| 1     | 0 | 0 | TEST Mode        |

| 1     | 0 | 1 | TEST Mode .      |

| 1     | 1 | 0 | TEST Mode        |

| 1     | 1 | 1 | Normal operation |

|       |   |   |                  |

TEST Mode are prohibited.

#### (7) Pulse Swallow Function

VCO frequency, Prescaler ratio, and Counter divide ratios(A, N and R), are determined follows.

$$f_{\text{vco}} = [(P \times N) + A] \times f_{\text{osc}} / R$$

$f_{\text{vco}}$  : Output frequency of external VCO(Voltage Controlled Oscillator)

P : Divide ratio of dual modulus prescaler (RF:64/65 or 128/129, IF:8/9 or 16/17)

N : Divide ratio of Binary 11bits programmable counter  $(3 \le N \le 2047)$

A : Divide ratio of Binary 7bits swallow counter ( $0 \le A \le 127$ ,  $A \le N$ )

$f_{\text{OSC}}\,$  : Output frequency of external reference frequency oscillator

R : Divide ratio of Binary 15bits programmable reference counter ( $3 \le R \le 32767$ )

#### 7. Absolute Maximum Ratings

| Parameter             | Symbol          | Rating                  | Units |

|-----------------------|-----------------|-------------------------|-------|

| Supply voltage        | Vdd, VPrf, VPif | $-0.3 \sim +4.0$        | V     |

| Input Voltage         | Vin             | $-0.3 \sim V d d + 0.3$ | V     |

| Operating temperature | Торг            | -40~ +85                | ೡ     |

| Storage temperature   | Tstg            | $-40 \sim +150$         | °C    |

# 8. Electrical Characteristics

# 8-1 Recommended Operating Conditions

| Parameter       | Symbol          | MIN    | TYP  | MAX        | Units |

|-----------------|-----------------|--------|------|------------|-------|

| Supply voltage  | Vdd, VPrf, VPif | 2.70   | 3.00 | 3.30       | V     |

| Input H Voltage | VIH             | 0.7Vdd |      | Vdd+0.3    | V     |

| Input L Voltage | VIL             | -0.3   |      | 0. 3 V d d | V     |

# 8 - 2 Electrical Characteristics

$(Vdd=3. OV, VPrf=3. OV, VPif=3. OV, Ta=25^{\circ}C)$

| f                       | T          | Condition        |         | TYP     |       | Units |

|-------------------------|------------|------------------|---------|---------|-------|-------|

| Parameter               | Symbol     | Condition        | MIN     |         | MAX   |       |

| Power Supply Voltage    |            | Vdd              | 2.70    | 3.00    | 3. 30 | V     |

| Power Supply Current    | Idd        | RF+IF Operated   |         | 2.80    |       | mА    |

| (Notel)                 | Idd(RF)    | RF Only Operated |         |         |       |       |

|                         | Idd(IF)    | IF Only Operated |         |         |       |       |

|                         | I d d-Pdwn | Power Down       |         | 1.00    |       | μА    |

| Operating Frequency     | RFin       | -10dBm           |         |         | 1200  | МНz   |

|                         | IFin       | -10dBm           |         |         | 500   | МН z  |

|                         | OSCi       |                  |         |         | 23    | МН z  |

| Input Sensitivity       | RFin       |                  | -10     |         |       | dBm   |

|                         | IFin       | ·                | -10     |         |       | dBm   |

| "H" Level Input Voltage | VIL        |                  | 0.7Vdd  |         |       | V     |

| "L" Level Input Voltage | VIH        |                  | 0. 5Vdd |         |       | V     |

| Charge pump             | I-source   |                  |         | -4.0    |       | mА    |

| Output Current (RF)     | I-sink     |                  |         | 4. 0    |       | m.A   |

| Charge pump             | I-source   |                  |         | -4.0    |       | m A   |

| Output Current (IF)     | I-sink     |                  |         | 4.0     |       | m.A   |

| Charge pump             | VPrf, Vpif |                  | 2.70    | . 3. 00 | 3.30  | V     |

| Supply Voltage          | <u> </u>   |                  |         |         |       |       |

Notel:[Conditions]Rfin=690MHZ, Ifin=257.6MHz, OSCi=14.4MHz)

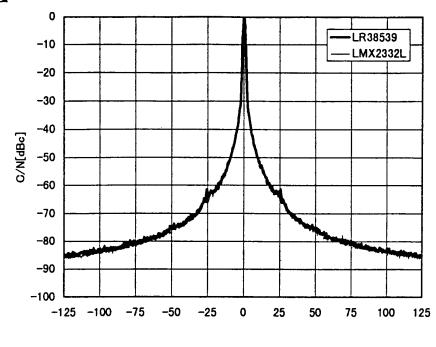

# Compatibility of LR38539(Sharp) and LMX2332L(National Semiconductor)

LR38539(Sharp) and LMX2332L(NS) are basically compatible and can exchange each other. However, please confirm the following difference.

# 1.Pin compatibility

Each of these two ICs can be used on the same board in the conventional case.

| Part Number | # Pin | Function | Condition                                                     |

|-------------|-------|----------|---------------------------------------------------------------|

| LR38539     | 6     | Vdd/2out | Connected to GND via bypass capacitor (more than 0.1 $\mu$ F) |

|             | 15    | Test     | Either connected to GND via bypass capacitor or free          |

| LMX2332L    | 6     | finRF    | Connected to GND via                                          |

| LIVIAZ33ZL  | 15    | finIF    | bypass capacitor                                              |

#### 2.Functional differences

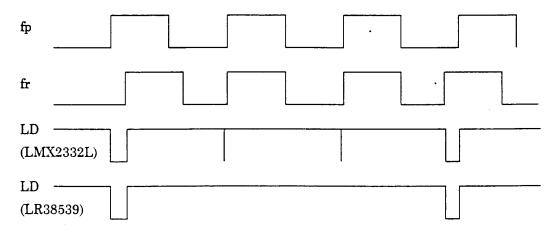

# 1)LD(Lock detect) Signal

In LR38539 "H" level output voltage are detected in the "Lock" condition. In this point LR38539 is similar to LMX2332L but the latter has "L" spike as shown in the following figure.

2)

|                                              | LR38539(Sharp)                          | LMX2332L(NS)                                          |  |

|----------------------------------------------|-----------------------------------------|-------------------------------------------------------|--|

| Fast lockup mode                             | N                                       | Y                                                     |  |

| IF swallow counters<br>(N7,N6,N5)            | Should be set either (0,0,0) or (1,1,1) | Don't care                                            |  |

| Powerdown operation                          | Asynchronous powerdown mode             | Selectable synchronous or asynchronous powerdown mode |  |

| Power for internal counter in powerdown mode | OFF                                     | ON                                                    |  |

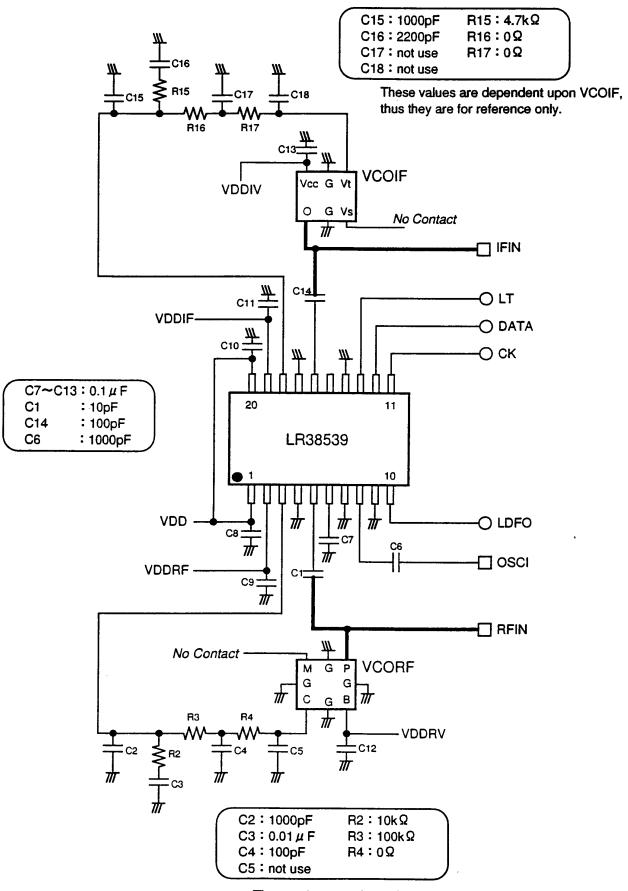

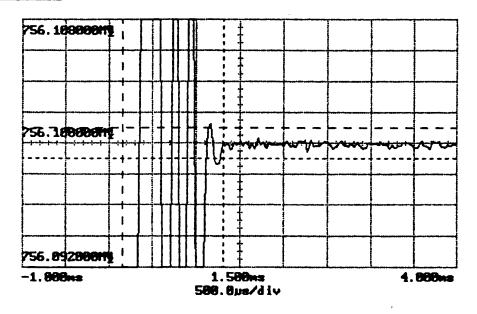

# LR38539 Eva. Board

These values are dependent upon VCORF, thus they are for reference only.

# Phase Noise

Offset Frequency [kHz]

CENTER:756.1MHz SPAN:250kHz RBW:1kHz VBW:10Hz

REFERENCE FREQUENCY: 25kHz

<u>Lock Up Time</u> 741.1MHz→756.1MHz 1.151msec

Phase Lock Loop, PLL, RF, IF, Cellular Phone, LR38539