## Low Power, Single Resistor Gain Programmable, Precision Instrumentation Amplifier

### **FEATURES**

Supply Current: 530µA Max

Meets IEC 1000-4-2 Level 4 (±15kV) ESD Tests with Two External 5k Resistors

Single Gain Set Resistor: G = 1 to 10,000

Gain Error: G = 10, 0.4% Max

Input Offset Voltage Drift: 0.3uV/°C Max

Gain Nonlinearity: G = 10, 20ppm Max

Input Offset Voltage: 40µV Max

Input Bias Current: 250pA Max

PSRR at  $A_V = 1$ : 103dB Min CMRR at  $A_V = 1$ : 90dB Min

Wide Supply Range:  $\pm 2.3V$  to  $\pm 18V$

1kHz Voltage Noise: 10nV/√Hz 0.1Hz to 10Hz Noise: 0.28µV<sub>P-P</sub>

Available in 8-Pin PDIP and SO Packages

### **APPLICATIONS**

**Bridge Amplifiers**

Strain Gauge Amplifiers

Thermocouple Amplifiers

Differential to Single-Ended Converters

Differential Voltage to Current Converters

**Data Acquisition**

Battery-Powered and Portable Equipment

Medical Instrumentation

Scales

## DESCRIPTION

The LT®1168 is a micropower, precision instrumentation amplifier that requires only one external resistor to set gains of 1 to 10,000. The low voltage noise of  $10\text{nV}/\sqrt{\text{Hz}}$  (at 1kHz) is not compromised by low power dissipation (350µA typical for  $\pm 15$ V supplies). The wide supply range of  $\pm 2.3$ V to  $\pm 18$ V allows the LT1168 to fit into a wide variety of industrial as well as battery-powered applications.

The high accuracy of the LT1168 is due to a 20ppm maximum nonlinearity and 0.4% max gain error (G = 10). Previous monolithic instrumentation amps cannot handle a 2k load resistor whereas the nonlinearity of the LT1168 is specified for loads as low as 2k. The LT1168 is laser trimmed for very low input offset voltage (40µV max), drift (0.3µV/°C), high CMRR (90dB, G = 1) and PSRR (103dB, G = 1). Low input bias currents of 250pA max are achieved with the use of superbeta processing. The output can handle capacitive loads up to 1000pF in any gain configuration while the inputs are ESD protected up to 13kV (human body). The LT1168 with two external 5k resistors passes the IEC 1000-4-2 level 4 specification.

The LT1168 is a pin-for-pin improved second source for the AD620 and INA118. The LT1168, offered in 8-pin PDIP and SO packages, requires significantly less PC board area than discrete op amp resistor designs. These advantages make the LT1168 the most cost effective solution for precision instrumentation amplifier applications.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

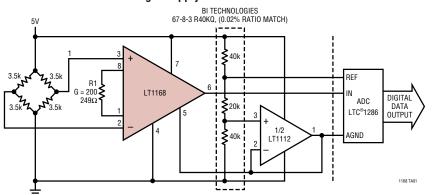

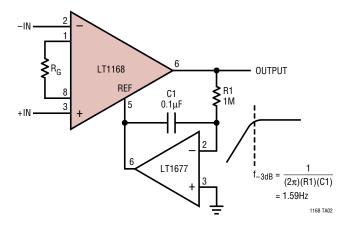

## TYPICAL APPLICATION

#### Single Supply\* Pressure Monitor

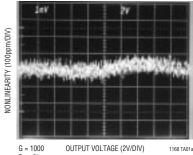

#### **Gain Nonlinearity**

\*See Theory of Operation section

### **ABSOLUTE MAXIMUM RATINGS**

###

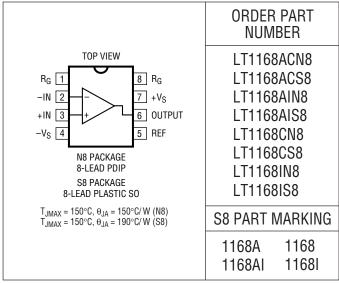

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## **ELECTRICAL CHARACTERISTICS** $T_A = 25 \,^{\circ}\text{C}$ . $V_S = \pm 15 V$ , $V_{CM} = 0 V$ , $R_L = 10 k$ unless otherwise noted.

| SYMBOL           | PARAMETER                           | CONDITIONS (Note 6)                               | LT1 | 168AC/LT     | 1168AI<br>MAX | LT1<br>MIN | 168C/LT1<br>TYP | 168I<br>MAX | UNITS             |

|------------------|-------------------------------------|---------------------------------------------------|-----|--------------|---------------|------------|-----------------|-------------|-------------------|

| G                | Gain Range                          | G = 1 + (49.4k/R <sub>G</sub> )                   | 1   |              | 10k           | 1          |                 | 10k         | 00                |

|                  | Gain Error                          | G = 1                                             |     | 0.008        | 0.02          |            | 0.015           | 0.03        | %                 |

|                  |                                     | G = 10 (Note 7)                                   |     | 0.04<br>0.04 | 0.4<br>0.5    |            | 0.05<br>0.05    | 0.5<br>0.6  | %<br>%            |

|                  |                                     | G = 100 (Note 7)<br>G = 1000 (Note 7)             |     | 0.04         | 0.5           |            | 0.03            | 0.6         | %<br>%            |

|                  | Gain Nonlinearity (Notes 7, 8)      | $V_0 = \pm 10V, G = 1$                            |     | 2            | 6             |            | 3               | 10          | ppm               |

|                  |                                     | $V_0 = \pm 10 \text{V}, G = 10 \text{ and } 100$  |     | 10           | 20            |            | 15              | 25          | ppm               |

|                  |                                     | $V_0 = \pm 10V, G = 1000$                         |     | 20           | 40            |            | 25              | 60          | ppm               |

|                  |                                     | $V_0 = \pm 10V$ , $G = 1$ , $R_L = 2k$            |     | 4            | 15            |            | 5               | 20          | ppm               |

|                  |                                     | $V_0 = \pm 10V$ , $G = 10$ and $100$ , $R_L = 2k$ |     | 20           | 40            |            | 30              | 60          | ppm               |

|                  |                                     | $V_0 = \pm 10V$ , G = 1000, R <sub>L</sub> = 2k   |     | 40           | 75            |            | 50              | 90          | ppm               |

| V <sub>OST</sub> | Total Input Referred Offset Voltage | $V_{OST} = V_{OSI} + V_{OSO}/G$                   |     |              |               |            |                 |             |                   |

| V <sub>OSI</sub> | Input Offset Voltage                | G = 1000, $V_S = \pm 5V$ to $\pm 15V$             |     | 15           | 40            |            | 20              | 60          | μV                |

| $V_{0S0}$        | Output Offset Voltage               | $G = 1$ , $V_S = \pm 5V$ to $\pm 15V$             |     | 40           | 200           |            | 50              | 300         | μV                |

| los              | Input Offset Current                |                                                   |     | 50           | 300           |            | 60              | 450         | pA                |

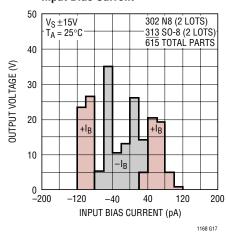

| I <sub>B</sub>   | Input Bias Current                  |                                                   |     | 40           | 250           |            | 80              | 500         | pA                |

| en               | Input Noise Voltage, RTI            | 0.1Hz to 10Hz, G = 1                              |     | 2.00         |               |            | 2.00            |             | μV <sub>P-P</sub> |

|                  |                                     | 0.1Hz to 10Hz, G = 1000                           |     | 0.28         |               |            | 0.28            |             | μV <sub>P-P</sub> |

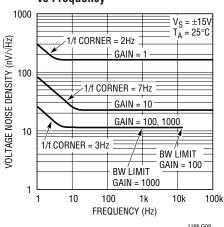

|                  | Input Noise Voltage Density, RTI    | f <sub>0</sub> = 1kHz                             |     | 10           | 15            |            | 10              | 15          | nV/√Hz            |

|                  | Output Noise Voltage Density, RTI   | f <sub>0</sub> = 1kHz (Note 9)                    |     | 165          | 220           |            | 165             | 220         | nV/√Hz            |

| i <sub>n</sub>   | Input Noise Current                 | f <sub>0</sub> = 0.1Hz to 10Hz                    |     | 5            |               |            | 5               |             | pA <sub>P-P</sub> |

|                  | Input Noise Current Density         | f <sub>0</sub> = 10Hz                             |     | 74           |               |            | 74              |             | fA/√Hz            |

| R <sub>IN</sub>  | Input Resistance                    | $V_{IN} = \pm 10V$                                | 300 | 1250         |               | 200        | 1250            |             | GΩ                |

## **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ . $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = 10k$ unless otherwise noted.

| SYMBOL                | PARAMETER                        | CONDITIONS (Note 6)                                                                            | LT116<br>MIN                                   | 8AC/LT                   | T1168AI<br>Max                                 | LT11<br>MIN                                    | 68C/LT                   | Γ1168I<br>ΜΑΧ                                  | UNITS                    |

|-----------------------|----------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------|------------------------------------------------|------------------------------------------------|--------------------------|------------------------------------------------|--------------------------|

| C <sub>IN(DIFF)</sub> | Differential Input Capacitance   | f <sub>0</sub> = 100kHz                                                                        |                                                | 1.6                      |                                                |                                                | 1.6                      |                                                | pF                       |

| C <sub>IN(CM)</sub>   | Common Mode Input<br>Capacitance | f <sub>0</sub> = 100kHz                                                                        |                                                | 1.6                      |                                                |                                                | 1.6                      |                                                | pF                       |

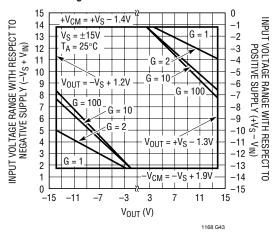

| V <sub>CM</sub>       | Input Voltage Range              | G = 1, Other Input Grounded $V_S = \pm 2.3V$ to $\pm 5V$ $V_S = \pm 5V$ to $\pm 18V$           | -V <sub>S</sub> + 1.9<br>-V <sub>S</sub> + 1.9 |                          | +V <sub>S</sub> - 1.2<br>+V <sub>S</sub> - 1.4 | -V <sub>S</sub> + 1.9<br>-V <sub>S</sub> + 1.9 |                          | +V <sub>S</sub> - 1.2<br>+V <sub>S</sub> - 1.4 | V                        |

| CMRR                  | Common Mode<br>Rejection Ratio   | 1k Source Imbalance,<br>V <sub>CM</sub> = 0V to ±10V<br>G = 1<br>G = 10<br>G = 100<br>G = 1000 | 90<br>106<br>120<br>126                        | 95<br>115<br>135<br>140  |                                                | 85<br>100<br>110<br>120                        | 95<br>115<br>135<br>140  |                                                | dB<br>dB<br>dB<br>dB     |

| PSRR                  | Power Supply<br>Rejection Ratio  | V <sub>S</sub> = ±2.3V to ±18V<br>G = 1<br>G = 10<br>G = 100<br>G = 1000                       | 103<br>122<br>131<br>135                       | 108<br>128<br>145<br>150 |                                                | 100<br>118<br>126<br>130                       | 108<br>128<br>145<br>150 |                                                | dB<br>dB<br>dB<br>dB     |

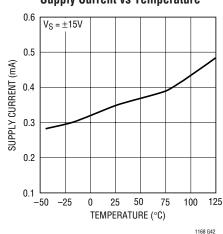

| Is                    | Supply Current                   | $V_S = \pm 2.3 V \text{ to } \pm 18 V$                                                         |                                                | 350                      | 530                                            |                                                | 350                      | 530                                            | μА                       |

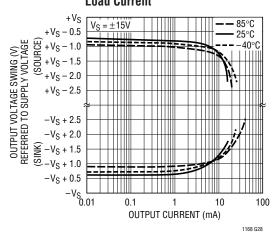

| V <sub>OUT</sub>      | Output Voltage Swing             | $R_L = 10k$ $V_S = \pm 2.3V \text{ to } \pm 5V$ $V_S = \pm 5V \text{ to } \pm 18V$             | -V <sub>S</sub> + 1.1<br>-V <sub>S</sub> + 1.2 |                          | +V <sub>S</sub> - 1.2<br>+V <sub>S</sub> - 1.3 | -V <sub>S</sub> + 1.1<br>-V <sub>S</sub> + 1.2 |                          | +V <sub>S</sub> - 1.2<br>+V <sub>S</sub> - 1.3 | V                        |

| I <sub>OUT</sub>      | Output Current                   |                                                                                                | 20                                             | 32                       |                                                | 20                                             | 32                       |                                                | mA                       |

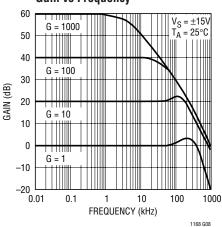

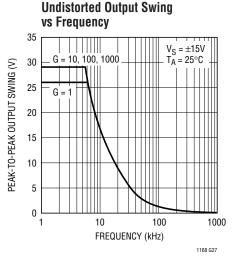

| BW                    | Bandwidth                        | G = 1<br>G = 10<br>G = 100<br>G = 1000                                                         |                                                | 400<br>200<br>13<br>1    |                                                |                                                | 400<br>200<br>13<br>1    |                                                | kHz<br>kHz<br>kHz<br>kHz |

| SR                    | Slew Rate                        | $G = 1, V_{OUT} = \pm 10V$                                                                     | 0.3                                            | 0.5                      |                                                | 0.3                                            | 0.5                      |                                                | V/µs                     |

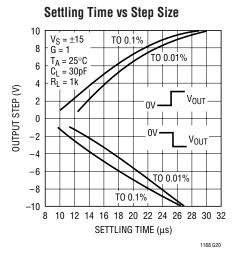

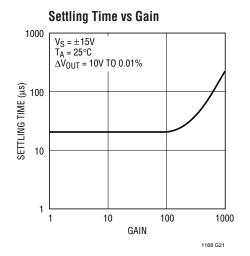

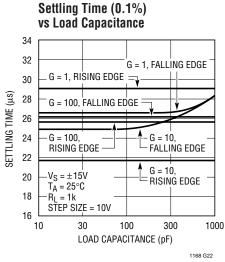

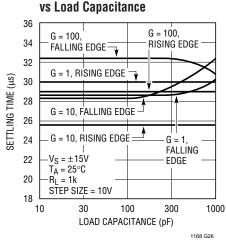

|                       | Settling Time to 0.01%           | 10V Step<br>G = 1 to 100<br>G = 1000                                                           |                                                | 30<br>200                |                                                |                                                | 30<br>200                |                                                | μs<br>μs                 |

| REFIN                 | Reference Input Resistance       |                                                                                                |                                                | 60                       |                                                |                                                | 60                       |                                                | kΩ                       |

| I <sub>REFIN</sub>    | Reference Input Current          | V <sub>REF</sub> = 0V                                                                          |                                                | 18                       |                                                |                                                | 18                       |                                                | μА                       |

| V <sub>REF</sub>      | Reference Voltage Range          |                                                                                                | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | V                        |

| A <sub>VREF</sub>     | Reference Gain to Output         |                                                                                                | 1                                              | ± 0.00                   | 01                                             | 1                                              | ± 0.00                   | 01                                             |                          |

The ullet denotes the specifications which apply over the 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C temperature range. V<sub>S</sub> =  $\pm$ 15V, V<sub>CM</sub> = 0V, R<sub>L</sub> = 10k unless otherwise noted.

|                     |                     |                                      |   |     | LT1168AC |      |     | LT1168C |      |        |

|---------------------|---------------------|--------------------------------------|---|-----|----------|------|-----|---------|------|--------|

| SYMBOL              | PARAMETER           | CONDITIONS (Note 6)                  |   | MIN | TYP      | MAX  | MIN | TYP     | MAX  | UNITS  |

|                     | Gain Error          | G = 1                                | • |     | 0.01     | 0.03 |     | 0.012   | 0.04 | %      |

|                     |                     | G = 10 (Note 7)                      | • |     | 0.40     | 1.5  |     | 0.500   | 1.6  | %      |

|                     |                     | G = 100 (Note 7)                     | • |     | 0.45     | 1.6  |     | 0.550   | 1.7  | %      |

|                     |                     | G = 1000 (Note 7)                    | • |     | 0.50     | 1.7  |     | 0.600   | 1.8  | %      |

|                     | Gain Nonlinearity   | $V_{OUT} = \pm 10V, G = 1$           | • |     | 2        | 15   |     | 3       | 20   | ppm    |

|                     | (Notes 7, 8)        | $V_{OUT} = \pm 10V$ , G = 10 and 100 | • |     | 7        | 30   |     | 10      | 35   | ppm    |

|                     |                     | $V_{OUT} = \pm 10V, G = 1000$        | • |     | 25       | 60   |     | 30      | 80   | ppm    |

| $\Delta G/\Delta T$ | Gain vs Temperature | G < 1000 (Note 7)                    | • | ·   | 100      | 200  |     | 100     | 200  | ppm/°C |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the $0^{\circ}C \leq T_A \leq 70^{\circ}C$ temperature range. $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = 10k$ unless otherwise noted.

| SYMBOL              | PARAMETER                          | CONDITIONS (Note 6)                                                                                      |   | MIN                                            | T1168A<br>TYP            | C<br>MAX                                       | MIN                                            | LT1168                   | C<br>MAX                                       | UNITS                |

|---------------------|------------------------------------|----------------------------------------------------------------------------------------------------------|---|------------------------------------------------|--------------------------|------------------------------------------------|------------------------------------------------|--------------------------|------------------------------------------------|----------------------|

| V <sub>OST</sub>    | Total Input Referred Offset Voltag | $V_{OST} = V_{OSI} + V_{OSO}/G$                                                                          |   | 1                                              |                          |                                                | ı                                              |                          |                                                |                      |

| V <sub>OSI</sub>    | Input Offset Voltage               | $V_S = \pm 5V \text{ to } \pm 15V$                                                                       | • |                                                | 18                       | 60                                             |                                                | 23                       | 80                                             | μV                   |

| V <sub>OSIH</sub>   | Input Offset Voltage Hysteresis    | (Notes 7, 10)                                                                                            | • |                                                | 3.0                      |                                                |                                                | 3.0                      |                                                | μV                   |

| V <sub>0S0</sub>    | Output Offset Voltage              | $V_S = \pm 5V \text{ to } \pm 15V$                                                                       | • |                                                | 60                       | 380                                            |                                                | 70                       | 500                                            | μV                   |

| V <sub>OSOH</sub>   | Output Offset Voltage Hysteresis   | (Notes 7, 10)                                                                                            | • |                                                | 30                       |                                                |                                                | 30                       |                                                | μV                   |

| V <sub>OSI</sub> /T | Input Offset Drift (RTI)           | (Note 9)                                                                                                 | • |                                                | 0.05                     | 0.3                                            |                                                | 0.06                     | 0.4                                            | μV/°C                |

| V <sub>OSO</sub> /T | Output Offset Drift                | (Note 9)                                                                                                 | • |                                                | 0.7                      | 3                                              |                                                | 0.8                      | 4                                              | μV/°C                |

| I <sub>OS</sub>     | Input Offset Current               |                                                                                                          | • |                                                | 100                      | 400                                            |                                                | 120                      | 550                                            | pA                   |

| I <sub>OS</sub> /T  | Input Offset Current Drift         |                                                                                                          | • |                                                | 0.3                      |                                                |                                                | 0.4                      |                                                | pA/°C                |

| I <sub>B</sub>      | Input Bias Current                 |                                                                                                          | • |                                                | 65                       | 350                                            |                                                | 105                      | 600                                            | pA                   |

| I <sub>B</sub> /T   | Input Bias Current Drift           |                                                                                                          | • |                                                | 1.4                      |                                                |                                                | 1.4                      |                                                | pA/°C                |

| V <sub>CM</sub>     | Input Voltage Range                | G = 1, Other Input Grounded<br>$V_S = \pm 2.3V \text{ to } \pm 5V$<br>$V_S = \pm 5V \text{ to } \pm 18V$ | • | -V <sub>S</sub> + 2.1<br>-V <sub>S</sub> + 2.1 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.4 | -V <sub>S</sub> + 2.1<br>-V <sub>S</sub> + 2.1 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.4 | V                    |

| CMRR                | Common Mode<br>Rejection Ratio     | 1k Source Imbalance,<br>$V_{CM} = 0V$ to $\pm 10V$<br>G = 1<br>G = 10<br>G = 100<br>G = 1000             | • | 88<br>100<br>115<br>117                        | 92<br>110<br>120<br>135  |                                                | 83<br>97<br>113<br>114                         | 92<br>110<br>120<br>135  |                                                | dB<br>dB<br>dB<br>dB |

| PSRR                | Power Supply<br>Rejection Ratio    | $V_S = \pm 2.3 V \text{ to } \pm 18 V$ $G = 1$ $G = 10$ $G = 100$ $G = 1000$                             | • | 102<br>123<br>127<br>129                       | 115<br>130<br>135<br>145 |                                                | 98<br>118<br>124<br>126                        | 115<br>130<br>135<br>145 |                                                | dB<br>dB<br>dB<br>dB |

| Is                  | Supply Current                     | $V_S = \pm 2.3 \text{V to } \pm 18 \text{V}$                                                             | • |                                                | 390                      | 615                                            |                                                | 390                      | 615                                            | μΑ                   |

| V <sub>OUT</sub>    | Output Voltage Swing               | $R_L = 10k$<br>$V_S = \pm 2.3V \text{ to } \pm 5V$<br>$V_S = \pm 5V \text{ to } \pm 18V$                 | • | -V <sub>S</sub> + 1.4<br>-V <sub>S</sub> + 1.6 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.5 | -V <sub>S</sub> + 1.4<br>-V <sub>S</sub> + 1.6 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.5 | V                    |

| I <sub>OUT</sub>    | Output Current                     |                                                                                                          | • | 16                                             | 25                       |                                                | 16                                             | 25                       |                                                | mA                   |

| SR                  | Slew Rate                          | $G = 1, V_{OUT} = \pm 10V$                                                                               | • | 0.25                                           | 0.48                     |                                                | 0.25                                           | 0.48                     |                                                | V/µs                 |

| V <sub>REF</sub>    | Voltage Range                      | (Note 9)                                                                                                 | • | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | V                    |

The ullet denotes the specifications which apply over the  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$  temperature range.  $V_S = \pm 15V$ ,  $V_{CM} = 0V$ ,  $R_L = 10k$  unless otherwise noted. (Note 8)

|                     |                     |                                  |   |     | LT1168AI |      |     | LT1168I |      |        |

|---------------------|---------------------|----------------------------------|---|-----|----------|------|-----|---------|------|--------|

| SYMBOL              | PARAMETER           | CONDITIONS (Note 6)              |   | MIN | TYP      | MAX  | MIN | TYP     | MAX  | UNITS  |

|                     | Gain Error          | G = 1                            | • |     | 0.014    | 0.04 |     | 0.015   | 0.05 | %      |

|                     |                     | G = 10 (Note 7)                  | • |     | 0.600    | 1.9  |     | 0.700   | 2.0  | %      |

|                     |                     | G = 100 (Note 7)                 | • |     | 0.600    | 2.0  |     | 0.700   | 2.1  | %      |

|                     |                     | G = 1000 (Note 7)                | • |     | 0.600    | 2.1  |     | 0.700   | 2.2  | %      |

| G <sub>N</sub>      | Gain Nonlinearity   | $V_0 = \pm 10V, G = 1$           | • |     | 3        | 20   |     | 5       | 25   | ppm    |

|                     | (Notes 7, 8)        | $V_0 = \pm 10$ V, G = 10 and 100 | • |     | 10       | 35   |     | 15      | 40   | ppm    |

|                     |                     | $VO = \pm 10V, G = 1000$         | • |     | 30       | 70   |     | 35      | 100  | ppm    |

| $\Delta G/\Delta T$ | Gain vs Temperature | G < 1000 (Note 7)                | • |     | 100      | 200  |     | 100     | 200  | ppm/°C |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ temperature range. $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = 10k$ unless otherwise noted. (Note 5)

| SYMBOL              | PARAMETER                          | CONDITIONS (Note 6)                                                                   |   | MIN L                                          | T1168/                   | AI<br>MAX                                      | MIN                                            | LT1168<br>TYP            | I<br>MAX                                       | UNITS                |

|---------------------|------------------------------------|---------------------------------------------------------------------------------------|---|------------------------------------------------|--------------------------|------------------------------------------------|------------------------------------------------|--------------------------|------------------------------------------------|----------------------|

| V <sub>OST</sub>    | Total Input Referred Offset Voltag | $V_{OST} = V_{OSI} + V_{OSO}/G$                                                       |   |                                                |                          |                                                |                                                |                          |                                                |                      |

| V <sub>OSI</sub>    | Input Offset Voltage               |                                                                                       | • |                                                | 20                       | 75                                             |                                                | 25                       | 100                                            | μV                   |

| V <sub>OSIH</sub>   | Input Offset Voltage Hysteresis    | (Notes 7, 10)                                                                         | • |                                                | 3.0                      |                                                |                                                | 3.0                      |                                                | μV                   |

| V <sub>OSO</sub>    | Output Offset Voltage              |                                                                                       | • |                                                | 180                      | 500                                            |                                                | 200                      | 600                                            | μV                   |

| V <sub>OSOH</sub>   | Output Offset Voltage Hysteresis   | (Notes 7, 10)                                                                         | • |                                                | 30                       |                                                |                                                | 30                       |                                                | μV                   |

| V <sub>OSI</sub> /T | Input Offset Drift (RTI)           | (Note 9)                                                                              | • |                                                | 0.05                     | 0.3                                            |                                                | 0.06                     | 0.4                                            | μV/°C                |

| V <sub>OSO</sub> /T | Output Offset Drift                | (Note 9)                                                                              | • |                                                | 0.8                      | 5                                              |                                                | 1                        | 6                                              | μV/°C                |

| I <sub>OS</sub>     | Input Offset Current               |                                                                                       | • |                                                | 110                      | 550                                            |                                                | 120                      | 700                                            | pA                   |

| I <sub>OS</sub> /T  | Input Offset Current Drift         |                                                                                       | • |                                                | 0.3                      |                                                |                                                | 0.3                      |                                                | pA/°C                |

| I <sub>B</sub>      | Input Bias Current                 |                                                                                       | • |                                                | 120                      | 500                                            |                                                | 220                      | 800                                            | pA                   |

| I <sub>B</sub> /T   | Input Bias Current Drift           |                                                                                       | • |                                                | 1.4                      |                                                |                                                | 1.4                      |                                                | pA/°C                |

| V <sub>CM</sub>     | Input Voltage Range                | $V_S = \pm 2.3V \text{ to } \pm 5V$<br>$V_S = \pm 5V \text{ to } \pm 18V$             | • | -V <sub>S</sub> + 2.1<br>-V <sub>S</sub> + 2.1 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.4 | $-V_S + 2.1$<br>$-V_S + 2.1$                   |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.4 | V                    |

| CMRR                | Common Mode<br>Rejection Ratio     | 1k Source Imbalance, $V_{CM} = 0V$ to $\pm 10V$ $G = 1$ $G = 10$ $G = 100$ $G = 1000$ | • | 86<br>98<br>114<br>116                         | 90<br>105<br>118<br>133  |                                                | 81<br>95<br>112<br>112                         | 90<br>105<br>118<br>133  |                                                | dB<br>dB<br>dB<br>dB |

| PSRR                | Power Supply<br>Rejection Ratio    | $V_S = \pm 2.3V \text{ to } \pm 18V$ $G = 1$ $G = 10$ $G = 100$ $G = 1000$            | • | 100<br>120<br>125<br>128                       | 112<br>125<br>132<br>140 |                                                | 95<br>115<br>120<br>125                        | 112<br>125<br>132<br>140 |                                                | dB<br>dB<br>dB<br>dB |

| Is                  | Supply Current                     |                                                                                       | • |                                                | 420                      | 650                                            |                                                | 420                      | 650                                            | μА                   |

| V <sub>OUT</sub>    | Output Voltage Swing               | $V_S = \pm 2.3V \text{ to } \pm 5V$<br>$V_S = \pm 5V \text{ to } \pm 18V$             | • | -V <sub>S</sub> + 1.4<br>-V <sub>S</sub> + 1.6 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.5 | -V <sub>S</sub> + 1.4<br>-V <sub>S</sub> + 1.6 |                          | +V <sub>S</sub> - 1.3<br>+V <sub>S</sub> - 1.5 | V<br>V               |

| I <sub>OUT</sub>    | Output Current                     |                                                                                       | • | 15                                             | 22                       |                                                | 15                                             | 22                       |                                                | mA                   |

| SR                  | Slew Rate                          |                                                                                       | • | 0.22                                           | 0.41                     |                                                | 0.22                                           | 0.42                     |                                                | V/µs                 |

| V <sub>REF</sub>    | Voltage Range                      | (Note 9)                                                                              | • | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | -V <sub>S</sub> + 1.6                          |                          | +V <sub>S</sub> - 1.6                          | V                    |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be imparied.

**Note 2:** If the input voltage exceeds the supplies, the input current should be limited to less than 20mA.

**Note 3:** A heat sink may be required to keep the junction temperature below absolute maximum.

**Note 4:** The LT1168AC/LT1168C are guaranteed functional over the operating temperature range of  $-40^{\circ}$ C and  $85^{\circ}$ C.

**Note 5:** The LT1168AC/LT1168C are guaranteed to meet specified performance from 0°C to 70°C. The LT1168AC/LT1168C are designed, characterized and expected to meet specified performance from -40°C to 85°C but are not tested or QA sampled at these temperatures. The LT1168AI/LT1168I are guaranteed to meet specified performance from -40°C to 85°C.

**Note 6:** Typical parameters are defined as the 60% of the yield parameter distribution.

**Note 7:** Does not include the tolerance of the external gain resistor R<sub>G</sub>.

**Note 8:** This parameter is measured in a high speed automatic tester that does not measure the thermal effects with longer time constants. The magnitude of these thermal effects are dependent on the package used, heat sinking and air flow conditions.

Note 9: This parameter is not 100% tested.

**Note 10:** Hysteresis in offset voltage is created by package stress that differs depending on whether the IC was previously at a higher or lower temperature. Offset voltage hysteresis is always measured at 25°C, but the IC is cycled to 85°C I-grade (or 70°C C-grade) or -40°C I-grade (0°C C-grade) before successive measurement. 60% of the parts will pass the typical limit on the data sheet.

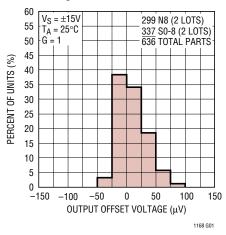

#### Distribution of Output Offset Voltage

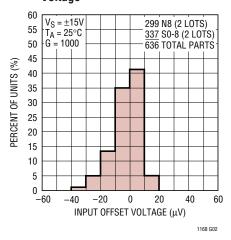

## Distribution of Input Offset Voltage

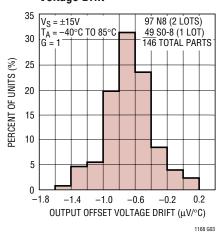

#### Distribution of Output Offset Voltage Drift

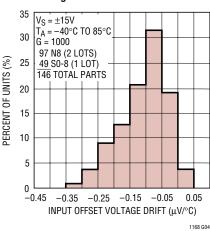

## Distribution of Input Offset Voltage Drift

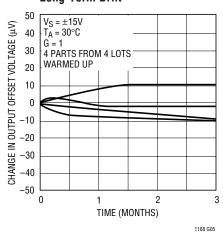

#### Output Offset Voltage Long-Term Drift

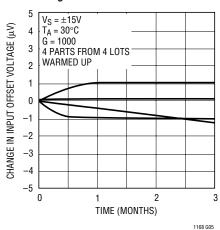

Input Offset Voltage Long-Term Drift

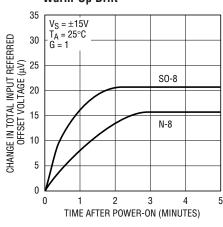

#### Warm-Up Drift

#### Gain vs Frequency

## Voltage Noise Density vs Frequency

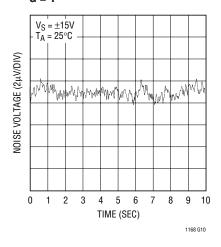

#### 0.1Hz to 10Hz Noise Voltage, G = 1

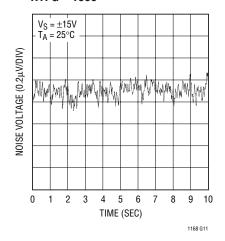

#### 0.1Hz to 10Hz Noise Voltage, RTI G = 1000

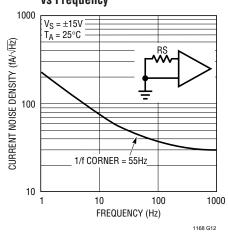

#### Current Noise Density vs Frequency

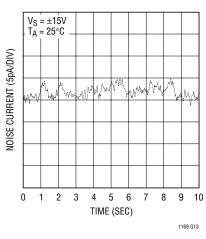

#### 0.1Hz to 10Hz Current Noise

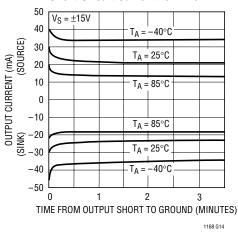

#### **Short-Circuit Current vs Time**

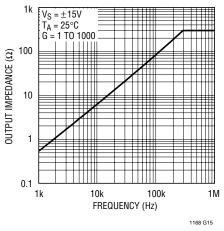

**Output Impedance vs Frequency**

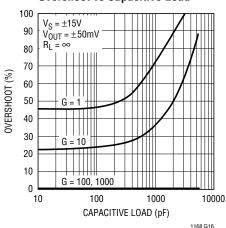

#### **Overshoot vs Capacitive Load**

Input Bias Current

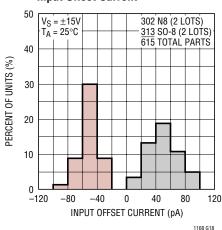

#### **Input Offset Current**

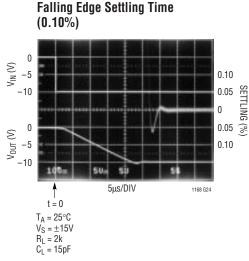

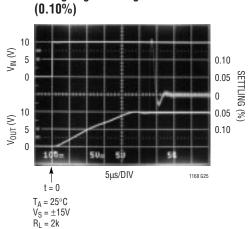

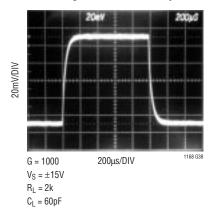

Rising Edge Settling Time

Settling Time (0.01%)

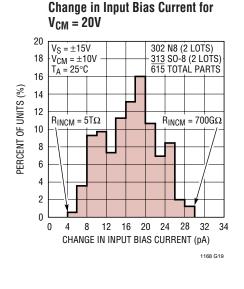

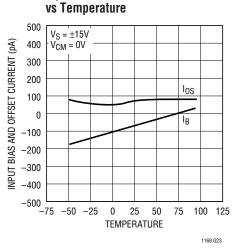

**Input Bias and Offset Current**

$C_L = 15pF$

#### Output Voltage Swing vs Load Current

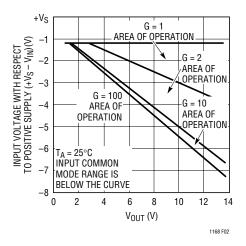

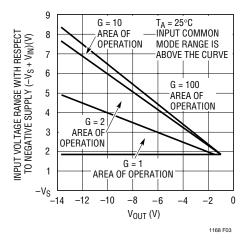

#### Input Voltage Range vs Output Voltage for Various Gains

## Output Short-Circuit Current vs Temperature

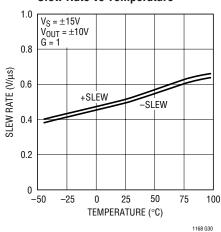

#### **Slew Rate vs Temperature**

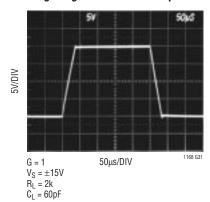

#### **Large-Signal Transient Response**

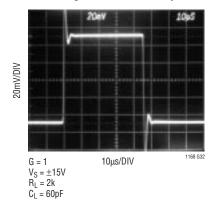

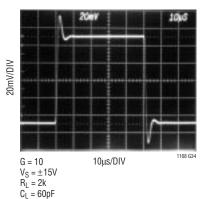

#### **Small-Signal Transient Response**

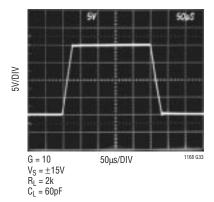

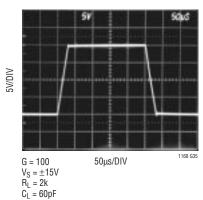

**Large-Signal Transient Response**

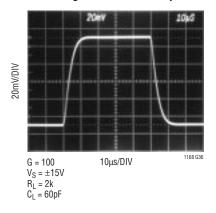

#### **Small-Signal Transient Response**

#### **Large-Signal Transient Response**

#### **Small-Signal Transient Response**

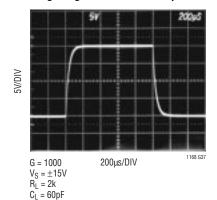

#### **Large-Signal Transient Response**

#### **Small-Signal Transient Response**

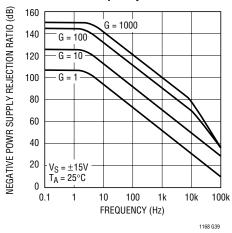

#### Negative Power Supply Rejection Ratio vs Frequency

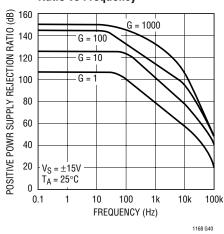

## Positive Power Supply Rejection Ratio vs Frequency

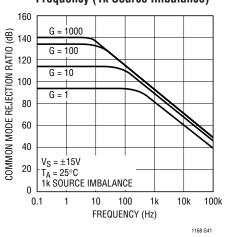

#### Common Mode Rejection Ratio vs Frequency (1k Source Imbalance)

#### **Supply Current vs Temperature**

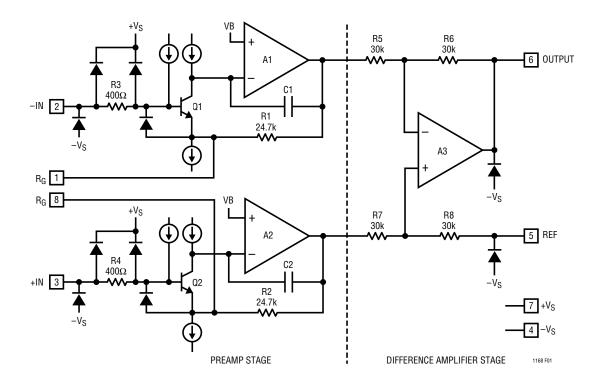

### **BLOCK DIAGRAM**

Figure 1. Block Diagram

## THEORY OF OPERATION

The LT1168 is a modified version of the three op amp instrumentation amplifier. Laser trimming and monolithic construction allow tight matching and tracking of circuit parameters over the specified temperature range. Refer to the block diagram (Figure 1) to understand the following circuit description. The collector currents in Q1 and Q2 are trimmed to minimize offset voltage drift, thus assuring a high level of performance. R1 and R2 are trimmed to an absolute value of 24.7k to assure that the gain can be set accurately (0.6% at G = 100) with only one external resistor R<sub>G</sub>. The value of R<sub>G</sub> in parallel with R1 (R2) determines the transconductance of the preamp stage. As R<sub>G</sub> is reduced for larger programmed gains, the transconductance of the input preamp stage increases to that of the input transistors Q1 and Q2. This increases the open-loop gain when the programmed gain is increased, reducing the input referred gain related errors and noise. The input

voltage noise at gains greater than 50 is determined only by Q1 and Q2. At lower gains the noise of the difference amplifier and preamp gain setting resistors increase the noise. The gain bandwidth product is determined by C1, C2 and the preamp transconductance which increases with programmed gain. Therefore, the bandwidth does not drop proportionally with gain.

The input transistors Q1 and Q2 offer excellent matching, which is inherent in NPN bipolar transistors, as well as picoampere input bias current due to superbeta processing. The collector currents in Q1 and Q2 are held constant due to the feedback through the Q1-A1-R1 loop and Q2-A2-R2 loop which in turn impresses the differential input voltage across the external gain set resistor  $R_G$ . Since the current that flows through  $R_G$  also flows through R1 and R2, the ratios provide a gained-up differential

## THEORY OF OPERATION

voltage,  $G = (R1 + R2)/R_G$ , to the unity-gain difference amplifier A3. The common mode voltage is removed by A3, resulting in a single-ended output voltage referenced to the voltage on the REF pin. The resulting gain equation is:

$$G = (49.4k\Omega/R_G) + 1$$

solving for the gain set resistor gives:

$$R_G = 49.4k\Omega/(G-1)$$

Table 1 shows appropriate 1% resistor values for a variety of gains.

Table 1

| DESIRED GAIN | R <sub>G</sub> | CLOSEST 1% VALUE | RESULTANT GAIN |

|--------------|----------------|------------------|----------------|

| 1            | Open           | Open             | 1              |

| 2            | 49400Ω         | 49900Ω           | 1.99           |

| 5            | 12350Ω         | 12400Ω           | 4.984          |

| 10           | 5488.89Ω       | 5490Ω            | 9.998          |

| 20           | 2600Ω          | 2610Ω            | 19.93          |

| 50           | 1008.16Ω       | 1000Ω            | 50.4           |

| 100          | 498.99Ω        | 499Ω             | 99.998         |

| 200          | 248.24Ω        | 249Ω             | 199.4          |

| 500          | 99Ω            | 100Ω             | 495            |

| 1000         | 49.95Ω         | 49.4Ω            | 1001           |

#### **Input and Output Offset Voltage**

The offset voltage of the LT1168 has two components: the output offset and the input offset. The total offset voltage referred to the input (RTI) is found by dividing the output offset by the programmed gain (G) and adding it to the input offset. At high gains the input offset voltage dominates, whereas at low gains the output offset voltage dominates. The total offset voltage is:

Total input offset voltage (RTI)

= input offset + (output offset/G)

Total output offset voltage (RTO)

= (input offset • G) + output offset

#### **Reference Terminal**

The reference terminal is one end of one of the four 30k resistors around the difference amplifier. The output

voltage of the LT1168 (Pin 6) is referenced to the voltage on the reference terminal (Pin 5). Resistance in series with the REF pin must be minimized for best common mode rejection. For example, a  $6\Omega$  resistance from the REF pin to ground will not only increase the gain error by 0.02% but will lower the CMRR to 80dB.

#### **Input Voltage Range**

The input voltage range for the LT1168 is specified in the data sheet at 1.4V below the positive supply to 1.9V above the negative supply for a gain of one. As the gain increases the input voltage range decreases. This is due to the IR drop across the internal gain resistors R1 and R2 in Figure 1. For the unity gain condition there is no IR drop across the gain resistors R1 and R2, the output of the GM amplifiers is just the differential input voltage at Pin 2 and Pin 3 (level shifted by one V<sub>BF</sub> from Q1 and Q2). When a gain resistor is connected across Pins 1 and 8, the output swing of the GM cells is now the differential input voltage (level shifted by  $V_{\mbox{\footnotesize{BE}}})$  plus the differential voltage times the gain (ratio of the internal gain resistors to the external gain resistor across Pins 1 and 8). To calculate how close to the positive rail the input  $(V_{IN})$  can swing for a gain of 2 and a maximum expected output swing of 10V, use the following equation:

$$+V_S - V_{IN} = -0.5 - (V_{OUT}/G) \cdot (G-1)/2$$

Substituting yields:

$$-0.5 - (10/2) \cdot (1/2) = -3V$$

below the positive supply or 12V for a 15V supply. To calculate how far above the negative supply the input can swing for a gain of 10 with a maximum expected output swing of -10V, the equation for the negative case is:

$$-V_S + V_{IN} = 1.5 - (V_{OIJT}/G) \cdot (G - 1)/2$$

Substituting yields:

$$1.5 - (-10/10) \cdot 9/2 = 6V$$

above the negative supply or -9V for a negative supply voltage of -15V. Figures 2 and 3 are for the positive common mode and negative common mode cases respectively.

## THEORY OF OPERATION

Figure 2. Positive Input Range vs Output Voltage for Different Gains

Figure 3. Negative Input Voltage Range vs Output Voltage for Various Gains

## **Single Supply Operation**

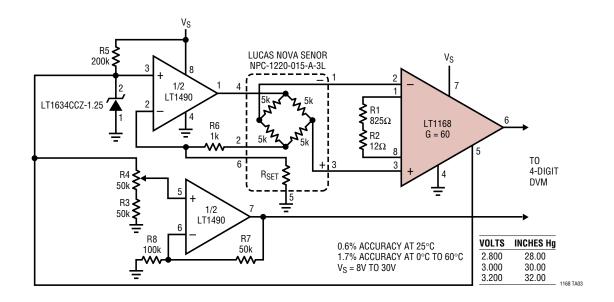

For best results under single supply operation, the REF pin should be raised above the negative supply (Pin 4) and one of the inputs should be at least 2.5V above ground. The barometer application later in this data sheet is an example that satisfies these conditions. The resistance  $R_{\text{SET}}$  from the bridge transducer to ground sets the operating current for the bridge, and with R6, also has the effect of raising the input common mode voltage. The output of the LT1168 is always inside the specified range since the barometric pressure rarely goes low enough to cause the output to clip (30.00 inches of Hg corresponds to 3.000V). For applications that require the output to swing at or below the REF

potential, the voltage on the REF pin can be further level shifted. The application in the front of this data sheet, Single Supply Pressure Monitor, is an example. An op amp is used to buffer the voltage on the REF pin since a parasitic series resistance will degrade the CMRR.

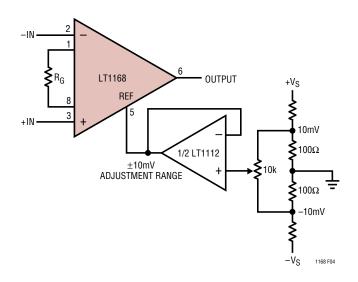

#### **Output Offset Trimming**

The LT1168 is laser trimmed for low offset voltage so that no external offset trimming is required for most applications. In the event that the offset needs to be adjusted, the circuit in Figure 4 is an example of an optional offset adjust circuit. The op amp buffer provides a low impedance to the REF pin where resistance must be kept to minimum for best CMRR and lowest gain error.

Figure 4. Optional Trimming of Output Offset Voltage

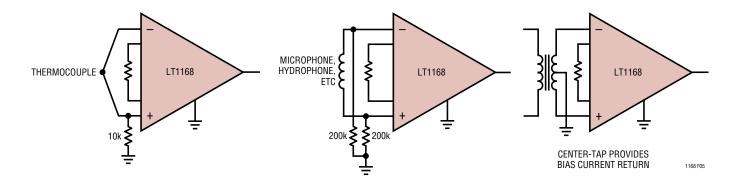

#### **Input Bias Current Return Path**

The low input bias current of the LT1168 (250pA) and the high input impedance (200G $\Omega$ ) allow the use of high impedance sources without introducing additional offset voltage errors, even when the full common mode range is required. However, a path must be provided for the input bias currents of both inputs when a purely differential signal is being amplified. Without this path the inputs will float to either rail and exceed the input common mode range of the LT1168, resulting in a saturated input stage. Figure 5 shows three examples of an input bias current

### THEORY OF OPERATION

path. The first example is of a purely differential signal source with a  $10k\Omega$  input current path to ground. Since the impedance of the signal source is low, only one resistor is needed. Two matching resistors are needed for higher

impedance signal sources as shown in the second example. Balancing the input impedance improves both common mode rejection and DC offset.

Figure 5. Providing an Input Common Mode Current Path

## APPLICATIONS INFORMATION

The LT1168 is a low power precision instrumentation amplifier that requires only one external resistor to accurately set the gain anywhere from 1 to 1000. The LT1168 is trimmed for critical DC parameters such as gain error (0.04%, G = 10), input offset voltage (40 $\mu$ V, RTI), CMRR (90dB min, G = 1) and PSRR (103dB min, G = 1). These trims allow the amplifier to achieve very high DC accuracy. The LT1168 achieves low input bias current of just 250pA (max) through the use of superbeta processing. The output can handle capacitive loads up to 1000pF in any gain configuration and the inputs are protected against ESD strikes up to  $\pm 13kV$  (human body).

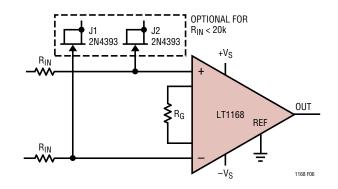

### **Input Protection**

The LT1168 can safely handle up to  $\pm 20$ mA of input current in an overload condition. Adding an external 5k input resistor in series with each input allows DC input fault voltage up to  $\pm 100$ V and improves the ESD immunity to  $\pm 8$ kV (contact) and  $\pm 15$ kV (air discharge), which is the IEC 1000-4-2 level 4 specification. If lower value input resistors must be used, a clamp diode from the positive supply to each input will maintain the IEC 1000-4-2

specification to level 4 for both air and contact discharge. A 2N4393 drain/source to gate is a good low leakage diode for use with resistors between 1k and 20k, see Figure 6. The input resistors should be carbon and not metal film or carbon film in order to withstand the fault conditions.

Figure 6. Input Protection

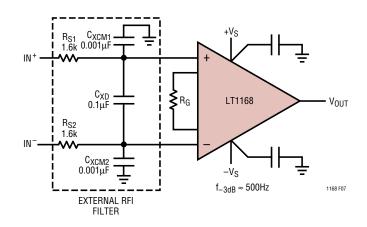

#### **RFI** Reduction

In many industrial and data acquisition applications, instrumentation amplifiers are used to accurately amplify small signals in the presence of large common mode

## APPLICATIONS INFORMATION

voltages or high levels of noise. Typically, the sources of these very small signals (on the order of microvolts or millivolts) are sensors that can be a significant distance from the signal conditioning circuit. Although these sensors may be connected to signal conditioning circuitry, using shielded or unshielded twisted-pair cabling, the cabling may act as antennae, conveying very high frequency interference directly into the input stage of the LT1168.

The amplitude and frequency of the interference can have an adverse effect on an instrumentation amplifier's input stage by causing an unwanted DC shift in the amplifier's input offset voltage. This well known effect is called RFI rectification and is produced when out-of-band interference is coupled (inductively, capacitively or via radiation) and rectified by the instrumentation amplifier's input transistors. These transistors act as high frequency signal detectors, in the same way diodes were used as RF envelope detectors in early radio designs. Regardless of the type of interference or the method by which it is coupled into the circuit, an out-of-band error signal appears in series with the instrumentation amplifier's inputs.

To significantly reduce the effect of these out-of-band signals on the input offset voltage of instrumentation amplifiers, simple lowpass filters can be used at the inputs. This filter should be located very close to the input pins of the circuit. An effective filter configuration is illustrated in Figure 7, where three capacitors have been added to the inputs of the LT1168. Capacitors C<sub>XCM1</sub> and C<sub>XCM2</sub> form lowpass filters with the external series resistors R<sub>S1.2</sub> to any out-of-band signal appearing on each of the input traces. Capacitor  $C_{XD}$  forms a filter to reduce any unwanted signal that would appear across the input traces. An added benefit to using  $C_{XD}$  is that the circuit's AC common mode rejection is not degraded due to common mode capacitive imbalance. The differential mode and common mode time constants associated with the capacitors are:

$$t_{DM(LPF)} = (R_{S1} + R_{S2})(C_{XD} + C_{XCM1} + C_{XCM2})$$

$t_{CM(LPF)} = (R_{S1} || R_{S2})(C_{XCM1} + C_{XCM2})$

Setting the time constants requires a knowledge of the frequency, or frequencies of the interference. Once this

frequency is known, the common mode time constants can be set followed by the differential mode time constant. To avoid any possibility of inadvertently affecting the signal to be processed, set the common mode time constant an order of magnitude (or more) smaller than the differential mode time constant. Set the common mode time constants such that they do not degrade the LT1168 inherent AC CMR. Then the differential mode time constant can be set for the bandwidth required for the application. Setting the differential mode time constant close to the sensor's BW also minimizes any noise pickup along the leads. To avoid any possibility of common mode to differential mode signal conversion, match the common mode time constants to 1% or better. If the sensor is an RTD or a resistive strain gauge and is in proximity to the instrumentation amplifier, then the series resistors R<sub>S1, 2</sub> can be omitted.

Figure 7. Adding a Simple RC Filter at the Inputs to an Instrumentation Amplifier is Effective in Reducing Rectification of High Frequency Out-of-Band Signals

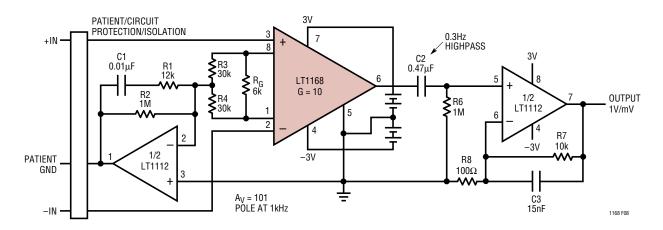

#### **Nerve Impulse Amplifier**

The LT1168's low current noise makes it ideal for EMG monitors that have high source impedances. Demonstrating the LT1168's ability to amplify low level signals, the circuit in Figure 8 takes advantage of the amplifier's high gain and low noise operation. This circuit amplifies the low level nerve impulse signals received from a patient at Pins 2 and 3.  $R_{\rm G}$  and the parallel combination of R3 and R4 set a gain of ten. The potential on LT1112's Pin 1 creates

## APPLICATIONS INFORMATION

a ground for the common mode signal. C1 was chosen to maintain the stability of the patient ground. The LT1168's high CMRR ensures that the desired differential signal is amplified and unwanted common mode signals are attenuated. Since the DC portion of the signal is not important, R6 and C2 make up a 0.3Hz highpass filter. The AC signal at LT1112's Pin 5 is amplified by a gain of 101 set by R7/R8 +1. The parallel combination of C3 and R7 form a lowpass filter that decreases this gain at frequencies above 1kHz. The ability to operate at  $\pm 3V$  on  $350\mu A$  of supply current makes the LT1168 ideal for battery-powered applications. Total supply current for this application is 1.05mA. Proper safeguards, such as isolation, must be added to this circuit to protect the patient from possible harm.

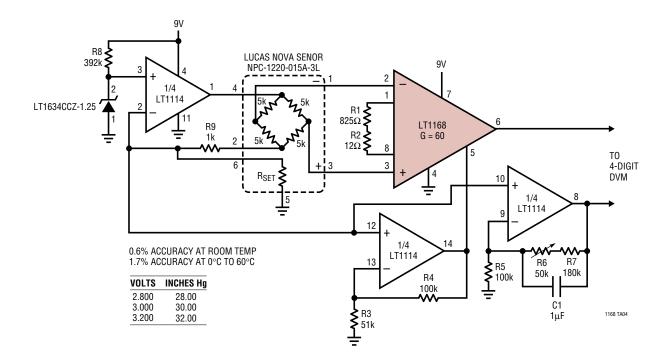

## Low I<sub>B</sub> Favors High Impedance Bridges, Lowers Dissipation

The LT1168's low supply current, low supply voltage operation and low input bias currents allow it to fit nicely into battery-powered applications. Low overall power dissipation necessitates using higher impedance bridges. The single supply pressure monitor application on the front of this data sheet, shows the LT1168 connected to the differential output of a 3.5k bridge. The picoampere input bias currents keep the error caused by offset current to a negligible level. The LT1112 level shifts the LT1168's reference pin and the ADC's analog ground pins above ground. The LT1168's and LT1112's combined power dissipation is still less than the bridge's. This circuit's total supply current is just 2.2mA.

Figure 8. Nerve Impulse Amplifier

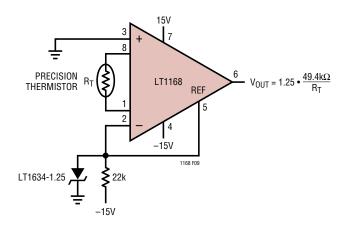

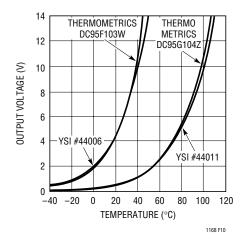

Figure 9. Precision Temperature Without Precision Resistors

Figure 10. Response of Figure 9 for Various Thermistors

## TYPICAL APPLICATIONS

#### **Single Supply Barometer**

#### **AC Coupled Instrumentation Amplifier**

## TYPICAL APPLICATIONS

#### **4-Digit Pressure Sensor**

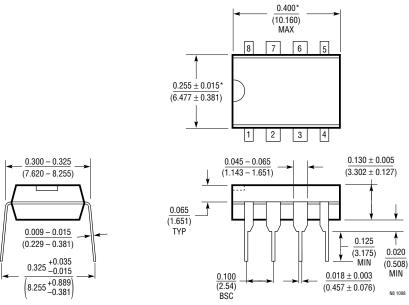

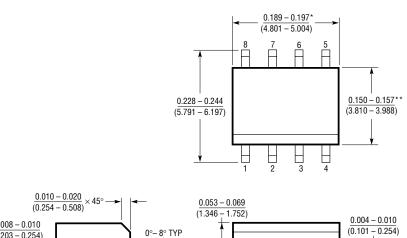

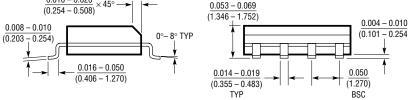

## PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

#### N8 Package 8-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

#### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

\*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

S08 1298

<sup>\*\*</sup>DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

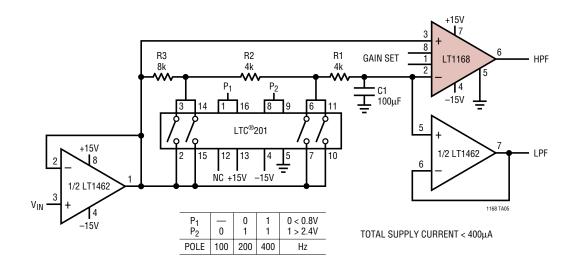

## TYPICAL APPLICATION

#### Low Power Programmable Audio HPF/LPF with "Pop-Less" Switching

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                      | COMMENTS                                                              |

|-------------|------------------------------------------------------------------|-----------------------------------------------------------------------|

| LTC1043     | Dual Precision Instrumentation Building Block                    | Switched Capacitor, Rail-to-Rail Input, 120dB CMRR                    |

| LTC1100     | Precision Chopper-Stabilized Instrumentation Amplifier           | $G = 10 \text{ or } 100, V_{OS} = 10 \mu\text{V}, I_B = 50 \text{pA}$ |

| LT1101      | Precision, Micropower, Single Supply Instrumentation Amplifier   | G = 10 or 100, I <sub>S</sub> = 105μA                                 |

| LT1102      | High Speed, JFET Instrumentation Amplifier                       | G = 10 or 100, Slew Rate = 30V/µs                                     |

| LT1167      | Single Resistor Programmable Precision Instrumentation Amplifier | Lower Noise than LT1168, $e_N = 7.5 \text{nV}/\sqrt{\text{Hz}}$       |