### L64021

# **MPEG-2** Digital Video Disk

## Decoder

# **Preliminary Datasheet**

The L64021 DVD Audio/Video Decoder balances high integration and low cost in a single chip design that delivers quality and performance for DVD systems. LSI Logic's integrated MPEG-2, Dolby Digital (AC-3) core provides full support for both consumer-based DVD players and DVD PC applications. Backward compatible with both existing CD-ROM and Video CD formats, the L64021 enables designers to develop low-cost next generation DVD systems.

The L64021 extends the capabilities of LSI Logic's time-tested and market-proven MPEG-2 decoders by integrating licensed Content Scrambling System (CSS) technology. The integrated CSS unit provides secure authentication and descrambling of protected DVD content. At the same time, the L64021 maintains low processor overhead and low system cost.

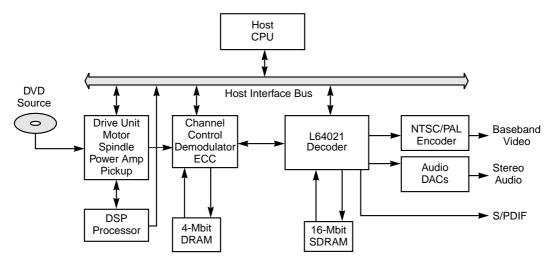

The L64021 DVD A/V Decoder receives coded audio, video, and private data to produce decoded audio/video output with subpicture graphics overlay. LSI Logic has optimized the input/output interfaces for low cost integration into any number of DVD system architectures. The block diagram in Figure 1 illustrates an L64021 DVD system implementation.

Figure 1 DVD System Block Diagram

April 1999 Copyright © 1995–1997 by LSI Logic Corporation. All rights reserved. LSI Logic's digital video architecture for the L64021 incorporates many unique features and capabilities. These architectural elements include flexible preparsing for system streams, processing up to the sequence layer, a flexible display controller, 24-bit/96-kHz Linear PCM support, and a multitap filter. Video features include a host of programmable, high quality trick play modes. LSI Logic's programmable trick play provides system designers the flexibility to develop unique features for easy product differentiation.

The L64021 Decoder is available in a 160-pin plastic quad flat package (PQFP) that is compatible with the other members of the LSI Logic decoder family. The L64021 is manufactured using a 0.25 micron low-power CMOS process and is available in a 3.3-V version.

### **Features**

### Video Decoding

- Includes an embedded RISC Processor

- ♦ Integrates studio quality MPEG-2 video decoder

- ◆ Fully complies with Main Profile at Main Level MPEG-2 standard, ISO 13818-2

- Decodes MPEG-2 bitstreams, including MPEG-2 program stream, with private stream support

- ♦ Decodes an MPEG-1 bitstream as defined in ISO IS 11172, including the MPEG-1 system layer

- ◆ Operates at image sizes up to CCIR601 resolution of 720 x 480 pixels @ 30 fps for NTSC and 720 x 576 @ 25 fps for PAL

### **Audio Decoding**

- Several audio output options available:

- PCM through the CD Bypass (2 ch.)

- Decoded PCM from MPEG, LPCM, or AC-3 (2 ch.)

- AC-3 coded stream with multichannel extensions (5.1 ch.)

- MPEG coded stream with multichannel extensions (7 ch.)

- ◆ Combines MPEG and Dolby Digital audio decoding with support for Linear PCM data

- ◆ Decodes dual channel MPEG audio, Layer I and II ISO 11172-3 supporting bit rates of 8–448 Kbps and sampling rates of 16, 22.05, 24, 32, 44.1, and 48 kHz

- Decodes 5.1 channel Dolby Digital, downmixing to 2 outputs over the entire range of compliant bit rates and sampling rates

- Supports Linear PCM streams with sample rates of 48 and 96 kHz

- ♦ Supports Dolby Pro Logic downmix

### **Data and Error Handling Capabilities**

- ♦ Up to 20-Mbits/s sustained input channel Adata rate

- ♦ Input data format: 8-bit parallel through dedicated channel interface output: 8-bit (Y, Cb, Cr) in slave mode

- ♦ Complete on-chip channel buffer and display buffer controls

- ♦ Error concealment maintains display of images during channel errors

- Mute on error for concealment in audio decoder

- ♦ No external microcode or external logic required

### **Video Display and Graphics Support**

- Integrates a flexible 4, 16, or 256-color on-screen display (OSD) controller

- Allows connection to an external OSD generator

- Programmable display management

- Programmable channel buffer and display buffer size

- ♦ Slave video timing operation

- Supports trick modes commonly needed in DVD systems

- Integrates postprocessing filters for image resizing (horizontal and vertical)

- Integrates vertical filter for letterbox format display

- ♦ Implements subpicture data processing on-chip

- ♦ Implements 3:2 pulldown directly from the bitstream

- ♦ Supports pan and scan with 1/8 pixel accuracy from the bitstream

- ♦ Supports 4:2:0 to 4:2:2 sampling filters

- ♦ 16-level alphablending for OSD

### **Cost Effective System Implementation**

- ♦ Programmable preparser accepts PES, ES, and PS streams

- ♦ Directly connects to commodity SDRAM

- Input/output interfaces are optimized for glueless integration into consumer video systems

- Channel interface includes an embedded Content Scramble System (CSS) Unit for A/V descrambling and key authentication.

- Operates from a single 27-MHz clock, with additional audio sample clock input

- ◆ Total external memory required for audio and video decoding: 16-Mbit SDRAM for CCIR601 resolution

- Interfaces to Intel or Motorola 8-bit Host CPU for initialization, testing, and status monitoring

- ♦ Directly interfaces to off-the-shelf NTSC/PAL encoders

- Directly interfaces to off-the-shelf audio DACs

- ♦ 160-pin PQFP package

- ♦ Low power 3.3-V process

- ♦ TTL-compatible I/O pins

L64021 MPEG-2 Digital Video Disk Decoder

## **Functional Description**

Figure 2 provides a block diagram of the L64021's major functional units. An overview of the major functions of the L64021 follows the diagram.

**Audio Decoder** CD 1/300 Stereo **Bypass** 27 MHz SCR DAC Clock U Audio İ/F Counter Divider SYSCLK ACLK A MPEG-2 Host Interface Serial Output Dolby Digital I/F S/PDIF Interrupt (IEC958) Generator Control Linear PCM Host CPU Data **FIFO** Video Decoder and MPEG-2 Address **Display Control** Video Decoder Filters RISC Baseband Processor Video Channel Display NTSC/PAI Data Interface OSD/Graphics Mix Controller Encoder MPEG-2 Timing Program CSS Stream Unit Strobe SDRAM Interface rogrammable Data 2 Preparser Data Request Data L64021 Address Control 16 16-Mbit **SDRAM**

Figure 2 L64021 Block Diagram

### **Video and Audio Decoding**

The L64021 can decode separate video and audio elementary streams, A/V PES streams (from transport decoders), and program elementary stream (PES) containing both audio, video, and private 1 and 2 streams. In addition, the PES decoding can parse critical headers for both Presentation Time Stamp (PTS) and Decoding Time Stamp (DTS) information necessary for video and audio synchronization.

### **Video Decoding**

This section includes a description of the major components involved in handling and decoding video:

- Video Decoder

- Video Postprocessing Filters and Letterbox Display

- On-Screen Display with Graphics Support and SPU Decoder

#### Video Decoder

The L64021 operates optimally at image sizes up to 720 x 480 pixels, with a frame rate of 30 fps for NTSC (or 720 x 576 @ 25 fps for PAL). The L64021 can also decode MPEG-1 sequences. The coded data channel may have a sustained bit rate of up to 20 Mbit/s. The L64021 also supports images with resolution lower than 720 x 480 pixels (see Video Postprocessing Filters).

### Video Postprocessing Filters and Letterbox Display

Images with resolutions below 720 x 480 pixels are interpolated to full size using on-chip filters. This allows programming produced at different resolutions to be decoded and displayed on televisions with standard NTSC or PAL timing, and it allows the use of digital or analog NTSC or PAL encoders operating at standard television frequencies (typically 27 MHz). In addition, the filters provide the capability to pan and scan the MPEG image to 1/8-pixel accuracy. The L64021 also supports letterbox display format with an integrated vertical filter for 3/4 decimation (720 x 480 images are decimated to 720 x 360 pixels).

### On-Screen Display Controller with Graphics Support and SPU Decoder

The L64021 integrates an on-screen display (OSD) controller capable of overlaying an image up to 720 x 480 pixels (720 x 576 for PAL) at up to 8 bits/pixel on top of an MPEG video sequence while it is being decoded. In addition, the L64021 contains an on-chip Subpicture Unit (SPU) decoder for cost-effective integration of the graphics function. The SPU decodes the bit map for graphic overlay and executes SPU instructions so the graphic display can be changed on the fly without CPU intervention.

### **Audio Decoding**

The L64021 integrates an MPEG (Musicam) and Dolby Digital audio decoder with support for Linear PCM audio. It can decode two channels of MPEG audio Layer I or Layer II over the full range of compliant bit rates and sample rates. It also can decode 5.1 channels of Dolby Digital and downmix this information to two channels of audio output over the full range of compliant bit rates and sample rates. The audio decoder uses the same memory as the video decoder for its channel buffers—which eliminates the need for extra SDRAM found in other nonintegrated audio solutions.

### **External Interfacing**

The L64021 includes the following external interfaces:

- ♦ Host Interface

- ♦ Channel Interface

- ♦ Memory Interface

- ♦ Video Output

- Audio Output

- Audio Input

#### **Host Interface**

A stand-alone, dedicated host interface allows the user to program a variety of options and monitor the operation of the L64021. In addition, through this port you can read user data that is present in the data channel and read errors flagged by the L64021. The device does not maintain unread user data indefinitely. The host interface includes a FIFO to which no more data can be written once the FIFO becomes full. Subsequent data will be lost. The system controller must read data transmitted in the user data records of the MPEG bitstream, even if that data is subsequently used to control some aspect of the video display subsystem. The controller must read this data, then write it to the L64021 internal state registers, if necessary. The host interface also allows you to read and write data into the memory for OSD and channel buffer access.

#### **Channel Interface**

The L64021 includes an independent parallel interface for direct connection to upstream error correction devices. The interface uses simple signal handshaking for compressed stream transfer to the decoder.

The L64021's channel interface handles the incoming coded data, which is assumed to be an MPEG-2 compliant bitstream, and provides error detection, reporting, CSS content descrambling, and disk/title key authentication. The channel interface detects data in the bitstream that does not meet MPEG-2 or Dolby Digital syntax or grammar rules and can flag the data for exception processing.

Hardware error handling includes error masking and the application of concealment vectors in video. Audio error concealment includes muting on errors and searching for error-free frames. The channel interface flags gross errors in the bitstream that are due to channel buffer overrun or underrun or to nonconformance in the bitstream. The error flagging is done so the errors can be masked in the display or in the audio output. To handle gross errors, you can program an external microcontroller with an error recovery mechanism.

The L64021 channel interface also includes a fully integrated CSS unit that provides on-core disk/title key authentication and A/V descrambling. The CSS unit can be run in one of five modes: bypass, data key extraction, A/V descrambling, authentication and disk key extraction, or authentication and title key decryption mode.

### **Memory Interface**

The L64021 supports direct connection to commercial SDRAM for use as frame stores, channel buffers, and overlay memory. The L64021 uses frame stores for intermediate frame reconstruction and display, separate video and audio channel buffers for rate matching, and zero or more regions for graphic overlays. This storage is combined into a single, contiguous memory space accessed over a 16-bit wide bus. In most cases, this is one 1M x 16-bit SDRAM, for a total memory space of 2 Mbytes.

The interface between the L64021 and SDRAM requires no external components. The L64021 pinout allows connection to the SDRAM to be made on a single PCB layer. During normal operation, the L64021

exclusively controls the SDRAM frame stores. However, it is possible to access the SDRAM through the host port on the L64021 for test, for verification, and for access to the overlay stores and channel information.

### **Video Output**

The L64021 provides a digitized video output for subsequent display. This data is in the CCIR601 (Y, Cb, Cr) color space. The video output operates with a luminance sample rate that is always exactly half the device clock—nominally 13.5 MHz from a 27-MHz input clock. The L64021 can accept external synchronization signals in slave mode. The L64021 supports a number of trick modes specific to the needs of DVD systems, including freeze frame, skip B pictures, skip B and P pictures, and search for GOP.

### **Audio Output**

The audio decoder produces a serial PCM output that is compatible with most commercial audio DACs. The audio decoder includes circuitry to maintain the correct audio output sample rate based upon an external audio clock. The decoder also provides an audio oversampling output clock to the external audio DAC; this audio output clock is selected from one of the audio clock inputs. In addition, the decoder supports the IEC958 output format for PCM samples, transporting compressed Dolby Digital bitstreams, and MPEG-2 multichannel extensions.

### **Audio Input**

The L64021 supports several audio input modes. It supports connection to a Sony/Philips Digital Interface Format (S/PDIF) input that can be routed directly to the S/PDIF output. The device also handles input signals that can be connected directly from a CD-ROM player to the PCM output.

# **Signal Descriptions**

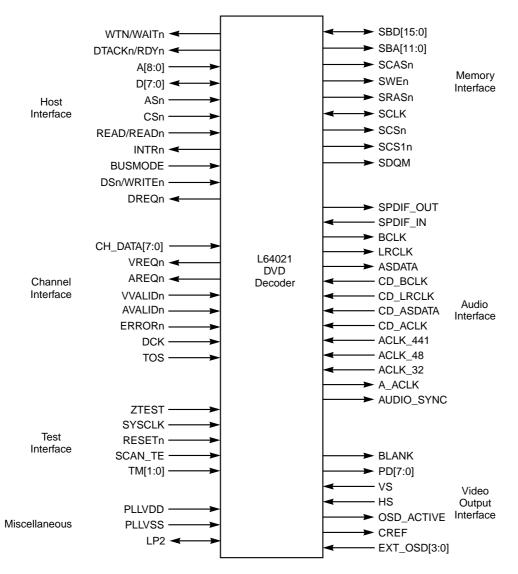

This section provides detailed information on the L64021 signals. The signal descriptions are useful for hardware designers who are interfacing the L64021 with other devices. Figure 3 shows the logic symbol for the L64021. Signals that end in an "n" are active LOW. Otherwise, it is active HIGH.

Figure 3 L64021 Logic Symbol

The L64021 has six major signal interfaces:

- Host Interface on page 11

- ♦ Channel Interface on page 14

- ♦ Memory Interface on page 15

- ♦ Video Output Interface on page 16

- ♦ Audio Interface on page 17

- Miscellaneous and Test Interfaces on page 19

### **Host Interface**

### A[8:0] Address Bus

Input

Input

This 9-bit address line provides access to the L64021's internal registers. The address value on these lines is latched on the falling edge of ASn (Motorola) or on the falling edge of READn/WRITEn (Intel).

### ASn Address Strobe (Motorola Mode only)

This signal latches (in the L64021) the address currently on the A[8:0] bus. The address latches on the falling edge of the ASn signal. ASn also indicates the start and end of a bus cycle transaction. ASn LOW and CSn LOW indicate the start of a bus transaction. The rising edge of ASn indicates the end of a bus transaction.

### **BUSMODE** Controller Select Pin

Input

This signal specifies whether the Host CPU is an Intel or a Motorola microprocessor. When HIGH, the Motorola mode is selected. When LOW, the Intel mode is selected. The Motorola processor uses one pin to specify read and write transfers. The Intel processor uses two separate pins to specify read and write transfers. Please see the DSn signal definition below.

### CSn Chip Select (Motorola and Intel Mode) Input

This active-LOW signal indicates an attempt by an external host CPU to access the L64021 either for a read or a write bus cycle. The event of CSn LOW and ASn LOW indicates the start of a bus transaction in Motorola mode. The CSn LOW and READn LOW or WRITEn LOW indicates the start of a bus cycle in Intel mode. The actual transaction type (either read or write) is determined by

the READ polarity (Motorola type interface) or by READn and WRITEn polarity (Intel type interface). The end of a bus cycle is determined by the rising edge of ASn (Motorola) or the rising edge of READn or WRITEn (Intel). CSn may stay active LOW for more than one bus transaction cycle.

### D[7:0] Host Data Bus Bidirectional

This host data bus is an 8-bit bidirectional data line used for data communication between the host CPU and the L64021. During a read bus cycle, D[7:0] carries valid information from an internal L64021 register. DTACK or WAITn indicate when the data on the host data bus is valid. The rising edge of WRITEn (Intel) or DSn (Motorola) indicates to the L64021 when to strobe the data into the chip.

### DREQn DMA Transfer Request Output

This signal is an active-LOW output that indicates when the decoder is ready to receive a new byte of DMA data. The decoder is considered ready when the interface is ready and the internal write FIFO is not full, or if the internal read FIFO is not empty. If these conditions are not met, DREQn is not asserted. The maximum transfer rate over this interface is 20 Mbit/s.

# DTACKn Data Acknowledge (Motorola) RDYn RDYn (Intel) 3-State Output

This signal is active LOW when used as DTACKn (Motorola mode). When used as RDYn (Intel mode), this signal is active LOW.

When used as DTACKn, the L64021 drives this signal LOW to indicate to the external host CPU that the current bus transaction can be completed. The signal is 3-stated if CSn is not active. L64021 drives DTACKn HIGH when it is not ready to end the bus cycle, and it drives DTACKn LOW when it is ready to end the bus cycle.

When used as RDYn, the L64021 drives this signal LOW to indicate to the external host CPU that the L64021 is ready to complete the current bus transaction. The L64021 drives RDYn HIGH when the L64021 is not ready. The signal is 3-stated if CSn is not active.

### INTRn Interrupt OD Output

This signal is an active-LOW interrupt output. It has an open drain. The L64021's host interface drives this signal LOW to send an interrupt to the Host CPU.

# DSn Data Strobe (Motorola) WRITEn WRITEn (Intel)

Input

DSn (Motorola mode) indicates when the CPU strobes the data in or out of the L64021. During a read bus cycle, the start of a read transaction is triggered when DSn, CSn, and ASn are all LOW. During a write bus cycle, the rising edge of DSn indicates when the L64021 latches the data present on D[7:0].

When WRITEn (Intel mode) is LOW it indicates that the external host CPU is performing a write bus cycle. READ/READn must be HIGH during a write cycle. CSn LOW indicates that the host CPU is attempting to write to the L64021's internal registers. The address is registered on the falling edge of READn. On the rising edge of WRITEn, the L64021 latches the data present on D[7:0].

# READ Read/Write Strobe (Motorola) READn READn (Intel)

Input

READ (Motorola mode) indicates whether the current bus cycle is a read or write. When READ is HIGH, a read bus cycle is in progress. When READ is LOW, a write bus cycle is in progress. CSn must be LOW for the CPU to access the L64021.

READn (Intel mode) is LOW when the external CPU is performing a bus read cycle. WRITEn must be HIGH during a read cycle. When both CSn and READn are LOW, the host CPU is reading from the L64021's internal registers. The address is registered on the falling edge of READn.

# WTN Device Wait (Motorola) WAITn Device Wait (Intel)

**3-State Output**

This signal is 3-state or active LOW when used as a WAITn signal. It may be used to interface to processors other than Motorola and Intel host CPUs. The signal's function is similar to DTACKn/RDYn (described earlier); however, the polarity is inverted. The L64021 drives this signal HIGH to indicate to the external host CPU that the current transaction can be completed. The signal is

3-stated if CSn is not active. The L64021 drives the signal LOW when it is not ready to end the bus cycle, and drives the signal HIGH when it is ready to end the bus cycle.

### Channel Interface

### AREQn Audio Transfer Request Output

When the L64021 asserts this signal LOW, it indicates that the L64021 is ready to receive a new byte of coded audio data (or system data in system mode). The L64021 is considered ready when both the interface is ready and there is room in the audio channel buffer. If this is not true, then AREQn is not asserted. The maximum transfer rate over this interface is 20 Mbit/s.

Note: In a DVD system, AREQn and AVALIDn input the

program stream that is present on CH\_DATA[7:0].

### AVALIDn Audio Data Valid Input

The rising edge of AVALIDn writes the next byte of audio data or program stream data that is present on the CH[7:0] pins. AVALIDn can be used with the DCK data clock for synchronous input to the L64021's channel interface.

### CH\_DATA[7:0]

#### Channel Data Bus

Input

CH\_DATA[7:0] is an input bus that serves as a parallel path for incoming channel data.

### DCK Channel Data Clock Input

The DCK is a free-running clock from the external channel. Together, the DCK and VALIDn signals can write data synchronously to the L64021 channel input.

### ERRORn Error Input

ERRORn is an active-LOW input signal. The external channel device asserts this signal to indicate that the channel data contains an error. The ERRORn signal is latched with the data on the rising edge of AVALIDn or VVALIDn. ERRORn indicates uncorrectable errors in the channel, and invokes error handling in the L64021.

ERRORn is not used for DMA transfers.

### TOS Top of Sector

The external channel device asserts TOS during the pack start code at the top of a sector. The L64021 uses TOS for error detection and registers the TOS signal on the rising edge of AVALIDn.

### VREQn Video Transfer Request Output

This signal is an active-LOW output. The L64021 asserts VREQn when it is ready to receive a new byte of coded video data. The L64021 is ready when both the interface is ready and there is room in the video channel buffer. If these conditions are not true, VREQn is not asserted. The maximum transfer rate over this interface is 20 Mbit/s.

Note: In a DVD system, the VREQn and VVALIDn pins are not used

### VVALIDn Video Data Valid Input

The rising edge of VVALIDn writes into the channel buffer the next byte of video data that is present on the CH[7:0] data bus. VVALIDn is not used in the system or program stream modes. VVALIDn can be used together with the DCK data clock for synchronous input to the L64021 channel.

### **Memory Interface**

### SBA[11:0] SDRAM Address Bus Output

This 12-bit output address bus specifies the row/column address and connects directly to an external SDRAM memory. The L64021 uses the external SDRAM memory for picture reconstruction and channel buffering.

### SBD[15:0] SDRAM Data Bus Bidirectional

This 16-bit bidirectional data bus connects directly to an external 1M x 16-bit SDRAM memory. The L64021 uses the external SDRAM memory for picture reconstruction and channel buffering.

### SCASn SDRAM Column Address Select Output

This is an active-LOW signal that drives the  $\overline{\text{CAS}}$  pin on the attached SDRAM.

Input

SCLK SDRAM 81-MHZ Clock Bidirectional

This 81-MHz clock signal drives the CLK pin on the attached SDRAM.

SCSn Chip Select for SDRAM

Output

SCSn is an active-LOW signal that selects the lowaddress bank of the SDRAM, which is used for the first 16 Mbits of memory.

SCS1n Chip Select for Second SDRAM

Output

SCS1n is an active-LOW signal that selects the highaddress bank of the SDRAM. This signal is used in systems that have more than 16 Mbits of DRAM.

SDQM SDRAM Control Pin

Output

SDQM is an active-HIGH output signal for the SDRAM

data control mask.

SRASn SDRAM Row Address Select

Output

This is an active-LOW signal that drives the RAS pin on the attached SDRAM.

SWEn SDRAM Write Enable

Output

This is an active-LOW signal that drives the  $\overline{\text{WE}}$  pin on the external SDRAM. The L64021 asserts this signal to enable an SDRAM write operation.

### **Video Output Interface**

BLANK Blank

Output

BLANK is a composite blank output from the L64021 display controller. Its polarity is active-HIGH.

CREF Display Controller Output

Output

This display controller output signal serves as a Chroma reference. CREF is HIGH during the Cb component of Chroma.

**EXT OSD[3:0]**

**Palette Selection Bus**

Input

This four-bit input bus selects from the 16 colors in the on-chip color palette for an external OSD function. The EXT\_OSD[3:0] data is sampled at SYSCLK/4 or 6.75 MHz, providing an OSD with a resolution of 352 pixels.

### **HS** Horizontal Sync

Input

HS is the horizontal sync signal, which resets the horizontal counters in the display controller. The horizontal sync signal must be synchronous to SYSCLK.

### **OSD ACTIVE**

### **On-Screen Display**

Output

This is an active-HIGH signal that indicates the on-chip OSD is active. This pin indicates which pixels have mixed OSD in the pixel port. Active output occurs at the pixel containing OSD mixed data.

### PD[7:0] Pixel Data Output Bus

Output

The data on the PD[7:0] bus represents the pixel data of the reconstructed picture. The pixel data is formatted in CCIR601 (Y, Cb, Cr) chromaticity.

### VS Vertical Sync / Odd-Even Field

Input

The host can program the L64021 so that VS is either a conventional Vertical Sync input or an even/odd field indicator. When in the even/odd field indicator mode, the internal display controller counters reset each time VS changes state (at the beginning of each field). The parity of the field is controlled by the timing of VS relative to HS. The odd/even field indicator should be synchronous to SYSCLK.

### **Audio Interface**

### A ACLK Audio Clock

Output

A\_ACLK is an audio output clock that is selected from one of the audio input clocks (ACLK\_32, ACLK\_441, or ACLK\_48).

### ACLK\_32 Audio Clock (32)

Input

This audio clock is 32 kHz \* N, where N equals 768, 512, 384, or 256.

### ACLK 441 Audio Clock (44.1)

Input

This audio clock is 44.1 kHz \* N, where N equals 768, 512, 384, or 256.

### ACLK\_48 Audio Clock (48)

Input

This audio clock is 48 kHz  $^{\ast}$  N, where N equals 768, 512, 384, or 256.

### ASDATA Audio Serial Data Line

Output

ASDATA is the output for serial audio data. The host can program the format for either PCM or I<sup>2</sup>S output mode.

### **AUDIO SYNC**

### **Audio Synchronization**

Output

This signal provides an audio sync indication for use in transport systems that require hardware sync controls. (Typically, this signal is used only in DSS systems.)

#### BCLK Serial DAC Bit Clock

Output

This signal clocks the ASDATA bit into the DAC on BCLK's rising edge. BCLK has a programmable frequency that the host can set during initialization.

### CD ACLK External Audio Clock

Input

This clock provides a reference source for the L64021's audio output stage that is used when the L64021 bypasses CD audio to the DAC output. Typically, the clock rate is either 256 \*  $f_s$  or 384 \*  $f_s$ .

### CD ASDATA Audio Serial Data Line

Input

This signal is the serial audio data input that is used when the L64021 bypasses CD audio to the DAC output.

#### CD BCLK Serial DAC Bit Clock

Input

This signal clocks the ASDATA bit into the L64021 on the clock's rising edge. The L64021 uses this clock when bypassing CD audio to the DAC output.

### CD LRCLK Serial DAC Left/Right Clock

Input

This input clock indicates which samples belong to the left and right stereo channels. The L64021 uses this clock when bypassing CD audio to the DAC output.

### LRCLK Serial DAC Left/Right Clock

Output

This output clock, which has a programmable frequency, indicates which samples belong to the left and right stereo channels.

#### SPDIF IN S/PDIF In

Input

This input signal is S/PDIF (IEC958) formatted data. During CD bypass mode, the L64021 routes the SPDIF\_IN signal directly to the SPDIF\_OUT pin.

### SPDIF OUT S/PDIF Out

Output

This signal, whose frequency is programmable, contains audio data for Linear PCM samples in the IEC958 consumer format. The host can configure the L64021 to provide this signal as either an MPEG Audio or Dolby Digital compressed bitstream.

### Miscellaneous and Test Interfaces

### LP2 PLL Loop Filter

**Bidirectional**

The system uses this pin to connect an external PLL loop filter to the L64021.

### PLLVDD PLL Power Supply Pin

Input

Phase-locked loop dedicated power input pin.

### PLLVSS PLL Ground Pin

Input

Phase-locked loop dedicated ground input pin.

### RESETn Reset

Input

This is an active-LOW input signal. When an external source asserts RESETn, the L64021 resets itself. The minimum RESET pulse width is eight cycles of SYSCLK. SYSCLK must be running during reset.

### SCAN TE Scan Test Enable

Input

When asserted, this signal enables the scan test mode. This mode is used only during manufacturing test. During normal system operation, tie this pin LOW.

### SYSCLK Device Clock

Input

SYSCLK is the L64021's input system clock. The clock has a nominal frequency of 27 MHz. Picture reconstruction and video timing are referenced with respect to this clock.

#### TM[1:0] Test Mode

Input

LSI Logic uses these two pins during manufacturing test. They are not intended for any other purpose. Tie both pins LOW during normal system operation.

### ZTEST Z Test Mode

Input

Z Test mode pin. This signal is used only for manufacturing test. Tie this pin HIGH during normal system operation.

## **Specifications**

This section contains the electrical parameters for the L64021 DVD Decoder. Table 1 lists the absolute maximum ratings. Exceeding these values may cause damage to the L64021. Table 2 defines the recommended operating supply voltage and temperature. Table 3 shows the pin capacitance, and Table 4 lists the DC characteristics.

Table 1 Absolute Maximum Ratings

| Symbol            | Parameter                                | Limits <sup>1</sup> | Units |

|-------------------|------------------------------------------|---------------------|-------|

| V <sub>DD</sub>   | DC Supply                                | -0.3 to +3.9        | V     |

| V <sub>IN</sub>   | 5-V Compatible Input Voltage             | -1.0 to +6.5        | V     |

| I <sub>IN</sub>   | DC Input Current                         | ±10                 | mA    |

| T <sub>STGP</sub> | Storage Temperature Range (PQFP Package) | -40 to +125         | °C    |

<sup>1.</sup> Referenced to V<sub>SS</sub>.

Table 2 Recommended Operating Conditions

| Symbol          | Parameter           | Limits       | Units |

|-----------------|---------------------|--------------|-------|

| V <sub>DD</sub> | DC Supply           | +2.15 to 3.6 | ٧     |

| T <sub>A</sub>  | Ambient Temperature | 0 to +70     | °C    |

Table 3 Capacitance

| Symbol           | Parameter <sup>1</sup> | Min | Units |

|------------------|------------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance      | 2.5 | pF    |

| C <sub>OUT</sub> | Output Capacitance     | 2.0 | pF    |

<sup>1.</sup> Measurement conditions are  $V_{IN}$  = 3.3 V ( $V_{IN}$  = 5.0 V for 5-V tolerant buffers),  $T_A$  = 25  $^{\circ}C,$  and clock frequency = 1 MHz.

Table 4 DC Characteristics

| Symbol             | Parameter                                                                          | Condition <sup>1</sup>                                                  | Min                                  | Тур                 | Max                           | Units          |

|--------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------|---------------------|-------------------------------|----------------|

| V <sub>IL</sub>    | Voltage Input Low<br>TTL<br>CMOS                                                   |                                                                         | _                                    | _                   | 0.8<br>0.2<br>V <sub>DD</sub> | V              |

| V <sub>IH</sub>    | Voltage Input High<br>TTL<br>CMOS<br>5-V Compatible                                |                                                                         | 2.0<br>0.7<br>V <sub>DD</sub><br>2.0 | _                   | <br>5.5                       | V<br>V<br>V    |

| V <sub>OL</sub>    | Voltage Output Low<br>4-mA Output Buffers<br>8-mA Output Buffers                   | I <sub>OL</sub> = 4.0 mA<br>I <sub>OL</sub> = 8.0 mA                    | _                                    | 0.2<br>0.2          | 0.4<br>0.4                    | V              |

| V <sub>OH</sub>    | Voltage Output High<br>4-mA Output Buffers<br>8-mA Output Buffers                  | I <sub>OH</sub> = -4.0 mA<br>I <sub>OH</sub> = -8.0 mA                  | 2.4<br>2.4                           |                     | _                             | V              |

| I <sub>IL</sub>    | Current Input Leakage <sup>2</sup> with Pulldown with Pullup                       | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{IN} = V_{DD}$<br>$V_{IN} = V_{SS}$ | -10<br>35<br>-214                    | ± 10<br>115<br>–115 | 222<br>-35                    | μΑ<br>μΑ<br>μΑ |

| I <sub>OZ</sub>    | Current 3-State Output<br>Leakage                                                  | $V_{DD} = Max, V_{OUT} = V_{SS} or$                                     | -10                                  | ± 1                 | + 10                          | μΑ             |

| I <sub>OSP</sub> 4 | Current P-Channel Output<br>Short Circuit (4-mA<br>Output Buffers) <sup>3, 4</sup> | $V_{DD} = Max, V_{OUT} = V_{SS}$                                        | -117                                 | -75                 | -40                           | mA             |

| I <sub>OSN</sub> 4 | Current N-Channel Output<br>Short Circuit (4-mA<br>Output Buffers) <sup>3, 4</sup> | $V_{DD} = Max, V_{OUT} = V_{DD}$                                        | 37                                   | 90                  | 140                           | mA             |

| I <sub>DD</sub>    | Quiescent Supply Current                                                           | $V_{IN} = V_{DD}$ or $V_{SS}$                                           | _                                    | 10                  | _                             | mA             |

| I <sub>CC</sub>    | Dynamic Supply Current                                                             | V <sub>DD</sub> = Max, f = 27 MHz                                       | _                                    | 330                 | _                             | mA             |

<sup>1.</sup> Specified at  $V_{DD}$  equals 3.3 V  $\pm$  5% at ambient temperature over the specified range. 2. For CMOS and TLL inputs.

<sup>3.</sup> Not more than one output may be shorted at a time for a maximum duration of one second.

<sup>4.</sup> These values scale proportionally for output buffers with different drive strengths.

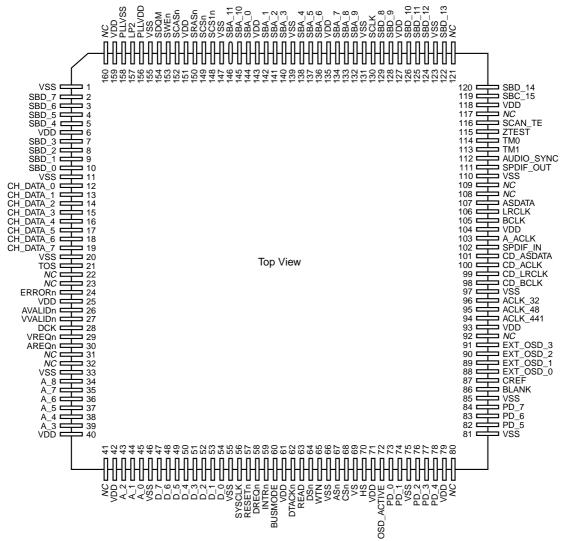

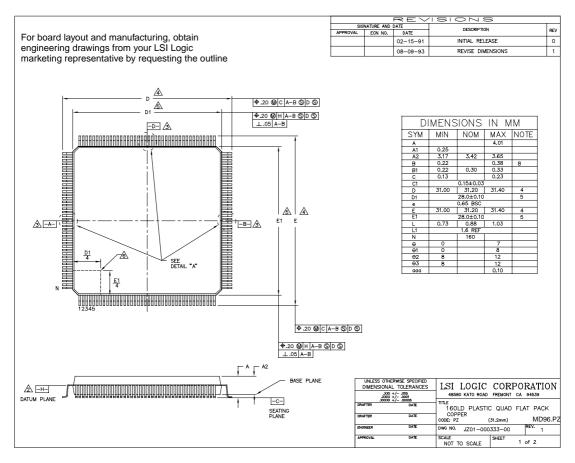

# Pinout, Package, and Ordering Information

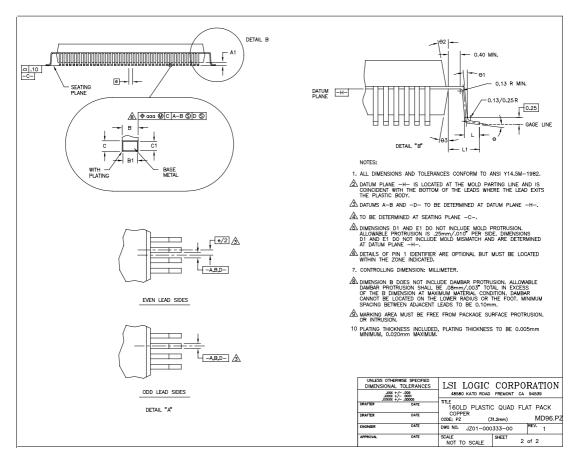

The L64021 is available in a 160-lead Plastic Quad Flat Package (PQFP). Table 5 provides the L64021 order number. Figure 4 supplies the L64021 DVD Decoder pinout diagram; Figure 5 and Figure 6 contain the package mechanical drawings.

Table 5 L64021 Ordering Information

| Order Number | Clock<br>Frequency | Package Type  | Operating Range |

|--------------|--------------------|---------------|-----------------|

| 65032A1      | 27 MHz             | 160-lead PQFP | Commercial      |

Figure 4 L64021 160-Lead PQFP Pinout Diagram

1. NC pins are not connected.

Figure 5 L64021 160-Lead PQFP Mechanical Drawing (Sheet 1 of 2)

Figure 6 L64021 160-Lead PQFP Mechanical Drawing (Sheet 2 of 2)

## **Notes**

## **Notes**

**LSI Logic Corporation Corporate Headquarters** Tel: 408.433.8000

Fax: 408.433.8989

#### NORTH AMERICA

#### California

Irvine

♦ Tel: 714.553.5600 Fax: 714.474.8101

> San Diego Tel: 619.635.1300 Fax: 619.635.1350 Silicon Valley

> Sales Office Tel: 408.433.8000 Fax: 408.954.3353 Design Center

Tel: 408.433.8000 Fax: 408.433.7695

#### Colorado

Roulder

Tel: 303.447.3800 Fax: 303.541.0641

Florida Boca Raton Tel: 561.989.3236 Fax: 561.989.3237

Illinois Schaumburg

♦ Tel: 847.995.1600 Fax: 847.995.1622

> Kentucky **Bowling Green** Tel: 502.793.0010

Fax: 502.793.0040 Maryland

Bethesda Tel: 301.897.5800 Fax: 301.897.8389

#### Massachusetts Waltham

Tel: 617.890.0180 Fax: 617.890.6158

### Minnesota

Minneapolis ◆ Tel: 612.921.8300 Fax: 612.921.8399

**New Jersey** Edison

◆ Tel: 908.549.4500 Fax: 908.549.4802

New York New York Tel: 716.223.8820 Fax: 716.223.8822

**North Carolina**

Raleigh Tel: 919.783.8833 Fax: 919.783.8909

Oregon Beaverton Tel: 503.645.0589 Fax: 503.645.6612

Tevas Austin Tel: 512.388.7294 Fax: 512 388 4171

Dallas Tel: 972.788.2966 Fax: 972.233.9234

Houston Tel: 281.379.7800 Fax: 281.379.7818

Washington Issaguah Tel: 425.837.1733 Fax: 425.837.1734

Canada Ontario Ottawa

Tel: 613.592.1263 Fax: 613.592.3253

Toronto

Tel: 416.620.7400 Fax: 416.620.5005

Quebec Montreal

Tel: 514.694.2417 Fax: 514.694.2699

#### INTERNATIONAL

**Australia** Reptechnic Pty Ltd **New South Wales**

Tel: 612.9953.9844 Fax: 612.9953.9683

Denmark **LSI Logic Development**  Centre

Ballerup Tel: 45.44.86.55.55 Fax: 45.44.86.55.56

France LSI Logic S.A. Paris

♦ Tel: 33.1.34.63.13.13 Fax: 33.1.34.63.13.19

Germany LSI Logic GmbH Munich

◆ Tel: 49.89.4.58.33.0 Fax: 49.89.4.58.33.108

Stuttgart Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

Hong Kong **AVT Industrial Ltd** Hong Kong Tel: 852.2428.0008 Fax: 852.2401.2105

LogiCAD India Private Ltd Bangalore

Tel: 91.80.526.2500 Fax: 91.80.338.6591

Israel LSI Logic

Ramat Hasharon ♦ Tel: 972.3.5.403741 Fax: 972.3.5.403747 Netanya

♦ Tel: 972.9.657190 Fax: 972.9.657194

LSI Logic S.P.A. Milano

Tel: 39.39.687371 Fax: 39.39.6057867

Japan LSI Logic K.K. Tokyo

◆ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

Osaka Tel: 81.6.947.5281 Fax: 81.6.947.5287

Korea LSI Logic Korea Inc. Seoul

Tel: 82.2.528.3400 Fax: 82.2.528.2250

Singapore LSI Logic Pte Ltd Singapore

♦ Tel: 65.334.9061 Fax: 65.334.4749

Spain LSI Logic S.A. Madrid

♦ Tel: 34.1.556.07.09 Fax: 34 1 556 75 65

Sweden LSI Logic AB Stockholm

◆ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

> Switzerland LSI Logic Sulzer AG Brugg/Biel

Tel: 41.32.536363 Fax: 41.32.536367

Taiwan LSI Logic Asia-Pacific Taipei

Tel: 886.2.718.7828 Fax: 886.2.718.8869

> Cheng Fong Technology Corporation Tel: 886.2.910.1180 Fax: 886.2.910.1175

**Lumax International** Corporation, Ltd Tel: 886.2.788.3656

Fax: 886.2.788.3568 Macro-Vision Technology Inc.

Tel: 886.2.698.3350 Fax: 886.2.698.3348 **United Kinadom**

LSI Logic Europe Ltd Bracknell ◆ Tel: 44.1344.426544 Fax: 44.1344.481039

♦ Sales Offices with **Design Resource Centers**

To receive product literature, call us at 1-800-574-4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com

### ISO 9000 Certified

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified the functional descriptions or electrical and mechanical specifications using production

Printed in USA Order No. 115028 Doc. No. DB08-000073-00 parts.

LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.