# LXT332 Redundancy Applications

**Application Note**

January 2001

Order Number: 249170-001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT332 Redundancy Applications may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| Intro            | oduction                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1              | General Description        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | ·                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.3              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.4              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | 1.4.2 Transmit Return Loss |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | 1.4.3 Test Conditions      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1<br>2<br>3<br>4 | LXT332 Block Diagram       | 8<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 2              | Receive Return Loss        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | 1.1<br>1.2<br>1.3<br>1.4   | 1.2 Circuit Description 1.2.1 Driver Tri-state Mode 1.2.2 Receive Circuit 1.2.3 Transmit Circuit 1.3 Transceiver Pulse Pictures 1.4 Return Loss 1.4.1 Receive Return Loss 1.4.2 Transmit Return Loss 1.4.3 Test Conditions  1 LXT332 Block Diagram 2 T1 at 133' With and Without Redundant Transceiver 3 T1 at 655' With and Without Redundant Transceiver 4 E1, 75 W With and Without Redundant Transceiver 5 E1, 120 W With and Without Redundant Transceiver 1 Receive Return Loss |

# 1.0 Introduction

The primary concern in most high speed data networks is reliability. Redundancy is one way to protect and ensure reliability in the event of catastrophic failure.

At low data rates, redundancy may not make sense, but as the number of lower data ports are multiplexed to the higher bit streams, it begins to play a major role. Because of this, most major network multiplexers and bandwidth managers use redundancy techniques to ensure data integrity.

The Intel LXT332 transceiver offers an unique tri-state function that allows the sharing of a single trunk for redundancy purposes.

This application note provides some guidelines for implementing redundancy systems both for T1 and E1 operation.

Note: This application note is not intended for designs that require error free switching.

# 1.1 General Description

Below is a block diagram showing two LXT332 transceivers with one used as a redundancy circuit. The redundant transceiver is tri-stated while the working transceiver carries the traffic.

The transceivers are connected at the secondary side of the transformers to provide DC isolation. This configuration was also tested with the redundant transceiver powered-down.

PRIMARY TRANSCEIVER T D1 R1 D2 TVcc D3 TCLK1 C1 TRANSMIT TVcc1 D3 R2 ₽ D4 T2 R3 **SWITCHING** R9 RECEIVE CONTROL CIRCUIT TGND1 TCLK TVcc2 D5 R5 TTIE D6 CONTRO TVcc2 D7 R6 D8 R7 TVCC2 VCC2 SECONDARY

Figure 1. LXT332 Block Diagram

# 1.2 Circuit Description

TRANSCEIVER

The LXT332 allows two transceiver output drivers to be tied together on the secondary side of the transformer. This is allowable if one driver is in a high impedance state (tri-state).

#### 1.2.1 Driver Tri-state Mode

To configure the transceiver for this option, simply remove TCLK of the driver that needs to be tristated. A TCLK monitor internal to the transceiver senses the absence of TCLK and then activates the tri-state mode for that driver. While in the tri-state mode the output driver enters a high impedance state which will have no adverse effects on the pulse shape of the operating driver.

#### 1.2.2 Receive Circuit

The transceiver's receive circuit uses a single terminating resistor R9. Because of the internal high impedance of the receive circuit, reflections are minimized and high return loss capabilities are maintained.

Resistors R3, R4, R7, and R8 limit current into the receivers under a single device power down condition. The value of these resistors is  $1k\Omega$ , which will help to isolate the powered down device and prevent it from loading the live transceiver's received data.

#### 1.2.3 Transmit Circuit

The transceiver's transmit circuit must ensure that the current into the TTIP/TRING pins is minimized. The use of series resistors R1, R2 and R5, R6 is thus essential in this type of configuration, and is required if the redundant transceiver is powered down. The purpose of capacitors C1 and C2 is to block the DC component from saturating the transformer. Additional protection against excessive surge currents is provided by including Schottky diodes D1-D8. In this case, a TVS, bi-directional 5V transient voltage suppressor, is needed to clamp surges coupled onto the power supply by the Schottky diodes (TVS1 and TVS2).

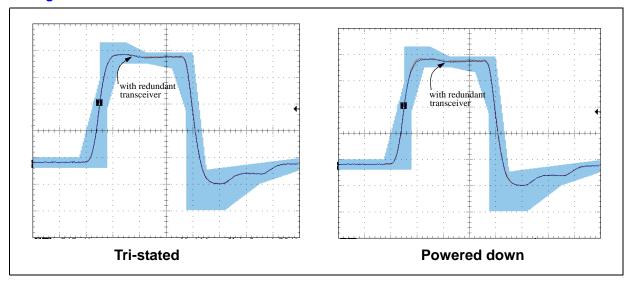

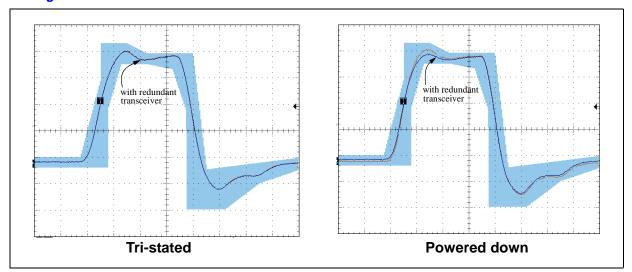

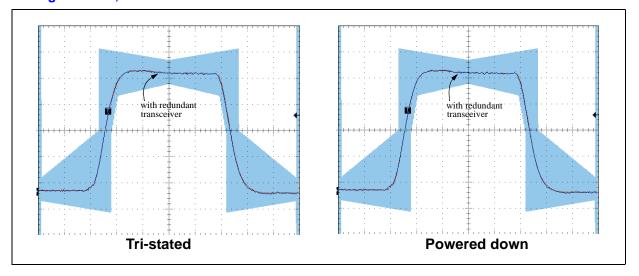

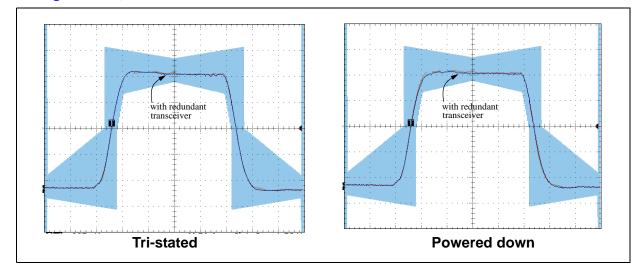

### 1.3 Transceiver Pulse Pictures

This configuration was tested for both E1  $(75\Omega$  and  $120\Omega)$  and T1 operation. The tests were performed using two separate LXT332 demo boards. The cable connections between the two demo board transmitters were kept at less than 6 inches in order to minimize reflections. Figure 2 through Figure 5 show the pulse shapes obtained with and without the redundant circuit in both a tri-state mode and also under a power-down condition. Note that the difference in the pulse shapes, with and without the redundant transceiver, is nearly indistinguishable.

Figure 2. T1 at 133' With and Without Redundant Transceiver

Figure 3. T1 at 655' With and Without Redundant Transceiver

Figure 4. E1, 75  $\Omega$  With and Without Redundant Transceiver

Figure 5. E1, 120  $\Omega$  With and Without Redundant Transceiver

#### 1.4 Return Loss

Return loss is an important factor to consider when designing redundancy systems. For E1 operation, recommendation G.703 and ETSI 300 166 clearly define the minimum return loss to be achieved both at the input and output ports.

#### 1.4.1 Receive Return Loss

Table 1 shows the minimum limits imposed by G.703 and typical values obtained with the LXT332 using the configuration described before (redundant board powered off). The receive transformers used in this configuration should have a minimum primary inductance of 2mH. The transformer inductance is the main factor determining the receive return loss at low frequencies. By using two transformers in parallel on the receive side, the total inductance is reduced to 1mH. This value should be kept as a minimum in order to meet G.703 low frequency band requirements with a comfortable margin.

#### 1.4.2 Transmit Return Loss

Table 2 contains the transmit return loss measured using the same configuration against ETSI, ETS 300 166.

**Table 1. Receive Return Loss**

| Config                                    | Frequency Band (kHz) |            |             |

|-------------------------------------------|----------------------|------------|-------------|

| Comig                                     | 50 -102              | 102 - 2048 | 2048 - 3072 |

| G.703<br>minimum                          | 12 dB                | 18 dB      | 14 dB       |

| LXT332<br>E1, 120 Ω<br>with<br>redundancy | 19.6 dB              | 19.3 dB    | 16.0 dB     |

**Table 2. Transmit Return Loss**

| Config                                    | Frequency Band (kHz) |            |             |

|-------------------------------------------|----------------------|------------|-------------|

| Comig                                     | 50 -102              | 102 - 2048 | 2048 - 3072 |

| ETS 300166<br>minimum                     | 6 dB                 | 8 dB       | 8 dB        |

| LXT332<br>E1, 120 Ω<br>with<br>redundancy | 12.8 dB              | 12.5 dB    | 12.1 dB     |

**Table 3. Component Specifications**

| Component      | Description                                                                                                                    | Manufacturer            | Part Number |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|

| T1, T2         | transformer, 1:2 CT + 1:2 CT                                                                                                   | Pulse Engineering       | PE64953     |

| T3, T4         | transformer, 1:2 CT + 1:2 CT                                                                                                   | Pulse Engineering       | PE64953     |

| D1 - D4        | Schottky diode                                                                                                                 | International Rectifier | 11DQ04      |

| TVS1, TVS2     | bi-directional TVS                                                                                                             | Semtech                 | SMCJ5.0AC   |

| R1, R2, R5, R6 | resistor, 9.1 Ω, 1%                                                                                                            |                         |             |

| R3, R4, R7, R8 | resistor, 1k Ω, 5%                                                                                                             |                         |             |

| R9             | <b>T1</b> = 100 Ω, 5% resistor<br><b>E1</b> , <b>75</b> Ω = 75 Ω, 5% resistor<br><b>E1</b> , <b>120</b> Ω = 120 Ω, 5% resistor |                         |             |

| C1, C2         | capacitor, 0.47 μF                                                                                                             |                         |             |

| C3, C5         | capacitor, 68 μF                                                                                                               |                         |             |

| C4, C6         | capacitor, 0.1μF                                                                                                               |                         |             |

## 1.4.3 Test Conditions

- All pulse pictures were taken at ambient temperature

- DC Supply voltage = +5.00V

- A Mountain Engineering Line simulator was used from 0-655'

- Intel demonstration boards were used to configure a redundancy system