### **LXP730**

#### Multi-Rate DSL Framer

#### **Datasheet**

The LXP730 is a multi-purpose Digital Subscriber Line (DSL) framer which complements the Level One SK70725/21 Enhanced MDSL Data Pump (EMDP) to provide seamless transport of data and voice signals over one or more DSL datapaths.

### **Applications**

The LXP730 in combination with the EMDP chipset is optimized for use as a framer or I/O interface device for the following applications:

- Digital Pair Gain Systems

- Ethernet Modems

- T1/E1 Fractional Transport Systems

- Videoconferencing Systems

- Simultaneous Data Voice Transport Systems

- Wireless Base Station Access Systems

#### **Product Features**

The LXP730 provides the basic functions required of a DSL framer:

- Synchronization of external data streams to the DSL line

- Multiplexing and demultiplexing of independent data streams for voice and data

- Loopback of payload data at the DSL interface

- Creation, insertion, and recovery of the MDSL Overhead (MOH) structure, performance monitoring, and message transport required in a DSL system with a capacity of up to 32 kbps

- Supports two input/output data streams simultaneously

- —Slave mode: external clock determines the rate at which data will be transferred to and from the framer

- Master mode: clock derived from received DSL clock or external oscillator

- Single part architecture allows one chip to be used economically in both central and remote locations

- Supports systems with point-to-point architectures

- Alternate Hardware Control mode (HWC) for operation without an external microprocessor

Order Number: 249266-001

January 2001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXP730 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Pin / | Assignments and Signal Descriptions                          | 10 |

|-----|-------|--------------------------------------------------------------|----|

| 2.0 | Fund  | ctional Description                                          | 14 |

|     | 2.1   | LXP730 Nx64 Framer                                           | 14 |

|     | 2.2   | Time Slot Interchange (TSI)                                  | 14 |

|     | 2.3   | PCM-Bus Interface                                            | 15 |

|     | 2.4   | Codec Interface                                              | 16 |

|     | 2.5   | T1/E1 Interface                                              |    |

|     | 2.6   | Asynchronous Data Port Interface (ADPI)                      |    |

|     | 2.7   | Overhead Interface                                           |    |

|     |       | 2.7.1 Overhead Serial I/O (OSIO)                             |    |

|     |       | 2.7.2 MDSL Overhead Μιχροπροχεσσορ Interface                 |    |

|     | 2.8   | MDSL Interface                                               |    |

|     | 2.9   | All Digital PLL (ADPLL)                                      |    |

|     |       | 2.9.1 ADPLL Performance: The Selection of Kloop              |    |

|     |       | 2.9.2 ADPLL Center Frequency: The computation of CFREQ       |    |

|     | 2.10  | Clock Generation and Distribution                            |    |

|     | 2.11  | Modes of Operation                                           |    |

|     |       | 2.11.1 Microprocessor Control (MPC) Mode                     |    |

|     | 0.40  | 2.11.2 Hardware Control (HWC) Mode                           |    |

|     | 2.12  | MDSL Overhead Definition                                     |    |

|     |       | 2.12.1 Predefined Overhead                                   |    |

|     | 2.13  | MDSL Frame Format                                            |    |

|     | 2.13  | Startup Operation                                            |    |

|     | 2.14  | Activation State Machine                                     |    |

| 0.0 |       |                                                              |    |

| 3.0 | • •   | lication Information                                         |    |

|     | 3.1   | Typical Applications                                         |    |

|     |       | 3.1.1 IOM Interface Circuitry                                |    |

|     |       | 3.1.2 Handling TIP/RING Reversal in Early Version of SK70725 |    |

|     |       | 3.1.3 DSL System Loopbacks                                   |    |

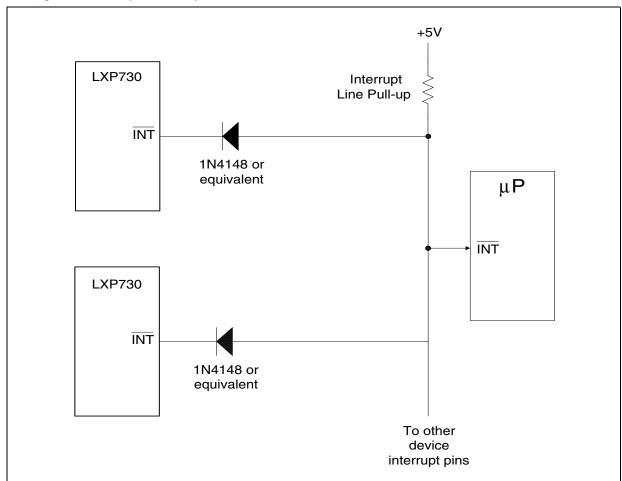

|     |       | 3.1.4 Using Multiple Devices on an Interrupt Line            |    |

| 4.0 | Test  | Specifications                                               | 33 |

| 5.0 | Regi  | ster Definitions                                             | 47 |

|     | 5.1   | Number MDSL Channels Register                                | 48 |

|     | 5.2   | MDSL Channel Configuration Registers (18 bytes)              | 49 |

|     |       | 5.2.1 Channel 1                                              |    |

|     |       | 5.2.2 Channel 2                                              | 49 |

|     |       | 5.2.3 Channel 3                                              | 49 |

|     |       | 5.2.4 Channel 4                                              |    |

|     |       | 5.2.5 Channel 5                                              | 50 |

|     |       | 5.2.6 Channel 6                                              |    |

|     |       | 5.2.7 Channel 7                                              | _  |

|     |       | 5.2.8 Channel 8                                              | 51 |

|      | 5.2.9    | Channel 9                         | .51  |

|------|----------|-----------------------------------|------|

|      | 5.2.10   | Channel 10                        | . 52 |

|      | 5.2.11   | Channel 11                        | . 52 |

|      | 5.2.12   | Channel 12                        | . 52 |

|      | 5.2.13   | Channel 13                        | . 53 |

|      | 5.2.14   | Channel 14                        | . 53 |

|      | 5.2.15   | Channel 15                        | . 53 |

|      | 5.2.16   | Channel 16                        | . 54 |

|      | 5.2.17   | Channel 17                        | . 54 |

|      | 5.2.18   | Channel 18                        | . 54 |

| 5.3  | Reserve  | ed Registers (3 bytes)            | . 55 |

| 5.4  | Wande    | r Reduction Register              | . 55 |

| 5.5  | FIFO/M   | liscellaneous Control Register    | . 55 |

| 5.6  | Slip But | ffer Lower Threshold Register     | . 56 |

| 5.7  | Slip But | ffer Upper Threshold Register     | . 57 |

| 5.8  | Version  | n Register                        | . 57 |

| 5.9  | Internal | Clock Control Registers (4 bytes) | . 57 |

|      | 5.9.1    | ADPLL Control 1                   | . 57 |

|      | 5.9.2    | ADPLL Control 2                   | . 58 |

|      | 5.9.3    | ADPLL Control 3                   | . 58 |

|      | 5.9.4    | MCLK Divide                       | . 58 |

| 5.10 | Prograr  | mmable Idle Code Byte             | . 58 |

| 5.11 | PCM C    | onfiguration Registers            | . 59 |

|      | 5.11.1   | PCM1 Configuration                | . 59 |

|      | 5.11.2   | PCM2 Configuration                | . 59 |

| 5.12 | Codec    | Configuration Register            | . 60 |

| 5.13 | Overhe   | ad Registers (25 bytes)           | . 60 |

|      |          | Miscellaneous Control             |      |

|      | 5.13.2   | Overhead Configuration            | .61  |

|      | 5.13.3   | CRC Error Counter                 | .61  |

|      | 5.13.4   | FEBE Error Counter                | .62  |

|      | 5.13.5   | CRC - FEBE - LOS Status           | . 62 |

|      | 5.13.6   | MX Overhead Bits 1 - 8            | . 62 |

|      | 5.13.7   | MX Overhead Bits 9 - 16           | . 63 |

|      | 5.13.8   | MX Overhead Bits 17 - 24          | . 63 |

|      | 5.13.9   | MX Overhead Bits 25 - 32          | . 63 |

|      | 5.13.10  | MX Z Bits 1 - 8                   | . 64 |

|      | 5.13.11  | MX Z Bits 9 - 16                  | .64  |

|      | 5.13.12  | MX Z Bits 17 - 24                 | .64  |

|      | 5.13.13  | MX Z Bits 25 - 32                 | .65  |

|      | 5.13.14  | MX Z Bits 33 - 40                 | .65  |

|      | 5.13.15  | MX Z Bits 41 - 48                 | .65  |

|      | 5.13.16  | DX Overhead Bits 1 - 8            | .65  |

|      |          | DX Overhead Bits 9 - 16           |      |

|      |          | DX Overhead Bits 17 - 24          |      |

|      |          | DX Overhead Bits 25 - 32          |      |

|      |          | DX Z Bits 1 - 8                   |      |

|      |          | DX Z Bits 9 - 16                  |      |

|      |          | DX Z Bits 17 - 24                 |      |

|      |          | DX Z Bits 25 - 32                 |      |

|      |          |                                   |      |

|                |      | 5.13.24 DX Z Bits 33 - 40<br>5.13.25 DX Z Bits 41 - 48 |    |

|----------------|------|--------------------------------------------------------|----|

|                | 5.14 | Reserved Registers (2 bytes)                           |    |

|                | 5.15 | Interrupt Registers (2 bytes)                          |    |

|                |      | 5.15.1 Interrupt Enables                               |    |

|                |      | 5.15.2 Interrupt Status                                | 69 |

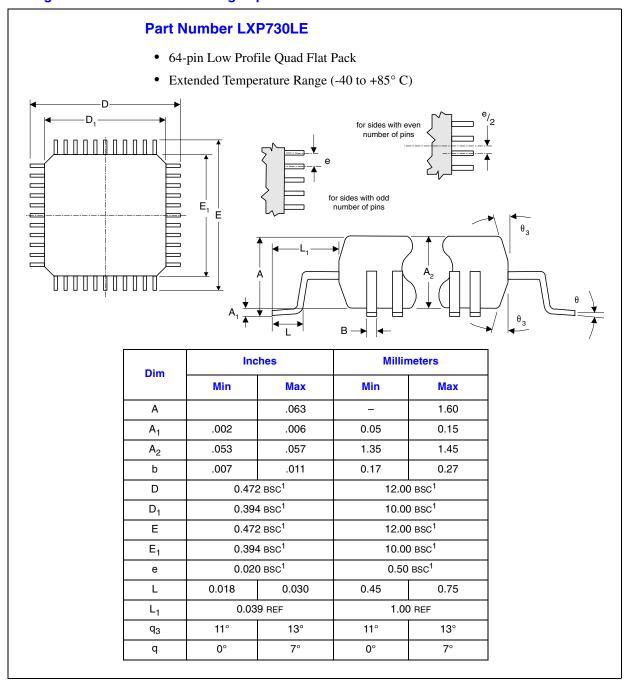

| 6.0            | Mech | nanical Specifications                                 | 70 |

|                |      |                                                        |    |

| <b>Figures</b> |      |                                                        |    |

|                | 1    | LXP730 Block Diagram                                   | 9  |

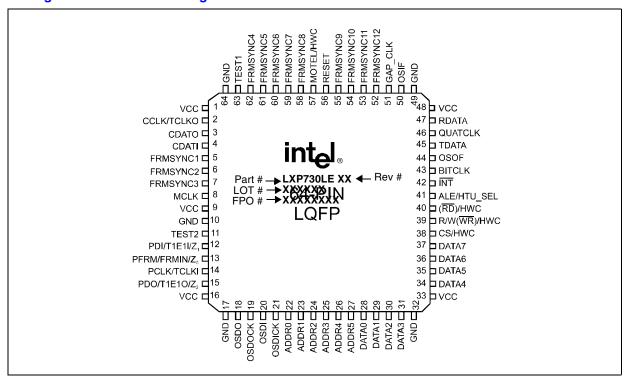

|                | 2    | LXP730 Pin Assignments                                 | 10 |

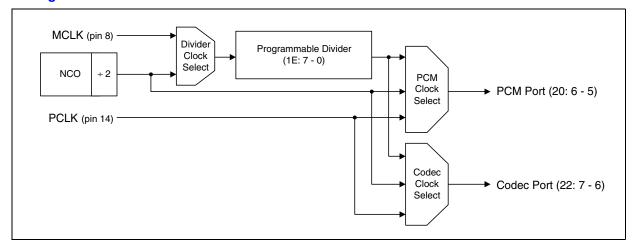

|                | 3    | Clock Generation and Distribution                      | 22 |

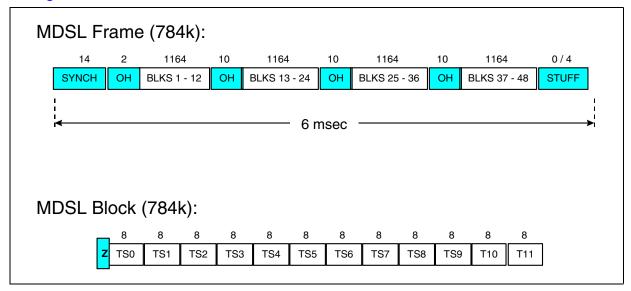

|                | 4    | Frame Format for N=12                                  | 26 |

|                | 5    | Activation State Machine                               | 27 |

|                | 6    | High Performance Voice/Data Transport                  | 28 |

|                | 7    | Pair Gain Transport                                    | 29 |

|                | 8    | T1/E1 Fractional Transport                             | 29 |

|                | 9    | IOM Adaption Circuitry                                 | 30 |

|                | 10   | Multiple Interrupt Line Circuit                        |    |

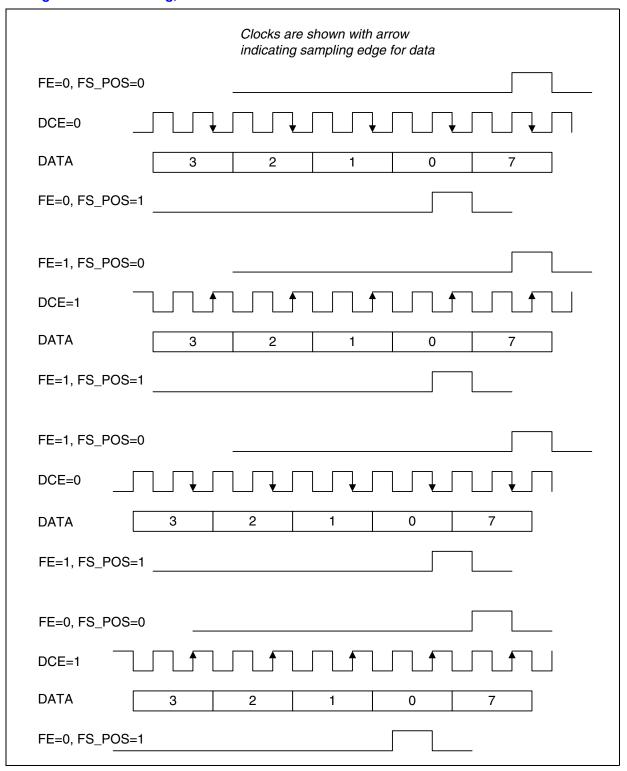

|                | 11   | Generic PCM Interface Timing                           |    |

|                | 12   | PCM Timing, 1X Clock                                   | 35 |

|                | 13   | PCM Timing, 2X Clock                                   | 36 |

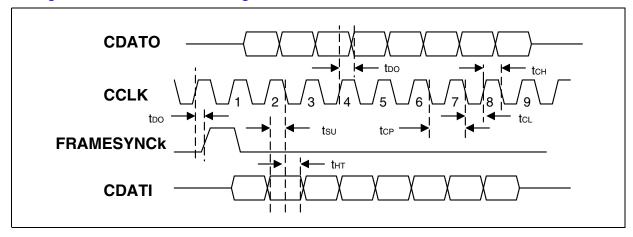

|                | 14   | Codec Interface Timing                                 | 37 |

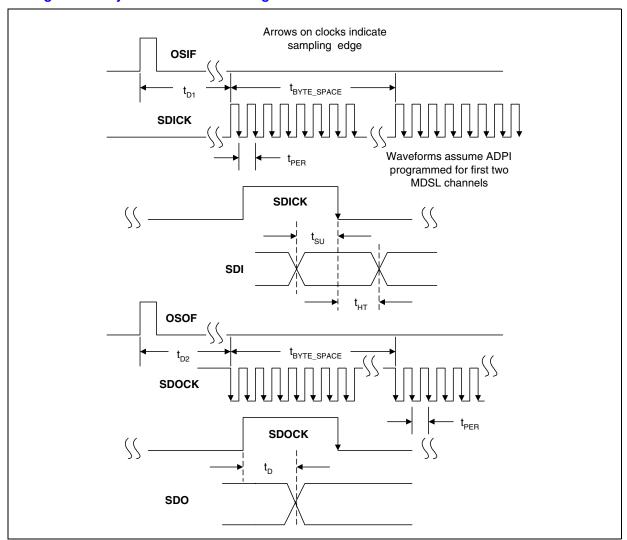

|                | 15   | Asynchronous Port Timing                               | 38 |

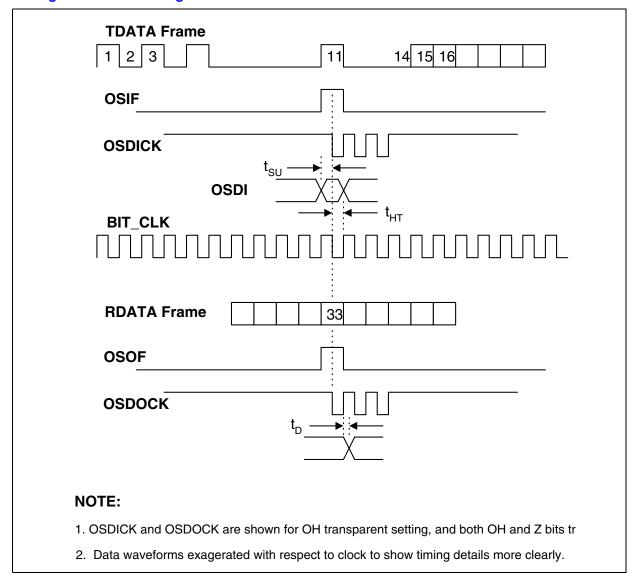

|                | 16   | OSIO Timing                                            | 39 |

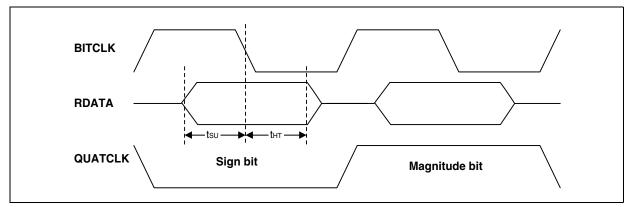

|                | 17   | MDSL Interface Input Timing                            | 40 |

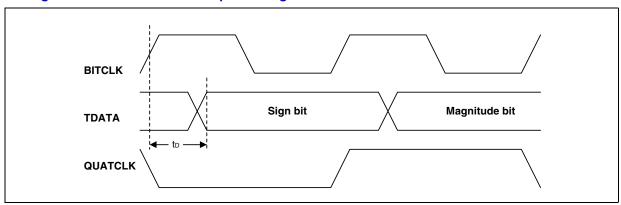

|                | 18   | MDSL Interface Output Timing                           | 40 |

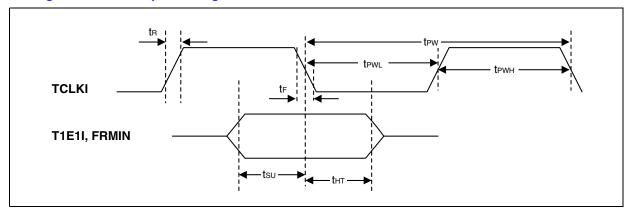

|                | 19   | E1/T1 Input Timing                                     | 41 |

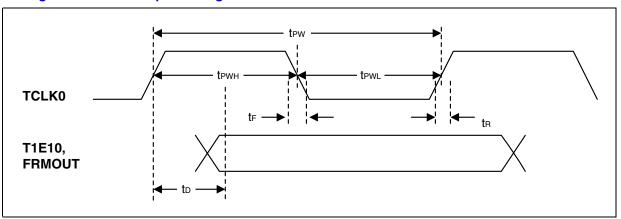

|                | 20   | E1/T1 Output Timing                                    | 41 |

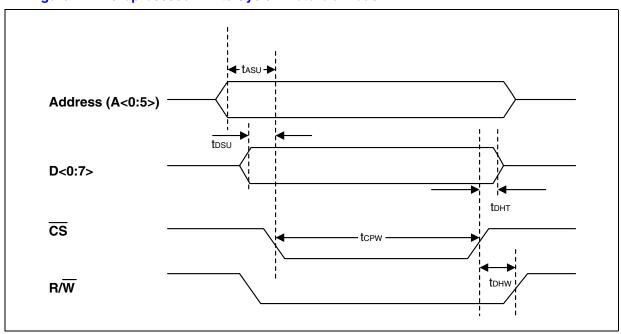

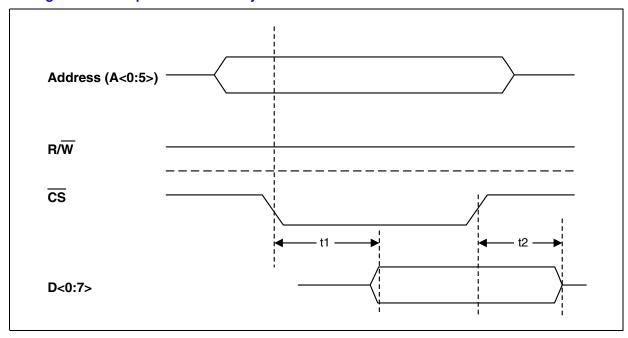

|                | 21   | Microprocessor Write Cycle - Motorola Mode             | 42 |

|                | 22   | Microprocessor Read Cycle - Motorola Mode              | 43 |

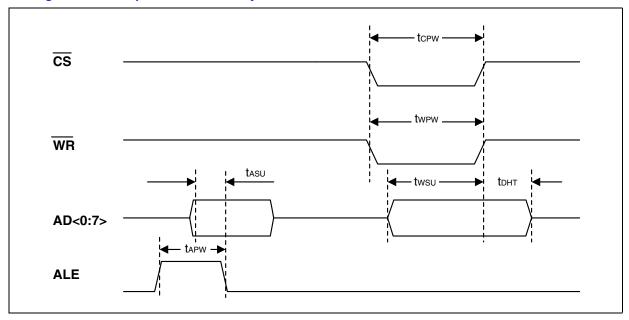

|                | 23   | Microprocessor Write Cycle - Intel Mode                |    |

|                | 24   | Microprocessor Read Cycle - Intel Mode                 | 45 |

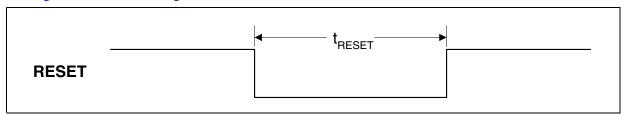

|                | 25   | Reset Timing                                           |    |

|                | 26   | 64 - Pin LQFP Package Specification                    | 70 |

## **Tables**

| 1        | LXP730 Pin Descriptions                                                  | 11       |

|----------|--------------------------------------------------------------------------|----------|

| 2        | Common Transport & Line Rates                                            | 19       |

| 3        | Kloop Values                                                             | 20       |

| 4        | Typical ADPLL Register Settings, MCLK = 16.384MHz                        | 22       |

| 5        | Pin settings for HWC DSL Line Rates                                      | 23       |

| 6        | MDSL Frame Sync Word (FSW) Patterns                                      | . 25     |

| 7        | MDSL Frame Format                                                        |          |

| 8        | Absolute Maximum Ratings                                                 |          |

| 9        | Recommended Operating Conditions                                         |          |

| 10       | I/O Electrical Characteristics                                           |          |

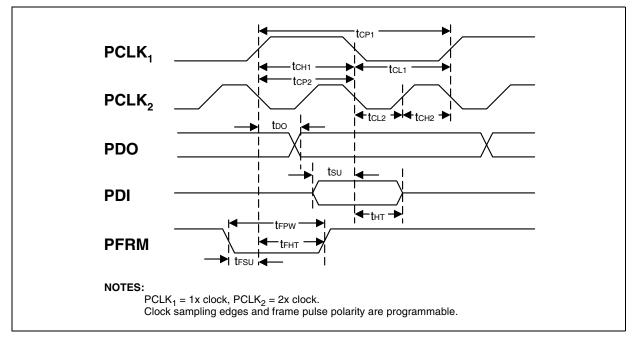

| 11       | Generic PCM Bus Interface Timing Specifications (See Figure 11)          | 34       |

| 12       | Codec Interface Timing Specifications (See Figure 14)                    |          |

| 13       | Asynchronous Port Timing Specifications (See Figure 15)                  |          |

| 14       | OSIO Timing Specifications (See Figure 16)                               |          |

| 15       | MDSL Interface Input Timing Specifications (See Figure 17)               |          |

| 16       | MDSL Interface Output Timing Specifications (See Figure 18)              | . 40     |

| 17       | E1/T1 Input Timing Specifications (See Figure 19)                        |          |

| 18       | E1/T1 Output Timing Specifications (See Figure 20)                       | .42      |

| 19       | Microprocessor Write Cycle Specifications—Motorola Mode (See Figure 21)  |          |

| 20       | Microprocessor Read Cycle Specifications - Motorola Mode (See Figure 22) |          |

| 21       | Microprocessor Write Cycle Specifications—Intel Mode (See Figure 23)     |          |

| 22       | Microprocessor Read Cycle Specifications—Intel Mode (See Figure 24)      |          |

| 23       | MCLK Frequency and Tolerance Specification                               |          |

| 24       | Reset Timing Specifications (See Figure 25)                              |          |

| 25       | LXP730 Register Summary                                                  |          |

| 26       | Number MDSL Channels                                                     |          |

| 27       | Timeslot to Channel 1                                                    |          |

| 28       | Timeslot to Channel 2                                                    |          |

| 29       | Timeslot to Channel 3                                                    |          |

| 30       | Timeslot to Channel 4                                                    |          |

| 31       | Timeslot to Channel 5                                                    |          |

| 32       | Timeslot to Channel 6                                                    |          |

| 33       | Timeslot to Channel 7                                                    |          |

| 34       | Timeslot to Channel 8                                                    |          |

| 35       | Timeslot to Channel 9                                                    |          |

| 36       | Timeslot to Channel 10                                                   |          |

| 37       | Timeslot to Channel 11                                                   |          |

| 38       | Timeslot to Channel 12                                                   |          |

| 39       | Timeslot to Channel 13                                                   |          |

| 40       | Timeslot to Channel 14                                                   |          |

| 41       | Timeslot to Channel 15                                                   |          |

| 42       | Timeslot to Channel 16                                                   |          |

| 43       | Timeslot to Channel 17                                                   |          |

| 44       | Timeslot to Channel 18                                                   |          |

| 45       | Reserved Registers                                                       |          |

| 46       | Wander Reduction Register                                                |          |

| 40<br>47 | FIFO/Miscellaneous Control Register                                      |          |

| 48       | Slip Buffer Lower Threshold                                              |          |

| 40<br>40 | Slip Buffer Upper Threshold                                              | 50<br>57 |

#### Multi-Rate DSL Framer — LXP730

| 50 | Version                     | 57 |

|----|-----------------------------|----|

| 51 | ADPLL Control 1             | 57 |

| 52 | ADPLL Control 2             | 58 |

| 53 | PROG Divide                 | 58 |

| 54 | Programmable Idle Code Byte | 59 |

| 55 | PCM 1 Configuration Bits    | 59 |

| 56 | PCM 2 Configuration Bits    | 60 |

| 57 | Codec Configuration         | 60 |

| 58 | Miscellaneous Control       | 60 |

| 59 | Overhead Configuration      | 61 |

| 60 | CRC Error Counter           | 62 |

| 61 | FEBE Error Counter          |    |

| 62 | CRC - FEBE Status           |    |

| 63 | MX Overhead Bits 1 - 8      |    |

| 64 | MX Overhead Bits 9 - 16     |    |

| 65 | MX Overhead Bits 17 - 24    |    |

| 66 | MX Overhead Bits 25 - 32    |    |

| 67 | MX Z Bits 1 - 8             |    |

| 68 | MX Z Bits 9 - 16            |    |

| 69 | MX Z Bits 17 - 24           |    |

| 70 | MX Z Bits 25 - 32           |    |

| 71 | MX Z Bits 33 - 40           |    |

| 72 | MX Z Bits 41 - 48           |    |

| 73 | DX Overhead Bits 1 - 8      |    |

| 74 | DX Overhead Bits 9 - 16     |    |

| 75 | DX Overhead Bits 17 - 24    |    |

| 76 | DX Overhead Bits 25 - 32    |    |

| 77 | DX Z Bits 1 - 8             |    |

| 78 | DX Z Bits 9 - 16            |    |

| 79 | DX Z Bits 17 - 24           |    |

| 80 | DX Z Bits 25 - 32           |    |

| 81 | DX Z Bits 33 - 40           |    |

| 82 | DX Z Bits 41 - 48           |    |

| 83 | Reserved Registers          |    |

| 84 | Interrupt Enables           |    |

| 85 | Interrupt Status            | 69 |

# **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

MX Elastic MOH MX PCM-Bus Store Slip Interface Buffer MDSL Time Slot Stuff Interface Codec Interchange Interface (TSI) DX Elastic MOH DX Shared Async Store Data Port Interface (ADPI) Recovered Clock All Digital PLL Receive (ADPLL) Registers Framer Overhead Serial I/O (OSIO) Interface Microprocessor Clock Generation and Distribution Interface

Figure 1. LXP730 Block Diagram

### 1.0 Pin Assignments and Signal Descriptions

Figure 2. LXP730 Pin Assignments

| Package Topside Markings |                                                                                                                       |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Marking Definition       |                                                                                                                       |  |  |  |

| Part #                   | Unique identifier for this product family.                                                                            |  |  |  |

| Rev #                    | Identifies the particular silicon "stepping" — refer to the specification update for additional stepping information. |  |  |  |

| Lot #                    | Identifies the batch.                                                                                                 |  |  |  |

| FPO #                    | Identifies the Finish Process Order.                                                                                  |  |  |  |

Table 1. LXP730 Pin Descriptions

| Pin                      | Symbol                | Type <sup>1</sup> | Description                                                                                                                                     |  |

|--------------------------|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 9, 16,<br>33, 48      | VCC                   | -                 | Power Supply.                                                                                                                                   |  |

| 10, 17,<br>32, 49,<br>64 | GND                   | ı                 | Ground.                                                                                                                                         |  |

| 28                       | DATA0/<br>CRC_ERROR   | DI/O, DO          | <b>DATA0.</b> MPC mode/ <b>CRC_ERROR.</b> flag HWC mode, indicates an error was detected in the previous frame.                                 |  |

| 29                       | DATA1/FEBE            | DI/O, DO          | <b>DATA1.</b> MPC mode/ <b>FEBE.</b> flag HWC mode, indicates the other side of the DSL link encountered a CRC error.                           |  |

| 30                       | DATA2/<br>LINK_ACTIVE | DI/O, DO          | <b>DATA2.</b> MPC mode/ <b>LINK_ACTIVE.</b> HWC mode, indicates that the DSL link is active and ready to transport data.                        |  |

| 31                       | DATA3/RUN-<br>STOP    | DI/O, DI          | <b>DATA3.</b> MPC mode/ <b>RUN-STOP.</b> HWC mode, set to low to activate the DSL link, edge triggered input.                                   |  |

| 34                       | DATA4/<br>FRMSYNC15   | DI/O, DO          | DATA4. MPC mode /FRMSYNC15. HWC mode, Frame Sync Pulse, channel 15.                                                                             |  |

| 35                       | DATA5/<br>FRMSYNC16   | DI/O, DO          | DATA5. MPC mode /FRMSYNC16. HWC mode. Frame Sync Pulse, channel 16.                                                                             |  |

| 36                       | DATA6/<br>FRMSYNC17   | DI/O, DO          | DATA6. MPC mode /FRMSYNC17. HWC mode. Frame Sync Pulse, channel 17.                                                                             |  |

| 37                       | DATA7/<br>FRMSYNC18   | DI/O, DO          | DATA7. MPC mode /FRMSYNC18. HWC mode. Frame Sync Pulse, channel 17.                                                                             |  |

| 22                       | ADDR0/<br>FRMSYNC13   | DI, DO            | ADDR0. MPC mode/FRMSYNC13. HWC mode. Frame Sync Pulse, channel 13, output.                                                                      |  |

| 23                       | ADDR1/N1              | DI                | ADDR1. MPC mode/N1. DSL rate select, HWC mode.                                                                                                  |  |

| 24                       | ADDR2/N2              | DI                | ADDR2. MPC mode/N2. DSL rate select, HWC mode.                                                                                                  |  |

| 25                       | ADDR3/N3              | DI                | ADDR3. MPC mode/N3. DSL rate select, HWC mode.                                                                                                  |  |

| 26                       | ADDR4/N4              | DI                | ADDR4. MPC mode/N4. DSL rate select, HWC mode.                                                                                                  |  |

| 27                       | ADDR5/<br>FRMSYNC14   | DI, DO            | ADDR5. MPC mode/FRMSYNC14. Frame Sync Pulse, channel 14, output, HWC mode.                                                                      |  |

| 57                       | MOTEL/HWC             | DI                | MOTEL/HWC. Set high for Motorola mode, set low for Intel mode, Micro Processor Control (MPC) mode, input /HWC. pull high for HWC mode, input.   |  |

| 39                       | R/W(WR)/HWC<br>select | DI                | R/W(WR). R/W for Motorola interface, WR for Intel interface /HWC select, set low for HWC mode.                                                  |  |

| 40                       | (RD)/HWC select       | DI                | (RD). Unused for Motorola interface, RD for Intel interface /HWC select, set low for HWC mode.                                                  |  |

| 38                       | CS /HWC select        | DI                | CS. Chip select, HWC select, set low for HWC mode.                                                                                              |  |

| 41                       | ALE/HTU_SEL           | DI                | <b>ALE.</b> Address latch enable for Intel interface, MPC mode, input /HTU_SEL. HTUC/HTUR select, High for HTUC, Low for HTUR, HWC mode, input. |  |

AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; NC = No Clamp. Pad will not clamp input in the absence of power; PU = Input contains pull-up; PD = Input contains pull-down; I/O = Input/Output; OD = Open Drain Output; TO = Tri-State Output.

Table 1. LXP730 Pin Descriptions (Continued)

| 42<br>56<br>8 | ĪNT                 |        |                                                                                                                                                                      |

|---------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -             |                     | DO     | INT. Interrupt output. Programmed by setting bits in the INT_EN register.                                                                                            |

| 8             | RESET               | DI     | RESET. Active low input. All registers revert to their default values.                                                                                               |

|               | MCLK                | DI     | MCLK. Master Clock.                                                                                                                                                  |

| 4             | CDATI               | DI     | CDATI. Codec Data In.                                                                                                                                                |

| 3             | CDATO               | то     | CDATO. Codec Data Out, Tri-state.                                                                                                                                    |

| 2             | CCLK/TCLKO          | то     | CCLK. Codec Clock, Nominal 2.048 MHz, tri-state. /TCLKO. Transport Clock for T1/E1: 1.544 MHz or 2.048 MHz clock derived from line rate.                             |

| 5             | FRMSYNC1/<br>FRMOUT | DO     | FRMSYNC1. Frame Sync Pulse, channel 1, output. /FRMOUT. Frame Out, for T1/E1 application, output.                                                                    |

| 6             | FRMSYNC2            | DO     | FRMSYNC2. Frame Sync Pulse, channel 2, output.                                                                                                                       |

| 7             | FRMSYNC3            | DO     | FRMSYNC3. Frame Sync Pulse, channel 3, output.                                                                                                                       |

| 62            | FRMSYNC4            | DO     | FRMSYNC4. Frame Sync Pulse, channel 4, output.                                                                                                                       |

| 61            | FRMSYNC5            | DO     | FRMSYNC5. Frame Sync Pulse, channel 5, output.                                                                                                                       |

| 60            | FRMSYNC6            | DO     | FRMSYNC6. Frame Sync Pulse, channel 6, output.                                                                                                                       |

| 59            | FRMSYNC7/<br>SDOCK  | DO     | FRMSYNC7. Frame Sync Pulse, channel 7, output. /SDOCK. Serial Data Out Clock, ADPI serial mode, output.                                                              |

| 58 F          | FRMSYNC8/ SDO       | DO     | FRMSYNC8. Frame Sync Pulse, channel 8, output. /SDO. Serial Data Out, ADPI serial mode, output.                                                                      |

| 55            | FRMSYNC9<br>SDICK   | DO     | FRMSYNC9. Frame Sync Pulse, channel 9, output. /SDICK. Serial Data In Clock, ADPI serial mode, output.                                                               |

| 54 F          | FRMSYNC10/ SDI      | DO, DI | FRMSYNC10. Frame Sync Pulse, channel 10, output. /SDI. Serial Data In, ADPI serial mode, input.                                                                      |

| 53            | FRMSYNC11           | DO     | FRMSYNC11. Frame Sync Pulse, channel 11, output.                                                                                                                     |

| 52            | FRMSYNC12/<br>PDOE  | DO     | FRMSYNC12. Frame Sync Pulse, channel 12, output. /PDOE. PCM Data Output Enable, control for external PCM interface buffer, output. Enabled by bit-3 of Register 23h. |

| 51            | GAP_CLK             | DO     | <b>GAP_CLK.</b> Gapped Clock, N x 64 kHz recovered from DSL for optional external ADPLL, output. Output is high when option not selected.                            |

| 63            | TEST1               | DI     | TEST1. Factory Test Pin 1, input; should be tied to GND.                                                                                                             |

| 11            | TEST2               | DI     | TEST2. Factory Test Pin 2, input; should be tied to VCC.                                                                                                             |

| 21            | OSDICK              | DO     | OSDCKI. Overhead Serial Data In Clock, output.                                                                                                                       |

| 20            | OSDI                | PU     | OSDI. Overhead Serial Data In, input.                                                                                                                                |

| 19            | OSDOCK              | DO     | OSDOCK. Overhead Serial Data Out Clock, output.                                                                                                                      |

| 18            | OSDO                | DO     | OSDO. Overhead Serial Data Out, output.                                                                                                                              |

<sup>1.</sup> AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; NC = No Clamp. Pad will not clamp input in the absence of power; PU = Input contains pull-up; PD = Input contains pull-down; I/O = Input/Output; OD = Open Drain Output;

TO = Tri-State Output.

Table 1. LXP730 Pin Descriptions (Continued)

| Pin | Symbol                           | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                             |  |

|-----|----------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 44  | OSOF                             | DO                | OSOF. Overhead Serial Output Flag, output. Indicates the first bit of OSIO output frame.                                                                                                                                                                                                                |  |

| 50  | OSIF                             | DO                | <b>OSIF.</b> Overhead Serial Input Flag, output. Indicates the first bit of OSIO input frame.                                                                                                                                                                                                           |  |

| 45  | TDATA                            | DO                | TDATA. Transmit Data, output. Connect to SK70725.                                                                                                                                                                                                                                                       |  |

| 47  | RDATA                            | DI                | RDATA. Receive Data, input. Connect to SK70725.                                                                                                                                                                                                                                                         |  |

| 46  | QUATCLK                          | DI                | QUATCLK. Quaternary alignment Clock, input. Connect to SK70725.                                                                                                                                                                                                                                         |  |

| 43  | BITCLK                           | DI                | BITCLK. Bit Clock, input. Connect to SK70725.                                                                                                                                                                                                                                                           |  |

| 13  | PFRM / FRMIN /<br>Z <sub>0</sub> | DI,DO,DI          | <b>PFRM.</b> PCM frame pulse: input for PCM slave, output for PCM master. Alignment signal for the first time slot for both PDI and PDO. /FRMIN. Frame In, for T1/E1 application, input. /Z <sub>o</sub> . Bit zero of the 3-bit word used to specify the number of Z bits in the Hardware mode, input. |  |

| 12  | PDI / T1E1I / Z <sub>1</sub>     | PU,DI,<br>DI      | <b>PDI.</b> PCM Data In, input. /T1E1I. T1 or E1 Input data, input. /Z <sub>1</sub> . Bit one of the 3-bit word used to specify the number of Z bits in the Hardware mode, input.                                                                                                                       |  |

| 15  | PDO / T1E1O / Z <sub>2</sub>     | TO,TO,DI          | <b>PDO.</b> PCM Data Out, tri-stateable output. /T1E10. T1 or E1 Output data, tri-stateable output. /Z <sub>2</sub> . Bit two of the 3-bit word used to specify the number of Z bits in the Hardware mode, input.                                                                                       |  |

| 14  | PCLK/TCLKI                       | DI/O              | PCLK. PCM clock: input for PCM slave, output for PCM master. /TCLKI. Transport Clock In, for T1/E1 application, 1.544MHZ - T1, 2.048MHz - E1, input.                                                                                                                                                    |  |

AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; NC = No Clamp. Pad will not clamp input in the absence of power; PU = Input contains pull-up; PD = Input contains pull-down; I/O = Input/Output; OD = Open Drain Output;

TO = Tri-State Output.

### 2.0 Functional Description

#### 2.1 LXP730 Nx64 Framer

The LXP730 is designed to multiplex/demultiplex two payload sources to/from a DSL stream, and add/recover overhead data for link control. Several popular interfaces are provided to support a variety of applications.

The two major categories of payload supported are synchronous (i.e. voice-frequency data - PCM) and asynchronous (i.e. digital data - Packet/Cell). The LXP730 supports Nx64 kbps channels in the DSL with N = 4 to 18. The LXP730 consists of the following functional blocks as shown on page 1:

- Time Slot Interchange (TSI)

- PCM-Bus Interface

- Codec Interface

- T1/E1 Interface

- Asynchronous Data Port Interface (ADPI)

- Microprocessor Interface

- Overhead Serial I/O (OSIO) Interface

- SK70725/SK70721 (MDSL) Interface

- All Digital PLL (ADPLL)

- Clock Generation and Distribution

The terms Local and Remote are used in this document to designate the two ends of a DSL link. The Local is usually the master in that it initiates the link startup and can control the actions and configuration of the Remote. There are several equivalent nomenclatures in the Telecom industry. Some of these are, respectively: CO and CPE, or HTU-C and HTU-R, or LTU and NTU.

The following is a description of the LXP730 functional blocks.

### 2.2 Time Slot Interchange (TSI)

The Time Slot Interchange (TSI) is the central module of the LXP730 Nx64 framer. The TSI maps payload to the available DSL N-channels for transport across the loop.

The TSI uses register settings to select time slots to map into the N MDSL channels. The total number of available payload channels is *N* and is set by the N\_MDSL register (00h), with selected valid values from 4 to 18. Each of the 18 Nx registers (01h -012h) is used to select the payload source, and if applicable, the PCM time slot assigned to the register's corresponding MDSL channel.

In the MX direction (from the TSI to the MDSL Interface), the TSI multiplexes the payload sources into the MX elastic store (MX ES). The payload and overhead are multiplexed into the DSL stream for loop transport.

In the DX direction (from the MSDL Interface to the TSI), the TSI reads from the DX elastic store (DX ES) and demultiplexes the loop data into its payload data sources.

Synchronous payload sources are typically 8-bit serial time slots, cascaded together with each source repeating every 125 µsec (i.e. 8 kHz). A framing pulse, separate from the data signal, signifies the start of a frame. A 2.048 Mbps data stream has 32 time slot sources, while a 1.544 Mbps data stream has 24 time slot sources plus one extra bit for framing.

When the PCM or codec interfaces are running, the framing pulses are used by the TSI to initialize operation to the MX ES. The MX ES and DX ES have triple buffering schemes that prevent the loss of data. The PCM/codec interfaces typically produce high speed data bursts while the MDSL interface runs at a slower though irregular rate.

Asynchronous data is typically a sequence of bytes which have no explicit timing relationship between them. Asynchronous Data Port Interface (ADPI) bytes may be inserted into payload slots that are not carrying PCM data. ADPI bytes are inserted into the DSL stream in the order they are received from the interface.

Channel blocking on a MDSL channel is achieved by setting the CH\_CFG bits in the Nx register to 01. The transported value for that MDSL channel will be the one stored in the IDLE register.

The TSI uses the MCLK clock to synchronize to the various interfaces. The MCLK frequency must be at least three times the highest interface clock frequency for the TSI to function properly. There are other considerations to select the operating frequency of MCLK when using the internal ADPLL.

#### 2.3 PCM-Bus Interface

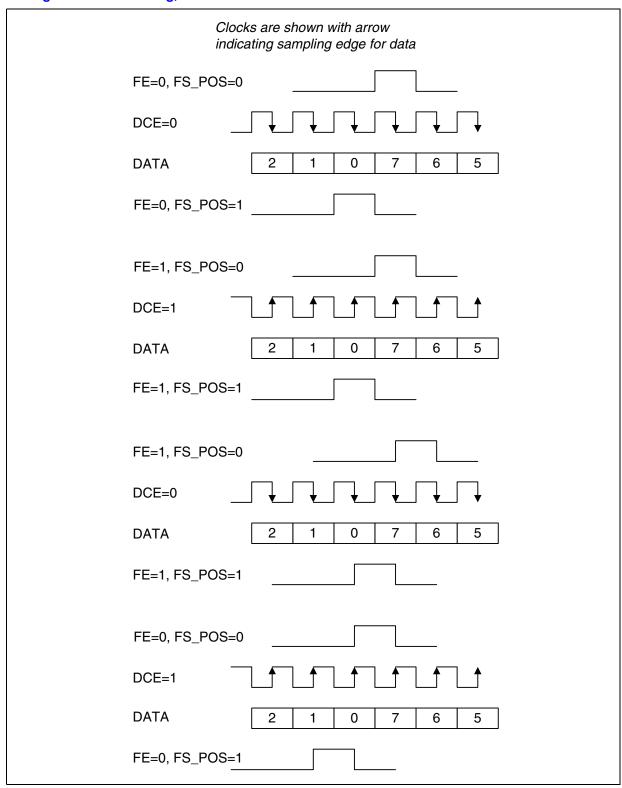

The LXP730 provides a generic interface for common PCM-bus configurations and can either be master or slave to these PCM busses. Some of the key features that allow flexibility are:

- Clock at 1x or 2x the data rate

- Programmable number of bytes per frame; 8, 16, 32, 64

- Programmable clock and frame pulse polarities

These features allow interfacing to standard PCM styles such as: ST, IOM, IOM2 (see Figure 9 for circuit) and CHI. The data rates can range from 256 kbps to 4096 kbps. The clock rates can range from 256 kHz to 8196 kHz.

The range of permissible PCM time slots are 0 to 31 for a 2.048 Mbps backplane and 0 to 63 for a 4.096 Mbps backplane for a total number of time slots up to the maximum number N. PCM time slots must be assigned in ascending order to MDSL channels. The value set in the TS-bits in the Nx registers select the PCM timeslot to go into the xth MDSL channel.

There is a limitation of the disparity allowed between the PCM clock and the BIT\_CLK. For N = 4, the PCM bit rate cannot exceed 2 Mbps. To use a 4 Mbps PCM interface the NMDSL setting must be at least 6 channels.

On these busses, the input and output data streams are synchronized to the same clock. A slip buffer is present on the receive side to accommodate the differences in the PCM clock frequencies of the two ends of the MDSL line.

The slip buffer is two frame lengths long. The buffer will empty if the PCM clock is reading data out of the slip buffer faster than the TSI is writing into it. When the last bit for the frame has been read and there is not another byte from the next frame to clock out, the read pointer is set back to the beginning of the current frame and repeated. The other slip situation occurs when the TSI is writing data faster than the PCM is clocking it out. When the write pointer gets close to the read pointer that hasn't finished a frame, then the read pointer is allowed to finish the current frame and then is advanced to skip the next frame.

The slip buffer may be bypassed by setting the SBBP bit, (bit 0, in the PCM\_CFG1, register). Slip occurrences are detected and signalled in the Interrupt Status register.

Normally the LXP730 PCM bus is configured as a slave in the Local unit, while the Remote LXP730 PCM bus can be either configured as slave or master off the PCM bus. When the Remote LXP730 is in PCM slave mode, the slip buffers accommodate the differences in the two PCM clocks. When the Remote LXP730 is in PCM master mode, the PCM clock and frame pulse are derived from the receive DSL clock using the internal ADPLL to provide loop timing to prevent the slip action from occurring.

The PCM bus timeslot assignments to the DSL channels may be altered while the DSL link is active. The Nx registers can be changed without interfering with other Nx registers and the effect of their settings.

The PDO pin is tri-stated except during programmed time slots.

The PFRM pulse defines the start of a PCM frame. The number of PCM time slots per frame is variable from 4 to 64. This is programmed by setting the six MAXPCHN bits in, the PCM\_CFG2 register, with the value n-1 number time slots.

PCM selection for a MDSL channel is accomplished by setting the CH\_CFG bits in the Nx register to '10' (binary).

#### 2.4 Codec Interface

The LXP730 primarily supports the COMBO codec I style devices. The LXP730 codec interface is programmable to allow the use of other codec type devices that require a positive frame pulse. The LXP730 provides a separate set of pins for this interface allowing simultaneous operation with a PCM bus with the following characteristics:

- Short frame positive sync pulse

- Clock at 1x or 2x the data rate

- Programmable number of bytes per frame in MPC; 8, 16, 32, 64

The data rates can range from 256 kbps to 4096 kbps. The clock rates can range from 256 kHz to 8196 kHz. Under HWC mode, the number of bytes per frame is limited to 32.

The input and output data from the TSI are connected to the codec CDATI and CDATO pins for the appropriate time slot. The CDATO pin is tri-stated except during programmed time slots. Only twelve (12) codecs are supported in the MPC mode.

The LXP730 is always the master on the codec bus. The LXP730 can be configured to derive the clock and frame pulse from either MCLK (in codec Master mode) or from the DSL clock using the internal ADPLL (in codec Slave mode). One LXP730 of the DSL link must be in the Master codec mode and the other in the Slave codec mode.

The LXP730 generates the codec clock and the framing pulses for eighteen (18) codecs from the selected reference. Selecting codec timeslot 0 in an Nx register corresponds to FRMSYNC1, 1 to FRMSYNC2, etc. In HWC mode, the FRMSYNC pins are automatically assigned with the programming of the Nx pins. The number of codec time slots per frame is variable from 4 to 64. This is programmed by setting the six MAXCCHN bits in the COD\_CFG register (22h) with the value n-1 number time slots.

Codec selection for a MDSL channel is accomplished by setting the CH\_CFG bits in the Nx register to '00' (binary).

#### 2.5 T1/E1 Interface

The LXP730 supports T1/E1 framer interfaces by using a hybrid of the PCM and codec interfaces to transport pleisiochronous data.

The PCM interface is used in its slave mode to connect a T1/E1 framer and its TxData (T1E1O), RxData (T1E1I), RxCLK (TCLKI) and FramePulseOut (FRMIN). The slip buffer must be in the bypass mode.

The codec interface is used in its slave mode to derive the FramePulseIn (FRMOUT) and TxCLK (TCLKO) to the T1/E1 framer. The derived T1/E1 FRMOUT tracks the MDSL frame rate from the DSL, and in cases where framing is lost, the DX tracking circuits slowly reacquire to prevent a drastic change in the output frame frequency.

The PCM and codec sections must each be configured through registers to handle the T1/E1 pleisiochronous data.

For T1, only *N*=12 or fractional T1 is supported. In T1, the only workable value for the PCM\_CFG2 register is 98h. The MX T1 F-bits must be part of the data stream coming from the external T1 framer. The 12 unused DX T1 time slots are filled with the value programmed in the IDLE register if the TFI bit (bit 0) is set to 0.

Key features of the T1E1 interface are:

• Framer interfaces: DS2141and DS2143

Data rates: 1544 and 2048 kbpsClock rates: 1544 and 2048 kHz

### 2.6 Asynchronous Data Port Interface (ADPI)

The LXP730 supports a serial method for the Asynchronous Data Port Interface (ADPI). The ADPI is available only in the MPC operating mode. MDSL channels are programmed for ADPI by setting the CH\_CFG bits to '11' (binary) in the desired Nx register. The operation of the ADPI is mutually exclusive with the LXP730 codec frame sync pins (FRMSYNC7-10).

The serial ADPI mode provides separate pins for data in, data out, clock-in and clock-out. This is compatible with the bit operation protocol (BOP) for HDLC devices. The LXP730 controls both of the clocks, and therefore, the data flow. The LXP730 moves the bits in and out in 8-bit groups. The maximum clock rate for the bit-to-bit transfer is set by the SAPCLKDIV bits in the FIFO\_MISC register. This allows the clocks to run at MCLK  $\div$  2 or slower. The groups of clock pulses will be gapped due to the availability of bit positions in the DSL data stream.

#### 2.7 Overhead Interface

The LXP730 provides two options for the interface to insert and receive overhead data for the link: via an external serial interface or through the microprocessor register interface. The data can either be user defined or partially predefined as described in "MDSL Overhead Definition" on page 23. The overhead channel is used for signalling, status flags, loopback control, and diagnostic messaging between the Local and Remote ends of a MDSL link. The LXP730 provides the transparent channel for the overhead data and does not interpret the protocol operation.

The F-bits in the fractional T1 mode are not part of the overhead.

#### 2.7.1 Overhead Serial I/O (OSIO)

The OSIO interface is the default overhead access for both the MPC and HWC operational modes. The serial interface provides six separate pins for data in (OSDI), data out (OSDO), clock-in (OSDICK) clock-out (OSDOCK), start flag in (OSIF), and start flag out (OSOF). The use of the first four pins is compatible with the bit operation protocol (BOP) for HDLC devices. The two flag pins (OSIF and OSOF) provide indications of the start of a MDSL frame and may used with custom overhead handling devices. The flag signals are coincident with the first overhead bit in the MDSL frame.

The LXP730 controls both of the clocks, and thus, the data flow. The clocks will be gapped due to the availability of bit positions in the DSL data stream. The OSIO may be disabled in the MPC mode by setting the Par/Ser bit in the OVRHD\_SEL register (24h). OSIF and OSOF will continue to operate.

The defined bits (except the indc\_r bit) go to the microprocessor interface registers. The undefined bits (plus the indc\_r bit) go to the OSIO interface. This allows a separate transport for HDLC devices while maintaining DSL performance monitoring.

#### 2.7.2 MDSL Overhead Microprocessor Interface

The MDSL overhead microprocessor interface mode uses internal registers to provide the access to insert and receive overhead data for the link. The Par/Ser bit must be set to access the contents of the overhead and Z bit registers. Interrupts may be used to synchronize the contents with the MDSL link. The data can either be user defined or partially predefined as described in "MDSL Overhead Definition" on page 23. Microprocessor writes to defined bits have no effect, with the exception of the indc\_r bit.

The registers for the OH and Z bits are double buffered for both the MX and DX sections. When the OHMX bit is set in the INT\_STAT, 3Fh, register, the values in the user assessable MX registers are latched into an internal set of registers, and then serially shift throughout the frame. The user has a nominal 6 ms to update the MX registers before they are latched again for transport. Likewise, the DX registers hold their values until the OHDX bit is set, then the overhead data from the latest frame is available. The user again has a nominal 6 ms to read the DX data before it is over written.

#### 2.8 MDSL Interface

Each LXP730 device works directly with one SK70725/21 data pump chip set. The SK70725/21 chip set must be in Mode 0 to work with the LXP730. Refer to the SK70725/21 data sheet for details.

The LXP730 provides TDATA to the data pump and accepts QUATCLK, BITCLK and RDATA signals from the data pump. The framer supports line data rates from 272 kbps to 1168 kbps. Table 2 shows some of the common even-numbered transport, nominal line rates and the number of bits per frame. Odd numbered N values may also be used.

The first value in the Bits/Frame column is the number of bits in an unstuffed frame, and the second value is with stuffing. MDSL Frame periods are a nominal 6 ms regardless of the nominal line rate.

| Table 2.  | Common | <b>Transport</b> | & Line  | Rates |

|-----------|--------|------------------|---------|-------|

| I UDIC E. |        | HUIDPOIL         | G LIIIC | liuto |

| Data Rate<br>(kbps) | Nominal Line<br>Rate (kbps) | 64 kbps Channels<br>(N) | Bits/Frame |

|---------------------|-----------------------------|-------------------------|------------|

| 256                 | 272                         | 4                       | 1630/1634  |

| 384                 | 400                         | 6                       | 2398/2402  |

| 512                 | 528                         | 8                       | 3166/3170  |

| 640                 | 656                         | 10                      | 3934/3938  |

| 768                 | 784                         | 12                      | 4702/4706  |

| 1152                | 1168                        | 18                      | 7006/7010  |

The line rate is calculated as  $N \times 64$  kbps + 16 kbps, where N is the number of 64 kbps channels to be transported. The 16 kbps is the total overhead provided by the MDSL transport system.

The 16 kbps holds true as long there is one Z bit per block as described in "MDSL Frame Format" on page 25. The LXP730 supports up to eight Z bits per block, but when greater than one, the overhead rate increases. This causes the line rate to increase accordingly. The equation to calculate the DSL line rate is as follows:

Line rate (kbps) =  $8[Z + 1 + (N \times 8)]$

The LXP730 will scramble payload data, but pass the sync word in the clear. In the Local mode, the LXP730 uses the following scrambling polynomial:

$$x^{-23} + x^{-5} + 1$$

,

In the Remote mode the scrambling polynomial is:

$$x^{-23} + x^{-18} + 1$$

.

In transparent mode, the LXP730 uses the quat alignment signal (QUATCLK) from the data pump to align the sign and magnitude bits in both the transmit and receive directions.

The overhead bits are described in "MDSL Overhead Definition" on page 23.

Before routing the data to the descrambler, the LXP730 will invert the sign bits of the received data stream, if the detected frame sync word has inverted sign bits.

The MDSL interface provides loopback of TDATA, bypassing the external RDATA. Loopback is activated by setting the DSL\_LB bit in the OVRHD\_CFG register (24h). This routes the 64 kbps channels and MDSL Overhead (MOH) from the MX section to the DX section. When using an external loopback configuration, such as FELB in the SK70725, it is necessary to switch the DX de-scrambling polynomial to the MX polynomial. The descrambling polynomial is inverted by setting the REMOTE\_LB bit of the FIFO\_MISC register (17h). The BITCLK and QUATCLK control the transfer of data from the MX to the DX section.

### 2.9 All Digital PLL (ADPLL)

The LXP730 ADPLL is necessary for clock recovery and to control output jitter and wander produced in the DSL environment.

The ADPLL uses MCLK to drive the NCO circuitry, while the reference frequency comes from the received DSL frame rate that has a nominal 6 ms period.

### 2.9.1 ADPLL Performance: The Selection of K<sub>loop</sub>

The performance of the ADPLL is user programmable via a register. As shown in Table 3, the 5-bit value,  $K_{loop}$ , in PLLCTL3 register controls the lock time and the bandwidth of the ADPLL. The lock time is the amount of time required for the ADPLL to acquire and synchronize to the input MDSL signal. The bandwidth of the ADPLL determines the jitter rejection characteristics of the ADPLL. The bandwidth and lock time are inversely related:  $BW = 3/T_{lock}$ .

Table 3. K<sub>loop</sub> Values

| Register Bits | Kloop_Value      |

|---------------|------------------|

| 00000         | PLL freeze       |

| 00001         | 20               |

| 00010         | 2-1              |

| 00011         | 2-2              |

| 00100         | 2-3              |

|               |                  |

| 11111         | 2 <sup>-30</sup> |

Kloop is a 5 bit control field found in register PLLCTL3 (address 1D hex, 29 dec). The register bits are used to select a constant (Kloop\_Value) that controls the loop bandwidth.

The Bandwidth of the loop filter is determined from the selected Kloop\_Value and the frequency of MCLK. Loop bandwidth (BW) is calculated as follows:

BW (3db) =  $Kloop\_Value \times MCLK \times 3.89e-5 Hz$

#### 2.9.2 ADPLL Center Frequency: The computation of CFREQ

The center frequency of the ADPLL is set by an 18-bit unsigned fractional number, CFREQ(17:0). This value is programmed in PLLCTL1, PLLCTL2, and PLLCTL3. CFREQ(17:0) is the ratio of the Numerically Controlled Oscillator (NCO) and MCLK, and is shown below. The 2<sup>18</sup> is the normalizing factor to express it in integer notation. It must then be converted to hexadecimal to load into the CFREQ register.

The output of the NCO is divided by 2 before being provided to the clock multiplex circuitry and the optional PROG\_DIV block. This must be taken into account when deciding upon the frequency for the NCO.

The NCO/MCLK ratio should be set to a value greater than or equal to 0.5 but less than 0.98. This ensures that there will be the maximum number of bits of accuracy for the NCO to generate the frequency. The ratio of 0.5 normalized with 2<sup>18</sup> is 131072 or in hexadecimal, 20000h. This is the smallest recommended value.

#### **Equation 1. Calculation of CFREQ**

$$CFREQ = ROUND \left[ \frac{(NCOFREQ \times 2^{18})}{MCLK} \right]$$

Table 4 list values for: CFREQ(17:0), Programmable Divider, and NCO frequency for a MCLK of 16.384MHz in several configurations.

#### 2.10 Clock Generation and Distribution

The LXP730 has a flexible clock generation circuit as shown in Figure 3. The clocks for the PCM and codec interfaces can be an independent external input, a division of MCLK, a division of the ADPLL output, or the ADPLL output as selected by the PCM Configuration 1 register (PCM CFG1) and the Codec Configuration register (COD CFG).

The PCM port is considered to be in slave mode when its clock source is the external pin. The PCM frame pulse is also sourced from its external PFRM pin when the clock is configured as such. The PCM port is in master mode for the other three settings. The PCM frame pulse is derived from the internal PCLK and driven out on the PFRM pin.

The codec port initially has the CCLK pin tristated until it is configured as an output by setting the CCLK\_OE bit in the MISC\_CTL register. It is never an input. The external source for the codec clock is the PCLK pin. This allows simultaneous use of the PCM and codec interfaces with the PCM bus providing the clock and allowing MCLK to be some other frequency that may not be suitable to divide down for the codecs.

The ADPI clock is not derived from the circuit shown in Figure 3, but rather comes from the TSI module. The TSI keeps track of opportunities to transmit bytes into the DSL frame and creates a burst of eight pulses to clock a byte of data to insert in the MX direction. The TSI unloads data from the DX DSL direction and also creates a burst of eight pulses to clock a byte of data to the external device connected to the ADPI interface.

The burst frequency of the ADPI clocks is derived from MCLK and can be adjusted by the SAPCLKDIV (bits 6 & 7, in register 17h, FIFO\_MISC).

Table 4. Typical ADPLL Register Settings, MCLK = 16.384MHz

| PCMCLK<br>Output<br>(MHz) | #B PCM | #B DSL | NCO Frequency<br>(MHz) | PROG_<br>DIV | NCOFREQ/<br>MCLK | CFREQ(17:0) |

|---------------------------|--------|--------|------------------------|--------------|------------------|-------------|

| 1.544                     | 24     | 12     | PCMCLK ×8              | 4            | 0.754            | 0x30400     |

| 2.048                     | 32     | 18     | PCMCLK × 4             | 2            | 0.5              | 0x20000     |

| 1.152                     | 18     | 18     | PCMCLK ×8              | 4            | 0.5625           | 0x24000     |

| 0.896                     | 14     | 14     | PCMCLK × 16            | 8            | 0.875            | 0x38000     |

| 0.768                     | 12     | 12     | PCMCLK × 16            | 8            | 0.75             | 0x30000     |

| 0.256                     | 4      | 4      | PCMCLK × 32            | 16           | 0.5              | 0x20000     |

Figure 3. Clock Generation and Distribution

### 2.11 Modes of Operation

#### 2.11.1 Microprocessor Control (MPC) Mode

The Microprocessor Control (MPC) mode provides access for a microprocessor to configure and control the operation of the framer. The LXP730 provides an 8-bit data bus for the purpose of reading and writing internal registers. The registers are used to configure framer settings, to read and write the MDSL Overhead bits and to configure interrupts and other run-time operational functions.

The microprocessor access circuits support both MOTEL (MOTorola/IntEL) microprocessor interfaces. A chip select signal activates the interface between the device and the microprocessor. In the Motorola mode, the LXP730 supports the R/W and  $\overline{CS}$  signals. The Motorola signal  $\overline{DS}$  is not used in this mode. In the Intel mode, the LXP730 supports the  $\overline{CS}$ , ALE,  $\overline{WR}$  and  $\overline{RD}$  signals. In the Intel mode, the data pins conform to the Intel style Address/Data (AD) functionality. The

address is presented to the AD pins and internally latched with ALE, then the data is either read from or written to the device. ALE may be held high for non-multiplexed address and data operation in the Intel mode for use of the  $\overline{WR}$  and  $\overline{RD}$  signals.

One interrupt pin is provided. Registers are provided for enabling/disabling the interrupts and monitoring the status of the interrupt signals.

In the MPC mode, both the PCM and Codec/Data Port interfaces may be used simultaneously. The assignment of the 64 kbps timeslots from the interfaces to the DSL is controlled by the TSI (Time Slot Interchange) block. This feature allows data from two different sources to be transported over the DSL.

#### 2.11.2 Hardware Control (HWC) Mode

This mode provides an operational method to run only the codec and OSIO interface without a microprocessor. Pins are provided to select the number (N) of 64 kbps channels to be transported. The following Error/Status flags output pins are provided: LINK\_ACTIVE, CRC\_ERR and FEBE. RESET, HTUC/HUTR and RUN-STOP control signals (input pins) are provided.

These pins are shared with the microprocessor mode pins. The HWC mode is selected by pulling the  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{CS}$  and ALE pins Low and the MOTEL pin High.

Only the codec and OSIO interfaces are accessible in the HWC mode. The first *N* codec frame sync pins are active in sequence from 1 to N. As shown in Table 5, pins N1 through N4 are used to select the quantity of codecs supported and to select the proper MDSL frame format. The N0 pin is not used since *N* is always an even number in the HWC mode. The codec interface runs only at the 2.048 MHz 1x clock in the HWC mode.

| Number of     | Pin |    |    |    |  |  |  |

|---------------|-----|----|----|----|--|--|--|

| MDSL Channels | N4  | N3 | N2 | N1 |  |  |  |

| 4             | 0   | 0  | 0  | 1  |  |  |  |

| 6             | 0   | 0  | 1  | 0  |  |  |  |

| 8             | 0   | 0  | 1  | 1  |  |  |  |

| 10            | 0   | 1  | 0  | 0  |  |  |  |

| 12            | 0   | 1  | 0  | 1  |  |  |  |

| 18            | 1   | 0  | 0  | 0  |  |  |  |

Table 5. Pin settings for HWC DSL Line Rates

#### 2.12 MDSL Overhead Definition

The MDSL overhead bits do not carry any payload values but are used for exchanging messaging and signalling information between the two ends of the DSL link. The overhead bits are divided into two categories; OH and Z bits.

The OH bits are defined in both the ETSI ERT/ETS-152 and ANSI T1E1.4/94-006 standards. These usually have specific definitions. In the LXP730, the OH bits may be partially defined, according to the standards, or totally user definable which is referred to as transparent mode.

The LXP730 supports DSL OH bits in four modes:

- Transparent and register accessible.

- Transparent and OSIO accessible.

- Partially Predefined and register accessible.

- Partially Predefined and OSIO accessible.

The reset default overhead mode is number 4. The modes are selected by setting bits 7 and 6 of register 24h, OVRHD\_CFG.

In the HWC mode some of the pre-defined bits' status is routed to external status pins, i.e. CRC\_ERROR, FEBE, LINK\_ACTIVE.

#### 2.12.1 Predefined Overhead

Pre-defined bit-fields support: frame sync word, stuff-bits, *los*, *CRC-6*, *febe*, *indc\_r*, *f* bits and user defined overhead bits. In this mode the user may write to the corresponding bits in the MXOH registers, but the LXP730 will ignore them and insert the predefined bits into the bit stream.

The frame sync word (FSW) bit pattern consists of the following 14 bits in order from left to right: (1010100001000), this generates the +3 +3 +3 -3 -3 +3 -3 quat valued sync waveform on the MDSL. Other valid sync patterns are the time-reversed, sign bit inverted, and the time reversed sign bit inverted patterns shown in Table 6. The generation and detection of the FSW is automatic.

Detection of a frame that has an inverted sign bit causes the MDSL block to invert the sign bits of the data stream before it is sent to the descrambler.

Stuff-bits are normally either four (4) bits or zero (0) bits immediately before the sync word of the next frame. The stuffing decision circuit is located in the MDSL Interface block. A special mode fixes the stuff bits at two per frame for applications that require fixed timing such as connections from a wireless base station to its remote sites. This is controlled by bit 0 in register 17h, FIFO\_MISC.

The los bit is used to notify the other side of the DSL of a loss of source from the PCM bus.

*CRC-6* bits are calculated at the transmitter for each frame and sent during the following frame. At the receiver the CRC-6 is calculated on the received frame, stored and then compared with the CRC-6 value received in the following frame. Sync word bits, stuff bits and *CRC-6* bits are the CRC-6 calculation.

The *febe* bit is set in the MX side to the other MDSL unit when a CRC-6 error detected is in the DX side.

The  $indc_r$  bit is set in the MX side to notify the other MDSL unit that it is ready to receive transport data.

#### 2.12.2 Z bits

The first three Z bits in an MDSL frame are reserved for loop ID for multi-loop DSL systems by the ETSI standard. All other Z bits are user defined. One common use is to send the time slot configuration from the Local unit to the Remote unit.

The Z bits may either accessed through the registers or the OSIO interface. This is controlled by the Z\_CTL bit in register 23h, MISC\_CTL. When OH and Z bits both go through the OSIO, they go in order as listed in the frame structure in Table 7. For example: if transparent OH and Z bits all go through the OSIO, then the order for an MDSL frame is 2 OH bits, 12 Z bits, 10 OH bits, 12 Z bits, 10 OH bits, 12 Z bits, 10 OH bits, 12 Z bits. Switching to OH predefined, the corresponding predefined OH bits would not appear at the OSIO and there would be a gap at those time locations.

In HWC mode all the Z bits and the user definable OH bits go through the OSIO.

When the LXP730 is in fractional T1 mode, Z bits are part of the payload and not accessible, otherwise they are accessible in the Z bit registers.

#### 2.13 MDSL Frame Format

The LXP730 has a transport frame format that adjusts automatically with the *N* setting. The overall structure remains constant while adjusting the number of time slots within the payload blocks. Table 7 and Figure 4 shows the overall frame format.

Table 6. MDSL Frame Sync Word (FSW) Patterns

| Type Pattern                | Bits           | Quat Value           |

|-----------------------------|----------------|----------------------|

| Normal                      | 10101000001000 | +3 +3 +3 -3 -3 +3 -3 |

| Time-reversed               | 00100000101010 | -3 +3 -3 -3 +3 +3 +3 |

| Inverted-Sign-Bit           | 00000010100010 | -3 -3 -3 +3 +3 -3 +3 |

| Inverted-Sign-Time-Reversed | 10001010000000 | +3 -3 +3 +3 -3 -3 -3 |

**Table 7. MDSL Frame Format**

| Description | Number of Bits                 |

|-------------|--------------------------------|

| Sync Word   | 14                             |

| МОН         | 2                              |

| B1-B12      | $[Z + (N \times 8)] \times 12$ |

| МОН         | 10                             |

| B13-B24     | $[Z + (N \times 8)] \times 12$ |

| MOH         | 10                             |

| B25-B36     | $[Z + (N \times 8)] \times 12$ |

| MOH         | 10                             |

| B37-B48     | $[Z + (N \times 8)] \times 12$ |

| Stuff       | 0 or 4, typ avg 2              |

The frame is made up of a sync word, followed by alternating sets of MDSL Overhead bits and groups of data blocks. The final element of each frame is a section set aside for stuffing, used to synchronize payload with DSL framing where required.

Each data block contains  $[Z + (N \times 8)]$  bits. The blocks are transmitted in groups of 12. In T1 mode Z=1 and the 12 Z-bits per block group are reserved for framing/signalling and are referred to as f-bits. In all other modes they are user accessible overhead bits known as Z-bits. The frame structure matches the 784 kbps structure adopted by T1E1 and ETSI. For N=18 and Z=1, the frame format follows that of an 1168 kbps HDSL system compliant with ETSI standards.

#### 2.14 Startup Operation

This description applies to the MPC mode for the LXP730. Typically the user sets most of the desired register values and then sets the RUN bit in register 24h, OVRHD\_CFG. At this point the MX side of the framer is sending data to TDATA and the DX side is looking for the FSW. The next step requires clearing of INT\_STAT register by writing OxFF to it. It must be ensured that the SK70725/21 chipset is in either Master or Slave mode as needed. The SK70725/21 chipset needs to be reset and the ACTIVATE bit toggled in the SK70725/21 chipsets. The main control register has to be toggled. In Master mode, the SK70725/21 will start the activation sequence with the Slave responding. In a few seconds the data pumps will have set their filter and echo coefficients and switch to transparent transport mode.

There is an additional setup to consider when the LXP730 is in PCM slave mode and N=18. If there is no clock running, then there is a halt condition when 18 PCM time slots are selected. The work around is to temporarily set the last two of the Nx registers to codec configuration, then set the RUN bit. Once that is done then change the Nx registers back to the desired PCM configuration.

Figure 4. Frame Format for N=12

The DX side of the LXP730 will go to ACTIVE upon receipt of two successive MDSL frames. When this first occurs, the ACTIVE bit in INT\_STAT is set, but will stay reset once it is cleared until the framer goes to inactive and back to active again. The ACTIVE bit is edge triggered. The DSLACTIVE bit in CRC\_FEBE\_ST is level triggered or 'sticky'.

Once the DSL is active, no support is required to keep it operating. At this point there are basically two tasks to perform: 1) monitor for error conditions, 2) use the overhead to pass messages/ signalling between the Local and Remote units.

Most of registers/bits can be changed while the RUN bit is set with the following exceptions:

- N\_MDSL register

- TX8KSSEL bit in 17h

The MX and DX FIFOs (MXFIFORXT & DXFIFORXT) should be reset whenever the PCM or codec clocks are changed while the framer is in the RUN mode. This will cause an interruption in the payload, but the DSL link will stay up.

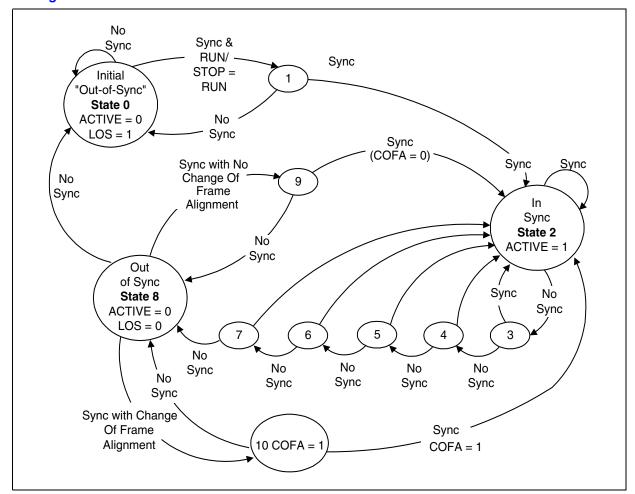

#### 2.15 Activation State Machine

The LXP730 framer has an ANSI T1E1.4/94-006 compatible activation state machine. The operation of the state machine is shown in Figure 5.

Figure 5. Activation State Machine

### 3.0 Application Information

### 3.1 Typical Applications

This section shows some block diagrams to serve as example applications. Connections to the LXP730 as shown emphasize those relevant for the application. Detailed connections to the processor are not shown.

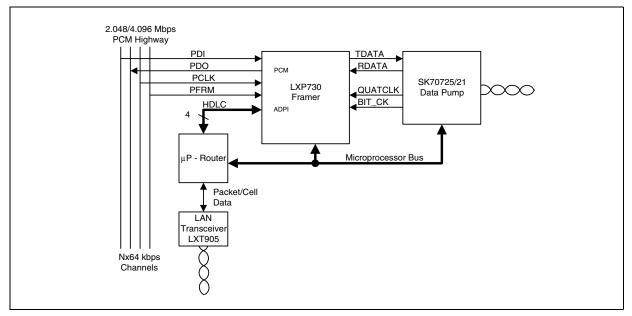

Figure 6 demonstrates how the LXP730 can simultaneously handle voice from a PCM circuit and packet-type data from an HDLC style device.

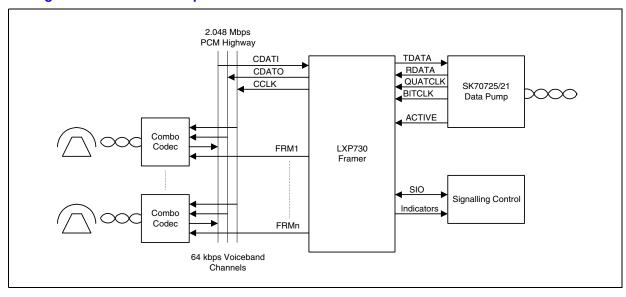

Figure 7 is an example of the HWC mode. The codecs' digital interfaces connect directly to the LXP730. An external device is needed to handle signalling information for each voice line supported. In this case the Z bits could be used to carry the signalling information such as off-hook status from the CPE and ringing signal from the CO. An FPGA or a fast dedicated processor could handle these tasks.

Figure 6. High Performance Voice/Data Transport

Figure 7. Pair Gain Transport

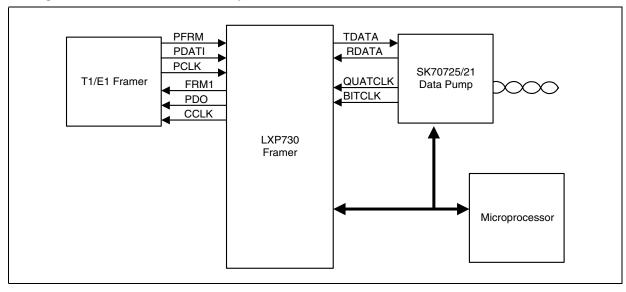

Figure 8 shows a more traditional DSL application to carry phone traffic over a longer distance on a single copper pair. The LXP730 supports the pleisiochronous nature of T1/E1 traffic.

#### 3.1.1 IOM Interface Circuitry

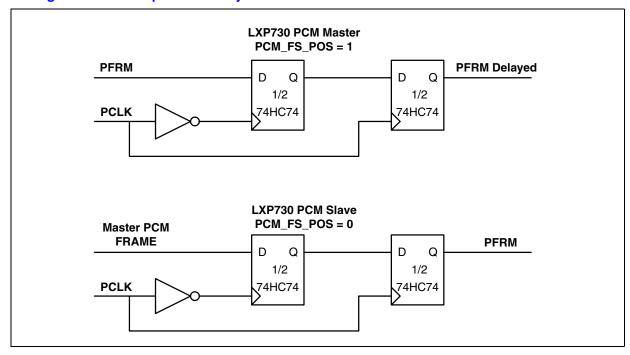

The LXP730 uses a frame pulse in the second cycle of the two clocks per data bit timing. This is directly compatible with the ST electrical interface. The IOM interfaces use the first clock cycle for the frame pulse. The circuit in Figure 9 shows how to adapt the LXP730 to the IOM bus. Note that even though the circuit is the same for the PCM master or slave modes, there is a difference in the connections to the LXP730 and the IOM device.

Figure 8. T1/E1 Fractional Transport

Figure 9. IOM Adaption Circuitry

#### 3.1.2 Handling TIP/RING Reversal in Early Version of SK70725

The early version of the SK70725 data pump device has an error in the Master (CO) mode. The QUAT\_CLK is not aligned correctly with the RDATA for the sign and magnitude bits. When there is no TIP/RING reversal, the LXP730 is able to correctly parse the data bits. However, when TIP/RING reversal has occurred the LXP730 detects that the sign bit is inverted by detecting the inverted Frame Sync Word (FSW) pattern. The LXP730 then uses the QUAT\_CLK to determine which bit to invert. The sign bit is already inverted and the LXP730 inverts the magnitude bit. This problem does not occur in the Slave (CPE) mode of the SK70725. The SK70725 has the ability to invert the received data pulses inside itself. This is done by setting bit 7 of the register WR2. The following procedure takes advantage of how the LXP730 reacts during the error condition and the ability to invert the data stream from the SK70725. The procedure uses one of the Z-bit bytes after frame sync has been achieved to determine if there is a tip-ring reversal at the LTU. DXZ2 and MXZ2 are good choices and are used only at the start up time. The TIP/RING reversal indicator in the SK70725 does not have any meaning in mode 0, as the transparent mode needed to work with LXP730. This procedure can be left in the code for the future SK70725 revision. The procedure also shows how to handle BELB from the CPE end.

#### **TIP/RING Reversal Procedure:**

- 1. Start.

- 2. Initialize the LXP730s for required configuration.

- 3. Activate the SK70725s.

- 4. Send the test pattern MXZ2 from the NTU side. MXZ2 = AAh.

- 5. If DXZ2 = AAh is received on LTU TIP/RING lines are straight and system is ready for transmission. Go to step 7.

- 6. Otherwise if DXZ2 = 55h, set B7 to 1 in register WR2 of SK70725 (Address 02, data 80h). Set bit B0 to 0 in register 24h of LXP730 to stop it and then set this bit back to 1 to re-start. The framer needs to be restarted to recognize the new sync word. TIP/RING lines are reversed and corrected for in the SK70725, and the system is ready for transmission.