These drawings and specifications are the property of Densitron International and may not be reproduced, copied or used without written permission

|      | REVISIONS   |      |          |  |  |  |  |  |  |

|------|-------------|------|----------|--|--|--|--|--|--|

| REV. | DESCRIPTION | DATE | APPROVED |  |  |  |  |  |  |

|      |             |      |          |  |  |  |  |  |  |

- 1. Specification subject to change without notice.

- 2. All dimensions and specifications apply to standard modules. This information may vary for modules with optional features.

- 3. All dimensions are in millimetres.

- 4. Precautions: These precautions apply equally to modules from all makers, not just Densitron. Violation of these guidelines may void the warranty and can cause problems ranging from erratic operation to catastrophic display failure.

#### Handling precautions:

• This device is susceptible to Electro-Static Discharge (ESD) damage. Observe Anti-Static precautions.

### Power supply precautions:

- ♦ Identify and, at all times, observe absolute maximum ratings for both logic and LC drivers. Note that there is some variance between models.

- Prevent the application of reverse polarity to VDD and VSS, however briefly.

- ♦ Use a clean power source free from transients. Power up conditions are occasionally "jolting" and may exceed the maximum ratings of the module.

- ♦ The +5V power of the module should also supply the power to all devices that may access the display. Don't allow the data bus to be driven when the logic supply to the module is turned off.

- DO NOT install a capacitor between the VO (contrast) pin and ground. VDD must, at all times, exceed the VO voltage level. The capacitor combines with the contrast potentiometer to form an R-C network which "holds-up" VO, at power-down, possibly damaging the module.

#### Operating precautions:

- DO NOT plug or unplug the module when the system is powered up.

- Minimise the cable length between the module and host MPU. (Recommended max. length 30 cm).

- For models with EL backlights, do not disable the backlight by interrupting the HV line. Unloaded inverters produce voltage extremes that may are within a cable or at the display.

- Operate the module within the limits of the modules temperature specifications.

### ${\it Mechanical / Environmental precautions:}$

- ♦ Improper soldering is the major cause of module difficulty. Use of flux cleaner is not recommended as they may seep under the elastomeric connection and cause display failure. Densitron recommends the use of Kester "245" noclean solder.

- Mount the module so that it is free from torque and mechanical stress.

- ♦ Surface of LCD panel should not be touched or scratched. The display front surface is an easily scratched, plastic polariser. Avoid contact and clean only when necessary with soft, absorbent cotton dampened with petroleum benzene.

- ♦ ALWAYS employ anti-static procedure while handling the module.

- Prevent moisture build-up upon the module and observe the environmental constraints for storage temperature and humidity.

- ♦ DO NOT store in direct sunlight.

- ♦ If leakage of the liquid crystal material should occur, avoid contact with this material, particularly ingestion. If the body or clothing becomes contaminated by the liquid crystal material, wash thoroughly with water and soap.

**Notes:** (unless otherwise specified)

| Unless otherwise                                                          | APPROVALS | DATE |         | DENSITRON EUROPE LTD       |              |  |  |  |

|---------------------------------------------------------------------------|-----------|------|---------|----------------------------|--------------|--|--|--|

| specified:  Dimensions are mm Tolerances are: $X = \pm 3$ $0.X = \pm 0.5$ | DRAWN     |      |         |                            |              |  |  |  |

|                                                                           | CHECKED   |      | TITLE   | 33 X 100 GRAPHIC LCD MODUL | Æ            |  |  |  |

| $0.X = \pm 0.3$<br>$0.XX = \pm 0.05$                                      | ISSUED    |      | DWG.NO. | LM4900                     | SHEET 1 of 9 |  |  |  |

### 1.0 DESCRIPTION

Dot matrix display module consisting of a Liquid Crystal Display, CMOS controller-driver LSI, printed circuit board, edge type Light Emitting Diode (LED) backlight and FFC cable.

Available LC fluids types are: NTN (supertwisted nematic)

Features fast 8-bit parallel interface, on-board negative voltage generation, software contrast control, low power standby function and other useful software command functions.

**Note**: type of parallel interface is determined by hardware settings at the factory and must be specified when ordering. See Section 13.0 'PART NUMBER DESCRIPTION FOR AVAILABLE OPTIONS'.

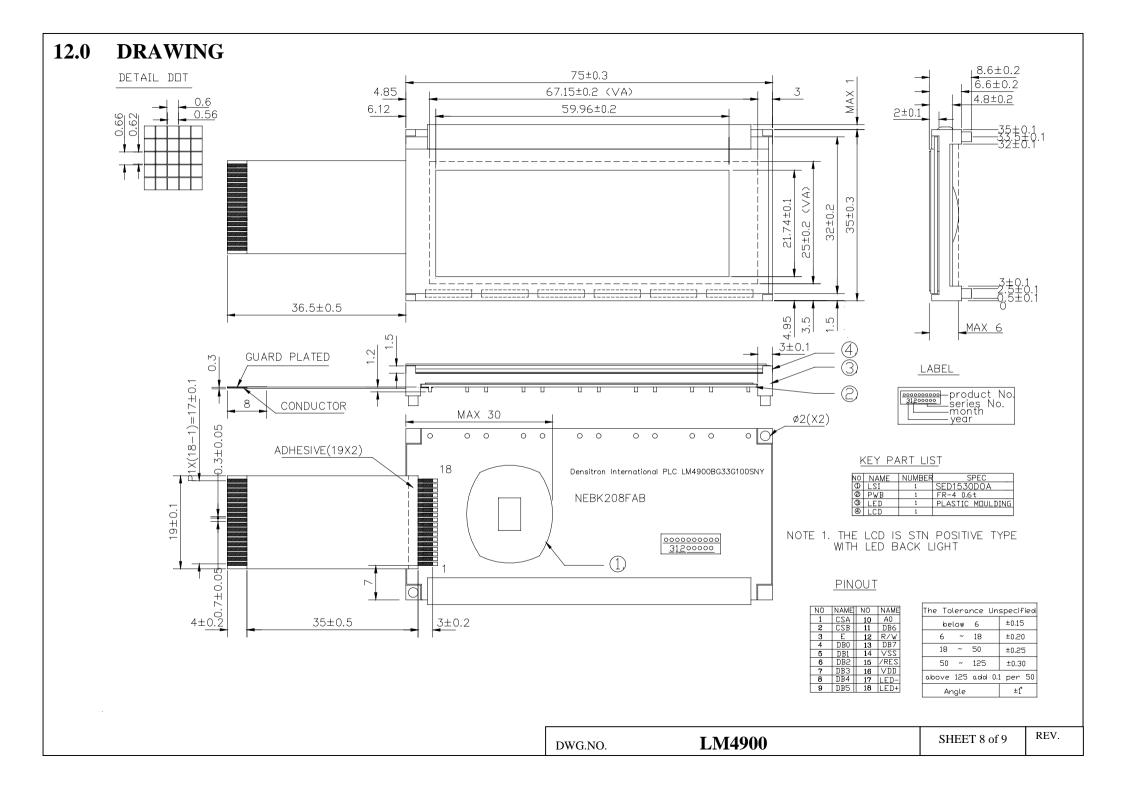

### 2.0 MECHANICAL CHARACTERISTICS

| Item                  | Specifications      | Unit       |

|-----------------------|---------------------|------------|

| Package Dimensions    | 75.0 x 35.0 x 8.6   | mm         |

| Display format        | 100x33 pixels       | -          |

| Character font format | n/a                 | dots       |

| Driving method        | 1/33 duty, 1/6 bias | duty, bias |

| Dot size              | 0.56 x 0.62         | mm         |

| Dot pitch             | 0.6 x 0.66          | mm         |

| Character Size        | n/a                 | mm         |

| Active display area   | 59.96 x 21.74       | mm         |

| Viewing area          | 67.15 x 25.0        | mm         |

| Weight                | 20 approx.          | g          |

Notes: W-Width; H-Height; D-Depth.

### 3.0 ABSOLUTE MAXIMUM RATINGS

Vss=0V;Ta=25°C

| Item                         | Symbol  | NTN  |      | N    | TN-H | Unit        |

|------------------------------|---------|------|------|------|------|-------------|

|                              |         | Min. | Max. | Min. | Max. |             |

| Logic supply voltage         | VDD-VSS | 0    | 7    | -    | -    | V           |

| LC driver supply voltage     | VDD-VO  | 0    | 6    | -    | -    | V           |

| Operating temperature        | Тор     | -10  | +60  | -    | -    | °C          |

| Storage temperature (Note 1) | Tst     | -20  | +70  | -    | -    |             |

| Humidity: Operating (@40°C)  | -       | -    | 85%  | -    | -    | RH (Note 2) |

| Non-operating (@40°C)        | -       | -    | 95%  | -    | -    | RH (Note 2) |

Notes: 1: Tested to 100 hrs.

2: Refers to non-condensing conditions.

### 4.0 ELECTRICAL CHARACTERISTICS

VDD=5±0.25V;Ta=25°C

| Item                 | Symbol | Test Condition | Min.      | Тур. | Max.      | Unit |

|----------------------|--------|----------------|-----------|------|-----------|------|

| Input "High" voltage | Vih    | =              | 0.7 x Vdd | =    | Vdd       | V    |

| Input "Low" voltage  | VIL    | -              | Vss       | -    | 0.3 x Vdd | V    |

| Power supply current | Idd    | VDD=5.0V       | -         | 1    | -         | mA   |

# **5.0 RECOMMENDED LC DRIVE VOLTAGE (VDD-Vo)**

Display contrast is software selectable via the controller (see 'Electronic Volume Register Set' in Section 8).

|  | DWG.NO. | LM4900 | SHEET 2 of 9 | REV. |

|--|---------|--------|--------------|------|

|--|---------|--------|--------------|------|

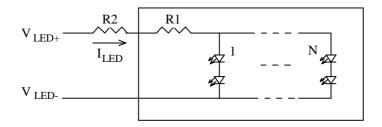

# **6.0 BACKLIGHT SPECIFICATIONS:**

Ta=20°C,60%RH,Darkroom.

| Item                               | Symbol    | Тур.                    | Max | Unit   |

|------------------------------------|-----------|-------------------------|-----|--------|

| LED input voltage                  | $V_{LED}$ | 6                       | 8   | V      |

| LED input current                  | $I_{LED}$ | 90                      | 180 | mA     |

| Built-in current limiting resistor | R1        | n/a                     | =   | Ohm,W  |

| External current limiting resistor | R2        | 10 (Vdd=5V)<br>(Vdd=3V) | -   | Ohm, W |

| Number of nodes                    | N         | 6                       | -   | -      |

# 7.0 INTERFACE DESCRIPTION

| Pin No | Symbol           | I/O | Function                                                                                                                                                                                                                    |

|--------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CS1              | I   | Chip Select 1 (active low)                                                                                                                                                                                                  |

| 2      | CS2              | I   | Chip Select 2                                                                                                                                                                                                               |

| 3      | E(RD)            | I   | Enable clock (6800 MPU)<br>Read (8080 MPU)                                                                                                                                                                                  |

| 4      | DB0              | I/O |                                                                                                                                                                                                                             |

| 5      | DB1              | I/O |                                                                                                                                                                                                                             |

| 6      | DB2              | I/O | Data bits 0 - 5                                                                                                                                                                                                             |

| 7      | DB3              | I/O | Data offs 0 - 3                                                                                                                                                                                                             |

| 8      | DB4              | I/O |                                                                                                                                                                                                                             |

| 9      | DB5              | I/O |                                                                                                                                                                                                                             |

| 10     | A0               | I   | <ul> <li>Command/display data flag input. This is connected to the LSB of the MPU address bus</li> <li>When LOW, the data on DB0 – DB7 is command data</li> <li>When HIGH, the data on DB0 – DB7 is display data</li> </ul> |

| 11     | DB6              | I/O | Data bit 6                                                                                                                                                                                                                  |

| 12     | $R/\overline{W}$ | I   | Read/Write (6800 MPU) Write (8080 MPU)                                                                                                                                                                                      |

| 13     | DB7              | I/O | Data bit 7                                                                                                                                                                                                                  |

| 14     | Vss              | -   | Ground                                                                                                                                                                                                                      |

| 15     | RES              | I   | Reset (active low)                                                                                                                                                                                                          |

| 16     | Vdd              | -   | Power supply                                                                                                                                                                                                                |

| 17     | LED-             | -   | LED backlight cathode                                                                                                                                                                                                       |

| 18     | LED+             | -   | LED backlight anode                                                                                                                                                                                                         |

| DWG.NO. | LM4900 | SHEET 3 of 9 | REV. |

|---------|--------|--------------|------|

#### 8.0 **COMMAND SET**

Note: this command set is for 80-series MPU.

| Command                          | Code |       |    |     |     |      |      |                                       | Function           |          |                                                             |                                                                                                            |  |  |  |  |  |      |                                                                                     |

|----------------------------------|------|-------|----|-----|-----|------|------|---------------------------------------|--------------------|----------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|------|-------------------------------------------------------------------------------------|

| Command                          | A0   | RD    | WR | D7  | D6  | D5   | D4   | D3                                    | D2                 | D1       | D0                                                          | Function                                                                                                   |  |  |  |  |  |      |                                                                                     |

| Display ON/OFF                   | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 1                                     | 1                  | 1        | 0                                                           | Turns the LCD display on and off. "0": OFF "1": ON                                                         |  |  |  |  |  |      |                                                                                     |

| Display start line set           | 0    | 1     | 0  | 0   | 1   |      | D    | isplay st                             | art addr           | ess      |                                                             | Determines the RAM display line displayed to COM0                                                          |  |  |  |  |  |      |                                                                                     |

| Page address set                 | 0    | 1     | 0  | 1   | 0   | 1    | 1    |                                       | Page a             | address  |                                                             | Sets the display RAM page to the page address register                                                     |  |  |  |  |  |      |                                                                                     |

| Column address set, first 4 bits | 0    | 1     | 0  | 0   | 0   | 0    | 1    | Мо                                    | st signif<br>addre | icant co | lumn                                                        | Sets the 4 most significant bits of the<br>display RAM column address to the<br>register                   |  |  |  |  |  |      |                                                                                     |

| Column address set, last 4 bits  | 0    | 1     | 0  | 0   | 0   | 0    | 0    | Least significant column address bits |                    |          |                                                             |                                                                                                            |  |  |  |  |  | lumn | Sets the 4 least significant bits of the display RAM column address to the register |

| Status read                      | 0    | 0     | 1  |     | Sta | atus |      | 0                                     | 0                  | 0        | 0                                                           | Read status data.                                                                                          |  |  |  |  |  |      |                                                                                     |

| Write display data               | 1    | 1     | 0  |     |     |      | Writ | e data                                |                    |          |                                                             | Writes to the display RAM                                                                                  |  |  |  |  |  |      |                                                                                     |

| Read display data                | 1    | 0     | 1  |     |     |      | Read | d data                                |                    |          |                                                             | Reads from the display RAM                                                                                 |  |  |  |  |  |      |                                                                                     |

| ADC select                       | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 0                                     | 0                  | 0        | 0                                                           | Sets the relationship between the<br>display RAM address and the SEG<br>output<br>"0": Normal "1": Reverse |  |  |  |  |  |      |                                                                                     |

| Display: Normal/Reverse          | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 0                                     | 1                  | 1        | 0                                                           | Sets 'inverted video mode'. "0": Normal "1": Reverse                                                       |  |  |  |  |  |      |                                                                                     |

| Display: All Pixel Lit: On/Off   | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 0                                     | 1                  | 0        | 0                                                           | Display: All pixels lit "0": Normal "1": all pixels ON                                                     |  |  |  |  |  |      |                                                                                     |

| LCD bias set                     | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 0                                     | 0                  | 1        | 0                                                           | Sets the LCD drive voltage ratio                                                                           |  |  |  |  |  |      |                                                                                     |

| Read/Modify/Write                | 0    | 1     | 0  | 1   | 1   | 1    | 0    | 0                                     | 0                  | 0        | 0                                                           | Increments the column address<br>counter by 1 when write, zero when<br>read                                |  |  |  |  |  |      |                                                                                     |

| End                              | 0    | 1     | 0  | 1   | 1   | 1    | 0    | 0                                     | 0                  | 1        | 0                                                           | Gets out of read/modify/write mode                                                                         |  |  |  |  |  |      |                                                                                     |

| Reset                            | 0    | 1     | 0  | 1   | 1   | 1    | 0    | 1                                     | 1                  | 1        | 0                                                           | Internal reset                                                                                             |  |  |  |  |  |      |                                                                                     |

| Output mode register set         | 0    | 1     | 0  | 1   | 1   | 0    | 0    | 0                                     | *                  | *        | *                                                           | Selects the direction of the COM output scan * = disabled                                                  |  |  |  |  |  |      |                                                                                     |

| Power control set                | 0    | 1     | 0  | 0   | 0   | 1    | 0    | 1                                     | 1                  | 1        | 1                                                           | Switches internal power supply ON                                                                          |  |  |  |  |  |      |                                                                                     |

| Electronic volume register set   | 0    | 1     | 0  | 1   | 0   | 0    |      | Electronic volume level               |                    |          | Sets LCD contrast. Recommend 00101 for 5V version at 25 °C. |                                                                                                            |  |  |  |  |  |      |                                                                                     |

| Standby set                      | 0    | 1     | 0  | 1   | 0   | 1    | 0    | 1                                     | 1                  | 0        | 0<br>1                                                      | Selects the standby mode "0": OFF "1": ON                                                                  |  |  |  |  |  |      |                                                                                     |

| Power save                       |      | FEODE |    | ONU | 1   |      |      |                                       |                    |          |                                                             | A composite command with display:<br>OFF and display: All pixels ON.                                       |  |  |  |  |  |      |                                                                                     |

NOTE:

- 'ADC select' must be set BEFORE 'Display ON' command.

Do not use any command that is not described above, or a system malfunction may result.

- 3. For a detailed description of the SED1530 controller-driver IC refer to Seiko-Epson manual (available from Epson and Densitron websites).

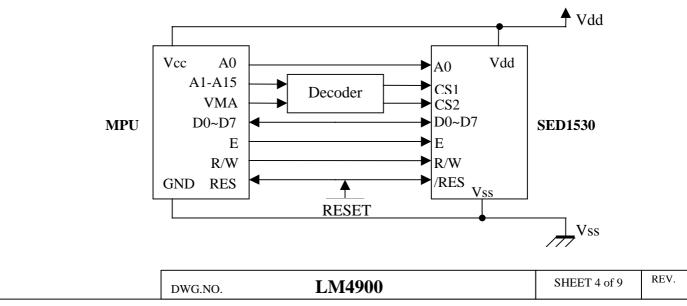

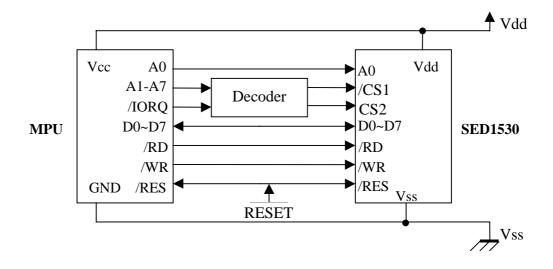

#### 9.0 **BLOCK DIAGRAM**

# 6800 series MPU

# 8080 MPU

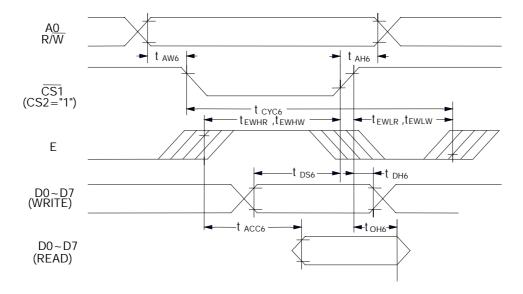

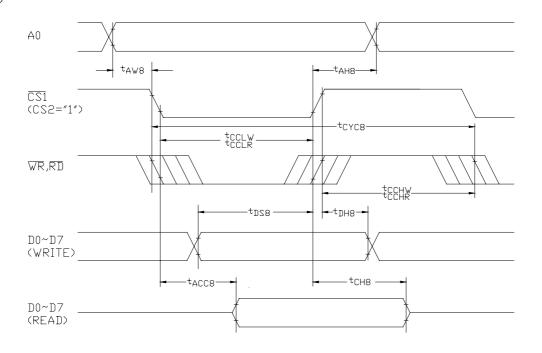

# 10.0 TIMING CHARACTERISTICS

# 6800 MPU

|                    |       |                  |                     | VDD = 5.0  | OV ± 10% | $6, T_a = -10$ | ) to 85 °C |

|--------------------|-------|------------------|---------------------|------------|----------|----------------|------------|

| Para               | meter | Signal           | Symbol              | Conditions | Min      | Max            | Unit       |

| System cycle time  | e     |                  | t <sub>CYC6</sub>   |            | 200      | -              | ns         |

| Address set up tii | me    | A0               | $t_{AW6}$           |            | 10       | -              | ns         |

| Address hold time  |       | $R/\overline{W}$ | $t_{AH6}$           |            | 10       | -              | ns         |

| Data setup time    |       |                  | $t_{ m DS6}$        |            | 20       | -              | ns         |

| Data hold time     |       | D0 ~ D7          | $t_{\mathrm{DH6}}$  |            | 10       | -              | ns         |

| Output disable tir | ne    | D0 ~ D7          | $t_{ m OH6}$        | CL=100pF   | 10       | 50             | ns         |

| Access time        |       |                  | $t_{ACC6}$          | CL_100pr   | -        | 70             | ns         |

| Enable H           | Read  | Е                | $t_{\rm EWHR}$      |            | 77       | -              | ns         |

| Pulse width        | Write | E                | $t_{\mathrm{EWHW}}$ |            | 22       | -              | ns         |

| Enable L           | Read  | Е                | $t_{EWLR}$          |            | 117      | -              | ns         |

| Pulse width        | Write | E                | $t_{EWLW}$          |            | 172      | -              | ns         |

| DWG.NO. | LM4900 | SHEET 5 of 9 | REV. |

|---------|--------|--------------|------|

|---------|--------|--------------|------|

|                         |                     |                  |                   |            |     | VDD=3.0V. Ta = - 10 to 85 C |      |  |  |

|-------------------------|---------------------|------------------|-------------------|------------|-----|-----------------------------|------|--|--|

| Parameter               |                     | Signal           | Symbol            | Conditions | Min | Max                         | Unit |  |  |

| System cycle time       |                     |                  | t <sub>CYC6</sub> |            | 450 | -                           | ns   |  |  |

| Address setup time      |                     | A0               | $t_{AW6}$         |            | 25  | -                           | ns   |  |  |

| Address hold time       |                     | $R/\overline{W}$ | $t_{AH6}$         |            | 25  | -                           | ns   |  |  |

| Data setup time         |                     |                  | $t_{ m DS6}$      |            | 40  | -                           | ns   |  |  |

| Data hold time          |                     | D0 ~ D7          | $t_{ m DH6}$      |            | 20  | -                           | ns   |  |  |

| Output disable ti       | Output disable time |                  | t <sub>OH6</sub>  | CL=100pF   | 20  | 50                          | ns   |  |  |

| Access time             | Access time         |                  | $t_{ACC6}$        | CL_100pr   | -   | 70                          | ns   |  |  |

| Enable H                | Read                | _                | $t_{\rm EWHR}$    |            | 194 | -                           | ns   |  |  |

| Pulse width             |                     | Е                |                   |            |     |                             | ns   |  |  |

|                         | Write               |                  | $t_{\rm EWHW}$    |            | 44  | -                           |      |  |  |

| Enable L<br>Pulse width | Read                | Е                | $t_{\rm EWLR}$    |            | 244 | _                           | ns   |  |  |

|                         | Write               | L                | t <sub>EWLW</sub> |            | 394 | -                           | ns   |  |  |

<sup>\*1.</sup> The input signal rise time and fall time (tr, tf) are specified at 15 ns or less. When the cycle time is used at high speed, the specification is

# 8080 MPU

|                            |                        |                   |                  | $V_{DD} = 5V \pm 109$ | %, Ta= -10 °C ~ | - +60 °C |

|----------------------------|------------------------|-------------------|------------------|-----------------------|-----------------|----------|

| Item                       | Signal                 | Symbol            | Condition        | Specificat            | Unit            |          |

| rtem                       | Digital                |                   |                  | Min.                  | Max.            |          |

| Address hold time          | A0, CS                 | t <sub>AH8</sub>  |                  | 10                    |                 |          |

| Address setup time         |                        | $t_{ m AW8}$      |                  | 10                    |                 |          |

| System cycle time          |                        | $t_{\rm CYC8}$    |                  | 166                   |                 |          |

| Control L pulse width (WR) | WR                     | $t_{CCLW}$        |                  | 30                    |                 |          |

| Control L pulse width (RD) | $\overline{\text{RD}}$ | $t_{CCLR}$        |                  | 70                    |                 |          |

| Control H pulse width (WR) | $\frac{RD}{WR}$        | $t_{CCHW}$        |                  | 100                   |                 | nS       |

| Control H pulse width (RD) | $\frac{WK}{RD}$        | $t_{CCHR}$        |                  | 70                    |                 |          |

| Data setup time            |                        | t <sub>DS8</sub>  |                  | 20                    |                 |          |

| Data hold time             |                        | $t_{ m DH8}$      |                  | 10                    |                 |          |

| /RD access time            | D0~D7                  | t <sub>ACC8</sub> | $C_{L} = 100 pF$ |                       | 70              | ]        |

| Output disable time        |                        | $t_{ m CH8}$      |                  | 10                    | 50              |          |

| DWG.NO. LM4 | 00 | SHEET 6 of 9 | REV. |

|-------------|----|--------------|------|

|-------------|----|--------------|------|

tr + tf ≤ (t<sub>CYC6</sub> − t<sub>EWLW</sub>- t<sub>EWHW</sub>) or is tr + tf ≤ (t<sub>CYC6</sub> − t<sub>EWLR</sub>- t<sub>EWHR</sub>)

\*2. All timings are specified based on 20% and 80% of V<sub>DD</sub>.

\*3. t<sub>EWHR</sub> and t<sub>EWHW</sub> are specified by the overlap period of CS1 = "0" (CS2 = "1") and E = "1" level.

| $V_{\rm DD} = 3V \pm 10\%$ , Ta= -10 °C ~ - |                          |                |                  |      |      |    |

|---------------------------------------------|--------------------------|----------------|------------------|------|------|----|

| Item                                        | Signal                   | Symbol         | Condition        | Spe  | Unit |    |

| Item                                        |                          |                |                  | Min. | Max. |    |

| Address hold time                           | A0, CS                   | $t_{AH8}$      |                  | 19   |      |    |

| Address setup time                          | Au, CS                   | $t_{ m AW8}$   |                  | 15   |      |    |

| System cycle time                           |                          | $t_{\rm CYC8}$ |                  | 450  |      |    |

| Control L pulse width (WR)                  | WR                       | $t_{CCLW}$     |                  | 60   |      |    |

| Control L pulse width (RD)                  | $\overline{\mathrm{RD}}$ | $t_{CCLR}$     |                  | 140  |      |    |

| Control H pulse width (WR)                  | $\frac{RD}{WR}$          | $t_{CCHW}$     |                  | 200  |      | nS |

| Control H pulse width (RD)                  | $\frac{WK}{RD}$          | $t_{CCHR}$     |                  | 140  |      |    |

| Data setup time                             |                          | $t_{ m DS8}$   |                  | 40   |      |    |

| Data hold time                              |                          | $t_{ m DH8}$   |                  | 15   |      |    |

| /RD access time                             | D0~D7                    | $t_{ACC8}$     | $C_{L} = 100 pF$ |      | 140  |    |

| Output disable time                         | ע~טע/                    | $t_{CH8}$      |                  | 10   | 100  |    |

Notes: 1.  $t_r + t_f \le (t_{CYC8} - t_{CCLW} - t_{CCHW})$  or  $t_r + t_f \le (t_{CYC8} - t_{CCLR} - t_{CCHR})$  at all times. 2. For timing purposes, LOW=20% Vdd, HIGH=80% Vdd.

3. READ/WRITE operation is performed while CS (/CS1 and CS2) is active and RD (WR) signal is LOW.

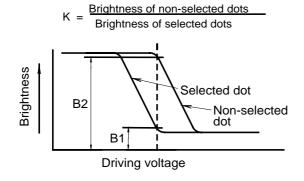

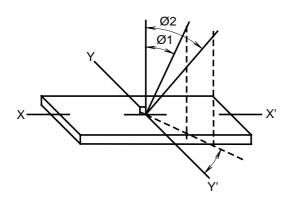

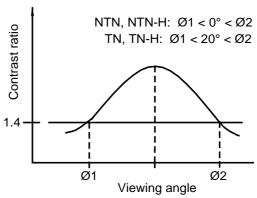

# 11.0 OPTICAL CHARACTERISTICS

| Item               | Symbol | Test Condition         | Min. | Тур. | Max. | Unit |

|--------------------|--------|------------------------|------|------|------|------|

| Contrast ratio STN | K      | Ø=20° θ=0°             | 5    | -    | -    | -    |

| Viewing angle STN  | Ø2-Ø1  | θ=0° K <u>&gt;</u> 1.4 | 40   | -    | -    | Deg. |

|                    | θ      | Ø=20° K=1.4            | ±30  | -    | -    | Deg. |

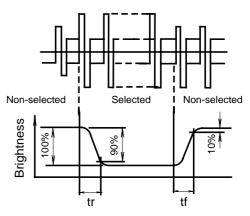

| Response time Rise | tr     | Ø=20° θ=0°             | -    | 150  | 250  | mS   |

| Fall               | tf     | Ø=20° θ=0°             | -    | 150  | 250  | mS   |

### DEFINITION OF CONTRAST RATIO (K)

#### DEFINITION OF ANGLES Ø AND

#### CONTRAST VERSUS VIEWING ANGLE

#### **DEFINITION OF OPTICAL RESPONSE**

REV.

SHEET 7 of 9 LM4900 DWG.NO.

# 13.0 PART NUMBER DESCRIPTION FOR AVAILABLE OPTIONS

# LM4900 @ 233G100 @ 4 \$ /X/Y

① Polariser Type

B = Transflective: light background with backlight

2 LED Backlight Color

G = Yellow-green (standard)

**3** Fluid Type and Power Supply

S = NTN with +5VDC operation

4 Fluid Type

N = STN

**S** Background Color for STN Fluid

G = Gray background

Y = Yellow background

/X Operating Voltage

Blank = 5V DC

/3V = 3V DC

/Y Interface Type

Blank = 6800 MPU

/80 = 8080 MPU

DWG.NO. **LM4900** SHEET 9 of 9 REV.