# **KH205**

# Overdrive-Protected Wideband Op Amp

## **Features**

- -3dB bandwidth of 170MHz

- 0.1% settling in 22ns

- Complete overdrive protection

- Low power: 570mW (190mW at ±5V)

- 3MΩ input resistance

- Output may be current limited

- Direct replacement for CLC205

# **Applications**

- Fast, precision A/D conversion

- Automatic test equipment

- Input/output amplifiers

- Photodiode, CCD preamps

- IF processors

- High-speed modems, radios

- Line drivers

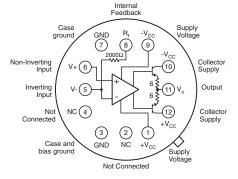

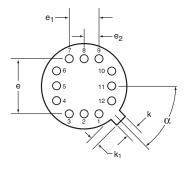

#### **Bottom View**

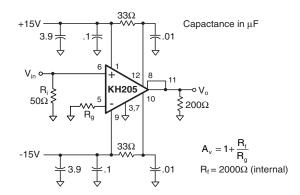

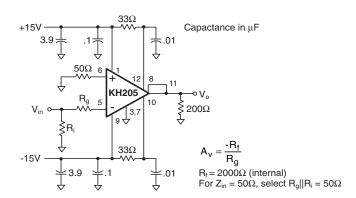

Pin 8 provides access to a  $2000\Omega$  feedback resistor which can be connected to the output or left open if an external feedback resistor is desired.

# **General Description**

The KH205 is a wideband overdrive-protected operational amplifier designed for applications needing both speed and low power operation. Utilizing a well-established current feedback architecture, the KH205 exhibits performance far beyond that of conventional voltage feedback op amps. For example, the KH205 has a bandwidth of 170MHz at a gain of +20 and settles to 0.1% in 22ns. Plus, the KH205 has a combination of important features not found in other high-speed op amps.

For example, the KH205 has been designed to consume little power – 570 mW at  $\pm 15 \text{V}$  supplies. The result is lower power supply requirements and less system-level heat dissipation. In addition, the device can be operated on supply voltages as low as  $\pm 5 \text{V}$  for even lower power dissipation.

Complete overdrive protection has been designed into the part. This is critical for applications, such as ATE and instrumentation, which require protection from signal levels high enough to cause saturation of the amplifier. This feature allows the output of the op amp to be protected against short circuits using techniques developed for low-speed op amps. With this capability, even the fastest signal sources can feature effective short circuit protection.

The KH205 is constructed using thin film resistor/bipolar transistor technology, and is available in the following versions:

| Κŀ | 1205AI  | -25°C to +85°C  | 12-pin TO-8 can                                                                           |

|----|---------|-----------------|-------------------------------------------------------------------------------------------|

| Kŀ | 1205AK  | -55°C to +125°C | 12-pin TO-8 can, features burn-in & hermetic testing                                      |

| Kŀ | 1205AM  | -55°C to +125°C | 12-pin TO-8 can,<br>environmentally<br>screened and electrically<br>tested to MIL-STD-883 |

| Κŀ | 1205HXC | -55°C to +125°C | SMD#: 5962-9083501HXC                                                                     |

| Κŀ | 1205HXA | -55°C to +125°C | SMD#: 5962-9083501HXA                                                                     |

# **Typical Performance**

|                         | Gain Setting |     |     |     |     |     |       |

|-------------------------|--------------|-----|-----|-----|-----|-----|-------|

| Parameter               | +7           | +20 | +50 | -1  | -20 | -50 | Units |

| -3dB bandwidth          | 220          | 170 | 80  | 220 | 130 | 80  | MHz   |

| rise time               | 1.7          | 2.2 | 4.7 | 1.7 | 2.9 | 4.7 | ns    |

| slew rate               | 2.4          | 2.4 | 2.4 | 2.4 | 2.4 | 2.4 | V/ns  |

| settling time (to 0.1%) | 22           | 22  | 20  | 21  | 20  | 19  | ns    |

KH205 Electrical Characteristics (A<sub>v</sub> = +20V, V<sub>CC</sub> =  $\pm$ 15V, R<sub>L</sub> = 200 $\Omega$ , R<sub>f</sub> = 2k $\Omega$ ; unless specified)

| PARAMETERS CONDITIONS                        |                                       | TYP        | MIN & MAX RATINGS |              |              | UNITS          | SYM        |

|----------------------------------------------|---------------------------------------|------------|-------------------|--------------|--------------|----------------|------------|

| Ambient Temperature                          | KH205AI                               | +25°C      | -55°C             | +25°C        | +125°C       |                |            |

| Ambient Temperature                          | KH205AK/AM/HXC/HXA                    | +25°C      | -55°C             | +25°C        | +125°C       |                |            |

| FREQUENCY DOMAIN RESPONSE                    |                                       |            |                   |              |              |                |            |

| + -3dB bandwidth                             | $V_0 = \langle 2V_{pp} \rangle$       | 170        | >140              | >140         | >125         | MHz            | SSBW       |

| large-signal bandwidth                       | $V_0 = \langle 10V_{pp} \rangle$      | 100        | >72               | >80          | >80          | MHz            | FPBW       |

| gain flatness                                | $V_0 = <2V_{pp}$<br>0.1 to 35MHz      | _          | -0.0              | -0.0         | -0 E         | ٩D             | GFPL       |

| <ul><li>peaking</li><li>peaking</li></ul>    | >35MHz                                | 0 0        | <0.3<br><0.5      | <0.3<br><0.5 | <0.5<br><0.8 | dB<br>dB       | GFPH       |

| t rolloff                                    | at 70MHz                              |            | <0.8              | <0.3         | <0.8         | dB<br>dB       | GFR        |

| group delay                                  | to 70MHz                              | 3.0 ± .2   | -                 | -            | -            | ns             | GD         |

| linear phase deviation                       | to 70MHz                              | 0.8        | <3.0              | <2.0         | <3.0         | 0              | LPD        |

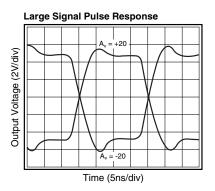

| TIME DOMAIN RESPONSE                         |                                       |            |                   |              |              |                |            |

| rise and fall time                           | 2V step                               | 2.2        | <2.6              | <2.6         | <3.0         | ns             | TRS        |

|                                              | 10V step                              | 4.8        | <5.5              | <5.5         | <5.5         | ns             | TRL        |

| settling time to 0.1%                        | 10V step, note 2                      | 22         | <27               | <27          | <27          | ns             | TS         |

| to 0.05%                                     | 10V step, note 2                      | 24<br>7    | <30               | <30          | <30          | ns<br>o/       | TSP        |

| overshoot<br>slew rate                       | 5V step<br>20V <sub>pp</sub> at 50MHz | 2.4        | <14<br>>1.8       | <14<br>>2.0  | <14<br>>2.0  | %<br>V/ns      | OS<br>SR   |

| NOISE AND DISTORTION RESPONSE                | - рр                                  |            |                   |              |              |                |            |

| + 2nd harmonic distortion                    | 2V <sub>pp</sub> , 20MHz              | -57        | <-50              | <-50         | <-50         | dBc            | HD2        |

| + 3rd harmonic distortion                    | 2V <sub>pp</sub> , 20MHz              | -68        | <-55              | <-55         | <-55         | dBc            | HD3        |

| equivalent input noise                       | bb,                                   |            |                   |              |              |                |            |

| voltage                                      | >100kHz                               | 2.1        | <3.0              | <3.0         | <3.5         | nV/√Hz         | VN         |

| inverting current                            | >100kHz                               | 22         | <30               | <30          | <35          | pA/√Hz         | ICN        |

| non-inverting current                        | >100kHz                               | 4.8        | <6.5              | <6.5         | <7.5         | pA/√Hz         | NCN        |

| noise floor                                  | >100kHz                               | -157       | <-154             | <-154        | <-153        | dBm(1Hz)       |            |

| integrated noise                             | 1kHz to 150MHz                        | 39         | <55               | <55          | <61          | μV             | INV        |

| noise floor<br>integrated noise              | >5MHz<br>5MHz to 150MHz               | -157<br>39 | <-154<br><55      | <-154<br><55 | <-153<br><61 | dBm(1Hz)<br>μV | SNF<br>INV |

| STATIC, DC PERFORMANCE                       |                                       |            |                   |              |              | P              |            |

| * input offset voltage                       |                                       | 3.5        | <8.0              | <8.0         | <11.0        | mV             | VIO        |

| average temperature coefficient              |                                       | 11         | <25               | <25          | <25          | μV/°C          | DVIO       |

| * input bias current                         | non-inverting                         | 3.0        | <25               | <15          | <15          | μA             | IBN        |

| average temperature coefficient              |                                       | 15         | <100              | <100         | <100         | nÀ/°C          | DIBN       |

| * input bias current                         | inverting                             | 2.0        | <22               | <10          | <25          | μΑ             | IBI        |

| average temperature coefficient              |                                       | 20         | <150              | <150         | <150         | nA/°C          | DIBI       |

| * power supply rejection ratio               |                                       | 69         | >55               | >55          | >55          | dB             | PSRR       |

| common mode rejection ratio * supply current | no load                               | 60<br>19   | >50<br><20        | >50<br><20   | >50<br><22   | dB<br>mA       | CMRR       |

| MISCELLANEOUS PERFORMANCE                    | 110 1000                              | 10         | \20               | \20          | \            | 1117.          | 100        |

| non-inverting input resistance               | DC                                    | 3.0        | >1.0              | >1.0         | >1.0         | MΩ             | RIN        |

| non-inverting input resistance               | 70MHz                                 | 5.0        | <7.0              | <7.0         | <7.0         | pF             | CIN        |

| output impedance                             | DC                                    |            | <0.1              | <0.1         | <0.1         | Ω              | RO         |

| output voltage range                         | no load                               | ±12        | >±11              | >±11         | >±11         | V              | VO         |

| internal feedback resistor                   |                                       |            |                   |              |              |                | -          |

| absolute tolerance                           |                                       | -          | _                 | <0.2         | _            | %              | RFA        |

| temperature coefficient                      |                                       | _          | _                 | -100 ±40     | _            | ppm/°C         | RFTC       |

| inverting input current self limit           |                                       | 2.2        | <3.0              | <3.0         | <3.2         | mA             | ICL        |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# **Absolute Maximum Ratings**

# **Recommended Operating Conditions**

$\begin{array}{ccc} V_{CC} & \pm 5 \text{V to } \pm 15 \text{V} \\ I_{o} & \pm 50 \text{mA} \\ \text{common mode input voltage} & \pm (|V_{CC}| - 5) \text{V} \\ \text{gain range} & +7 \text{ to } +50, -1 \text{ to } -50 \end{array}$

note 1:

\* AI/AK/AM/HXC/HXA

100% tested at +25°C

† AK/AM/HXC/HXA

100% tested at +25°C and at -55°C and +125°C sample tested at +25°C

**note 2:** Settling time specifications require the use of an

external feedback resistor (2 $\Omega$ )

KH205 DATA SHEET

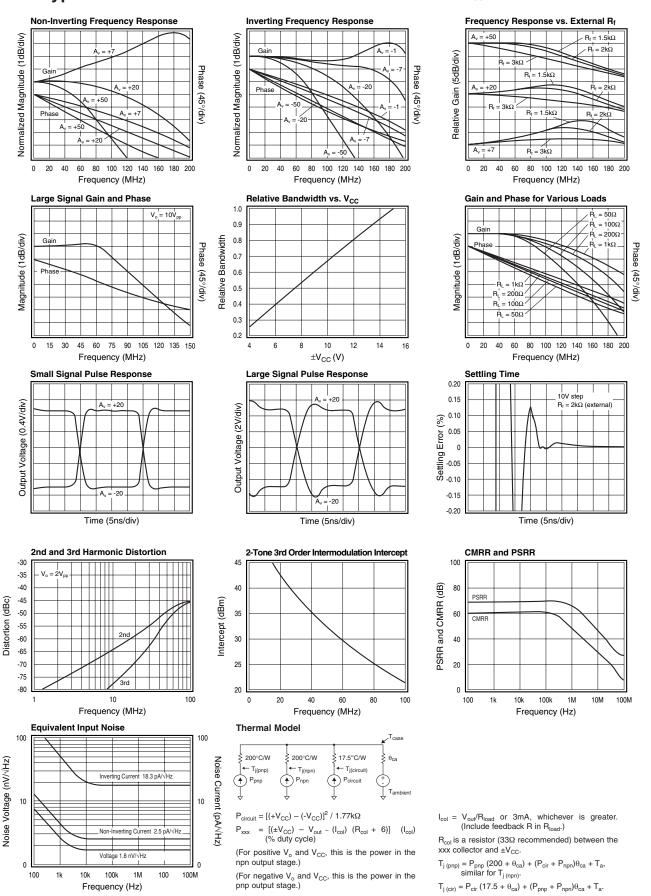

# KH205 Typical Performance Characteristics (T<sub>A</sub> = +25°C, A<sub>V</sub> = +20, V<sub>CC</sub> = ±15V, R<sub>L</sub> = 200Ω; unless specified)

REV. 1A February 2001

#### **Current Feedback Amplifiers**

Some of the key features of current feedback technology are:

- Independence of AC bandwidth and voltage gain

- Adjustable frequency response with feedback resistor

- High slew rate

- Fast settling

Current feedback operation can be described using a simple equation. The voltage gain for a non-inverting or inverting current feedback amplifier is approximated by Equation 1.

$$\frac{V_o}{V_{in}} = \frac{A_v}{1 + \frac{R_f}{Z(j\omega)}}$$

Equation 1

where:

- A<sub>v</sub> is the closed loop DC voltage gain

- R<sub>f</sub> is the feedback resistor

- Z(jω) is the CLC205's open loop transimpedance gain

- $\frac{Z(j\omega)}{R_f}$  is the loop gain

The denominator of Equation 1 is approximately equal to 1 at low frequencies. Near the -3dB corner frequency, the interaction between  $R_f$  and  $Z(j\omega)$  dominates the circuit performance. The value of the feedback resistor has a large affect on the circuits performance. Increasing  $R_f$  has the following affects:

- Decreases loop gain

- Decreases bandwidth

- Reduces gain peaking

- Lowers pulse response overshoot

- Affects frequency response phase linearity

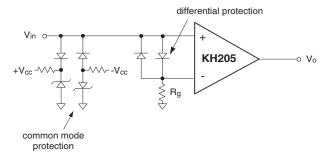

#### **Overdrive Protection**

Unlike most other high-speed op amps, the KH205 is not damaged by saturation caused by overdriving input signals (where  $V_{in}$  x gain > max.  $V_{o}$ ). The KH205 self limits the current at the inverting input when the output is saturated (see the inverting input current self limit specification); this ensures that the amplifier will not be damaged due to excessive internal currents during overdrive. For protection against input signals which would exceed either the maximum differential or common mode input voltage, the diode clamp circuits below may be used.

Figure 1: Diode Clamp Circuits for Common Mode and Differential Mode Protection

#### **Short Circuit Protection**

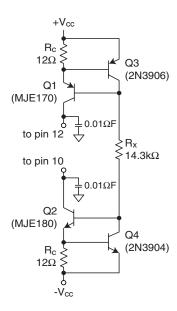

Damage caused by short circuits at the output may be prevented by limiting the output current to safe levels. The most simple current limit circuit calls for placing resistors between the output stage collector supplies and the output stage collectors (pins 12 and 10). The value of this resistor is determined by:

$$R_C = \frac{V_C}{I_I} - R_I$$

where  $I_I$  is the desired limit current and  $R_I$  is the minimum expected load resistance (0 $\Omega$  for a short to ground). Bypass capacitors of  $0.01\mu F$  on should be used on the collectors as in Figures 2 and 3.

Figure 2: Recommended Non-Inverting Gain Circuit

Figure 3: Recommended Inverting Gain Circuit

A more sophisticated current limit circuit which provides a limit current independent of  ${\sf R}_{\sf I}$  is shown in Figure 4 on page 5.

With the component values indicated, current limiting occurs at 50mA. For other values of current limit ( $I_I$ ), select  $R_C$  to equal  $V_{be}/I_I$ . Where  $V_{be}$  is the base to emitter voltage drop of Q3 (or Q4) at a current of  $[2V_{CC}-1.4]/R_x$ , where  $R_x \le [(2V_{CC}-1.4)/I_I]$   $B_{min}$ .

Also,  $B_{min}$  is the minimum beta of Q1 (or Q2) at a current of  $I_{l}$ . Since the limit current depends on  $V_{be}$ , which is temperature dependent, the limit current is likewise temperature dependent.

KH205 DATA SHEET

Figure 4: Active Current Limit Circuit (50mA)

## **Controlling Bandwidth and Passband Response**

In most applications, a feedback resistor value of  $2k\Omega$  will provide optimum performance; nonetheless, some applications may require a resistor of some other value. The response versus  $R_f$  plot on the previous page shows how decreasing  $R_f$  will increase bandwidth (and frequency response peaking, which may lead to instability). Conversely, large values of feedback resistance tend to roll off the response.

The best settling time performance requires the use of an external feedback resistor (use of the internal resistor results in a 0.1% to 0.2% settling tail). The settling

performance may be improved slightly by adding a capacitance of 0.4pF in parallel with the feedback resistor (settling time specifications reflect performance with an external feedback resistor but with no external capacitance).

## **Noise Analysis**

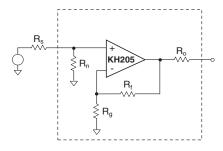

Approximate noise figure can be determined for the KH205 using the *Equivalent Input Noise* plot on page 3 and the equations shown below.

kT = 4.00 x 10<sup>-21</sup> Joules at 290°K  $V_n$  is spot noise voltage (V/ $\sqrt{Hz}$ )  $i_n$  is non-inverting spot noise current (A/ $\sqrt{Hz}$ )  $i_i$  is inverting spot noise current (A/ $\sqrt{Hz}$ )

$$F = 10 log \left[ 1 + \frac{R_s}{R_n} + \frac{R_s}{4 kT} \cdot \left( i_n^2 + \frac{V_n^2}{R_p^2} + \frac{R_f^2 i_i^2}{R_p^2 A_v^2} \right) \right]$$

where

$$R_p = \frac{R_s R_n}{R_s + R_n}$$

;  $A_v = \frac{R_f}{R_a} + 1$

Figure 5: Noise Figure Diagram and Equations (Noise Figure is for the Network Inside this Box.)

#### **Driving Cables and Capacitive Loads**

When driving cables, double termination is used to prevent reflections. For capacitive load applications, a small series resistor at the output of the KH205 will improve stability and settling performance.

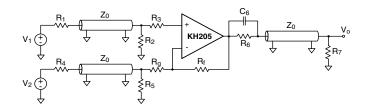

## **Transmission Line Matching**

One method for matching the characteristic impedance  $(Z_0)$  of a transmission line or cable is to place the appropriate resistor at the input or output of the amplifier. Figure 6 shows typical inverting and non-inverting circuit configurations for matching transmission lines.

Figure 6: Transmission Line Matching

Non-inverting gain applications:

- Connect R<sub>a</sub> directly to ground.

- Make  $R_1$ ,  $R_2$ ,  $R_6$ , and  $R_7$  equal to  $Z_0$ .

- Use R<sub>3</sub> to isolate the amplifier from reactive loading caused by the transmission line, or by parasitics.

Inverting gain applications:

- Connect R<sub>3</sub> directly to ground.

- Make the resistors R<sub>4</sub>, R<sub>6</sub>, and R<sub>7</sub> equal to Z<sub>0</sub>.

- Make  $R_5$  II  $R_q = Z_o$ .

The input and output matching resistors attenuate the signal by a factor of 2, therefore additional gain is needed. Use  $C_6$  to match the output transmission line over a greater frequency range.  $C_6$  compensates for the increase of the amplifier's output impedance with frequency.

## **Dynamic Range (Intermods)**

For RF applications, the KH205 specifies a third order intercept of 30dBm at 60MHz and  $P_0 = 10dBm$ . A **2-Tone, 3rd Order IMD Intercept** plot is found in the **Typical Performance Characteristics** section. The output power level is taken at the load. Third-order harmonic distortion is calculated with the formula:

$$HD3^{rd} = 2 \cdot (IP3_0 - P_0)$$

REV. 1A February 2001 5

where:

- IP3<sub>o</sub> = third-order output intercept, dBm at the load.

- $\blacksquare$  P<sub>o</sub> = output power level, dBm at the load.

- HD3<sup>rd</sup> = third-order distortion from the fundamental, -dBc.

- dBm is the power in mW, at the load, expressed in dB.

Realized third-order output distortion is highly dependent upon the external circuit. Some of the common external circuit choices that improve 3<sup>rd</sup> order distortion are:

- short and equal return paths from the load to the supplies.

- de-coupling capacitors of the correct value.

- higher load resistance.

- a lower ratio of the output swing to the power supply voltage.

#### **Printed Circuit Layout**

As with any high frequency device, a good PCB layout will enhance the performance of the KH205. Good ground plane construction and power supply bypassing close to the package are critical to achieving full performance. In the non-inverting configuration, the amplifier is sensitive to stray capacitance to ground at the inverting input. Hence, the inverting node connections should be small with minimal stray capacitance to the ground plane or other nodes. Shunt capacitance across the feedback resistor should not be used to compensate for this effect. General layout and supply bypassing play major roles in

high frequency performance. Follow the steps below as a basis for high frequency layout:

- Include 6.8μF tantalum and 0.1μF ceramic capacitors on both supplies.

- Place the 6.8µF capacitors within 0.75 inches of the power pins.

- Place the 0.1µF capacitors less than 0.1 inches from the power pins.

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitance.

- Minimize all trace lengths to reduce series inductances.

- Use flush-mount printed circuit board pins for prototyping, never use high profile DIP sockets.

Evaluation PC boards (part number 730008 for inverting, 730009 for non-inverting) for the KH205 are available to aid in device testing.

6 REV. 1A February 2001

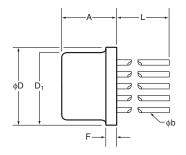

# **KH205 Package Dimensions**

| TO-8            |           |         |            |              |  |  |  |  |

|-----------------|-----------|---------|------------|--------------|--|--|--|--|

| SYMBOL          | INC       | HES     | MILIMETERS |              |  |  |  |  |

| STWDOL          | Minimun   | Maximum | Minimum    | Maximum      |  |  |  |  |

| А               | 0.142     | 0.181   | 3.61       | 4.60         |  |  |  |  |

| фЬ              | 0.016     | 0.019   | 0.41       | 0.48         |  |  |  |  |

| φD              | 0.595     | 0.605   | 15.11      | 15.37        |  |  |  |  |

| φD <sub>1</sub> | 0.543     | 0.555   | 13.79      | 14.10        |  |  |  |  |

| е               | 0.400 BSC |         | 10.16 BSC  |              |  |  |  |  |

| e <sub>1</sub>  | 0.200     | ) BSC   | 5.08 BSC   |              |  |  |  |  |

| e <sub>2</sub>  | 0.100 BSC |         | 2.54 BSC   |              |  |  |  |  |

| F               | 0.016     | 0.030   | 0.41       | 0.76         |  |  |  |  |

| k               | 0.026     | 0.036   | 0.66       | 0.91         |  |  |  |  |

| k <sub>1</sub>  | 0.026     | 0.036   | 0.66       | 0.91<br>8.64 |  |  |  |  |

| L               | 0.310     | 0.340   | 7.87       |              |  |  |  |  |

| α               | 45° BSC   |         | 45° BSC    |              |  |  |  |  |

#### NOTES:

Seal: cap weld Lead finish: gold per MIL-M-38510 Package composition: Package: metal

Lid: Type A per MIL-M-38510

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICES TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- . Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.