1

# PRODUCT OVERVIEW

## **OVERVIEW**

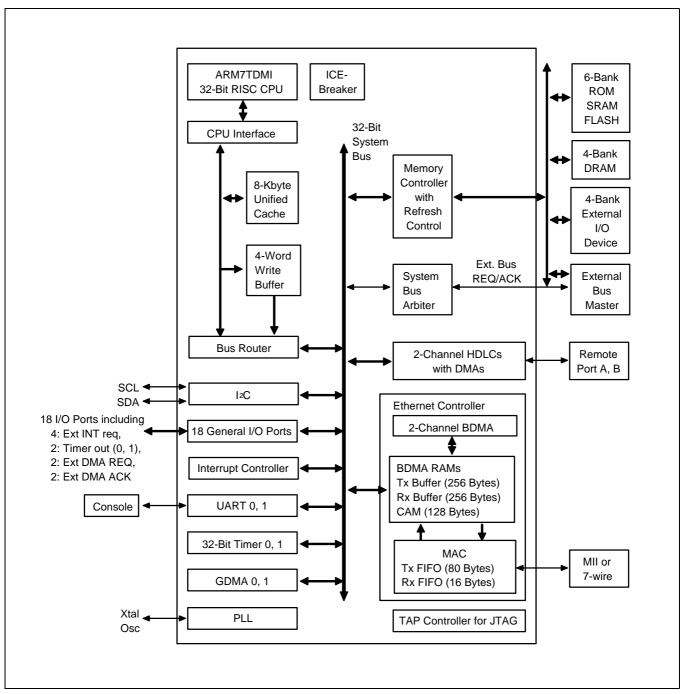

Samsung's KS32C50100 16/32-bit RISC microcontroller is a cost-effective, high-performance microcontroller solution for Ethernet-based systems. An integrated Ethernet controller, the KS32C50100, is designed for use in managed communication hubs and routers.

The KS32C50100 is built around an outstanding CPU core: the 16/32-bit ARM7TDMI RISC processor designed by Advanced RISC Machines, Ltd. The ARM7TDMI core is a low-power, general purpose microprocessor macro-cell that was developed for use in application-specific and custom-specific integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost-sensitive and power-sensitive applications.

The KS32C50100 offers a configurable 8-Kbyte unified cache/SRAM and Ethernet controller which reduces total system cost. Most of the on-chip function blocks have been designed using an HDL synthesizer and the KS32C50100 has been fully verified in Samsung's state-of-the-art ASIC test environment.

Important peripheral functions include two HDLC channels with buffer descriptor, two UART channels, 2-channel GDMA, two 32-bit timers, and 18 programmable I/O ports. On-board logic includes an interrupt controller, DRAM/ SDRAM controller, and a controller for ROM/SRAM and flash memory. The System Manager includes an internal 32-bit system bus arbiter and an external memory controller.

The following integrated on-chip functions are described in detail in this user's manual:

- 8-Kbyte unified cache/SRAM

- I<sup>2</sup>C interface

- · Ethernet controller

- HDLC

- GDMA

- UART

- Timers

- Programmable I/O ports

- Interrupt controller

### **FEATURES**

#### **Architecture**

- Integrated system for embedded ethernet applications

- Fully 16/32-bit RISC architecture

- Little/Big-Endian mode supported basically, the internal architecture is big-endian.

So, the little-endian mode only support for external memory.

- Efficient and powerful ARM7TDMI core

- Cost-effective JTAG-based debug solution

- Boundary scan

### **System Manager**

- 8/16/32-bit external bus support for ROM/SRAM, flash memory, DRAM, and external I/O

- One external bus master with bus request/ acknowledge pins

- Support for EDO/normal or SDRAM

- Programmable access cycle (0–7 wait cycles)

- Four-word depth write buffer

- Cost-effective memory-to-peripheral DMA interface

## **Unified Instruction/Data Cache**

- Two-way, set-associative, unified 8-Kbyte cache

- Support for LRU (least recently used) protocol

- · Cache is configurable as an internal SRAM

## I<sup>2</sup>C Serial Interface

- Master mode operation only

- Baud rate generator for serial clock generation

### **Ethernet Controller**

- DMA engine with burst mode

- DMA Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

- MAC Tx/Rx FIFO buffers (80 bytes Tx, 16 bytes Rx)

- Data alignment logic

- Endian translation

- 100/10-Mbit per second operation

- Full compliance with IEEE standard 802.3

- MII and 7-wire 10-Mbps interface

- Station management signaling

- On-chip CAM (up to 21 destination addresses)

- Full-duplex mode with PAUSE feature

- Long/short packet modes

- PAD generation

### **HDLCs**

- HDLC protocol features:

- Flag detection and synchronization

- Zero insertion and deletion

- Idle detection and transmission

- FCS generation and detection (16-bit)

- Abort detection and transmission

- Address search mode (expandable to 4 bytes)

- Selectable CRC or No CRC mode

- Automatic CRC generator preset

- Digital PLL block for clock recovery

- Baud rate generator

- NRZ/NRZI/FM/Manchester data formats for Tx/Rx

- Loop-back and auto-echo modes

- Tx/Rx FIFOs have 8-word (8 × 32-bit) depth

- Selectable 1-word or 4-word data transfer mode

- Data alignment logic

- Endian translation

- Programmable interrupts

- Modem interface

- Up to 10 Mbps operation

- HDLC frame length based on octets

- 2-channel DMA buffer descriptor for Tx/Rx on each HDLC

### **DMA Controller**

- 2-channel General DMA for memory-to-memory, memory-to-UART, UART-to-memory data transfers without CPU intervention

- Initiated by a software or external DMA request

- Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

- 4-data burst mode

#### **UARTs**

- Two UART (serial I/O) blocks with DMA-based or interrupt-based operation

- Support for 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit and receive

- Programmable baud rates

- 1 or 2 stop bits

- Odd or even parity

- · Break generation and detection

- Parity, overrun, and framing error detection

- ×16 clock mode

- Infra-red (IR) Tx/Rx support (IrDA)

## **Timers**

- Two programmable 32-bit timers

- Interval mode or toggle mode operation

### Programmable I/O

18 programmable I/O ports

Pins individually configurable to input, output, or I/O mode for dedicated signals

## **Interrupt Controller**

- 21 interrupt sources, including 4 external interrupt sources

- Normal or fast interrupt mode (IRQ, FIQ)

- Prioritized interrupt handling

#### **PLL**

- The external clock can be multiplied by on-chip PLL to provide high frequency system clock

- The input frequency range is 10-40MHz

- The output frequency is 5 times of input clock. To get 50MHz, input clock frequency should be 10MHz.

## **Operating Voltage Range**

• 3.3 V ± 5 %

## **Operating Temperature Range**

• 0 °C to + 70 °C

## **Operating Frequency**

• Up to 50 MHz

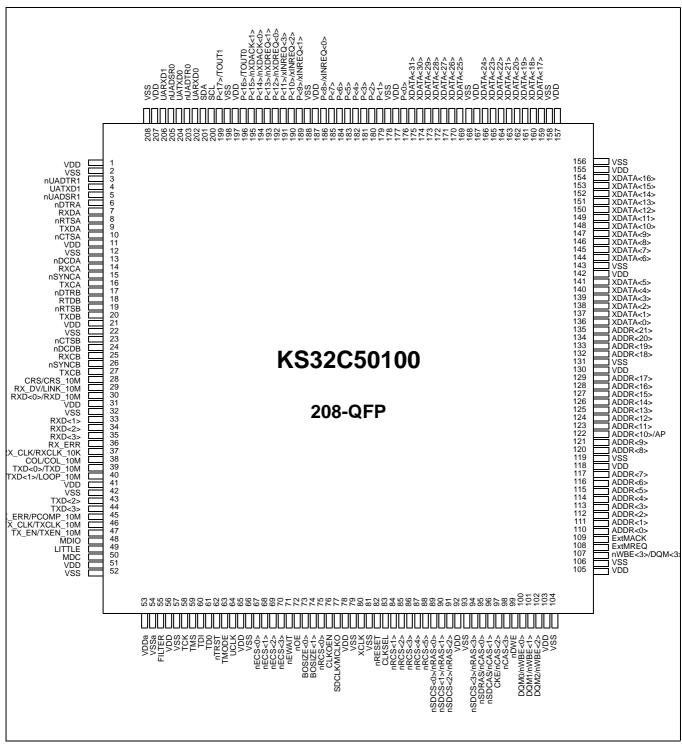

## Package Type

208 pin QFP

Figure 1-1 KS32C50100 Block Diagram

Figure 1-2 KS32C50100 Pin Assignment Diagram

# **SIGNAL DESCRIPTIONS**

Table 1-1 KS32C50100 Signal Descriptions

| Signal          | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                |  |

|-----------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XCLK            | 80      | I    | KS32C50100 System Clock source. If CLKSEL is Low, PLL output clock is used as the KS32C50100 internal system clock. If CLKSEL is High, XCLK is used as the KS32C50100 internal system clock.                                                                                                                               |  |

| MCLKO/SDCLK (1) | 77      | 0    | System Clock Out. MCLKO is monitored as the same phase of internal system clock, MCLK. SDCLK is system clock for SDRAM                                                                                                                                                                                                     |  |

| CLKSEL          | 83      | I    | Clock Select. When CLKSEL is '0'(low level), PLL output clock can be used as the master clock. When CLKSEL is '1'(high level), the XCLK is used as the master clock.                                                                                                                                                       |  |

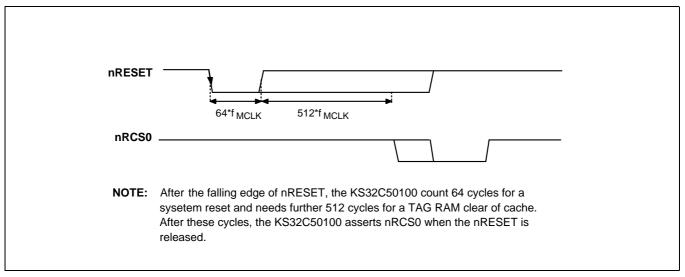

| nRESET          | 82      | I    | Not Reset. nRESET is the global reset input for the KS32C50100. TO allow a system reset, and for internal digital filtering, nRESET must be held to Low level for at least 64 master clock cycles. Refer to "Figure 3. KS32C50100 reset timing diagram" for more details about reset timing.                               |  |

| CLKOEN          | 76      | I    | Clock Out Enable/Disable. (See the pin description for MCLKO.)                                                                                                                                                                                                                                                             |  |

| TMODE           | 63      | I    | Test Mode. The TMODE bit settings are interpreted as follows: '0' = normal operating mode, '1' = chip test mode. This TMODE pin also can be used to change MF of PLL. To get 5 times internal system clock from external clock, '0'(low level) should be assigned to TMODE. If '1'(high level), MF will be changed to 6.6. |  |

| FILTER          | 55      | Al   | If the PLL is used, 820pF capacitor should be connected between the pin and analog groud.                                                                                                                                                                                                                                  |  |

| ТСК             | 58      | I    | JTAG Test Clock. The JTAG test clock shifts state information and test data into, and out of, the KS32C50100 during JTAG test operations. This pin is internally connected pull-down.                                                                                                                                      |  |

| TMS             | 59      | I    | JTAG Test Mode Select. This pin controls JTAG test operations in the KS32C50100. This pin is internally connected pull-up.                                                                                                                                                                                                 |  |

| TDI             | 60      | I    | JTAG Test Data In. The TDI level is used to serially shift test data and instructions into the KS32C50100 during JTAG test operations. This pin is internally connected pull-up.                                                                                                                                           |  |

| TDO             | 61      | 0    | JTAG Test Data Out. The TDO level is used to serially shift test data and instructions out of the KS32C50100 during JTAG test operations.                                                                                                                                                                                  |  |

| nTRST           | 62      | I    | JTAG Not Reset. Asynchronous reset of the JTAG logic. This pin is internally connected pull-up.                                                                                                                                                                                                                            |  |

Table 1-1 KS32C50100 Signal Descriptions

| Signal                                                                      | Pin No.                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------|---------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR[21:0]/<br>ADDR[10]/AP <sup>(1)</sup>                                   | 117–110,<br>129–120,<br>135–132             | O    | Address Bus. The 22-bit address bus, ADDR[21:0], covers the full 4M word address range of each ROM/SRAM, flash memory, DRAM, and the external I/O banks.  The 23-bit internal address bus used to generate DRAM address. The number of column address bits in DRAM bank can be programmed 8bits to 11bits use by DRAMCON registers.  ADDR[10]/AP is the auto precharge control pin. The auto precharge command is issued at the same time as burst read or burst write by asserting high on ADDR[10]/AP.                                                                                                                                                                                     |

| XDATA[31:0]                                                                 | 141–136,<br>154–144,<br>166–159,<br>175–169 | I/O  | External (bi-directional, 32-bit) Data Bus. The KS32C50100 data bus supports external 8-bit, 16-bit, and 32-bit bus sizes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| nRAS[3:0]/<br>nSDCS[3:0] <sup>(1)</sup>                                     | 94, 91, 90,<br>89                           | 0    | Not Row Address Strobe for DRAM. The KS32C50100 supports up to four DRAM banks. One nRAS output is provided for each bank. nSDCS[3:0] are chip select pins for SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nCAS[3:0]<br>nCAS[0]/nSDRAS<br>nCAS[1]/nSDCAS<br>nCAS[2]/CKE <sup>(1)</sup> | 98, 97, 96,<br>95                           | 0    | Not column address strobe for DRAM. The four nCAS outputs indicate the byte selections whenenver a DRAM bank is accessed. nSDRAS is row address strobe signal for SDRAM. Latches row addresses on the positive going edge of the SDCLK with nSDRAS low. Enable row access and precharge. nSDCAS is column address strobe for SDRAM. Latches column addresses on the positive going edge of the SDCLK with nSDCAS low. Enables column access. CKE is clock enable signal for SDRAM. Masks SDRAM system clock, SDCLK to freeze operation from the next clock cycle. SDCLK should be enabled at least one cycle prior to new command. Disable input buffers of SDRAM for power down in standby. |

| nDWE                                                                        | 99                                          | 0    | DRAM Not Write Enable. This pin is provided for DRAM bank write operations. (nWBE[3:0] is used for write operations to the ROM/SRAM/flash memory banks.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| nECS[3:0]                                                                   | 70, 69, 68,<br>67                           | O    | Not External I/O Chip Select. Four external I/O banks are provided for external memory-mapped I/O operations. Each I/O bank stores up to 16 Kbytes. nECS signals indicate which of the four external I/O banks is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nEWAIT                                                                      | 71                                          | I    | Not External Wait. This signal is activated when an external I/O device or ROM/SRAM/flash bank 5 needs more access cycles than those defined in the corresponding control register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nRCS[5:0]                                                                   | 88–84, 75                                   | O    | Not ROM/SRAM/Flash Chip Select. The KS32C50100 can access up to six external ROM/SRAM/Flash banks. By controlling the nRCS signals, you can map CPU addresses into the physical memory banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| B0SIZE[1:0]                                                                 | 74, 73                                      | I    | Bank 0 Data Bus Access Size. Bank 0 is used for the boot program. You use these pins to set the size of the bank 0 data bus as follows: '01' = one byte, '10' = half-word, '11' = one word, and '00' = reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 1-1 KS32C50100 Signal Descriptions

| Signal                                | Pin No.              | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nOE                                   | 72                   | 0    | Not Output Enable. Whenever a memory access occurs, the nOE output controls the output enable port of the specific memory device.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| nWBE[3:0]/<br>DQM[3:0] <sup>(1)</sup> | 107,<br>102–100      | 0    | Not Write Byte Enable. Whenever a memory write access occurs, the nWBE output controls the write enable port of the specific memory device (except for DRAM). For DRAM banks, CAS[3:0] and nDWE are used for the write operation. DQM is data input/output mask signal for SDRAM.                                                                                                                                                                                                                                                                                         |  |

| ExtMREQ                               | 108                  | I    | External Bus Master Request. An external bus master uses this pi to request the external bus. When it activates the ExtMREQ signal the KS32C50100 drives the state of external bus pins to high impedance. This lets the external bus master take control of the external bus. When it has the control, the external bus master assumes responsibility for DRAM refresh operations. The ExtMREQ signal is deactivated when the external bus master releases the external bus. When this occurs, ExtMACK goes Low level and the KS32C50100 assumes the control of the bus. |  |

| ExtMACK                               | 109                  | 0    | External Bus Acknowledge. (See the ExtMREQ pin description.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| MDC                                   | 50                   | 0    | Management Data Clock. The signal level at the MDC pin is used as a timing reference for data transfers that are controlled by the MDIO signal.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| MDIO                                  | 48                   | I/O  | Management Data I/O. When a read command is being executed, data that is clocked out of the PHY is presented on this pin. When a write command is being executed, data that is clocked out of the controller is presented on this pin for the Physical Layer Entity, PHY.                                                                                                                                                                                                                                                                                                 |  |

| LITTLE                                | 49                   | I    | Little endian mode select pin. If LITTLE is High, KS32C50100 operate in little endian mode. If Low, then in Big endian mode. Default value is low because this pin is pull-downed internally.                                                                                                                                                                                                                                                                                                                                                                             |  |

| COL/COL_10M                           | 38                   | I    | Collision Detected/Collision Detected for 10M. COL is asserted asynchronously with minimum delay from the start of a collision on the medium in MII mode. COL_10M is asserted when a 10-Mbit/s PHY detects a collision.                                                                                                                                                                                                                                                                                                                                                   |  |

| TX_CLK/<br>TXCLK_10M                  | 46                   | I    | Transmit Clock/Transmit Clock for 10M. The controller drives TXD[3:0] and TX_EN from the rising edge of TX_CLK. In MII mode, the PHY samples TXD[3:0] and TX_EN on the rising edge of TX_CLK. For data transfers, TXCLK_10M is provided by the 10-Mbit/s PHY.                                                                                                                                                                                                                                                                                                             |  |

| TXD[3:0]<br>LOOP_10M<br>TXD_10M       | 44, 43,<br>40,<br>39 | 0    | Transmit Data/Transmit Data for 10 M/Loop-back for 10M. Transmit data is aligned on nibble boundaries. TXD[0] corresponds to the first bit to be transmitted on the physical medium, which is the LSB of the first byte and the fifth bit of that byte during the next clock. TXD_10M is shared with TXD[0] and is a data line for transmitting to the 10-Mbit/s PHY. LOOP_10M is shared with TXD[1] and is driven by the loop-back bit in the control register.                                                                                                          |  |

Table 1-1 KS32C50100 Signal Descriptions

| Signal               | Pin No.           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_EN/<br>TXEN_10M   | 47                | 0    | Transmit Enable/Transmit Enable for 10M. TX_EN provides precise framing for the data carried on TXD[3:0]. This pin is active during the clock periods in which TXD[3:0] contains valid data to be transmitted from the preamble stage through CRC. When the controller is ready to transfer data, it asserts TXEN_10M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TX_ERR/<br>PCOMP_10M | 45                | 0    | Transmit Error/Packet Compression Enable for 10M. TX_ERR is driven synchronously to TX_CLK and sampled continuously by the Physical Layer Entity, PHY. If asserted for one or more TX_CLK periods, TX_ERR causes the PHY to emit one or more symbols which are not part of the valid data, or delimiter set located somewhere in the frame that is being transmitted. PCOMP_10M is asserted immediately after the packet's DA field is received. PCOMP_10M is used with the Management Bus of the DP83950 Repeater Interface Controller (from National Semiconductor). The MAC can be programmed to assert PCOMP if there is a CAM match, or if there is not a match. The RIC (Repeater Interface Controller) uses this signal to compress (shorten) the packet received for management purposes and to reduce memory usage. (See the DP83950 Data Sheet, published by National Semiconductor, for details on the RIC Management Bus.) This pin is controlled by a special register, with which you can define the polarity and assertion method (CAM match active or not match active) of the PCOMP signal. |

| CRS/CRS_10M          | 28                | I    | Carrier Sense/Carrier Sense for 10M. CRS is asserted asynchronously with minimum delay from the detection of a non-idle medium in MII mode. CRS_10M is asserted when a 10-Mbit/s PHY has data to transfer. A 10-Mbit/s transmission also uses this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RX_CLK/<br>RXCLK_10M | 37                | I    | Receive Clock/Receive Clock for 10M. RX_CLK is a continuous clock signal. Its frequency is 25 MHz for 100-Mbit/s operation, and 2.5 MHz for 10-Mbit/s. RXD[3:0], RX_DV, and RX_ERR are driven by the PHY off the falling edge of RX_CLK, and sampled on the rising edge of RX_CLK. To receive data, the TXCLK_10 M clock comes from the 10-Mbit/s PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RXD[3:0]/<br>RXD_10M | 35, 34, 33,<br>30 | I    | Receive Data/Receive Data for 10M. RXD is aligned on nibble boundaries. RXD[0] corresponds to the first bit received on the physical medium, which is the LSB of the byte in one clock period and the fifth bit of that byte in the next clock. RXD_10M is shared with RXD[0] and it is a line for receiving data from the 10-Mbit/s PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 1-1 KS32C50100 Signal Descriptions

| Signal         | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_DV/LINK_10M | 29      | I    | Receive Data Valid/Link Status for 10M. PHY asserts RX_DV synchronously, holding it active during the clock periods in which RXD[3:0] contains valid data received. PHY asserts RX_DV no later than the clock period when it places the first nibble of the start frame delimiter (SFD) on RXD[3:0]. If PHY asserts RX_DV prior to the first nibble of the SFD, then RXD[3:0] carries valid preamble symbols. LINK_10M is shared with RX_DV and used to convey the link status of the 10-Mbit/s endec. The value is stored in a status register. |

| RX_ERR         | 36      | I    | Receive Error. PHY asserts RX_ERR synchronously whenever it detects a physical medium error (e.g., a coding violation). PHY asserts RX_ERR only when it asserts RX_DV.                                                                                                                                                                                                                                                                                                                                                                           |

| TXDA           | 9       | 0    | HDLC Ch-A Transmit Data. The serial output data from the transmitter is coded in NRZ/NRZI/FM/Manchester data format.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RXDA           | 7       | I    | HDLC Ch-A Receive Data. The serial input data received by the device should be coded in NRZ/NRZI/FM/Manchester data format. The data rate should not exceed the rate of the KS32C50100 internal master clock.                                                                                                                                                                                                                                                                                                                                    |

| nDTRA          | 6       | 0    | HDLC Ch-A Data Terminal Ready. nDTRA output indicates that the data terminal device is ready for transmission and reception.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nRTSA          | 8       | 0    | HDLC Ch-A Request To Send. The nRTSA output goes low when there is exist data to be sent in TxFIFO. The data to be sent is transmitted the nCTS is active state.                                                                                                                                                                                                                                                                                                                                                                                 |

| nCTSA          | 10      | I    | HDLC Ch-A Clear To Send. The KS32C50100 stores each transition of nCTS to ensure that its occurrence would be acknowledged by the system.                                                                                                                                                                                                                                                                                                                                                                                                        |

| nDCDA          | 13      | I    | HDLC Ch-A Data Carrier Detected. A High level on this pin resets and inhibits the receiver register. Data from a previous frame that may remain in the RxFIFO is retained. The KS32C50100 stores each transition of nDCD.                                                                                                                                                                                                                                                                                                                        |

| nSYNCA         | 15      | 0    | HDLC Ch-A Sync is detected. This indicates the reception of a flag. The nSYNC output goes low for one bit time beginning at the last bit of the flag.                                                                                                                                                                                                                                                                                                                                                                                            |

| RXCA           | 14      | I    | HDLC Ch-A Receiver Clock. When this clock input is used as the receiver clock, the receiver samples the data on the positive edge of RXCA clock. This clock can be the source clock of the receiver, the baud rate generator, or the DPLL.                                                                                                                                                                                                                                                                                                       |

| TXCA           | 16      | I/O  | HDLC Ch-A Transmitter Clock. When this clock input is used as the transmitter clock, the transmitter shifts data on the negative transition of the TXCA clock. If you do not use TXCA as the transmitter clock, you can use it as an output pin for monitoring internal clocks such as the transmitter clock, receiver clock, and baud rate generator output clocks.                                                                                                                                                                             |

| TXDB           | 20      | 0    | HDLC Ch-B Transmit Data. See the TXDA pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RXDB           | 18      | I    | HDLC Ch-B Receive Data. See the RXDA pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 1-1 KS32C50100 Signal Descriptions

| Signal                   | Pin No.         | Туре | Description                                                                                                                                                                                        |  |

|--------------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nDTRB                    | 17              | 0    | HDLC Ch-B Data Terminal Ready. See the nDTRA pin description.                                                                                                                                      |  |

| nRTSB                    | 19              | 0    | HDLC Ch-B Request To Send. See the nRTSA pin description.                                                                                                                                          |  |

| nCTSB                    | 23              | I    | HDLC Ch-B Clear To Send. See the nCTSA pin description.                                                                                                                                            |  |

| nDCDB                    | 24              | I    | HDLC Ch-B Data Carrier Detected. See the nDCDA pin description.                                                                                                                                    |  |

| nSYNCB                   | 26              | 0    | HDLC Ch-B Sync is detected. See the nSYNCA pin description.                                                                                                                                        |  |

| RXCB                     | 25              | I    | HDLC Ch-B Receiver Clock. See the RXCA pin description.                                                                                                                                            |  |

| TXCB                     | 27              | I/O  | HDLC Ch-B Transmitter Clock. See the TXCA pin description.                                                                                                                                         |  |

| UCLK                     | 64              | I    | The external UART clock input. MCLK or PLL generated clock can be used as the UART clock. You can use UCLK, with an appropriate divided by factor, if a very precious baud rate clock is required. |  |

| UARXD0                   | 202             | I    | UART0 Receive Data. RXD0 is the UART 0 input signal for receiving serial data.                                                                                                                     |  |

| UATXD0                   | 204             | 0    | UART0 Transmit Data. TXD0 is the UART 0 output signal for transmitting serial data.                                                                                                                |  |

| nUADTR0                  | 203             | ı    | Not UART0 Data Terminal Ready. This input signals the KS32C50100 that the peripheral (or host) is ready to transmit or receive serial data.                                                        |  |

| nUADSR0                  | 205             | 0    | Not UART0 Data Set Ready. This output signals the host (or peripheral) that UART 0 is ready to transmit or receive serial data.                                                                    |  |

| UARXD1                   | 206             | 1    | UART1 Receive Data. See the RXD0 pin description.                                                                                                                                                  |  |

| UATXD1                   | 4               | 0    | UART1 Transmit Data. See the TXD0 pin description.                                                                                                                                                 |  |

| nUADTR1                  | 3               | I    | Not UART1 Data Terminal Ready. See the DTR0 pin description.                                                                                                                                       |  |

| nUADSR1                  | 5               | 0    | Not UART1 Data Set Ready. See the DSR0 pin description.                                                                                                                                            |  |

| P[7:0]                   | 185–179,<br>176 | I/O  | General I/O ports. See the I/O ports, chapter 12.                                                                                                                                                  |  |

| XINTREQ[3:0]<br>P[11:8]  | 191–189,<br>186 | I/O  | External interrupt request lines or general I/O ports. See the I/O ports, chapter 12.                                                                                                              |  |

| nXDREQ[1:0]/<br>P[13:12] | 193, 192        | I/O  | Not External DMA requests for GDMA or general I/O ports. See the I/O ports, chapter 12.                                                                                                            |  |

| nXDACK[1:0]<br>P[15:14]  | 195, 194        | I/O  | Not External DMA acknowledge from GDMA or general I/O ports. See the I/O ports, chapter 12.                                                                                                        |  |

| TOUT0/P[16]              | 196             | I/O  | Timer 0 out or general I/O port. See the I/O ports, chapter 12.                                                                                                                                    |  |

| TOUT1/P[17]              | 199             | I/O  | Timer 1 out or general I/O port. See the I/O ports, chapter 12.                                                                                                                                    |  |

| SCL                      | 200             | I/O  | I <sup>2</sup> C serial clock.                                                                                                                                                                     |  |

| SDA                      | 201             | I/O  | I <sup>2</sup> C serial data.                                                                                                                                                                      |  |

|                          | 1               | 1    |                                                                                                                                                                                                    |  |

Table 1-1 KS32C50100 Signal Descriptions

| Signal    | Pin No.                                                                     | Туре  | Description                |

|-----------|-----------------------------------------------------------------------------|-------|----------------------------|

| VDDP      | 1, 21, 41,<br>56, 78, 92,<br>105, 118,<br>130, 155,<br>167, 177,<br>197     | Power | I/O pad power              |

| VDDI      | 11, 31, 51,<br>65, 103,<br>142, 157,<br>187, 207                            | Power | Internal core power        |

| VSSP      | 2, 22, 42,<br>57, 79, 81,<br>93, 106,<br>119, 131,<br>156, 168,<br>178, 198 | GND   | I/O pad ground             |

| VSSI      | 12, 32, 52,<br>66, 104,<br>143, 158,<br>188, 208                            | GND   | Internal core ground       |

| VDDA      | 53                                                                          | Power | Analog power for PLL       |

| VSSA/VBBA | 54                                                                          | GND   | Analog/Bulk ground for PLL |

## NOTES:

1. SDRAM or EDO/normal DRAM interface signal pins are shared functions. It's functions will be configured by SYSCFG[31].

Table 1-2 KS32C50100 Pin List and PAD Type

| Group             | Pin Name    | Pin<br>Counts | I/O<br>Type | Pad Type | Description                                |

|-------------------|-------------|---------------|-------------|----------|--------------------------------------------|

| System            | XCLK        | 1             | I           | ptic     | KS32C50100 system source clock.            |

| Configuration (8) | MCLKO       | 1             | 0           | pob4     | System clock out.                          |

| (0)               | CLKSEL      | 1             | I           | ptic     | Clock select.                              |

|                   | nRESET      | 1             | I           | ptis     | Not reset.                                 |

|                   | CLKOEN      | 1             | I           | ptic     | Clock out enable/disable.                  |

|                   | TMODE       | 1             | I           | ptic     | Test mode.                                 |

|                   | LITTLE      | 1             | I           | pticd    | Little endian mode select pin              |

|                   | FILTER      | 1             | I           | pia_bb   | PLL filter pin                             |

| TAP Control       | TCK         | 1             | I           | ptic     | JTAG test clock.                           |

| (5)               | TMS         | 1             | I           | pticu    | JTAG test mode select.                     |

|                   | TDI         | 1             | I           | pticu    | JTAG test data in.                         |

|                   | TDO         | 1             | 0           | ptot2    | JTAG test data out.                        |

|                   | nTRST       | 1             | I           | pticu    | JTAG not reset.                            |

| Memory            | ADDR[21:0]  | 22            | 0           | ptot6    | Address bus.                               |

| Interface<br>(83) | XDATA[31:0] | 32            | I/O         | ptbsut6  | External, bi-directional, 32-bit data bus. |

| (66)              | nRAS[3:0]   | 4             | 0           | pot4     | Not row address strobe for DRAM.           |

|                   | nCAS[3:0]   | 4             | 0           | pot4     | Not column address strobe for DRAM.        |

|                   | nDWE        | 1             | 0           | pot4     | Not write enable                           |

|                   | nECS[3:0]   | 4             | 0           | pot4     | Not external I/O chip select.              |

|                   | nEWAIT      | 1             | I           | ptic     | Not external wait signal.                  |

|                   | nRCS[5:0]   | 6             | 0           | pot4     | Not ROM/SRAM/flash chip select.            |

|                   | B0SIZE[1:0] | 2             | I           | ptic     | Bank 0 data bus access size.               |

|                   | nOE         | 1             | 0           | pot4     | Not output enable.                         |

|                   | nWBE[3:0]   | 4             | 0           | pot4     | Not write byte enable.                     |

|                   | ExtMREQ     | 1             | I           | ptic     | External master bus request.               |

|                   | ExtMACK     | 1             | 0           | pob1     | External bus acknowledge.                  |

Table 1-2 KS32C50100 Pin List and PAD Type

| Group            | Pin Name                          | Pin<br>Counts | I/O<br>Type | Pad Type | Description                                       |

|------------------|-----------------------------------|---------------|-------------|----------|---------------------------------------------------|

| Ethernet         | MDC                               | 1             | 0           | pob4     | Management data clock.                            |

| Controller (18)  | MDIO                              | 1             | I/O         | ptbcut4  | Management data I/O.                              |

| (10)             | COL/<br>COL_10M                   | 1             | I           | ptis     | Collision detected/collision detected for 10M.    |

|                  | TX_CLK/<br>TXCLK_10M              | 1             | I           | ptis     | Transmit data/transmit data for 10M.              |

|                  | TXD[3:0]/<br>TXD_10M/<br>LOOP_10M | 4             | 0           | pob4     | Transmit data/transmit data for 10M.              |

|                  | TX_EN/<br>TXEN_10M                | 1             | 0           | pob4     | Transmit enable or transmit enable for 10M.       |

|                  | TX_ERR/<br>PCOMP_10M              | 1             | 0           | pob4     | Transmit error/packet compression enable for 10M. |

|                  | CRS/<br>CRS_10M                   | 1             | I           | ptis     | Carrier sense/carrier sense for 10M.              |

|                  | RX_CLK/<br>RXCLK_10M              | 1             | I           | ptis     | Receive clock/receive clock for 10M.              |

|                  | RXD[3:0]/<br>RXD_10M              | 4             | I           | ptis     | Receive data/receive data for 10M.                |

|                  | RX_DV/<br>LINK_10M                | 1             | I           | ptis     | Receive data valid.                               |

|                  | RX_ERR                            | 1             | I           | ptis     | Receive error.                                    |

| HDLC             | TXDA                              | 1             | 0           | pob4     | HDLC channel A transmit data.                     |

| Channel A<br>(9) | RXDA                              | 1             | I           | ptis     | HDLC channel A receive data.                      |

| (6)              | nDTRA                             | 1             | 0           | pob4     | HDLC channel A data terminal ready.               |

|                  | nRTSA                             | 1             | 0           | pob4     | HDLC channel A request to send.                   |

|                  | nCTSA                             | 1             | I           | ptis     | HDLC channel A clear to send.                     |

|                  | nDCDA                             | 1             | I           | ptis     | HDLC channel A data carrier detected.             |

|                  | nSYNCA                            | 1             | 0           | pob4     | HDLC channel A sync is detected.                  |

|                  | RXCA                              | 1             | I           | ptis     | HDLC channel A receiver clock.                    |

|                  | TXCA                              | 1             | I/O         | ptbsut1  | HDLC channel A transmitter clock.                 |

Table 1-2 KS32C50100 Pin List and PAD Type

| Group                              | Pin Name                 | Pin<br>Counts | I/O<br>Type | Pad Type | Description                                              |

|------------------------------------|--------------------------|---------------|-------------|----------|----------------------------------------------------------|

| HDLC                               | TXDB                     | 1             | 0           | pob4     | HDLC channel B transmit data.                            |

| Channel B<br>(9)                   | RXDB                     | 1             | I           | ptis     | HDLC channel B receive data.                             |

| (0)                                | nDTRB                    | 1             | 0           | pob4     | HDLC channel B data terminal ready.                      |

|                                    | nRTSB                    | 1             | 0           | pob4     | HDLC channel B request to send.                          |

|                                    | nCTSB                    | 1             | I           | ptis     | HDLC channel B clear to send.                            |

|                                    | nDCDB                    | 1             | I           | ptis     | HDLC channel B data carrier detected.                    |

|                                    | nSYNCB                   | 1             | 0           | pob4     | HDLC channel B sync is detected.                         |

|                                    | RXCB                     | 1             | I           | ptis     | HDLC channel B receiver clock.                           |

|                                    | TXCB                     | 1             | I/O         | ptbsut1  | HDLC channel B transmitter clock.                        |

| UART 0                             | UCLK                     | 1             | I           | ptis     | UART External Clock for UART0/UART1                      |

| (5)                                | UARXD0                   | 1             | I           | ptic     | UART 0 receive data.                                     |

|                                    | UATXD0                   | 1             | 0           | pob4     | UART 0 transmit data.                                    |

|                                    | nUADTR0                  | 1             | I           | ptic     | Not UART 0 data terminal ready.                          |

|                                    | nUADSR0                  | 1             | 0           | pob4     | Not UART0 data set ready.                                |

| UART 1                             | UARXD1                   | 1             | I           | ptic     | UART 1 receive data.                                     |

| (4)                                | UATXD1                   | 1             | 0           | pob4     | UART 1 transmit data.                                    |

|                                    | nUADTR1                  | 1             | I           | ptic     | Not UART 1 data terminal ready.                          |

|                                    | nUADSR1                  | 1             | 0           | pob4     | Not UART 1 data set ready.                               |

| General-                           | P[7:0]                   | 8             | I/O         | ptbst4sm | General I/O ports.                                       |

| Purpose<br>I/O Ports,<br>(xINTREQ, | xINTREQ[3:0]<br>/P[11:8] | 4             | I/O         | ptbst4sm | External interrupt requests or general I/O ports.        |

| nXDREQ,                            | nXDREQ[1:0]/<br>P[13:12] | 2             | I/O         | ptbst4sm | External DMA requests for GDMA or general I/O ports.     |

| Timer 0, 1)                        | nXDACK[1:0]/<br>P[15:14] | 2             | I/O         | ptbst4sm | External DMA acknowledge from GDMA or general I/O ports. |

|                                    | TIMER0/P[16]             | 1             | I/O         | ptbst4sm | Timer 0 out or general I/O port.                         |

|                                    | TIMER1/P[17]             | 1             | I/O         | ptbst4sm | Timer 1 out or general I/O port.                         |

| I <sup>2</sup> C                   | SCL                      | 1             | I/O         | ptbcd4   | I <sup>2</sup> C serial clock.                           |

| (2)                                | SDA                      | 1             | I/O         | ptbcd4   | I <sup>2</sup> C serial data.                            |

Table 1-3 KS32C50100 PAD Type

| Pad<br>Type | I/O<br>Type | Current<br>Drive | Cell Type                                    | Feature                           | Slew-Rate<br>Control |

|-------------|-------------|------------------|----------------------------------------------|-----------------------------------|----------------------|

| ptic        | I           | _                | LVCMOS Level                                 | 5V-tolerant                       | _                    |

| ptis        | 1           | -                | LVCMOS Schmit<br>Trigger Level               | 5V-tolerant                       | -                    |

| pticu       | I           | -                | LVCMOS Level                                 | 5V-tolerant<br>Pull-up register   | _                    |

| pticd       | I           | _                | LVCMOS Level                                 | 5V-tolerant<br>Pull-down register | _                    |

| pia_bb      | I           | _                | Analog input with seperate bulk bias         | _                                 | _                    |

| pob1        | 0           | 1mA              | Normal Buffer                                | _                                 | -                    |

| ptot2       | 0           | 2mA              | Tri-state Buffer                             | 5V-tolerant                       | -                    |

| pob4        | 0           | 4mA              | Normal Buffer                                | _                                 | 1                    |

| ptot4       | 0           | 4mA              | Tri-state Buffer                             | 5V-tolerant                       | _                    |

| ptot6       | 0           | 6mA              | Tri-state Buffer                             | 5V-tolerant                       | _                    |

| ptbsut1     | I/O         | 1mA              | LVCMOS Schmit trigger level Tri-state Buffer | 5V-tolerant<br>Pull-up register   | _                    |

| ptbcut4     | I/O         | 4mA              | LVCMOS Level<br>Tri-state Buffer             | 5V-tolerant                       | Medium               |

| ptbcd4      | I/O         | 4mA              | LVCMOS Level<br>Open drain Buffer            | 5V-tolerant                       | _                    |

**NOTE:** 1. pticu and pticd provides 100K Ohm Pull-up(down) register.

For detail information about the pad type, see Chapter 4. Input/Output Cells of the "STD90/MDL90 0.35um 3.3V Standard Cell Library Data Book", produced by Samsung Electronics Co., Ltd, ASIC Team .

Figure 1-3 Reset Timing Diagramt

## **CPU CORE OVERVIEW**

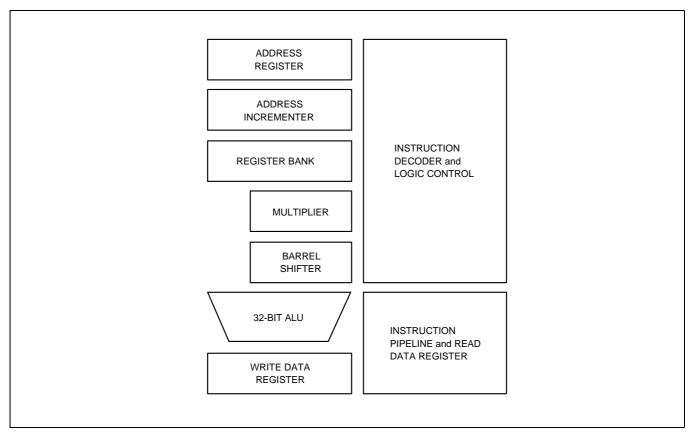

The KS32C50100 CPU core is a general purpose 32-bit ARM7TDMI microprocessor, developed by Advanced RISC Machines, Ltd. (ARM). The core architecture is based on Reduced Instruction Set Computer (RISC) principles. The RISC architecture makes the instruction set and its related decoding mechanism simpler and more efficient than those with microprogrammed Complex Instruction Set Computer (CISC) systems. High instruction throughput and impressive real-time interrupt response are among the major beneifts of the architecture. Pipelining is also employed so that all components of the processing and memory systems can operate continuously. The ARM7TDMI has a 32-bit address bus.

An important feature of the ARM7TDMI processor that makes itself distinct from the ARM7 processor is a unique architectural strategy called *THUMB*. The THUMB strategy is an extension of the basic ARM architecture consisting of 36 instruction formats. These formats are based on the standard 32-bit ARM instruction set, while having been re-coded using 16-bit wide opcodes.

As THUMB instructions are one-half the bit width of normal ARM instructions, they produce very high-density codes. When a THUMB instruction is executed, its 16-bit opcode is decoded by the processor into its equivalent instruction in the standard ARM instruction set. The ARM core then processes the 16-bit instruction as it would a normal 32-bit instruction. In other words, the THUMB architecture gives 16-bit systems a way to access the 32-bit performance of the ARM core without requiring the full overhead of 32-bit processing.

As the ARM7TDMI core can execute both standard 32-bit ARM instructions and 16-bit THUMB instructions, it allows you to mix the routines of THUMB instructions and ARM code in the same address space. In this way, you can adjust code size and performance, routine by routine, to find the best programming solution for a specific application.

Figure 1-4 ARM7TDMI Core Block Diagram

## **INSTRUCTION SET**

The KS32C50100 instruction set is divided into two subsets: a standard 32-bit ARM instruction set and a 16-bit THUMB instruction set.

The 32-bit ARM instruction set is comprised of thirteen basic instruction types, which can, in turn, be divided into four broad classes:

- Four types of branch instructions which control program execution flow, instruction privilege levels, and switching between an ARM code and a THUMB code.

- Three types of data processing instructions which use the on-chip ALU, barrel shifter, and multiplier to perform high-speed data operations in a bank of 31 registers (all with 32-bit register widths).

- Three types of load and store instructions which control data transfer between memory locations and the

registers. One type is optimized for flexible addressing, another for rapid context switching, and the third for

swapping data.

- Three types of co-processor instructions which are dedicated to controlling external co-processors. These

instructions extend the off-chip functionality of the instruction set in an open and uniform way.

### **NOTE**

All 32-bit ARM instructions can be executed conditionally.

The 16-bit THUMB instruction set contains 36 instruction formats drawn from the standard 32-bit ARM instruction set. The THUMB instructions can be divided into four functional groups:

- · Four branch instructions.

- Twelve data processing instructions, which are a subset of the standard ARM data processing instructions.

- Eight load and store register instructions.

- Four load and store multiple instructions.

## **NOTE**

Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with an identical processing model.

The 32-bit ARM instruction set and the 16-bit THUMB instruction set are good targets for compilers of many different high-level languages. When an assembly code is required for critical code segments, the ARM programming technique is straightforward, unlike that of some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

Pipelining is employed so that all parts of the processor and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and the third instruction is being fetched from memory.

## **MEMORY INTERFACE**

The CPU memory interface has been designed to help the highest performance potential to be realized without incurring high costs in the memory system. Speed-critical control signals are pipelined so that system control functions can be implemented in standard low-power logic. These pipelined control signals allow you to fully exploit the fast local access modes, offered by industry standard dynamic RAMs.

## **OPERATING STATES**

From a programmer's point of view, the ARM7TDMI core is always in one of two operating states. These states, which can be switched by software or by exception processing, are:

- ARM state (when executing 32-bit, word-aligned, ARM instructions), and

- THUMB state (when executing 16-bit, half-word aligned THUMB instructions).

## **OPERATING MODES**

The ARM7TDMI core supports seven operating modes:

- User mode: a normal program execution state

- FIQ (Fast Interrupt Request) mode: for supporting a specific data transfer or channel processing

- IRQ (Interrupt ReQuest) mode: for general purpose interrupt handling

- Supervisor mode: a protected mode for the operating system

- Abort mode: entered when a data or instruction pre-fetch is aborted

- System mode: a privileged user mode for the operating system

- Undefined mode: entered when an undefined instruction is executed

Operating mode changes can be controlled by software. They can also be caused by external interrupts or exception processing. Most application programs execute in User mode. Privileged modes (that is, all modes other than User mode) are entered to service interrupts or exceptions, or to access protected resources.

### **REGISTERS**

The KS32C50100 CPU core has a total of 37 registers: 31 general-purpose 32-bit registers, and 6 status registers. Not all of these registers are always available. Whether a registers is available to the programmer at any given time depends on the current processor operating state and mode.

### **NOTE**

When the KS32C50100 is operating in ARM state, 16 general registers and one or two status registers can be accessed at any time. In privileged mode, mode-specific banked registers are switched in.

Two register sets, or banks, can also be accessed, depending on the core's current state, the *ARM* state register set and the *THUMB* state register set:

- The ARM state register set contains 16 directly accessible registers: R0–R15. All of these registers, except for R15, are for general-purpose use, and can hold either data or address values. An additional (17th) register, the CPSR (Current Program Status Register), is used to store status information.

- The THUMB state register set is a subset of the ARM state set. You can access 8 general registers, R0–R7, as

well as the program counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. Each

privileged mode has a corresponding banked stack pointer, link register, and saved process status register

(SPSR).

The THUMB state registers are related to the ARM state registers as follows:

- THUMB state R0–R7 registers and ARM state R0–R7 registers are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP, LR, and PC are mapped directly to ARM state registers R13, R14, and R15, respectively

In THUMB state, registers R8–R15 are not part of the standard register set. However, you can access them for assembly language programming and use them for fast temporary storage, if necessary.

## **EXCEPTIONS**

An exception arises when the normal flow of program execution is interrupted, e.g., when processing is diverted to handle an interrupt from a peripheral. The processor state just prior to handling the exception must be preserved so that the program flow can be resumed when the exception routine is completed. Multiple exceptions may arise simultaneously.

To process exceptions, the KS32C50100 uses the banked core registers to save the current state. The old PC value and the CPSR contents are copied into the appropriate R14 (LR) and SPSR register.s The PC and mode bits in the CPSR are adjusted to the value corresponding to the type of exception being processed.

The KS32C50100 core supports seven types of exceptions. Each exception has a fixed priority and a corresponding privileged processor mode, as shown in Table 1-4.

Table 1-4 KS32C50100 CPU Exceptions

| Exception             | Mode on Entry   | Priority    |

|-----------------------|-----------------|-------------|

| Reset                 | Supervisor mode | 1 (Highest) |

| Data abort            | Abort mode      | 2           |

| FIQ                   | FIQ mode        | 3           |

| IRQ                   | IRQ mode        | 4           |

| Prefetch abort        | Abort mode      | 5           |

| Undefined instruction | Undefined mode  | 6           |

| SWI                   | Supervisor mode | 6 (Lowest)  |

# **SPECIAL REGISTERS**

Table 1-5 KS32C50100 Special Registers