1

# **PRODUCT OVERVIEW**

### SAM87RI PRODUCT FAMILY

Samsung's SAM87RI family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes.

A dual address/data bus architecture and a large number of bit- or nibble-configurable I/O ports provide a flexible programming environment for applications with varied memory and I/O requirements. Timer/counters with selectable operating modes are included to support real-time operations. Many SAM87RI microcontrollers have an external interface that provides access to external memory and other peripheral devices.

## KS86C0004/P0004/C0104/P0104 MICROCONTROLLER

The KS86C0004/P0004/C0104/P0104 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. It is built around the powerful SAM87RI CPU core.

Stop and Idle power-down modes were implemented to reduce power consumption. To increase on-chip register space, the size of the internal register file was logically expanded. The KS86C0004/P0004/C0104/P0104 has 4 K bytes of program memory on-chip.

Using the SAM87RI design approach, the following peripherals were integrated with the SAM87RI core:

- Five configurable I/O ports (32 pins)

- 12 bit-programmable pins for external interrupts

- 8-bit timer/counter with three operating modes

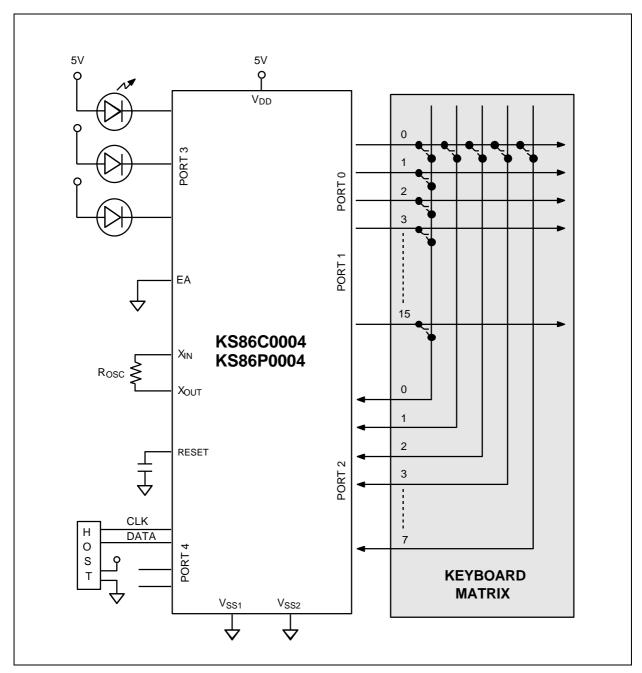

The KS86C0004/P0004/C0104/P0104 is a versatile microcontroller that can be used in a wide range of general purpose applications. It is especially suitable for use as a keyboard controller and is available in a 40-pin DIP and a 44-pin QFP package.

## **OTP**

The KS86C0004/C0104 microcontroller is also available in OTP (One Time Programmable) version, KS86P0004/P0104. KS86P0004/P0104 microcontroller has an on-chip 8-Kbyte one-time-programmable EPROM instead of masked ROM. The KS86P0004/P0104 is comparable to KS86C0004/C0104, both in function and in pin configuration.

1-1

## **FEATURES**

#### **CPU**

SAM87RI CPU core

## Memory

- 4-Kbyte internal program memory (ROM)

- 208-byte internal register file

- 8-Kbyte external program memory

- 8-Kbyte external data memory

#### **Instruction Set**

- 41 instructions

- IDLE and STOP instructions added for powerdown modes

#### **Instruction Execution Time**

• 1.5 μs at 4 MHz f<sub>OSC</sub>

## Interrupts

- 14 interrupt sources with one vector, Each source has its pending bit

- · One level, one vector interrupt structure

## **Oscillation Circuit Options**

- 4 MHz RC oscillator with on chip capacitor for KS86C0004/P0004 (± 10% RC accuracy at V<sub>DD</sub> ± 5% and Ta = 0°C - 70°C, using 1% external precision resistor)

- RC oscillator for KS86C0004/P0004

- Crystal/ceramic oscillator for KS86C0104/P0104

## General I/O

- Five ports (32 pins total)

- Three bit-programmable ports (20 pins total)

- Two bit-programmable ports with external interrupts (12 pins total)

#### Timer/Counter

- One 8-bit basic timer for watchdog function and programmable oscillation stabilization interval generation function

- One 8-bit timer/counter with PWM mode

## **Operating Temperature Range**

•  $-40^{\circ}$ C to  $+85^{\circ}$ C

## **Operating Voltage Range**

- 4.5 V to 5.5 V for KS86C0004/P0004

- 2.7 V to 5.5 V for KS86C0104/P0104

## **Package Types**

40-pin DIP

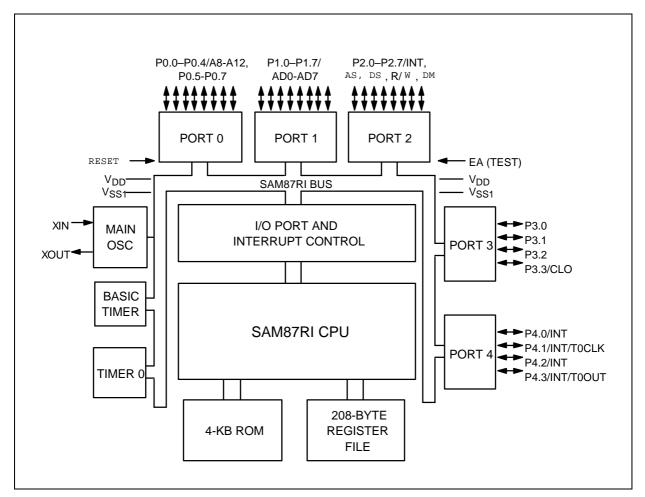

# **BLOCK DIAGRAM**

Figure 1-1. Block Diagram

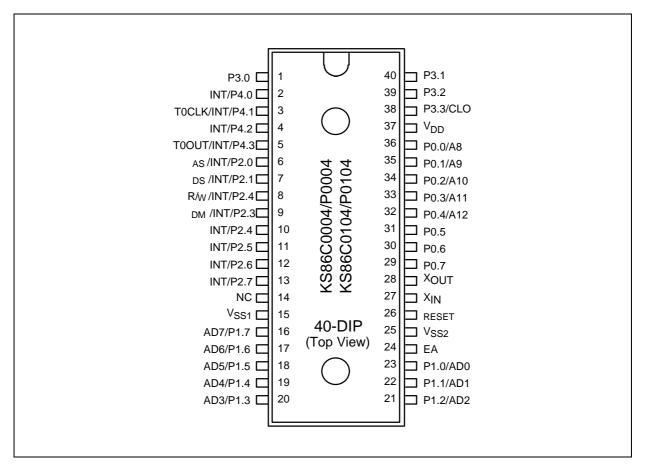

# **PIN ASSIGNMENTS**

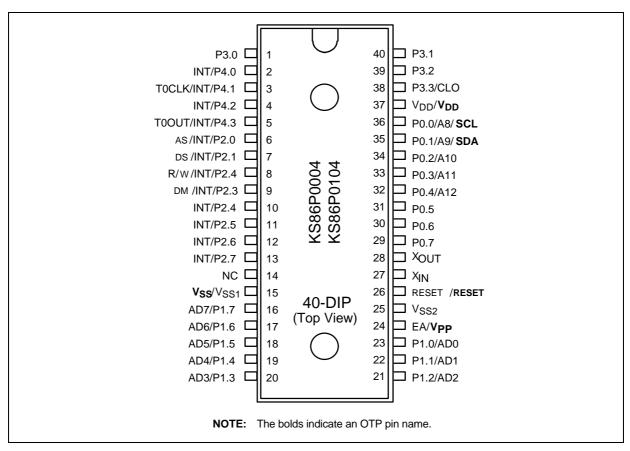

Figure 1-2. Pin Assignment Diagram (40-Pin DIP Package)

# **PIN DESCRIPTIONS**

Table 1-1. KS86C0004/P0004/C0104/P0104 Pin Descriptions

| Pin<br>Names                        | Pin<br>Type | Pin<br>Description                                                                                                                                                                                                                                                                             | Circuit<br>Number | Pin<br>Numbers | Share<br>Pins              |

|-------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|----------------------------|

| P0.0–P0.7                           | I/O         | Bit-programmable I/O port for Schmitt trigger input or open-drain output. Port0 can also be configured as external interface address lines A8–A12.                                                                                                                                             | С                 | 36–29          | A8-A12                     |

| P1.0-P1.7                           | I/O         | Bit-programmable I/O port for Schmitt trigger input, push-pull, or open-drain output. Port1 can alternatively be used as external interface address/data lines AD0–AD7.                                                                                                                        | С                 | 23–16          | AD0-AD7                    |

| P2.0-P2.7                           | I/O         | Bit-programmable I/O port for Schmitt trigger input or push-pull output. Port2 can be individually configured as external interrupt inputs. Especially, P2.0–2.3 can be configured for external bus control signal.                                                                            | D                 | 6–13           | INT, AS,<br>DS, R/W,<br>DM |

| P3.0-P3.3                           | I/O         | Same general characteristics as Port1. Port3 are designed for to drive LED directly. P3.3 can be used to system clock output (CLO) port.                                                                                                                                                       | С                 | 1, 40–38       | P3.3/CLO                   |

| P4.0-P4.3                           | I/O         | Bit-programmable I/O port. Input mode or n-channel open-drain output mode is software assignable. Port4 can be individually configured as external interrupt inputs. Pull-up resistors are also software assignable. Especially, P4.1 can be used TOCLK input and P4.3 also TOOUT for Timer 0. | D                 | 2–5            | INT,<br>TOCLK,<br>TOOUT    |

| X <sub>IN</sub> , X <sub>OUT</sub>  | _           | System clock input and output pin (for RC oscillator, crystal/ceramic oscillator, or external clock source)                                                                                                                                                                                    | -                 | 27, 28         | _                          |

| INT                                 | I           | External interrupt for bit-programmable port2 and port4 pins when set to input mode.                                                                                                                                                                                                           | _                 | 2-13           | PORT2/<br>PORT4            |

| RESET                               | _           | RESET signal input pin. Schmitt trigger input with internal pull-up resistor.                                                                                                                                                                                                                  | Α                 | 26             | _                          |

| EA                                  | I           | External Memory Access (EA) pin with 2 modes:  0V = Normal Operation Mode  5V = ROMLESS Operation Mode  (Must be connected to V <sub>SS</sub> during normal operation mode)                                                                                                                    | В                 | 24             | _                          |

| $V_{DD}$                            | _           | Power input pin                                                                                                                                                                                                                                                                                | _                 | 37             | _                          |

| V <sub>SS1</sub> , V <sub>SS2</sub> | _           | Vss1 is a ground power for CPU core. Vss2 is a ground power for I/O and OSC block                                                                                                                                                                                                              | _                 | 15, 25         | _                          |

| NC                                  | _           | No connection (This pin would be better connecting to V <sub>SS</sub> )                                                                                                                                                                                                                        | _                 | 14             | _                          |

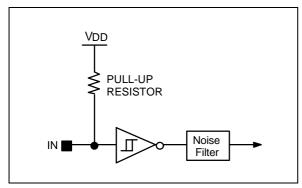

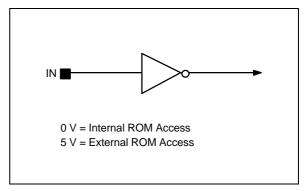

# **PIN CIRCUITS**

Table 1-2. Pin Circuit Assignments for the KS86C0004/P0004/C0104/P0104

| Circuit Number | Circuit Type | KS86C0004/P0004/C0104/P0104 Assignment |  |

|----------------|--------------|----------------------------------------|--|

| Α              | 1            | RESET signal input                     |  |

| В              | 1            | EA input                               |  |

| С              | I/O          | Ports 0, 1, and 3                      |  |

| D              | I/O          | Ports 2 and 4                          |  |

Figure 1-3. Pin Circuit Type A (RESET)

Figure 1-4. Pin Circuit Type B (EA)

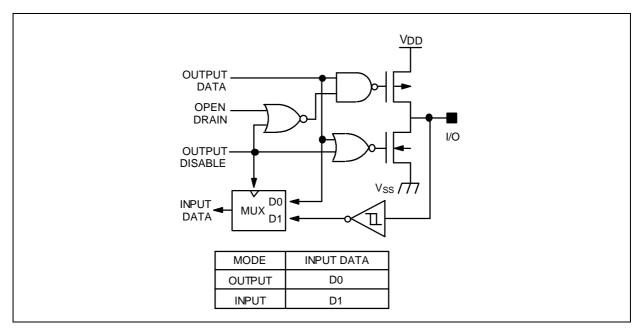

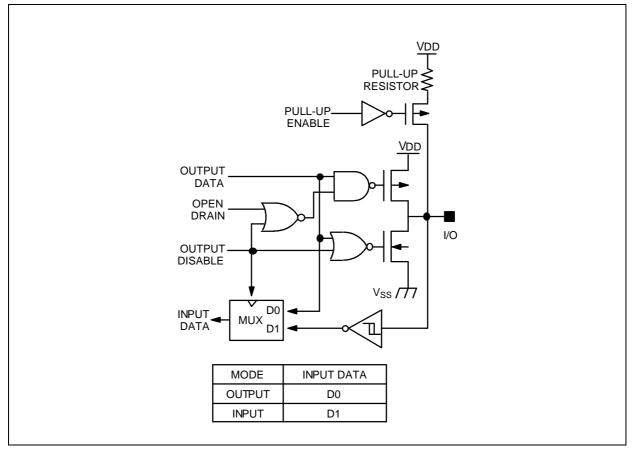

Figure 1-5. Pin Circuit Type C (Ports 0, 1, and 3)

Figure 1-6. Pin Circuit Type D (Ports 2 and 4)

# **APPLICATION CIRCUIT**

Figure 1-7. Keyboard Control Application Circuit Diagram

# 12 ELECTRICAL DATA

## **OVERVIEW**

In this section, the following KS86C0004/P0004/C0104/P0104 electrical characteristics are presented in tables and graphs:

- Absolute maximum ratings

- D.C. electrical characteristics

- I/O capacitance

- A.C. electrical characteristics

- Input timing for RESET

- Input timing for external interrupts (ports 2 and 4, RESET, and EA)

- Oscillator characteristics

- Oscillation stabilization time

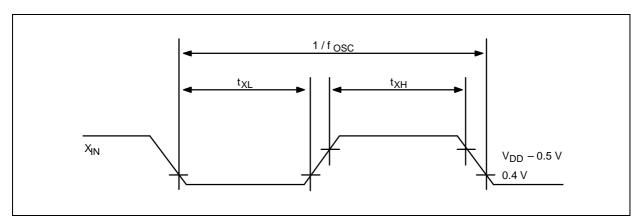

- Clock timing measurement points at X<sub>IN</sub>

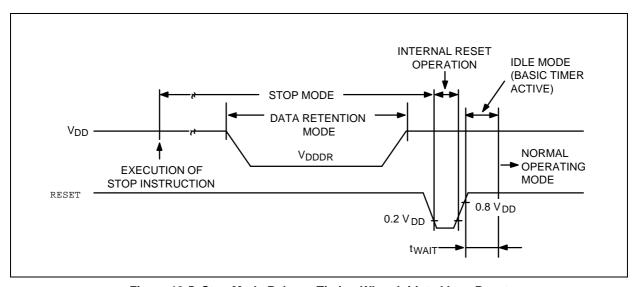

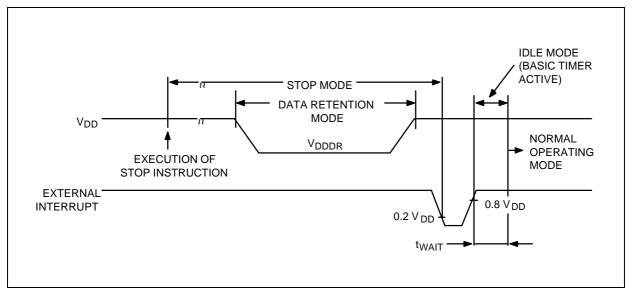

- Data retention supply voltage in Stop mode

- Stop mode release timing when initiated by a reset

- Stop mode release timing when initiated by an external interrupt

- External Memory timing characteristics (8 MHz)

- External Memory Read and Write timing

- Characteristic curves

**Table 12-1. Absolute Maximum Ratings**

$(T_A = 25^{\circ}C)$

| Parameter                | Symbol           | Conditions                             | Rating                   | Unit |

|--------------------------|------------------|----------------------------------------|--------------------------|------|

| Supply Voltage           | V <sub>DD</sub>  | _                                      | - 0.3 to + 6.5           | V    |

| Input Voltage            | V <sub>IN</sub>  | All input ports                        | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Output Voltage           | Vo               | All output ports                       | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Output Current           | I <sub>OH</sub>  | One I/O pin active                     | <b>– 18</b>              | mA   |

| High                     |                  | All I/O pins active                    | - 60                     |      |

| Output Current           | I <sub>OL</sub>  | One I/O pin active                     | + 25                     | mA   |

| Low                      |                  | Total pin current for ports 3          | + 100                    |      |

|                          |                  | Total pin current for ports 0, 1, 2, 4 | + 100                    |      |

| Operating<br>Temperature | T <sub>A</sub>   | -                                      | - 40 to + 85             | °C   |

| Storage<br>Temperature   | T <sub>STG</sub> | -                                      | - 65 to + 150            | °C   |

# **Table 12-2. D.C. Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V }^{(1)})$

| Parameter                                    | Symbol            | Conditions                                                                  | Min                   | Тур | Max                 | Unit |

|----------------------------------------------|-------------------|-----------------------------------------------------------------------------|-----------------------|-----|---------------------|------|

| Input High<br>Voltage                        | V <sub>IH1</sub>  | All inputs except V <sub>IH2</sub>                                          | 0.8 V <sub>DD</sub>   | _   | V <sub>DD</sub>     | V    |

|                                              | V <sub>IH2</sub>  | X <sub>IN</sub>                                                             | V <sub>DD</sub> - 0.5 |     | V <sub>DD</sub>     |      |

| Input Low Voltage                            | V <sub>IL1</sub>  | All inputs except V <sub>IL2</sub>                                          |                       | _   | 0.2 V <sub>DD</sub> | V    |

|                                              | $V_{IL2}$         | X <sub>IN</sub>                                                             |                       |     | 0.4                 |      |

| Output High<br>Voltage                       | V <sub>OH</sub>   | I <sub>OH</sub> = - 200 μA<br>All outputs except P4.1,<br>P4.3, and port0   | V <sub>DD</sub> – 1.0 | -   | _                   | V    |

| Output Low<br>Voltage                        | V <sub>OL</sub>   | I <sub>OL</sub> = 2 mA<br>All outputs except port3                          | _                     | -   | 0.4                 | V    |

| Output Low<br>Current                        | I <sub>OL</sub>   | V <sub>OL</sub> = 3 V<br>Port3 only                                         | 8                     | 15  | 23                  | mA   |

| Input High I <sub>LIH1</sub> Leakage Current |                   | $V_{IN} = V_{DD}$<br>All inputs except I <sub>LIH2</sub> , P4.0<br>and P4.1 | -                     | -   | 3                   | μА   |

|                                              | I <sub>LIH2</sub> | $V_{IN} = V_{DD}$<br>$X_{IN}, X_{OUT}$                                      |                       |     | 20                  |      |

Table 12-2. D.C. Electrical Characteristics (Continued)

$$(T_A = -40^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}^{(1)})$$

| Parameter                      | Symbol            | Conditions                                                                      | Min | Тур | Max  | Unit |

|--------------------------------|-------------------|---------------------------------------------------------------------------------|-----|-----|------|------|

| Input Low<br>Leakage Current   | I <sub>LIL1</sub> | V <sub>IN</sub> = 0 V<br>All inputs except I <sub>LIL2</sub> , P4.0 and<br>P4.1 | _   | _   | -3   | μА   |

|                                | I <sub>LIL2</sub> | $V_{IN} = 0 V$<br>$X_{OUT}, X_{IN}$                                             |     |     | - 20 |      |

| Output High<br>Leakage Current | I <sub>LOH</sub>  | $V_{OUT} = V_{DD}$<br>All outputs                                               | ı   | _   | 3    | μA   |

| Output Low<br>Leakage Current  | I <sub>LOL</sub>  | V <sub>OUT</sub> = 0 V<br>All outputs                                           | _   | _   | - 3  | μΑ   |

| Pull-up Resistors              | $R_{L1}$          | V <sub>IN</sub> = 0 V; Port 2 only                                              | 30  | 60  | 90   | ΚΩ   |

|                                | R <sub>L2</sub>   | V <sub>IN</sub> = 0 V; Port 4 only                                              | 1.8 | 2.8 | 4.0  |      |

|                                | R <sub>L3</sub>   | V <sub>IN</sub> = 0 V; RESET only                                               | 50  | 90  | 150  |      |

|                                |                   | Normal operation mode<br>4 MHz CPU clock                                        | _   | 4.5 | 10   | mA   |

|                                | I <sub>DD2</sub>  | Idle mode; 4 MHz oscillator                                                     |     | 0.9 | 3    | mA   |

|                                | I <sub>DD3</sub>  | Stop mode                                                                       |     | 0.5 | 5    | μA   |

# NOTES:

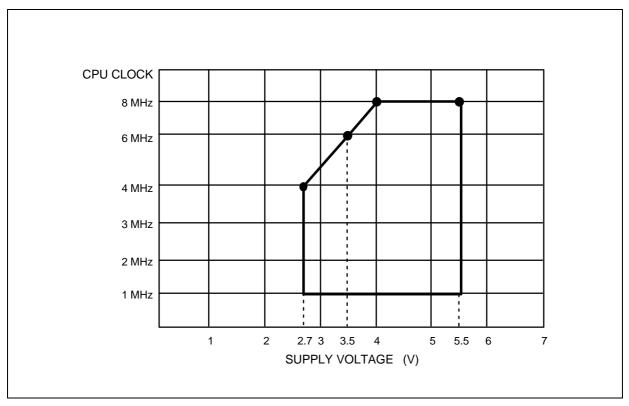

- The operating voltage range of KS86C0104/P0104 is from 2.7 V to 5.5 V according to oscillation frequency.

Supply current does not include current drawn through internal pull-up resistors or external output current loads.

# Table 12-3. Input/Output Capacitance

$$(T_A = -40^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 0 \text{ V})$$

| Parameter             | Symbol           | Conditions                                                  | Min | Тур | Max | Unit |

|-----------------------|------------------|-------------------------------------------------------------|-----|-----|-----|------|

| Input<br>Capacitance  | C <sub>IN</sub>  | f = 1 MHz; unmeasured pins are connected to V <sub>SS</sub> | -   | 1   | 10  | pF   |

| Output<br>Capacitance | C <sub>OUT</sub> |                                                             |     |     |     |      |

| I/O Capacitance       | C <sub>IO</sub>  |                                                             |     |     |     |      |

# **Table 12-4. A.C. Electrical Characteristics**

$$(T_A = -40^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$$

| Parameter                          | Symbol                                | Conditions | Min | Тур   | Max | Unit |

|------------------------------------|---------------------------------------|------------|-----|-------|-----|------|

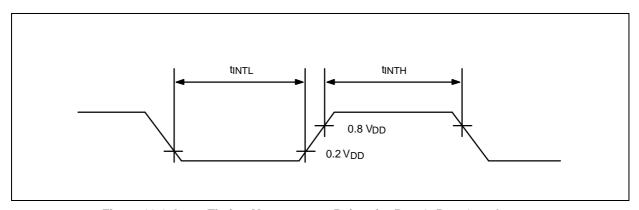

| Interrupt Input<br>High, Low Width | t <sub>INTH</sub> , t <sub>INTL</sub> | P2 and P4  | -   | 200   | 1   | ns   |

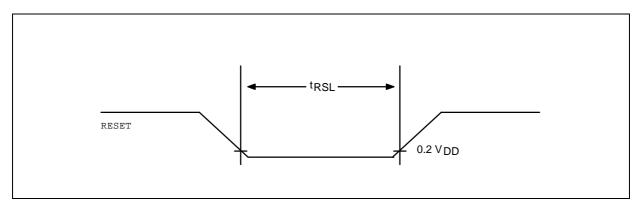

| RESET Input Low Width              | t <sub>RSL</sub>                      | RESET      | -   | 1,000 | -   |      |

Figure 12-1. Input Timing for RESET

Figure 12-2. Input Timing Measurement Points for Port 2, Port 4, and RESET

**Table 12-5. Oscillator Characteristics**

$$(T_A = -40^{\circ}C + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$$

| Oscillator                                                   | Clock Circuit                                    | Clock Circuit Test Condition Min                                                                        |     | Тур | Max | Unit |

|--------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| RC Oscillator (with Internal Capacitor; for KS86C0004/P0004) | R XIN XOUT                                       | $V_{DD} = 4.75 \text{ to } 5.25 \text{ V}$ $TA = 0^{\circ}C + 70^{\circ}C$ Tolerance: $\pm 10\%$ (note) | _   | 4   | _   | MHz  |

| Crystal/Ceramic<br>Oscillator<br>(for KS86C0104/P0104)       | X <sub>IN</sub> X <sub>IN</sub> X <sub>OUT</sub> | Crystal/Ceramic oscillation frequency                                                                   | 1.0 | -   | 8.0 |      |

**NOTE**: The KS86C0004/P0004 provides an internal capacitor to accommodate an RC oscillator configuration. A 1% precision resistor must be used to achieve an oscillation frequency with an acceptable tolerance.

Figure 12-3. Operating Voltage Range (KS86C0104/P0104)

Table 12-6. Oscillation Stabilization Time

$$(T_A = -40^{\circ}C + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$$

| Oscillator                               | Test Condition                                                                                            | Min | Тур                                   | Max | Unit |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|---------------------------------------|-----|------|

| Main Crystal                             | f <sub>OSC</sub> = 4 MHz                                                                                  | _   | _                                     | 10  | ms   |

| Main Ceramic                             | (Oscillation stabilization occurs when $V_{\text{DD}}$ is equal to the minimum oscillator voltage range.) |     |                                       |     |      |

| Oscillator<br>Stabilization Wait<br>Time | t <sub>WAIT</sub> stop mode release time by a reset                                                       |     | 2 <sup>16</sup> /<br>f <sub>OSC</sub> | _   |      |

|                                          | t <sub>WAIT</sub> stop mode release time by an interrupt                                                  | _   | (note)                                | _   |      |

$\textbf{NOTE}: \quad \text{The oscillator stabilization wait time, } t_{WAIT}, \text{is determined by the setting in the basic timer control register, BTCON}.$

Figure 12-4. Clock Timing Measurement Points at  $X_{\rm IN}$

Table 12-7. Data Retention Supply Voltage in Stop Mode

$$(T_A = -40^{\circ}C + 85^{\circ}C)$$

| Parameter                        | Symbol            | Conditions                           | Min | Тур | Max | Unit |

|----------------------------------|-------------------|--------------------------------------|-----|-----|-----|------|

| Data Retention<br>Supply Voltage | $V_{DDDR}$        | Stop mode                            | 2.0 | _   | 6   | V    |

| Data Retention<br>Supply Current | I <sub>DDDR</sub> | Stop mode; V <sub>DDDR</sub> = 2.0 V | _   | _   | 5   | μA   |

Figure 12-5. Stop Mode Release Timing When Initiated by a Reset

Figure 12-6. Stop Mode Release Timing When Initiated by an External Interrupt

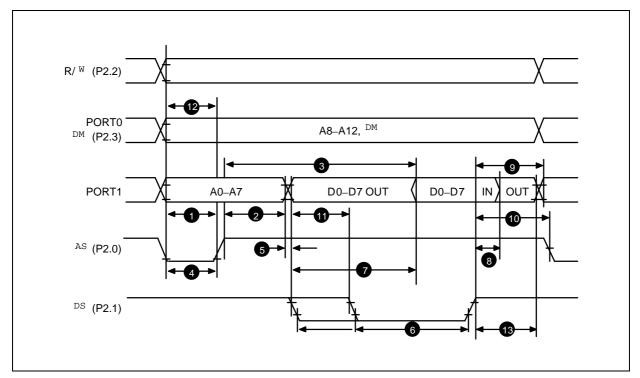

Table 12-8. External Memory Timing Characteristics (4 MHz)

$(T_A = -40^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V})$

| Number | Symbol                   | Parameter                                 | Normal T | iming (ns) |

|--------|--------------------------|-------------------------------------------|----------|------------|

|        |                          |                                           | Min      | Max        |

| 1      | t <sub>dA</sub> (AS)     | Address valid to AS ↑ delay               | 10       | _          |

| 2      | t <sub>dAS</sub> (A)     | AS ↑ to address float delay               | 35       | _          |

| 3      | t <sub>dAS</sub> (DR)    | AS ↑ to read data required valid          | _        | 140        |

| 4      | t <sub>wAS</sub>         | AS Low width                              | 88       | _          |

| 5      | t <sub>dA</sub> (DS)     | Address float to DS $\downarrow$          | 0        | _          |

| 6a     | t <sub>wDS</sub> (read)  | DS (read) Low width                       | 314      | _          |

| 6b     | t <sub>wDS</sub> (write) | DS (write) Low width                      | 164      | _          |

| 7      | t <sub>dDS</sub> (DR)    | DS ↓ to read data required valid          | _        | 80         |

| 8      | t <sub>hDS</sub> (DR)    | Read data to DS ↑ hold time               | 0        | _          |

| 9      | t <sub>dDS</sub> (A)     | DS ↑ to address active delay              | 20       | _          |

| 10     | t <sub>dDS</sub> (AS)    | DS ↑ to AS ↓ delay                        | 30       | _          |

| 11     | t <sub>dDO</sub> (DS)    | Write data valid to DS (write) ↓ delay 10 |          | _          |

| 12     | t <sub>dRW</sub> (AS)    | R/W valid to AS ↑ delay 20                |          | -          |

| 13     | t <sub>dDS</sub> (DW)    | DS ↑ to write data not valid delay 20     |          | -          |

## NOTES:

- All times are in nano seconds (ns) and assume an 4 MHz input frequency.

Wait states add 100 ns to the time of numbers 3, 6a, 6b, and 7.

Figure 12-7. External Memory Read and Write Timing

(See Table 12-8 for a description of each timing point.)

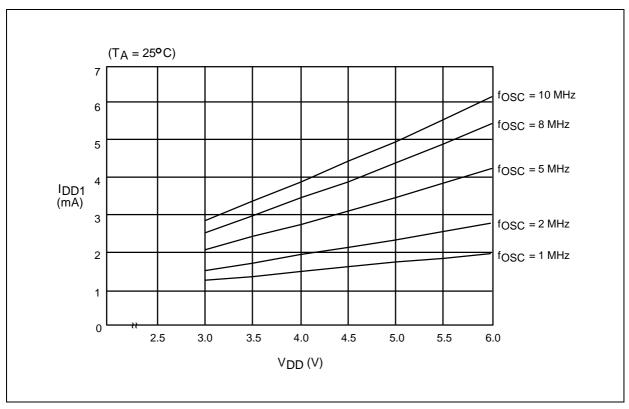

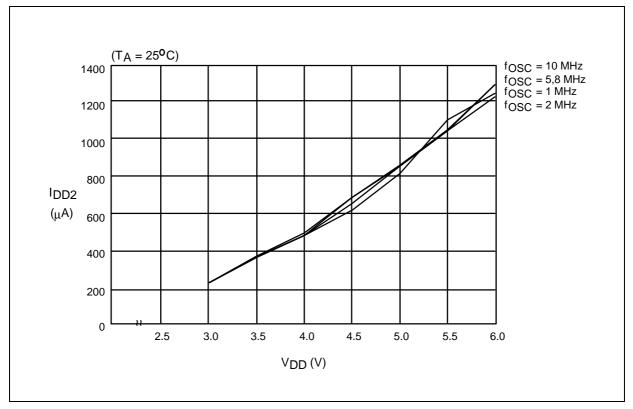

# **CHARACTERISTIC CURVES**

# NOTE

The characteristic values shown in the following graphs are based on actual test measurements. They do not, however, represent guaranteed operating values.

Figure 12-8.  $I_{\rm DD1}$  vs.  $V_{\rm DD}$

Figure 12-9.  $I_{\rm DD2}$  vs.  $V_{\rm DD}$

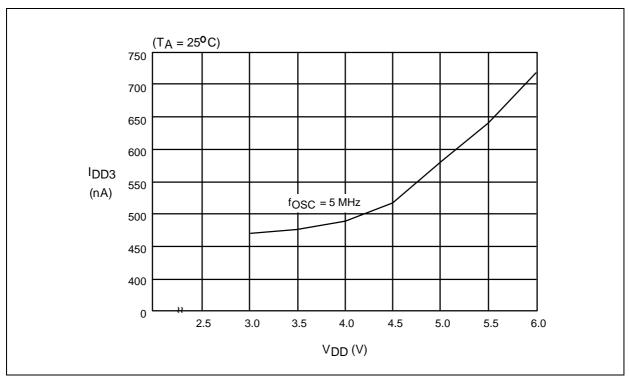

Figure 12-10.  $\rm I_{DD3}$  vs.  $\rm V_{DD}$

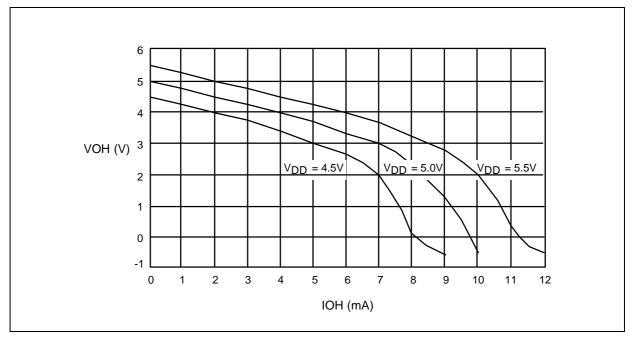

Figure 12-11.  $I_{OH}$  vs.  $V_{OH}$

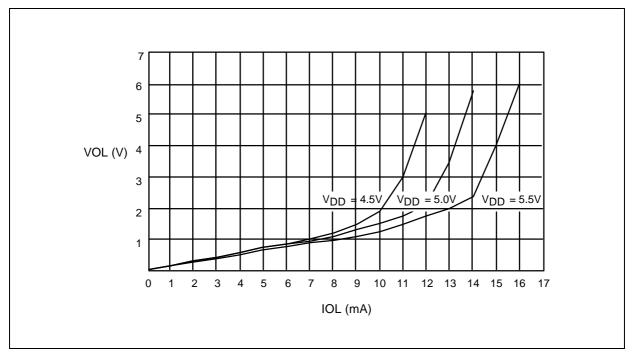

Figure 12-12.  $V_{OL}$  vs.  $I_{OL}$  (Port 0, 1, 2, and 4)

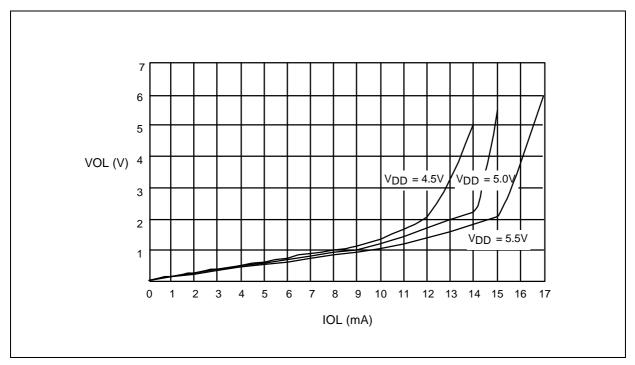

Figure 12-13.  $V_{OL}$  vs.  $I_{OL}$  (Port 3)

# 13 MECHANICAL DATA

# **OVERVIEW**

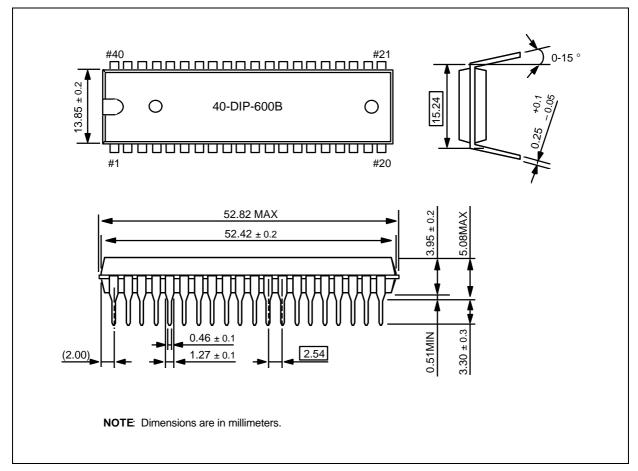

The KS86C0004/P0004/C0104/P0104 is currently available in a 40-pin DIP package.

Figure 13-1. 40-Pin DIP Package Mechanical Data (40-DIP-600B)

# **NOTES**

14

# KS86P0004/P0104 OTP

#### **OVERVIEW**

The KS86P0004/P0104 single-chip CMOS microcontroller is the OTP (One Time Programmable) version of the KS86C0004/C0104 microcontroller. It has an on-chip OTP ROM instead of masked ROM. The EPROM is accessed by serial data format.

The KS86P0004/P0104 is fully compatible with the KS86C0004/C0104, both in function and in pin configuration. Because of its simple programming requirements, the KS86P0004/P0104 is ideal for use as an evaluation chip for the KS86C0004/C0104.

Figure 14-1. KS86P0004/P0104 Pin Assignments (40-DIP Package)

14-1

Table 14-1. Descriptions of Pins Used to Read/Write the EPROM

| Main Chip                          |                                   | During Programming |     |                                                                                                                                                                                                     |  |  |  |

|------------------------------------|-----------------------------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                           | Pin Name                          | Pin No.            | I/O | Function                                                                                                                                                                                            |  |  |  |

| P0.1                               | SDAT                              | 35                 | I/O | Serial data pin (output when reading, Input when writing) Input and push-pull output port can be assigned                                                                                           |  |  |  |

| P0.0                               | SCLK                              | 36                 | I/O | Serial clock pin (input only pin)                                                                                                                                                                   |  |  |  |

| EA                                 | V <sub>PP</sub>                   | 24                 | I   | Power supply pin for EPROM cell writing (indicates that OTP enters into the writing mode). When 12.5 V is applied, OTP is in writing mode and when 5 V is applied, OTP is in reading mode. (Option) |  |  |  |

| RESET                              | RESET                             | 26                 | I   | Chip Initialization                                                                                                                                                                                 |  |  |  |

| V <sub>DD</sub> / V <sub>SS1</sub> | V <sub>DD</sub> / V <sub>SS</sub> | 37 / 15            | _   | Logic Power Supply Pin.                                                                                                                                                                             |  |  |  |

Table 14-2. Comparison of KS86P0004/P0104 and KS86C0004/C0104 Features

| Characteristic                                         | KS86P0004/P0104                                      | KS86C0004/C0104           |  |

|--------------------------------------------------------|------------------------------------------------------|---------------------------|--|

| Program Memory                                         | 4-Kbyte EPROM                                        | 4-Kbyte mask ROM          |  |

| Operating Voltage (V <sub>DD</sub> ) <sup>(note)</sup> | 4.5 V to 5.5 V                                       | 4.5 V to 5.5 V            |  |

| OTP Programming Mode                                   | V <sub>DD</sub> = 5 V, V <sub>PP</sub> (EA) = 12.5 V | _                         |  |

| Pin Configuration                                      | 40 DIP                                               | 40 DIP                    |  |

| EPROM Programmability                                  | User Program 1 time                                  | Programmed at the factory |  |

NOTE: The operating voltage range of KS86C0104/P0104 is from 2.7 V to 5.5 V according to oscillation frequency.

## **OPERATING MODE CHARACTERISTICS**

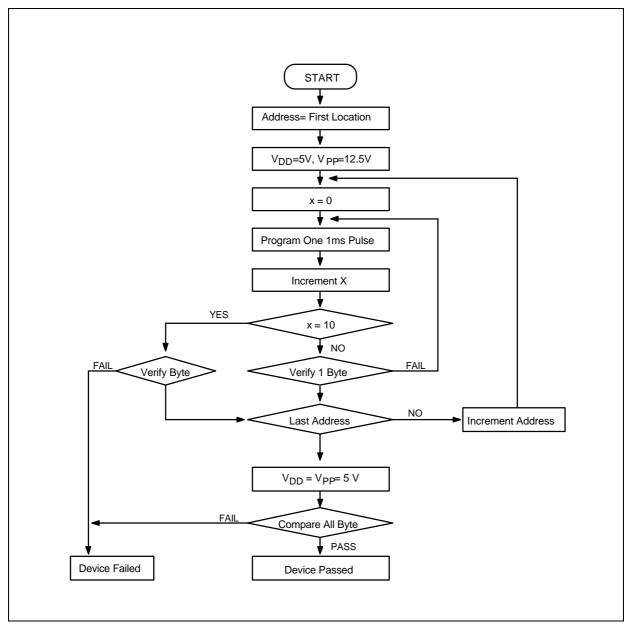

When 12.5 V is supplied to the VPP (EA) pin of the KS86P0004/P0104, the EPROM programming mode is entered. The operating mode (read, write, or read protection) is selected according to the input signals to the pins listed in Table 14-3 below.

**Table 14-3. Operating Mode Selection Criteria**

| V <sub>DD</sub> | VPP<br>(EA) | REG/<br>MEM | ADDRESS<br>(A15-A0) | R/W | MODE                  |

|-----------------|-------------|-------------|---------------------|-----|-----------------------|

| 5 V             | 5 V         | 0           | 0000H               | 1   | EPROM read            |

|                 | 12.5 V      | 0           | 0000H               | 0   | EPROM program         |

|                 | 12.5 V      | 0           | 0000H               | 1   | EPROM verify          |

|                 | 12.5 V      | 1           | 0E3FH               | 0   | EPROM read protection |

NOTE: "0" means Low level; "1" means High level.

Figure 14-2. OTP Programming Algorithm

# **Table 14-4. D.C. Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } + 85^{\circ}C, V_{DD} = 4.5 \text{ V to } 5.5 \text{ V} ^{(1)})$

| Parameter          | Symbol           | Conditions                                | Min | Тур | Max | Unit |

|--------------------|------------------|-------------------------------------------|-----|-----|-----|------|

| Supply Current (2) | I <sub>DD1</sub> | Normal operation mode;<br>4 MHz CPU clock | _   | 4.5 | 10  | mA   |

|                    | I <sub>DD2</sub> | Idle mode;<br>4 MHz oscillator            |     | 0.9 | 3   |      |

|                    | I <sub>DD3</sub> | Stop mode                                 |     | 0.5 | 5   | μΑ   |

## NOTES:

- The operating voltage range of KS86C0104/P0104 is from 2.7 V to 5.5 V according to oscillation frequency.

Supply current does not include current drawn through internal pull-up resistors or external output current loads.