# **Document Title**

64Kx18-Bit Synchronous Burst SRAM, 5V Power Data Sheets for 52 PLCC

# **Revision History**

| Rev.No.  | <u>History</u>                                                                              | <b>Draft Date</b> | <u>Remark</u> |

|----------|---------------------------------------------------------------------------------------------|-------------------|---------------|

| Rev. 1.0 | - Final specification release                                                               |                   | Final         |

| Rev. 1.1 | <ul> <li>Change specification format.</li> <li>No change was made in parameters.</li> </ul> | April, 1997       | Final         |

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

# 64Kx18-Bit Synchronous Burst SRAM FEATURES

- <sup>a</sup> Synchronous Operation.

- Don-Chip Address Counter.

- Self-Timed Write Cycle.

- On-Chip Address and Control Registers.

- <sub>ρ</sub> Single 5V±5% Power Supply.

- Byte Writable Function.

- Asynchronous Output Enable Control.

- ADSP, ADSC, ADV Burst Control Pins.

- □ TTL-Level Three-State Output.

- <sub>a</sub> 3.3V I/O Compatible.

- 52-Pin PLCC Package.

#### **FAST ACCESS TIMES**

| Parameter            | Symbol | -8 | -9 | -10 | -12 | Unit |

|----------------------|--------|----|----|-----|-----|------|

| Cycle Time           | tcyc   | 15 | 15 | 17  | 20  | ns   |

| Clock Access Time    | tcD    | 8  | 9  | 10  | 12  | ns   |

| Output Enable Access | toE    | 5  | 5  | 5   | 6   | ns   |

#### **GENERAL DESCRIPTION**

The KM718B86 is a 1,179,648 bits Synchronous Static Random Access Memory designed to support 66MHz of Intel secondary caches.

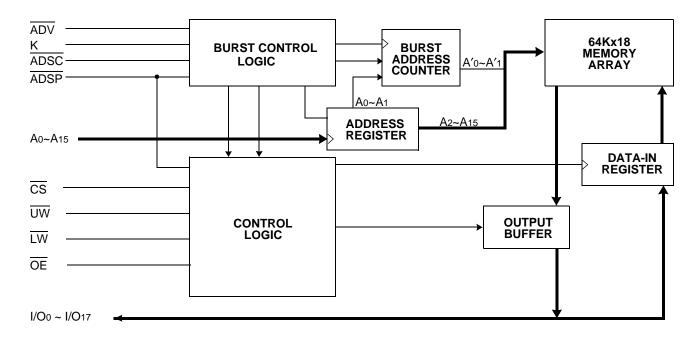

It is organized as 65,536 words of 18bits and integrates address and control registers, a 2-bit burst address counter and high output drive circuitry onto a single integrated circuit for reduced components count implementations of high performance cache RAM applications.

Write cycles are internally self-timed and synchronous.

The self-timed write feature eliminates complex off chip write pulse shaping logic, simplifying the cache design and further reducing the component count.

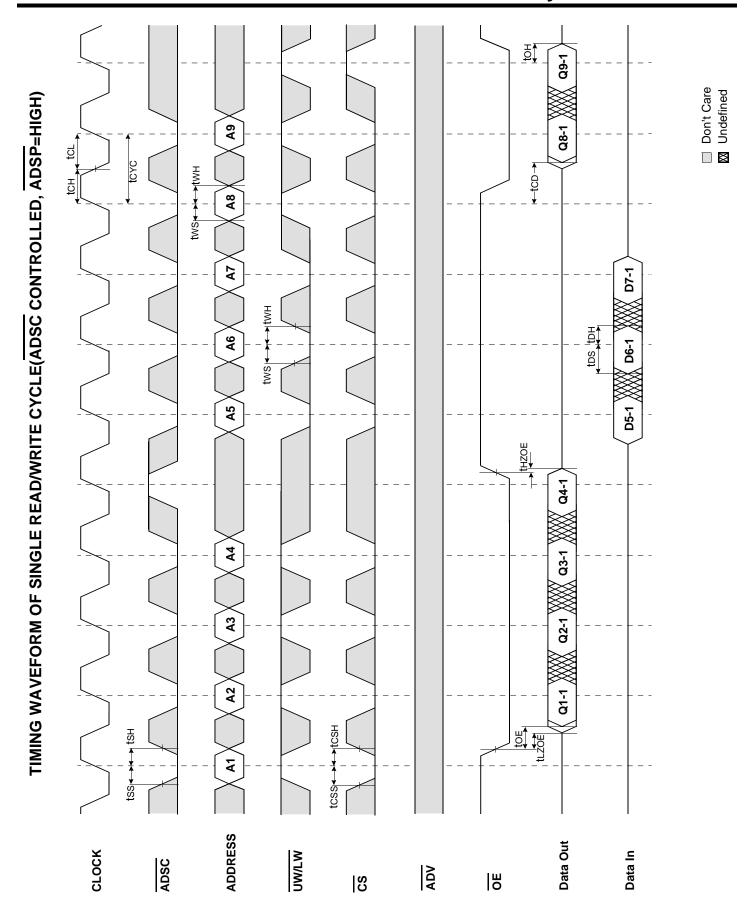

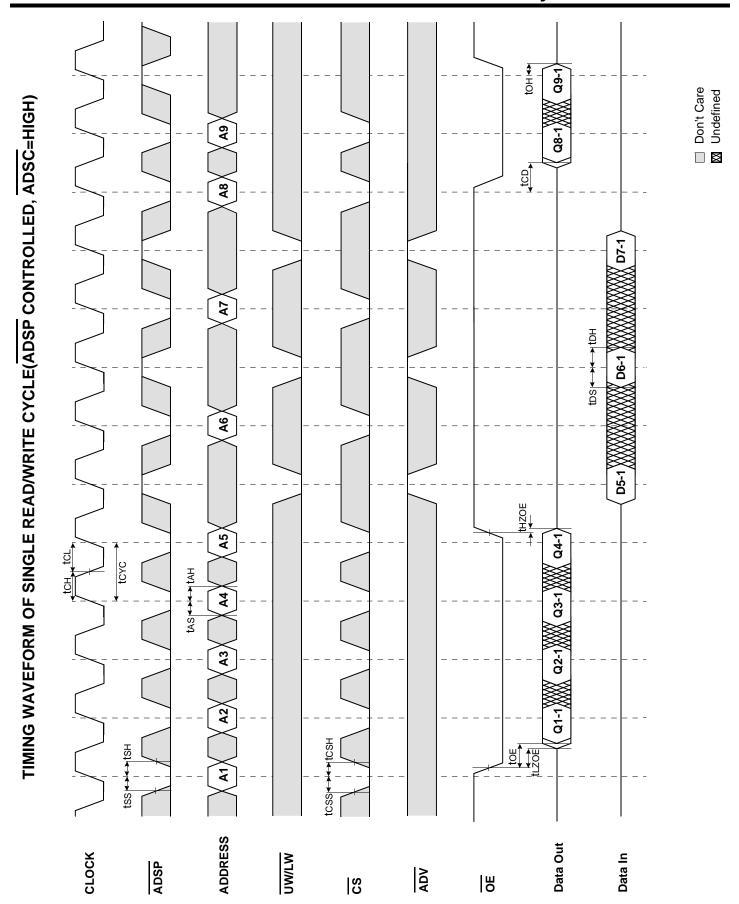

Burst cycle can be initiated with either the address status processor( $\overline{ADSP}$ ) or address status cache controller( $\overline{ADSC}$ ) inputs. Subsequent burst addresses are generated internally in the system's burst sequence and are controlled by the burst address advance( $\overline{ADV}$ ) input.

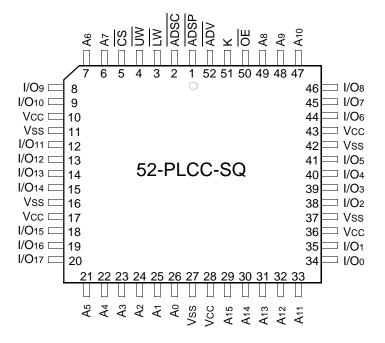

The KM718B86 is implemented with SAMSUNG's high performance BiCMOS technology and is available in a 52pin PLCC package. Multiple power and ground pins are utilized to minimize ground bounce.

## PIN CONFIGURATION(TOP VIEW)

#### **PIN NAME**

| Pin Name   | Pin Function          |

|------------|-----------------------|

| A0 - A15   | Address Inputs        |

| K          | Clock                 |

| W, UW      | Write Enable          |

| CS         | Chip Selects          |

| ŌĒ         | Output Enable         |

| ADV        | Burst Address Advance |

| ADSP, ADSC | Address Status        |

| I/O0~I/O17 | Data Inputs/Outputs   |

| Vcc        | +5V Power Supple      |

| Vss        | Ground                |

### LOGIC BLOCK DIAGRAM

#### **FUNCTION DESCRIPTION**

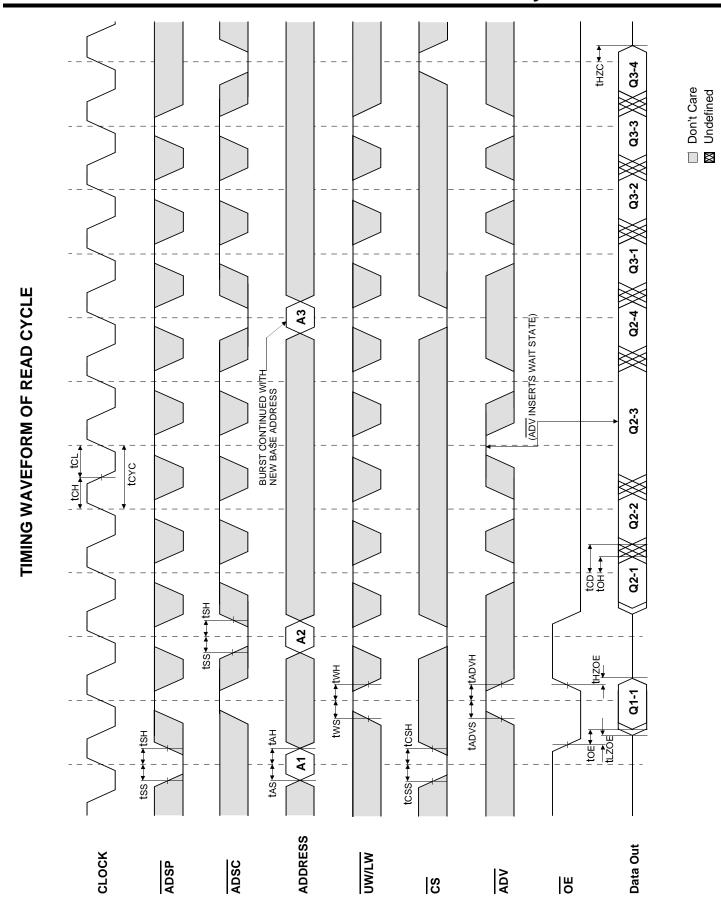

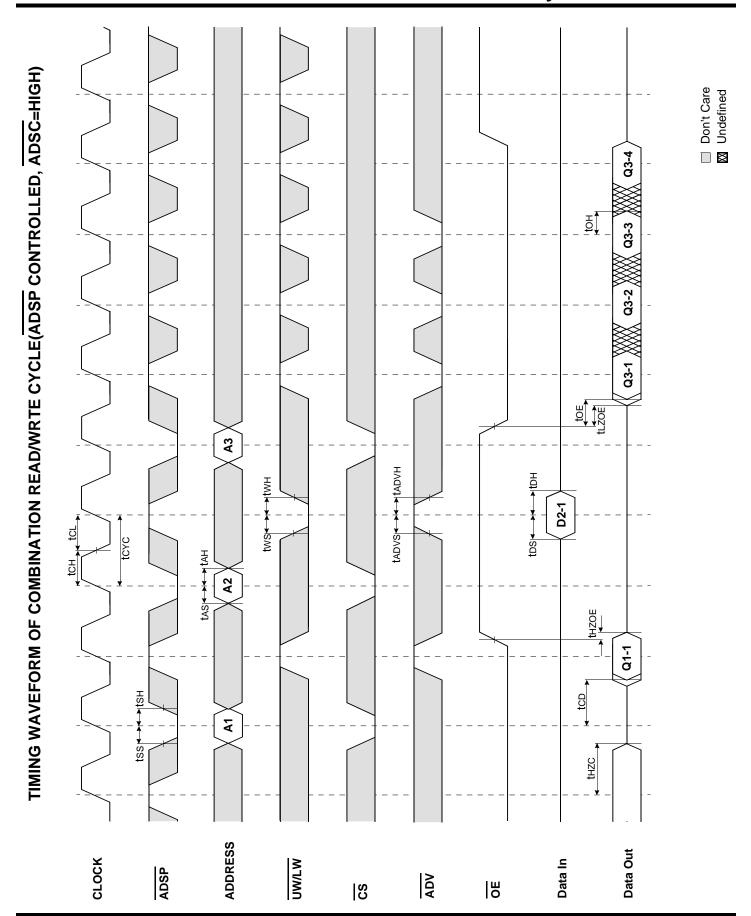

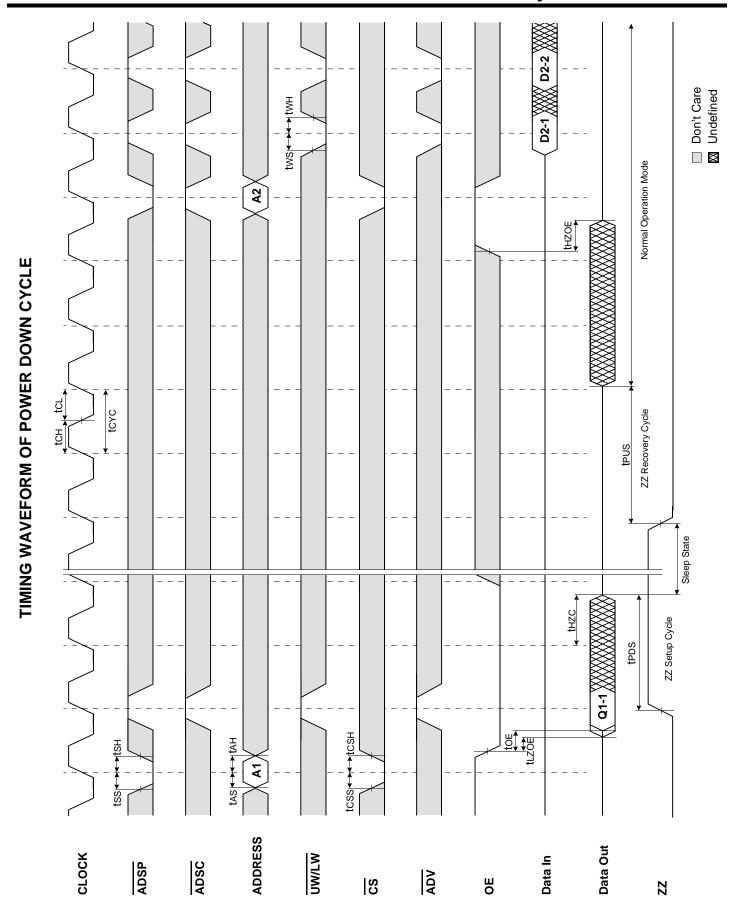

The KM718B86 is a synchronous SRAM designed to support the burst address accessing sequence of the Power microprocessor. All inputs(with the exception of OE) are sampled on rising clock edges. The start and duration of the burst access is controlled by ADSP and ADSC. The accesses are enabled with the chip select signals and output enable. Wait states are inserted into the access with ADV.

Read cycles are in<u>itiated</u> with ADSP(regardless of LW, UW and ADSC) using the new external address clocked into <u>the on-chip</u> address register whenever ADSP is sample low, The chip selects are sampled active, and the output buffer is enabled with OE, ADV is ignored on the clock edge that samples ADSP asserted, <u>but</u> is sampled on the next and subsequent clock edges. The address is increased internally for the next access of the burst when LW, UW is sampled HIGH and ADV is sampled low.

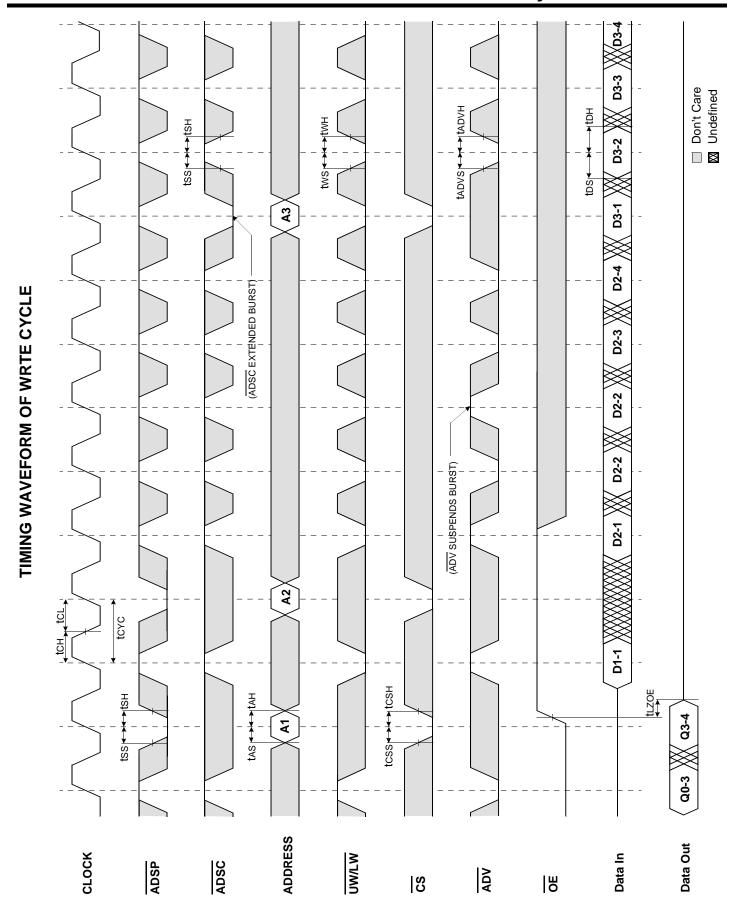

Write cycles are performed by disabling the output buffers with  $\overline{OE}$  and asserting  $\overline{LW}$ ,  $\overline{UW}$ .  $\overline{LW}$ ,  $\overline{UW}$  is ignored on the clock edge that sampled ADSP low, but is sampled on the next and subsequent clock edges. The output buffers are disabled when  $\overline{LW}$ ,  $\overline{UW}$  is sampled low (regardless of  $\overline{OE}$ ). Data is clocked into the input register when  $\overline{LW}$ ,  $\overline{UW}$  is sampled low. The address increases internally to the next address of burst, if both  $\overline{LW}$ ,  $\overline{UW}$  and  $\overline{ADV}$  are sampled  $\overline{LW}$ . Individual byte write cycles are performed sampling low only one byte write enable signals( $\overline{LW}$  or  $\overline{LU}$ )and  $\overline{LW}$  controls  $\overline{LW}$ 00~ $\overline{LW}$ 017.

Read or write cycles (depending on LW, LU)may also be initiated with ADSC, instead of ADSP. The differences between cycles initiated with ADSC and ADSP are as follows:

ADSP must be sampled high when ADSC is sampled low to initiate a cycle with ADSC. LW, UW is sampled on the same clock edge that sampled ADSC low(and ADSP high).

Addresses are generated for the burst accesses as shown below. The starting point of the burst sequence is provided by the external address. The burst address counter wraps around to its initial state upon completion.

### **BURST SEQUENCE TABLE**

(Interleaved Burst)

|                | Cas        | Case 1         |            | Case 2         |            | Case 3         |            | Case 4         |  |

|----------------|------------|----------------|------------|----------------|------------|----------------|------------|----------------|--|

|                | <b>A</b> 1 | A <sub>0</sub> |  |

| First Address  | 0          | 0              | 0          | 1              | 1          | 0              | 1          | 1              |  |

|                | 0          | 1              | 0          | 0              | 1          | 1              | 1          | 0              |  |

| .].            | 1          | 0              | 1          | 1              | 0          | 0              | 0          | 1              |  |

| Fourth Address | 1          | 1              | 1          | 0              | 0          | 1              | 0          | 0              |  |

## TRUTH TABLES

SYNCHRONOUS TRUTH TABLE(See Notes 1 and 2)

| cs | ADSP | ADSC | ADV | LW/UW | K        | Address Accessed | Operation                  |

|----|------|------|-----|-------|----------|------------------|----------------------------|

| Н  | L    | Х    | Х   | Х     | <b>↑</b> | N/A              | Not Selected               |

| Н  | Х    | L    | Х   | Х     | 1        | N/A              | Not Selected               |

| L  | L    | Х    | Х   | Х     | 1        | External Address | Begin Burst Read Cycle     |

| L  | Н    | L    | Х   | Н     | 1        | External Address | Begin Burst Read Cycle     |

| Х  | Н    | Н    | L   | Н     | <b>↑</b> | Next Address     | Continue Burst Read Cycle  |

| Х  | Н    | Н    | Н   | Н     | <b>↑</b> | Current Address  | Suspend Burst Read Cycle   |

| L  | Н    | L    | Х   | L     | 1        | External Address | Begin Burst Write Cycle    |

| Х  | Н    | Н    | L   | L     | <b>↑</b> | Next Address     | Continue Burst Write Cycle |

| Х  | Н    | Н    | Н   | L     | <b>↑</b> | Current Address  | Suspend Burst Write Cycle  |

NOTE1: X means "Don't Care".

NOTE2 : The rising edge of clock is symbolized by  $\uparrow$ .

#### ASYNCHRONOUS TRUTH TABLE(See Notes 1 and 2)

| OE | Operation                    |

|----|------------------------------|

| L  | Read I/O0~I/O17              |

| Н  | Output High-Z                |

| X  | Not Selected, Outputs High-Z |

NOTE1: X means "Don't Care".

NOTE2: For write cycles that following read cycles, the output buffers must be disabled with OE, otherwise data bus contention will occur.

## **ABSOLUTE MAXIMUM RATING\***

| Parameter                                | Symbol | Rating      | Unit |

|------------------------------------------|--------|-------------|------|

| Voltage on VDD Supply Relative to Vss    | Vcc    | -0.5 to 7.0 | V    |

| Voltage on Any Other Pin Relative to Vss | VIN    | -0.5 to 7.0 | V    |

| Power Dissipation                        | PD     | 1.2         | W    |

| Storage Temperature                      | Tstg   | -65 to 150  | °C   |

| Operating Temperature                    | Topr   | 0 to 70     | °C   |

| Storage Temperature Range Under Bias     | TBIAS  | -10 to 85   | °C   |

\*NOTE: Stresses greater than those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **OPERATING CONDITIONS**(0°C≤TA ≤70°C)

| Parameter      | Symbol | Min  | Тур. | Max  | Unit |

|----------------|--------|------|------|------|------|

| Supply Voltage | Vcc    | 4.75 | 5.0  | 5.25 | V    |

| Ground         | Vss    | 0    | 0    | 0    | V    |

## CAPACITANCE\*(TA=25°C, f=1MHz)

| Parameter          | Symbol | Test Condition | Min | Max | Unit |

|--------------------|--------|----------------|-----|-----|------|

| Input Capacitance  | Cin    | VIN=0V         | -   | 5   | pF   |

| Output Capacitance | Соит   | Vout=0V        | -   | 8   | pF   |

<sup>\*</sup>NOTE: Sampled not 100% tested.

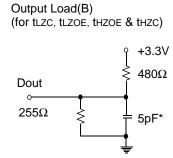

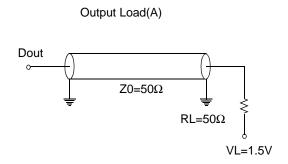

## **TEST CONDITIONS**(TA= 0 to 70°C, VDD=5V±5%, unless otherwise specified)

| Parameter                                           | Value      |

|-----------------------------------------------------|------------|

| Input Pulse Level                                   | 0 to 3V    |

| Input Rise and Fall Time(Measured at 0.3V and 2.7V) | 2ns        |

| Input and Output Timing Reference Levels            | 1.5V       |

| Output Load                                         | See Fig. 1 |

## DC ELECTRICAL CHARACTERISTICS(TA=0 to 70°C, VDD=3.3V±5%)

| Parameter                        | Symbol | Test Conditions                                                        | Min  | Max   | Unit    |    |

|----------------------------------|--------|------------------------------------------------------------------------|------|-------|---------|----|

| Input Leakage Current(except ZZ) | lıL    | VDD=Max ; VIN=Vss to Vcc                                               |      | -2    | +2      | μΑ |

| Output Leakage Current           | lol    | Output Disabled                                                        |      | -2    | +2      | μΑ |

|                                  |        | Vcc=Max                                                                | 15ns | -     | 270     |    |

| Operating Current                | Icc    | IOUT=0mA<br>Cycle Time≥tcYc min                                        | 17ns | -     | 260     | mA |

|                                  |        |                                                                        | 20ns | -     | 250     |    |

| Standby Current                  | ISB    | Device deselected, IouT=0mA, Min<br>Inputs=Viн and Vi∟, Viн≥3V and Vi∟ | -    | 90    | mA      |    |

| Output Low Voltage               | Vol    | IoL=8.0mA                                                              |      | -     | 0.4     | V  |

| Output High Voltage              | Voн    | IOH=-4.0mA                                                             | 2.4  | 3.3   | V       |    |

| Input Low Voltage                | VIL    |                                                                        |      | -0.5* | 0.8     | V  |

| Input High Voltage               | VIH    |                                                                        |      | 2.2   | Vcc+0.5 | V  |

<sup>\*</sup> VIL(Min)=-3.0(Pulse Width≤20ns)

## AC TIMING CHARACTERISTICS(TA=0 to 70°C, Vcc=5V±5%)

|                                     |        | KM718B86-8 |     | KM718B86-9 |     | KM718B86-10 |     | KM718B86-12 |     | 1111 |

|-------------------------------------|--------|------------|-----|------------|-----|-------------|-----|-------------|-----|------|

| Parameter                           | Symbol | Min        | Max | Min        | Max | Min         | Max | Min         | Max | Unit |

| Cycle Time                          | tcyc   | 15         | -   | 15         | -   | 17          | -   | 20          | -   | ns   |

| Clock Access Time                   | tcp    | -          | 8   | -          | 9   | -           | 10  | -           | 12  | ns   |

| Output Enable to Data Valid         | toe    | -          | 5   | -          | 5   | -           | 5   | -           | 6   | ns   |

| Clock High to Output Low-Z          | tLZC   | 6          | -   | 6          | -   | 6           | -   | 6           | -   | ns   |

| Output Hold from Clock High         | tон    | 3          | -   | 3          | -   | 3           | -   | 3           | -   | ns   |

| Output Enable Low to Output Low-Z   | tlzoe  | 0          | -   | 0          | -   | 0           | -   | 0           | -   | ns   |

| Output Enable High to Output High-Z | tHZOE  | 2          | 5   | 2          | 5   | 2           | 5   | 2           | 5   | ns   |

| Clock High to Output High-Z         | tHZC   | -          | 6   | -          | 6   | -           | 6   | -           | 6   | ns   |

| Clock High Pulse Width              | tcH    | 5          | -   | 5          | -   | 5           | -   | 6           | -   | ns   |

| Clock Low Pulse Width               | tCL    | 5          | -   | 5          | -   | 5           | -   | 6           | -   | ns   |

| Address Setup to Clock High         | tas    | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Address Status Setup to Clock High  | tss    | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Data Setup to Clock High            | tDS    | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Write Setup to Clock High           | tws    | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Address/Advance Setup to Clock      | tadvs  | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Chip Select Setup to Clock High     | tcss   | 2.5        | -   | 2.5        | -   | 2.5         | -   | 2.5         | -   | ns   |

| Address Hold from Clock High        | tah    | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

| Address Status Hold from Clock High | tsH    | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

| Data Hold from Clock High           | tDH    | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

| Write Hold from Clock High          | twH    | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

| Address Advance Hold from Clock     | tadvh  | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

| Chip Select Hold from Clock High    | tcsh   | 0.5        | -   | 0.5        | -   | 0.5         | -   | 0.5         | -   | ns   |

NOTE: All address inputs must meet the specified setup and hold times for all rising clock edges whenever ADSC and/or ADSP is sampled low and CS is sampled low. All other synchronous inputs must meet the specified setup and hold times whenever this device is chip selected. Both chip selects must be active whenever ADSC or ADSP is sampled low in order for this device to remain enabled.

<sup>\*</sup> Including Scope and Jig Capacitance

Fig. 1