TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# JT6N57

#### LSIs for Serial Port Controller with Built-in Non-Volatile Memory

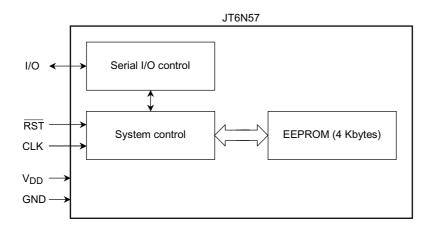

JT6N57 is a low-power-dissipation, low-operating-voltage LSI developed using Toshiba's CMOS and EEPROM technology combined. The LSI integrates a serial I/O controller and 4-KB EEPROM on a single chip. With low power dissipation, 3- to 5-V operating voltage, Sleep mode, and battery level detector, JT6N57 is ideal for hand-held devices and battery-operated systems.

To protect data, JT6N57 can prohibit write to EEPROM when the LSI is abnormal (eg, power supply voltage is low). JT6N57 features protect bits which prevent written data from being erroneously overwritten, a response function which confirms that operation is normal, and a parity check function which confirms that data communications are performed correctly.

#### **Features**

- Built-in EEPROM: 4 Kbytes (32 bytes/page × 128 pages)

- Pins: five (VDD, GND, CLK, RST, I/O (I/O-port-only pin))

- Battery level detector (anti-erroneous EEPROM write operations)

- Byte/Page-write/read function

- Sleep mode (low-power dissipation at standby for input)

- Operating voltage: 2.7 to 5.5 V

- Operating frequency: 1 kHz to 1 MHz (1 kHz to 100 kHz for Page-write)

- · Response function and function to display after reset information about the LSI type

- EEPROM protect bits against erroneous overwrite

- · Parity check function

- Package: chip/wafer

Note: Overwrite time: 8 ms (max)

Number of writes: 10<sup>5</sup> times (provisional) Year for retaining data: 10 years (provisional)

000707EAA

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices." or "TOSHIBA Semiconductor Reliability Handbook" etc..

<sup>•</sup> TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others

<sup>•</sup> The information contained herein is subject to change without notice.

### **Block Diagram**

#### **Pad Functions**

| Pad             | Input or Output | Name and Function                                                                                  |

|-----------------|-----------------|----------------------------------------------------------------------------------------------------|

| I/O             | Input or output | I/O port: Serial interface for external devices. Internally pulled up.                             |

| RST             | Input           | Reset: Input for reset signals from external devices. Schmitt trigger input with internal pull-up. |

| CLK             | Input           | Clock: Input for clock signals from external devices. Schmitt trigger input with internal pull-up. |

| V <sub>DD</sub> | _               | Power supply: Input for power supply from external devices.                                        |

| GND             | _               | Ground: Input for power supply from external devices. (+0 V)                                       |

# **Equivalent Circuit Diagrams**

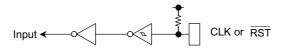

(1) CLK,  $\overline{RST}$

Both CLK and  $\overline{RST}$  are Schmitt trigger inputs with a pull-up resistor.

Figure 1

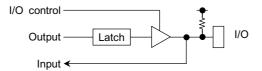

(2) I/O

Serial I/O interface with a pull-up resistor.

Figure 2

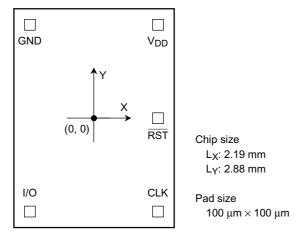

#### **External View**

#### **Pad Coordinates**

(μm, μm)

| Signal | (X Point, Y Point) | Signal   | (X Point, Y Point) |

|--------|--------------------|----------|--------------------|

| RST    | (900, -50)         | $V_{DD}$ | (900, 1060)        |

| CLK    | (900, -1030)       | GND      | (-880, 1050)       |

| I/O    | (-880, -1040)      | _        | _                  |

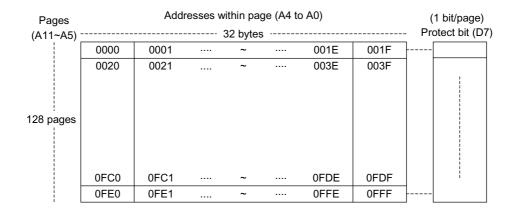

#### 1. Data Memory

Features are listed below:

- 4 Kbytes (32 bytes  $\times$  128 pages)

- Automatic byte overwrite

- Automatic page overwrite (32 bytes)

- Data protection function by protect bits

- Write cycle time: 8 ms (max)

Figure 3 below is the memory map.

Figure 3 Memory Map

#### 2. Write to EEPROM

JT6N57 supports a Page Write mode for 1-byte write and 32-byte (A4 to A0) write, thus implementing high-speed data storing.

#### 3. Protect Bits

JT6N57 supports protect bits which prohibit writes to EEPROM in units of pages. A protect bit prevents data from being erroneously written to or erased from EEPROM. Writing to a protect bit is the same as writing to the EEPROM data area. A protect bit is assigned to each page. The protect bit address uses A11 to A5 to specify the page. A4 to A0 can be any value.

The data bus for input/output of a protect bit is D7.

Once a protect bit is set to disable write to EEPROM, the protect bit cannot be modified.

| Protect Bit (D7) Value | Write to EEPROM Data Area |

|------------------------|---------------------------|

| 0                      | Disable                   |

| 1                      | Enable                    |

#### 4. Basic Timing

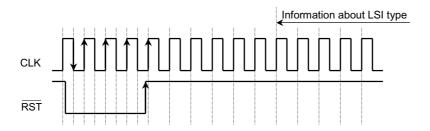

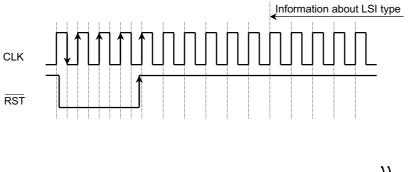

Figure 4 shows the timing when JT6N57 is reset by a reset signal ( $\overline{\text{RST}}$ ). To reset JT6N57, the  $\overline{\text{RST}}$  pin must be Low for 3 CLKs or longer from a CLK falling edge followed by a rising edge. After the reset signal ( $\overline{\text{RST}}$ ) goes High, information about the LSI type is output at the seventh CLK rising edge following the rising edge of the next CLK signal. I/O input can start from the 35th CLK.

Figure 4 Timing at Reset

#### 5. Sleep Mode

At standby for I/O input after reset or at completion of command execution, JT6N57 automatically enters low-power-dissipation state (Sleep mode). JT6N57 is woken up from Sleep mode by command input.

#### 6. Battery Level Detector

Prohibits erroneous write to EEPROM at low power supply voltage to protect data.

If power supply voltage is abnormal, the response function indicates abnormality.

#### 7. Parity Check Function

An even-parity check function is used for data transfer. Whether communication data are transmitted/received correctly is checked.

If data reception is abnormal, the function prohibits command reception, indicating abnormality using the response function.

#### 8. Response Function

Whether command transmission is normal can be checked.

The response function outputs whether there is a parity error or 2-state battery level detector (BLD) error. If operation is normal, outputs 00h.

# Maximum Ratings (levels are shown with $\mbox{GND} = 0 \mbox{ V.}$ )

| Characteristics       | Symbol           | Rating                     | Unit |

|-----------------------|------------------|----------------------------|------|

| Supply voltage        | $V_{DD}$         | -0.5~6.0                   | V    |

| Input voltage         | V <sub>IN</sub>  | -0.5~V <sub>DD</sub> + 0.5 | V    |

| Operating temperature | T <sub>opr</sub> | -40~85                     | °C   |

| Storage temperature   | T <sub>stg</sub> | -55~125                    | °C   |

#### **Electrical Characteristics**

# DC Characteristics (unless otherwise noted, $V_{DD} = 2.7 \sim 5.5 \text{ V}$ , GND = 0 V, Ta = -40~85°C)

| Par                             | ameter                      | Pad             | Symbol            | Test Condition                                  | Min                      | Max                      | Unit |

|---------------------------------|-----------------------------|-----------------|-------------------|-------------------------------------------------|--------------------------|--------------------------|------|

| High-level input voltage        |                             | RST             |                   | _                                               | V <sub>DD</sub><br>× 0.8 | V <sub>DD</sub><br>+ 0.3 | V    |

|                                 |                             | CLK             | V <sub>IH</sub>   | _                                               | V <sub>DD</sub> × 0.7    | V <sub>DD</sub><br>+ 0.3 | V    |

|                                 |                             | I/O             |                   | _                                               | V <sub>DD</sub> × 0.7    | V <sub>DD</sub><br>+ 0.3 | V    |

| Low-level input voltage         |                             | RST —           |                   | _                                               | -0.3                     | V <sub>DD</sub><br>× 0.2 | V    |

|                                 |                             | CLK             | V <sub>IL</sub>   | _                                               | -0.3                     | V <sub>DD</sub><br>× 0.2 | ٧    |

|                                 |                             | I/O             |                   | _                                               | -0.3                     | V <sub>DD</sub><br>× 0.2 | ٧    |

| High-level output voltage       |                             | I/O             | V <sub>OH</sub>   | $I_{OH} = -100 \mu A, V_{DD} = 2.5 V$           | V <sub>DD</sub><br>- 0.8 | V <sub>DD</sub>          | V    |

| Low-level output voltage        |                             |                 | V <sub>OL</sub>   | $I_{OL} = 1 \text{ mA}, V_{DD} = 2.5 \text{ V}$ | 0                        | 0.4                      | V    |

| High-level input current        |                             | RST             | Luc               | $V_{IN} = V_{DD} \times 0.8 \sim V_{DD}$        | -20                      | 10                       | μΑ   |

|                                 |                             | CLK             | I <sub>IH</sub>   | $V_{IN} = V_{DD} \times 0.7 \sim V_{DD}$        | -20                      | 10                       | μА   |

| Low-level input current         |                             | RST             | - I <sub>IL</sub> | $V_{IN} = GND \sim V_{DD} \times 0.12$          | -50                      | -0.1                     | μА   |

|                                 |                             | CLK             |                   | $V_{IN} = GND \sim V_{DD} \times 0.12$          | -50                      | -0.1                     | μΑ   |

| Pull-up resistance              |                             | I/O             | R <sub>IN</sub>   | _                                               | 10                       | 30                       | kΩ   |

| Battery level detection voltage |                             | V <sub>DD</sub> | BLD               | _                                               | 2.10                     | 2.65                     | V    |

| Current dissipation             | Normal conditions           | V <sub>DD</sub> | I <sub>DD</sub>   | V <sub>DD</sub> = 5.5 V, f (CLK) = 1 MHz        | _                        | 7                        | mA   |

|                                 | Battery open check (CLK IN) |                 |                   | V <sub>DD</sub> = 5.5 V, f (CLK) = 1 MHz        | _                        | 70                       | μА   |

|                                 | Sleep mode<br>(CLK H STOP)  |                 |                   | V <sub>DD</sub> = 5.5 V, f (CLK) = 1 MHz        | _                        | 7                        | μΑ   |

# AC Characteristics (unless otherwise noted, $V_{DD} = 2.7 \sim 5.5 \text{ V}$ , GND = 0 V, $Ta = -40 \sim 85 ^{\circ}\text{C}$ )

# AC Characteristics at Byte Write/Read and PAGE Read (values enclosed by square brackets [—] are AC characteristics at page write)

| Parameter                                      | Pad | Symbol            | Test Condition | Min             | Max                         | Unit  |

|------------------------------------------------|-----|-------------------|----------------|-----------------|-----------------------------|-------|

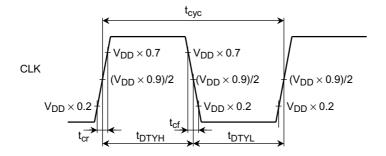

| Clock cycle time                               | CLK | t <sub>cyc</sub>  | Figure 5       | 1.0<br>[10]     | 1000<br>[1000]              | μs    |

| Clock pulse width (high)                       | CLK | t <sub>DTYH</sub> | Figure 5       | 0.35<br>[3.5]   | Tcyc – 0.35<br>[tcyc – 3.5] | μs    |

| Clock pulse width (low)                        | CLK | t <sub>DTYL</sub> | Figure 5       | 0.35<br>[3.5]   | Tcyc – 0.35<br>[tcyc – 3.5] | μs    |

| Clock fall time                                | CLK | t <sub>cf</sub>   | Figure 5       | _               | 100                         | ns    |

| Clock rise time                                | CLK | t <sub>cr</sub>   | Figure 5       | _               | 100                         | ns    |

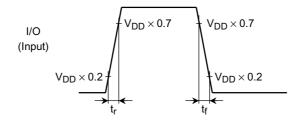

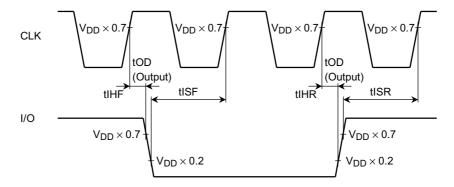

| I/O port fall time                             | I/O | t <sub>f</sub>    | Figure 6       | _               | 200                         | ns    |

| I/O port rise time                             | I/O | t <sub>r</sub>    | Figure 6       | _               | 200                         | ns    |

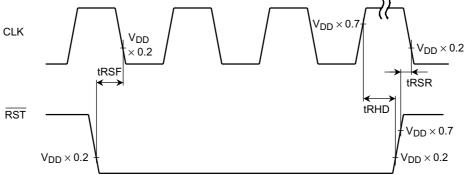

| Setup time:  RST fall to CLK falling time      | RST | tRSF              | Figure 7       | 90              | _                           | ns    |

| Setup time:  RST rise to CLK falling time      | RST | tRSR              | Figure 7       | 90              | _                           | ns    |

| Hold time:  RST rise to CLK rising time        | RST | tRHD              | Figure 7       | 50              | _                           | ns    |

| I/O output delay to CLK rising time            | I/O | tOD               | Figure 6       | _               | 200                         | ns    |

| Hold time:  I/O input rise to CLK rising time  | I/O | tIHR              | Figure 6       | 200             | _                           | ns    |

| Setup time:  I/O input rise to CLK rising time | I/O | tISR              | Figure 6       | 200             | _                           | ns    |

| Hold time:  I/O input fall to CLK rising time  | I/O | tIHF              | Figure 6       | 200             | _                           | ns    |

| Setup time: I/O input fall to CLK rising time  | I/O | tISF              | Figure 6       | 200             | _                           | ns    |

| EEPROM write cycle time                        | _   | twc               | _              | _               | 8                           | ms    |

| EEPROM data hold term                          | _   | _                 | Ta = 85°C      | 10              | _                           | years |

| EEPROM data re-write times (tentative)         | _   | _                 | _              | 10 <sup>5</sup> | _                           | times |

#### **AC Test Conditions**

Figure 5 CLK Input Waveform

Figure 6 I/O Input Waveform

#### **Reset Timing**

To reset JT6N57, the  $\overline{RST}$  pin must be Low for 3 states or longer from a CLK falling edge followed by a rising edge. After the reset signal ( $\overline{RST}$ ) goes High, information about the LSI type is output at the seventh state following the rising edge of the next CLK signal. I/O input can start from the  $35^{th}$  state.

Figure 7 RST Input Waveform