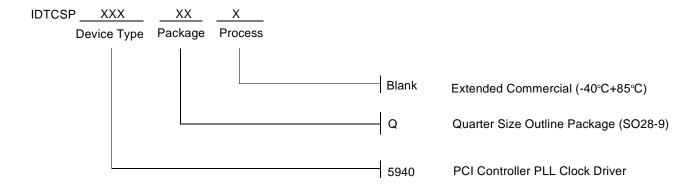

# PCI CONTROLLER PLL CLOCK DRIVER

### IDTCSP5940

#### **FEATURES:**

- 10 Clock Outputs configured in 3 groups

- Internal loop filter

- 5V tolerant inputs

- Output enable (OE)

- PLL lock indicator output

- Extended -40 to 85°C operation

- Low skew guaranteed between outputs

- Sense control input

- Low output jitter

- 3V to 3.6V supply voltage

- Available in 28-pin QSOP package

### **DESCRIPTION:**

The CSP5940 is a high-performance, low skew, low jitter phase locked loop (PLL) clock driver. Two banks of outputs can be programmed to generate multiple copies of different clock frequencies from a single system clock input. The CSP5940 has been specially designed to interface PCI controllers by providing simultaneous 33MHz, 66MHz, and 99MHz clock outputs.

The CSP5940 has an internal RC filter which provides excellent jitter characteristics and eliminates the need for external components. The LOCK output asserts to indicate when phase lock has been achieved.

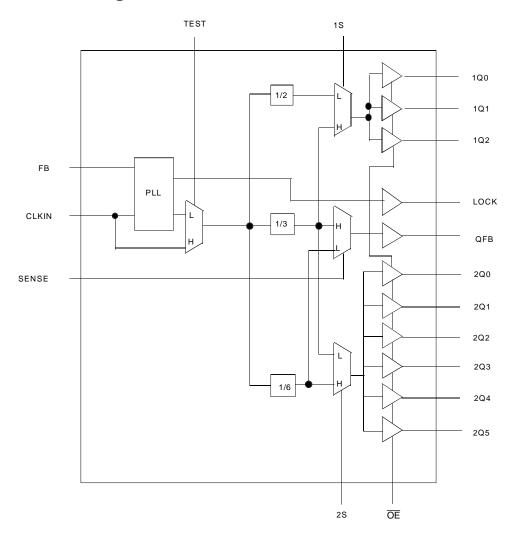

## **Functional Block Diagram**

**EXTENDED COMMERCIAL TEMPERATURE RANGE**

**JULY 1999**

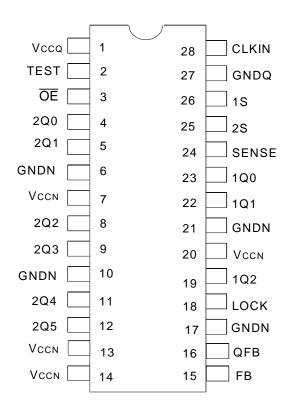

### PIN CONFIGURATION

QSOP TOP VIEW

### **ABSOLUTE MAXIMUM RATING (1)**

| Symbol | Description                           | Max.         | Unit      |

|--------|---------------------------------------|--------------|-----------|

|        | Supply Voltage to Ground              | – 0.5 to + 7 | V         |

|        | DC Input Voltage VIN                  | - 0.5 to + 7 | ٧         |

|        | DC Input Diode Current with VI < 0    | - 20         | mA        |

|        | Maximum Power Dissipation at TA = 70° | .80          | W         |

|        | Ta = 85°                              | .66          |           |

|        | TSTG Storage Temperature              | -65 to 150   | °C        |

|        |                                       | •            | NEW16link |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **CAPACITANCE** (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter(1)       | Min. | Тур. | Max. | Units |

|--------|--------------------|------|------|------|-------|

| CIN    | Input Capacitance  |      | 4    | 6    | pF    |

| Соит   | Output Capacitance | _    | 3    | 6    | pF    |

NEW16lin

### NOTE:

1. Limits guaranteed by characterization only.

### **FREQUENCY SELECTION**

| Sense | 1S | 2S | 1Qx Output  | 2Qx Output  |

|-------|----|----|-------------|-------------|

|       | L  | Χ  | 3 x CLKIN   |             |

| L     | Н  | Х  | 2 x CLKIN   |             |

|       | Х  | L  |             | 2 x CLKIN   |

|       | Х  | Н  |             | 1 x CLKIN   |

|       | L  | Х  | 1.5 x CLKIN |             |

| Н     | Н  | Х  | 1 x CLKIN   |             |

|       | Х  | L  |             | 1 x CLKIN   |

|       | Х  | Н  |             | 0.5 x CLKIN |

# PIN DESCRIPTION

| Pin Name             | Description                                                                                                                                           |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKIN <sup>(1)</sup> | System Clock Input                                                                                                                                    |  |

| FB                   | Feedback Input                                                                                                                                        |  |

| QFB                  | Clock Output for PLL Feedback                                                                                                                         |  |

| SENSE <sup>(1)</sup> | Sense Input from System Control Bus. When LOW, system clock is from 24MHz to 33MHz. When HIGH, system clock is from 48MHz to 66MHz.                   |  |

| 1S <sup>(1)</sup>    | Select Input of Bank 1. When LOW, divide VCO frequency by 2. When HIGH, divide VCO frequency by 3.                                                    |  |

| 1Q0:2                | Clock Outputs of Bank 1                                                                                                                               |  |

| OE                   | Output Enable. Set LOW in normal operation. When HIGH, clock outputs are 3-stated.                                                                    |  |

| 2S <sup>(1)</sup>    | Select Input of Bank 2. When LOW, divide VCO frequency by 3. When HIGH, divide VCO frequency by 6.                                                    |  |

| 2Q0:5                | Clock Outputs of Bank 2                                                                                                                               |  |

| LOCK                 | PLL lock indication signal. HIGH indicates positive lock. LOW indicates that the PLL is not locked and outputs may not be synchronized to the inputs. |  |

| TEST                 | Enables and Disables the PLL. Useful for testing purposes. Set LOW in normal operation.                                                               |  |

| Vcca                 | Power Supply (quiet) for PLL                                                                                                                          |  |

| Vccn                 | Power Supply for Output Buffers                                                                                                                       |  |

| GNDQ                 | Ground Supply (quiet) for PLL                                                                                                                         |  |

| GNDN                 | Ground for Output Buffers                                                                                                                             |  |

#### NOTE:

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = - 40°C to +85°C

| Symbol | Parameter                 | Test Conditions                  | Min. | Typ. <sup>(1)</sup> | Max.  | Unit |

|--------|---------------------------|----------------------------------|------|---------------------|-------|------|

| VIH    | Input HIGH Voltage Level  | Guaranteed Logic HIGH for Inputs | 2    | _                   | -     | ٧    |

| VIL    | Input LOW Voltage Level   | Guaranteed Logic LOW for Inputs  | _    | _                   | 0.8   | V    |

| Vic    | Clamp Diode Voltage Level | Vcc = 3V, lin = -18mA            | _    | - 0.7               | - 1.2 | V    |

| Vон    | Output HIGH Voltage Level | Vcc = 3V, Iон = -12mA            | 2.4  | _                   |       | V    |

|        |                           | Vcc = 3V, Iон = -100µA           | 2.8  | _                   | -     |      |

| Vol    | Output LOW Voltage Level  | Vcc = 3V, lo <sub>L</sub> = 12mA | _    | _                   | .55   | V    |

|        |                           | Vcc = 3V, loL = 100µA            | -    | _                   | 0.2   |      |

| lin    | Input Leakage Current     | Vcc = 3V, Vin = 0V or 5.5V       | _    | _                   | 1     | μA   |

#### NOTE

1. Typical values are at Vcc = 3.3V, +25°C ambient.

SENSE control input should ensure VCO operates at its optimal frequency range from 144MHz to 200MHz. When SENSE is LOW, VCO is running at 6xCLKIN. When SENSE is HIGH, VCO is running at 3xCLKIN. Operation with CLKIN input outside specified frequency ranges may result in invalid or out-of-lock outputs.

### **OUTPUT DRIVE CHARACTERISTICS**

| Symbol | Parameter                      | Test Conditions                      | Min. | Тур. | Max. | Unit |

|--------|--------------------------------|--------------------------------------|------|------|------|------|

| Icco   | Quiescent Power Supply Current | Vcc = 3.6, OE = Test = Vcc, Sense 1S | 1    | 0.6  | 5    | mA   |

|        |                                | = Sense 2S = GND                     |      |      |      |      |

| ICCD   | Dynamic Power Supply Current   | All Outputs Unloaded                 |      | 77   | 130  | mA   |

# OPERATING CHARACTERISTICS, $T_A = 25$ °C

| Symbol | Parameter                          | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| Vcc    | Power Supply Voltage               | 3    | 3.6  | V    |

| VIN    | Input Voltage                      | 0    | 3.6  | V    |

| Vout   | Voltage Applied to 3-State Outputs | 0    | Vcc  | V    |

| TA     | Ambient Operating Temperature      | -40  | 85   | °C   |

### **SWITCHING CHARACTERISTICS (1)**

| Symbol  | Parameter                                                              | Test Conditions <sup>(1)</sup>                                | Min. | Тур. | Max. | Unit |

|---------|------------------------------------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| FCLKIN  | Clock Input Frequency                                                  | Sense = L                                                     | 24   |      | 33   | MHz  |

|         |                                                                        | Sense = H                                                     | 48   |      | 66   |      |

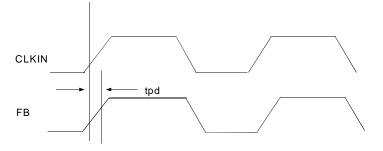

| TPD     | CLKIN input to FB delay <sup>(1)</sup>                                 | Measured at Vcc/2 with AC test load on QFB                    |      |      | 200  | ps   |

| TSKQ    | 1Q output to QFB output skew same transition, same bank <sup>(3)</sup> | Measured at Vcc/2                                             |      |      | 150  | ps   |

| TSK1    | Output to output skew same transition, same bank                       | Measured at Vcc/2                                             |      |      | 200  | ps   |

| TSK2    | Output to output skew same transition, all outputs                     | Measured at Vcc/2                                             |      |      | 200  | ps   |

| TI/OJ   | Input to output jitter Input ref to 1Q output 1000 samples             | Measured TR of ref to TR of 1Q SPEC in RMS and peak to peak   |      |      |      |      |

| TI/OJcc | Input to output jitter Input ref to 1Q output 1000 samples             | Measured TR of ref to TR of 1Q SPEC in RMS and cycle to cycle |      |      |      |      |

|         |                                                                        | fCLKIN = 66MHz, 1Qn = 66MHz,<br>2Qn = 66MHz                   |      |      | ±100 |      |

| TJ      | Cycle to cycle jitter <sup>(1)</sup> Peak to peak                      | fCLKIN = 66MHz, 1Qn = 66MHz,<br>2Qn = 33MHz                   |      |      | ±100 | ps   |

|         |                                                                        | fCLKIN = 33MHz, 1Qn = 99MHz,<br>2Qn = 66MHz                   |      |      | ±100 |      |

| TPW     | Ouput duty cycle distortion <sup>(1, 2)</sup>                          | Measured at Vcc/2                                             | 45%  |      | 55%  |      |

| TLOCK   | CLKIN to phase lock                                                    |                                                               |      | 0.1  | 0.5  | ms   |

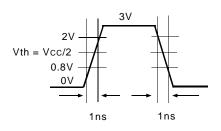

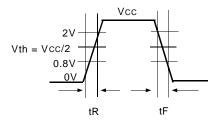

| TR      | Rise Time <sup>(1)</sup>                                               | 0.8V to 2V                                                    |      | 0.7  | 1.5  | ns   |

| TF      | Fall Times <sup>(1)</sup>                                              | 2V to 0.8V                                                    |      | 0.7  | 1.5  | ns   |

#### NOTES:

- 1. Limits guaranteed by characterization but not tested.

- 2. Output signal is nominally 50% duty cycle: maximum error is ±5% of the period.

- 3. TSKQ is measured from TR of 1Q to TR of QFB.

### **TIMING DIAGRAM**

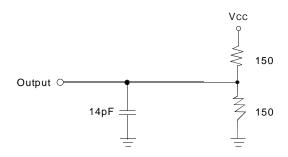

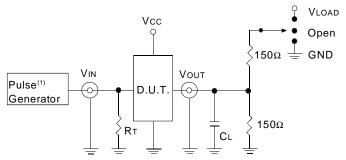

Figure 1. AC Test Load and Waveforms

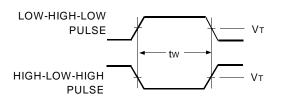

**Figure 2. Input Test Waveform**

Figure 3. AC Timing Diagram

Figure 4. Output Waveform

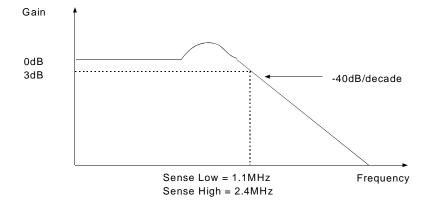

Figure 5. F\_3dB Closed Loop Frequency

### **TEST CIRCUITS AND WAVEFORMS:**

### **TEST CONDITIONS**

| Symbol | Vcc <sup>(1)</sup> = 3.3V±0.3V | Unit |

|--------|--------------------------------|------|

| VLOAD  | 6                              | V    |

| ViH    | 2.7                            | V    |

| VT     | 1.5                            | V    |

| VLZ    | 300                            | mV   |

| VHZ    | 300                            | mV   |

| CL     | 14                             | pF   |

### **TEST CIRCUITS FOR ALL OUTPUTS**

#### **DEFINITIONS:**

CL= Load capacitance: includes jig and probe capacitance.

$\mathsf{RT} = \mathsf{Termination}$  resistance: should be equal to  $\mathsf{ZOUT}$  of the Pulse Generator.

#### NOTE:

1. Pulse Generator for All Pulses: Rate  $\leq$  10MHz; tF  $\leq$  2.5ns; tR  $\leq$  2.5ns.

### **SWITCH POSITION**

| Test            | Switch    |

|-----------------|-----------|

| Open Drain      | Vload     |

| Disable Low     |           |

| Enable Low      |           |

| Disable High    | GND       |

| Enable High     |           |

| All Other tests | Open      |

|                 | NEW16link |

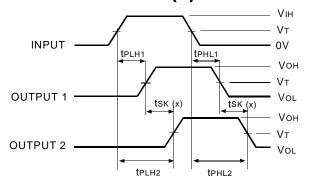

### OUTPUT SKEW - TSK (x)

tsk(x) = |tplh2 - tplh1| or |tphl2 - tphl1|

#### NOTES:

- 1. For tsk2 OUTPUT1 and OUTPUT2 are any two outputs.

- 2. For tsk1 OUTPUT1 and OUTPUT2 are in the same bank.

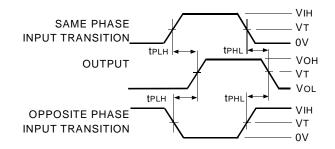

### PROPAGATION DELAY

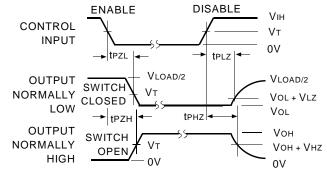

### **ENABLE AND DISABLE TIMES**

#### NOTE:

Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

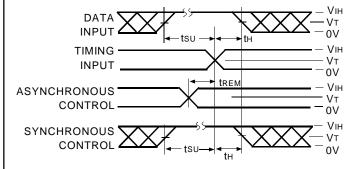

# SET-UP, HOLD, AND RELEASE TIMES

### **PULSE WIDTH**

### ORDERING INFORMATION

CORPORATE HEADQUARTERS

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*