## Frequency Generator & Integrated Buffers for PENTIUM™

#### **General Description**

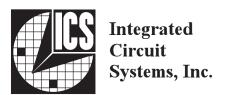

The ICS9147-06 generates all clocks required for high speed RISC or CISC microprocessor systems such as Intel PentiumPro. Two different reference frequency multiplying factors are externally selectable with smooth frequency transitions. Glitch-free Stop clock control is provided for CPU and BUS clocks. Complete chip low current mode is achieved with the Power Down# pin.

High drive BUS outputs typically provide greater than 1V/ns slew rate into  $30\,\text{pF}$  loads. CPU outputs typically provide better than 1V/ns slew rate into  $20\,\text{pF}$  loads while maintaining  $50\pm5\%$  duty cycle. The REF and IOAPIC clock outputs typically provide better than 0.5V/ns slew rates. Separate buffer supply pins VDDL allow for nominal 3.3V voltage or reduced voltage swing (from 2.9 to 2.5V) for CPU (1:4) and IOAPIC outputs.

#### **Block Diagram**

#### **Features**

- Generates five processor, eight bus, four 14.31818 MHz, two 48 MHz clocks for USB support and one 24 MHz clock.

- CPU to BUS clock skew 1 to 4ns (CPU early)

- Synchronous clocks skew matched to 250ps window on CPU and 500ps window on BUS.

- Selectable multiplying ratios

- · Glitch free stop clock controls CPUEN and BUSEN

- 3.0V 3.7V supply range, 2.5V to VDD supply range for CPU (1:4) clocks and IOAPIC clock.

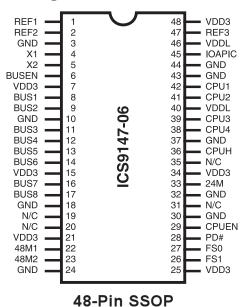

- 48-pin SSOP package

#### **Pin Configuration**

Pentium is a trademark of Intel Corporation

# **Functionality**

| PD# | BUSEN | CPUEN | FS1 | FS0 | CPU (1:4)<br>CPUH | BUS      | REF<br>IOAPIC | 24<br>(MHz) | 48<br>(MHz) |

|-----|-------|-------|-----|-----|-------------------|----------|---------------|-------------|-------------|

| 1   | 1     | 1     | 0   | 0   | Tristate          | Tristate | Tristate      | Tristate    | Tristate    |

| 1   | 1     | 1     | 0   | 1   | 60                | 30       | 14.31818      | 24          | 48          |

| 1   | 1     | 1     | 1   | 0   | 66.6              | 33.3     | 14.31818      | 24          | 48          |

| 1   | 1     | 1     | 1   | 1   | REF/2             | REF/4    | REF           | REF/4       | REF/2       |

| 1   | 1     | 0     | X   | X   | LOW               | Running  | 14.31818      | 24          | 48          |

| 1   | 0     | 1     | X   | X   | Running           | LOW      | 14.31818      | 24          | 48          |

| 0   | X     | X     | X   | X   | LOW               | LOW      | LOW           | LOW         | LOW         |

# **Pin Descriptions**

| PIN NUMBER                           | PIN NAME         | TYPE | DESCRIPTION                                                                                                                                |

|--------------------------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 47                             | REF1, REF2, REF3 | OUT  | 14.318 MHz reference clock outputs.                                                                                                        |

| 3, 10, 18, 24, 30, 32,<br>37, 43, 44 | GND              | PWR  | Ground.                                                                                                                                    |

| 4                                    | X1               | IN   | Crystal input, has internal crystal load capacitor, and feedback resistor from X2. Nominally 14.31818MHz.                                  |

| 5                                    | X2               | OUT  | Crystal output, has internal crystal load capacitor                                                                                        |

| 8, 9, 11, 12, 13, 14,<br>16, 17      | BUS (1:8)        | OUT  | BUS clock outputs, operates synchronously at CPU/2.                                                                                        |

| 26, 27                               | FS (0:1)         | IN   | Select pin for enabling CPU and BUS clock frequencies.*                                                                                    |

| 7, 15, 21, 25, 34, 48                | VDD3             | PWR  | Core and Buffer output clock power supply.                                                                                                 |

| 22, 23                               | 48M (1:2)        | OUT  | 48 MHz clock output                                                                                                                        |

| 28                                   | PD#              | IN   | Device power down input, stops outputs low and shuts off crystal oscillator and PLLs when low.*                                            |

| 29                                   | CPUEN            | IN   | Output enable for all CPU clocks, a logic low will Stop low all CPU clocks.*                                                               |

| 36                                   | СРИН             | OUT  | 3.3 (VDD3 dependent) CPU clock output                                                                                                      |

| 38, 39, 41, 42                       | CPU (1:4)        | OUT  | CPU clock output clocks, operates at VDDL supply voltage (with IOAPIC), either nominal 3.3V VDD or reduced voltage 2.9 to 2.5V.            |

| 6                                    | BUSEN            | IN   | Output enable for all BUS clock, a logic low will stop Low all Bus clocks.*                                                                |

| 45                                   | IOAPIC           | OUT  | IOAPIC clock output. (14.318 MHz), operates at VDDL supply voltage with CPU (1:4), either nominal 3.3V VDD or reduced voltage 2.9 to 2.5V. |

| 40, 46                               | VDDL             | PWR  | Power supply for CPU and IOAPIC block buffers, operates at nominal 3.3V VDD or reduced voltage 2.9 to 2.5V.                                |

| 33                                   | 24M              | OUT  | 24 MHz clock output                                                                                                                        |

<sup>\*</sup> Has internal pull-up to  $V_{\text{DD3}}$ .

## **Absolute Maximum Ratings**

Supply Voltage ...... 7.0 V

Logic Inputs . . . . . . . . . . . . . GND -0.5~V to  $~V_{DD}$  +0.5~V

Ambient Operating Temperature . . . . .  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature . . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics at 3.3V**

$V_{DDL}=V_{DD3}=3.0-3.7 \text{ V}, T_A=0-70^{\circ} \text{ C}$  unless otherwise stated

| DC Characteristics  |                   |                                                                                  |                    |          |        |       |  |  |  |

|---------------------|-------------------|----------------------------------------------------------------------------------|--------------------|----------|--------|-------|--|--|--|

| PARAMETER           | SYMBOL            | TEST CONDITIONS                                                                  | MIN                | TYP      | MAX    | UNITS |  |  |  |

| Input Low Voltage   | V <sub>IL</sub>   |                                                                                  | - ()               |          | 0.2VDD | V     |  |  |  |

| Input High Voltage  | V <sub>IH</sub>   |                                                                                  | 0.7V <sub>DD</sub> | <u> </u> | -      | V     |  |  |  |

| Input Low Current   | I <sub>IL</sub> / | VIN=0V                                                                           | -28.0              | -10.5    | -      | μΑ    |  |  |  |

| Input High Current  | I                 | VIN=VDD                                                                          | -5.0               | -        | 5.0    | μΑ    |  |  |  |

| Output Low Current  | I <sub>Ob1</sub>  | VOL=0.8V;<br>for CPUH, BUS & REF1<br>(and CPU & IOAPIC at VDDL= 3.0<br>to 3.7V)  | <u>)</u>           | 33.0     | -      | mA    |  |  |  |

| Output High Current | I <sub>OH1</sub>  | VOH=2.0V;<br>for CPUH, BUS & REF1<br>(and CPU & IOAPIC at VDDL = 3.0<br>to 3.7V) |                    | -28.0    |        | mA    |  |  |  |

| Output Low Current  | I <sub>OL2</sub>  | VOL=0.8V; REF (2:3), 24, 48 CLKs                                                 | <u>-</u> (O)       | 26.0     | -      | mA    |  |  |  |

| Output High Current | I <sub>OH2</sub>  | VOH=2.0V; REF (2:3), 24, 48 CLKs                                                 |                    | -21.0    | -      | mA    |  |  |  |

| Output Low Current  | I <sub>OL3</sub>  | VOL=0.8V; for CPUL at<br>VDDL = 2.5V                                             | <b>\(\)</b> - \(\) | 26       | -      | mA    |  |  |  |

| Output High Current | ОНЗ               | VOH = 1.7V; for CPUL at<br>VDDL = 2.5V                                           |                    | 24       | -      | mA    |  |  |  |

| Output Low Voltage  | V <sub>OL1</sub>  | IOL = 10mA;<br>for CPUH, BUS & REF1<br>(and CPUL at VDDL = 3.0 to 3.7V)          | <u> </u>           | 0.22     | 0.4    | V     |  |  |  |

| Output High Voltage | V <sub>OH1</sub>  | IOH = -10mA;<br>for CPUH, BUS & REF<br>(and CPUL at VDDL = 3.0 to 3.7V)          | 2.4                | 2.8      | -      | V     |  |  |  |

| Output Low Voltage  | $v_{\rm OL2}$     | IOL = 8mA                                                                        | -                  | 0.25     | 0.4    | V     |  |  |  |

| Output High Voltage | V <sub>OH2</sub>  | IOH = -8mA                                                                       | 2.4                | 2.6      | -      | V     |  |  |  |

| Output Low Voltage  | V <sub>OL3</sub>  | IOL = 8 mA; for CPUL at<br>VDDL = 2.5V                                           | -                  | 0.25     | 0.4    | V     |  |  |  |

| Output High Voltage | V <sub>OH3</sub>  | IOH = -8mA; for CPUL at<br>VDDL = 2.5V                                           | 2.1                | 2.25     | -      | V     |  |  |  |

| Supply Current      | I <sub>DD</sub>   | @66.6 MHz; all outputs unloaded                                                  | -                  | 70       | 140    | mA    |  |  |  |

| Supply Current      | I <sub>DD</sub>   | PD#                                                                              |                    | 230      | 500    | μΑ    |  |  |  |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

## **Electrical Characteristics at 3.3V**

$V_{DDL}=V_{DD3}=3.0-3.7~V,~T_A=0-70^{\circ}\,\mathrm{C}$  unless otherwise stated

|                                           |                 | AC Characteristics                                               |                   |        |      |       |

|-------------------------------------------|-----------------|------------------------------------------------------------------|-------------------|--------|------|-------|

| PARAMETER                                 | SYMBOL          | TEST CONDITIONS                                                  | MIN               | TYP    | MAX  | UNITS |

| Rise Time <sup>1</sup>                    | Tr1             | 20pF load, 0.8 to 2.0V<br>CPU, BUS & REF1                        | -                 | 0.9    | 1.5  | ns    |

| Fall Time <sup>1</sup>                    | Tf1             | 20pF load, 2.0 to 0.8V<br>CPU, BUS & REF1                        | -                 | 0.8    | 1.4  | ns    |

| Rise Time <sup>1</sup>                    | Tr2             | 20pF load, 20% to 80%<br>CPU, BUS & REF1                         | -                 | 1.5    | 2.5  | ns    |

| Fall Time <sup>1</sup>                    | Tf2             | 20pF load, 80% to 20%<br>CPU, BUS & REF1                         | <u> </u>          | (1.4   | 2.4  | ns    |

| Rise Time <sup>1</sup>                    | Tr1             | 30pF load, 0.8 to 2.0V<br>CPU, BUS & REF1                        | -/-               | 0.9    | 1.5  | ns    |

| Fall Time <sup>1</sup>                    | Tf1             | 30pF load, 2.0 to 0.8V<br>CPU, BUS & REF1                        | (-)               | 0.8    | 1.4  | ns    |

| Rise Time <sup>1</sup>                    | Tr2             | 30pF load, 20% to 80%<br>CPU, BUS & REF1                         |                   | 1.5    | 2.5  | ns    |

| Fall Time <sup>1</sup>                    | T <sub>f2</sub> | 30pF load, 80% to 20%<br>CPU, BUS & REF1                         |                   | 1.4    | 2.4  | ns    |

| Rise Time <sup>1</sup>                    | Tr3             | 20pF load, 0.8 to 2.0V<br>24 & 48 clocks & REF (2:3)             | -                 | -      | -    | ns    |

| Fall Time <sup>1</sup>                    | Tf3             | 20pF load, 2.0 to 0.8V<br>24 & 48 clocks & REF (2:3)             | -                 | -      |      | ns    |

| Rise Time <sup>1</sup>                    | Tr4             | 20pF load, 0.4 to 2.0V , CPU with VDDL = 2.5V and IOAPIC         | -                 | - (    | 1.6  | ns    |

| Fall Time <sup>1</sup>                    | Tf4             | 20pF load, 2.0 to 0.4V, CPU with VDDL = 2.5V and IOAPIC          | // <sub>/</sub> - |        | 1.6  | ns    |

| Duty Cycle <sup>1</sup>                   | Dt1             | 20pF load @ VOUT=1.4V                                            | 45                | 50     | 55   | %     |

| Duty Cycle                                | Dt2             | REF (1:3)                                                        | $10^{\circ}$      | 45     | 50   | %     |

| Jitter, One Sigma <sup>1</sup>            | Tjis1           | CPU & Fixed BUS Load=20pF,<br>BUS; Load = 30pF                   | -4                | 50     | 150  | ps    |

| Jitter, Absolute <sup>1</sup>             | Tjab1           | CPU & Fixed BUS Load=20pF,<br>BUS; Load = 30pF                   | -250              | -      | 250  | ps    |

| Jitter, One Sigma <sup>1</sup>            | Tjis2           | REF1; Load = 47pF                                                | ⟨/⟩⟩-             | 55     | 250  | ps    |

| Jitter, Absolute <sup>1</sup>             | Tjab2           | REF1; Load = 47pF                                                | -500              | 200    | 500  | ps    |

| Input Frequency <sup>1</sup>              | Fi              |                                                                  | 12.0              | 14.318 | 16.0 | MHz   |

| Logic Input Capacitance <sup>1</sup>      | CIN             | Logic input pins                                                 | -                 | 5      | -    | pF    |

| Oscillator Input Capacitance <sup>1</sup> | CINX            | X1, X2 pins                                                      | -                 | 18     | -    | pF    |

| Power-on Time <sup>1</sup>                | ton             | From VDD=3.0V to 1st crossing of 66.6 MHz VDD supply ramp < 1 ms | -                 | 1.5    | 3.0  | ms    |

| Clock Skew <sup>1</sup>                   | Tsk1            | CPU to CPU; Load=20pF; @1.4V (Same VDD)                          | -                 | 150    | 250  | ps    |

| Clock Skew <sup>1</sup>                   | Tsk2            | BUS to BUS; Load=20pF; @1.4V                                     | -                 | 300    | 500  | ps    |

| Clock Skew <sup>1</sup>                   | Tsk3            | CPU to BUS; Load=20pF; @1.4V (CPU is early) (All at 3.3V)        | 1                 | 3.3    | 4    | ns    |

| Clock Skew <sup>1</sup>                   | Tsk4<br>Tsk5    | CPU @ 2.5 to CPUH @ 3.3V<br>CPU @ 2.5V to BUS @ 3.3V             |                   |        |      |       |

|                                           | Tsk6            | REF @ 3.3V to IOAPIC @ 2.5V                                      |                   |        |      |       |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

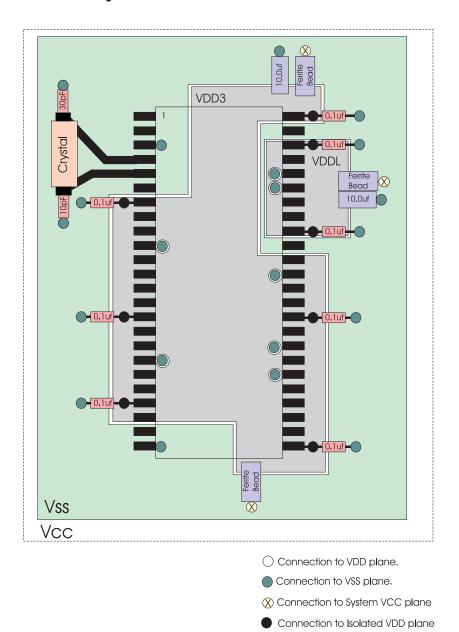

#### **Recommended PCB Layout for ICS9147-06**

#### NOTE:

This PCB Layout is based on a 4 layer board with an internal Ground (common) and Vcc plane. Placement of components will depend on routing of signal trace. The 0.1uf Capacitors should be placed as close as possible to the Power pins. Placement on the backside of the board is also possible. The Ferrite Beads can be replaced with 10-150hm Resistors. For best results, use a Fixed Voltage Regulator between the main (board) Vcc and the different Vdd planes.

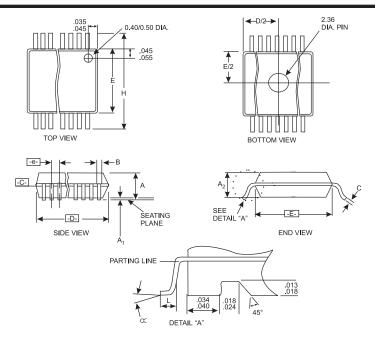

### **SSOP Package**

| SYMBOL | COMMON DIMENSIONS |              |       | VARIATIONS | D    |      |      | N  |

|--------|-------------------|--------------|-------|------------|------|------|------|----|

|        | MIN.              | NOM.         | MAX.  |            | MIN. | NOM. | MAX. |    |

| A      | .095              | .101         | .110  | AC         | .620 | .625 | .630 | 48 |

| A1     | .008              | .012         | .016  |            |      |      |      |    |

| A2     | .088              | .090         | .092  |            |      |      |      |    |

| В      | .008              | .010         | .0135 |            |      |      |      |    |

| C      | .005              | -            | .010  |            |      |      |      |    |

| D      |                   | See Variatio | ns    |            |      |      |      |    |

| Е      | .292              | .296         | .299  |            |      |      |      |    |

| e      | 0.025 BSC         |              |       |            |      |      |      |    |

| Н      | .400              | .406         | .410  |            |      |      |      |    |

| h      | .010              | .013         | .016  |            |      |      |      |    |

| L      | .024              | .032         | .040  |            |      |      |      |    |

| N      | See Variations    |              |       |            |      |      |      |    |

| ~      | 0°                | 5°           | 8°    |            |      |      |      |    |

| X      | .085              | .093         | .100  |            |      |      |      |    |

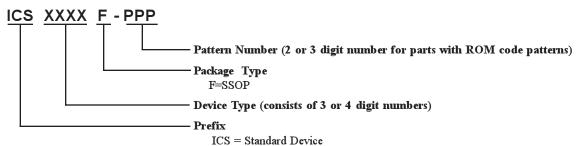

## **Ordering Information**

ICS9147F-06

Example: