Data Sheet May 2001 File Number 3403.4

# Dual, Low Power CMOS Operational Amplifiers

The ICL761X/762X series is a family of monolithic CMOS operational amplifiers. These devices provide the designer with high performance operation at low supply voltages and selectable quiescent currents. They are an ideal design tool when ultra low input current and low power dissipation are desired.

The basic amplifier will operate at supply voltages ranging from  $\pm 1 \text{V}$  to  $\pm 8 \text{V}$ , and may be operated from a single Lithium cell. The output swing ranges to within a few millivolts of the supply voltages.

The quiescent supply current of these amplifiers is set to  $100\mu A$  at the factory. This results in power consumption as low as  $200\mu W$  per amplifier.

Of particular significance is the extremely low (1pA) input current, input noise current of  $0.01 pA/\sqrt{Hz}$ , and  $10^{12}\Omega$  input impedance. These features optimize performance in very high source impedance applications.

The inputs are internally protected. Outputs are fully protected against short circuits to ground or to either supply.

Because of the low power dissipation, junction temperature rise and drift are quite low. Applications utilizing these features may include stable instruments, extended life designs, or high density packages.

## Ordering Information

| DART NUMBER   | TEMP.<br>RANGE (°C) | DACKACE                                                | PKG.  |  |

|---------------|---------------------|--------------------------------------------------------|-------|--|

| PART NUMBER   | RANGE (*C)          | PACKAGE                                                | NO.   |  |

| ICL7621BCPA   | 0 to 70             | 8 Ld PDIP -<br>B Grade - I <sub>Q</sub> = 100μA        | E8.3  |  |

| ICL7621DCPA   | 0 to 70             | 8 Ld PDIP -<br>D Grade - I <sub>Q</sub> = 100μA        | E8.3  |  |

| ICL7621DCBA   | 0 to 70             | 8 Ld SOIC -<br>D Grade - I <sub>Q</sub> = 100μA        | M8.15 |  |

| ICL7621DCBA-T | 0 to 70             | 8 Ld SOIC - D Grade - Tape and Reel - $I_Q = 100\mu A$ | M8.15 |  |

#### **Features**

| • Wide Operating Voltage Range $\pm 1 \text{V}$ to $\pm 8 \text{V}$ |

|---------------------------------------------------------------------|

| • High Input Impedance                                              |

| Input Current Lower Than BIFETs 1pA (Typ)                           |

| Output Voltage Swing                                                |

| Available as Duals (Refer to ICL7611 for Singles)                   |

| Low Power Replacement for Many Standard Op Amps                     |

## **Applications**

- · Portable Instruments

- Telephone Headsets

- · Hearing Aid/Microphone Amplifiers

- Meter Amplifiers

- Medical Instruments

- · High Impedance Buffers

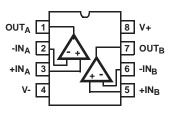

## **Pinouts**

ICL7621 (PDIP, SOIC)

TOP VIEW

#### **Absolute Maximum Ratings**

| Supply Voltage V+ to V                    |                       |

|-------------------------------------------|-----------------------|

| Input Voltage                             | V0.3 to V+ +0.3V      |

| Differential Input Voltage (Note 1)       | [(V+ +0.3) - (V0.3)]V |

| Duration of Output Short Circuit (Note 2) | Unlimited             |

### **Operating Conditions**

**Electrical Specifications**

**PARAMETER**

Supply Current (Per Amplifier)

**Channel Separation**

Overshoot Factor

Slew Rate

Rise Time

| Temperature Range |             |

|-------------------|-------------|

| ICL7621C          | 0°C to 70°C |

#### **Thermal Information**

TEMP. (°C) | MIN

25

25

25

25

25

0.1

120

0.16

2

10

0.25

0.1

120

0.16

2

0.25

mΑ

dB

V/µs

μs

| Thermal Resistance (Typical, Note 3)  | $\theta_{JA}$ (oC/W) | $\theta_{JC}$ (oC/W) |  |  |  |

|---------------------------------------|----------------------|----------------------|--|--|--|

| PDIP Package                          | 120                  | N/A                  |  |  |  |

|                                       |                      | N/A                  |  |  |  |

|                                       |                      |                      |  |  |  |

|                                       |                      |                      |  |  |  |

| Maximum Lead Temperature (Soldering 1 | 0s)                  | 300°C                |  |  |  |

| (SOIC - Lead Tips Only)               |                      |                      |  |  |  |

ICL7621B

TYP MAX MIN

ICL7621D

TYP MAX UNITS

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

1. Long term offset voltage stability will be degraded if large input differential voltages are applied for long periods of time.

**TEST CONDITIONS**

V<sub>SUPPLY</sub> = ±5V, Unless Otherwise Specified

- 2. The outputs may be shorted to ground or to either supply, for V<sub>SUPPLY</sub> ≤10V. Care must be taken to insure that the dissipation rating is not exceeded.

- 3.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

SYMBOL

| Input Offset Voltage                                            | Vos                  | $R_S \le 100 k\Omega$                                        | 25         | -    | -                | 5    | -    | -                | 15   | mV                 |

|-----------------------------------------------------------------|----------------------|--------------------------------------------------------------|------------|------|------------------|------|------|------------------|------|--------------------|

|                                                                 |                      |                                                              | Full       | -    | -                | 7    | -    | -                | 20   | mV                 |

| Temperature Coefficient of VOS                                  | ΔV <sub>OS</sub> /ΔT | $R_S \le 100 k\Omega$                                        | -          | -    | 15               | -    | -    | 25               | -    | μV/ <sup>o</sup> C |

| Input Offset Current                                            | los                  |                                                              | 25         | -    | 0.5              | 30   | -    | 0.5              | 30   | pА                 |

|                                                                 |                      |                                                              | 0 to 70    | -    | -                | 300  | -    | -                | 300  | pА                 |

|                                                                 |                      |                                                              | -55 to 125 | -    |                  | 800  | -    |                  | 800  | pA                 |

| Input Bias Current                                              | I <sub>BIAS</sub>    |                                                              | 25         | -    | 1.0              | 50   | -    | 1.0              | 50   | pA                 |

|                                                                 |                      |                                                              | 0 to 70    | -    | -                | 400  | -    | -                | 400  | рА                 |

|                                                                 |                      |                                                              | -55 to 125 | -    | -                | 4000 | -    | -                | 4000 | pА                 |

| Common Mode Voltage Range                                       | V <sub>CMR</sub>     | $I_Q = 100\mu A$                                             | 25         | ±4.2 | -                | -    | ±4.2 | -                | -    | V                  |

| Output Voltage Swing                                            | Vout                 | $I_Q = 100 \mu A$ , $R_L = 100 k Ω$                          | 25         | ±4.9 | -                | -    | ±4.9 | -                | -    | V                  |

|                                                                 |                      |                                                              | 0 to 70    | ±4.8 | -                | -    | ±4.8 | -                | -    | V                  |

|                                                                 |                      |                                                              | -55 to 125 | ±4.5 | -                | -    | ±4.5 | -                | -    | V                  |

| Large Signal<br>Voltage Gain                                    | A <sub>VOL</sub>     | $V_O = \pm 4.0 V$ , $R_L = 100 k \Omega$ , $I_Q = 100 \mu A$ | 25         | 80   | 102              | -    | 80   | 102              | -    | dB                 |

|                                                                 |                      |                                                              | 0 to 70    | 75   | -                | -    | 75   | -                | -    | dB                 |

|                                                                 |                      |                                                              | -55 to 125 | 68   | -                | -    | 68   | -                | -    | dB                 |

| Unity Gain Bandwidth                                            | GBW                  | $I_Q = 100\mu A$                                             | 25         | -    | 0.48             | -    | -    | 0.48             | -    | MHz                |

| Input Resistance                                                | R <sub>IN</sub>      |                                                              | 25         | -    | 10 <sup>12</sup> | -    | -    | 10 <sup>12</sup> | -    | Ω                  |

| Common Mode Rejection Ratio                                     | CMRR                 | $R_S \le 100 k\Omega$ , $I_Q = 100 \mu A$                    | 25         | 70   | 91               | -    | 70   | 91               | -    | dB                 |

| Power Supply Rejection Ratio (V <sub>SUPPLY</sub> = ±8V to ±2V) | PSRR                 | $R_S \le 100 k\Omega$ , $I_Q = 100 \mu A$                    | 25         | 80   | 86               | -    | 80   | 86               | -    | dB                 |

| Input Referred Noise Voltage                                    | e <sub>N</sub>       | $R_S = 100\Omega$ , $f = 1kHz$                               | 25         | -    | 100              | -    | -    | 100              | -    | nV/√Hz             |

| Input Referred Noise Current                                    | i <sub>N</sub>       | $R_S = 100\Omega$ , $f = 1kHz$                               | 25         | -    | 0.01             | -    | -    | 0.01             | -    | pA/√ <del>Hz</del> |

| No Signal, No Load, I<sub>Q</sub> = 100μA

$A_V = 1$ ,  $C_L = 100pF$ ,  $V_{IN} = 8V_{P-P}$ ,

$I_Q = 100\mu A$ ,  $R_L = 100k\Omega$

$I_Q = 100\mu A$ ,  $R_L = 100k\Omega$

$I_Q = 100\mu A$ ,  $R_L = 100k\Omega$

$V_{IN} = 50 \text{mV}, C_L = 100 \text{pF},$

$V_{IN} = 50 \text{mV}, C_L = 100 \text{pF},$

ISUPPLY

V<sub>01</sub>/V<sub>02</sub>

SR

$t_R$

OS

$A_{V} = 100$

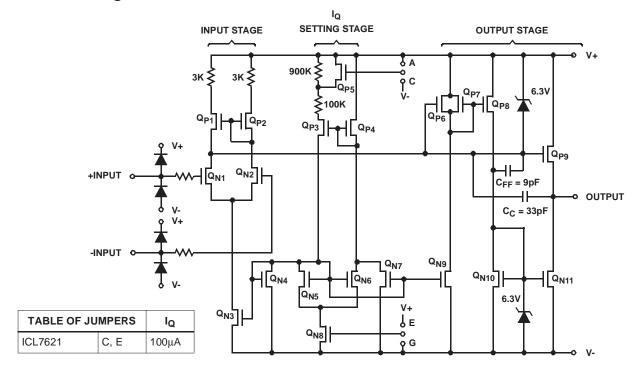

## Schematic Diagram

## Application Information

### Static Protection

All devices are static protected by the use of input diodes. However, strong static fields should be avoided, as it is possible for the strong fields to cause degraded diode junction characteristics, which may result in increased input leakage currents.

#### Latchup Avoidance

Junction-isolated CMOS circuits employ configurations which produce a parasitic 4-layer (PNPN) structure. The 4-layer structure has characteristics similar to an SCR, and under certain circumstances may be triggered into a low impedance state resulting in excessive supply current. To avoid this condition, no voltage greater than 0.3V beyond the supply rails may be applied to any pin. In general, the op amp supplies must be established simultaneously with, or before any input signals are applied. If this is not possible, the drive circuits must limit input current flow to 2mA to prevent latchup.

#### Choosing the Proper IQ

Each device in the ICL76XX family has a similar  $I_Q$  setup scheme, which allows the amplifier to be set to nominal quiescent currents of  $10\mu A$ ,  $100\mu A$  or 1mA. These current settings change only very slightly over the entire supply voltage range. The ICL7611/12 have an external  $I_Q$  control terminal, permitting user selection of each amplifiers' quiescent current. The ICL7621 has a fixed  $I_Q$  setting of  $100\mu A$ .

#### Output Stage and Load Driving Considerations

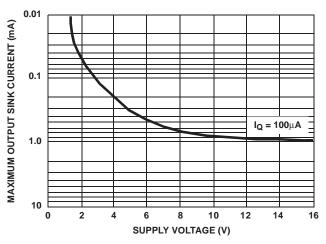

Each amplifiers' quiescent current flows primarily in the output stage. This is approximately 70% of the  $I_Q$  settings. This allows output swings to almost the supply rails for output loads of  $1M\Omega$ ,  $100k\Omega$ , and  $10k\Omega$ , using the output stage in a highly linear class A mode. In this mode, crossover distortion is avoided and the voltage gain is maximized. However, the output stage can also be operated in Class AB for higher output currents. (See graphs under Typical Operating Characteristics). During the transition from Class A to Class B operation, the output transfer characteristic is nonlinear and the voltage gain decreases.

#### Frequency Compensation

The ICL76XX are internally compensated, and are stable for closed loop gains as low as unity with capacitive loads up to 100pF.

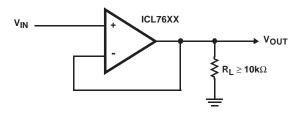

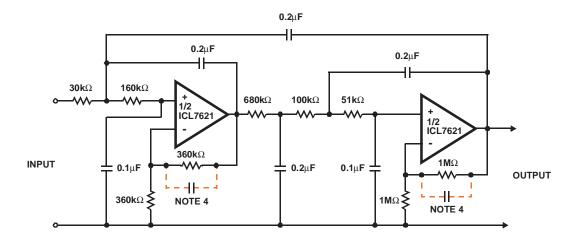

# **Typical Applications**

The user is cautioned that, due to extremely high input impedances, care must be exercised in layout, construction,

FIGURE 1. SIMPLE FOLLOWER

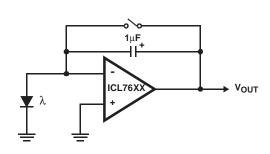

NOTE: Low leakage currents allow integration times up to several hours.

FIGURE 3. PHOTOCURRENT INTEGRATOR

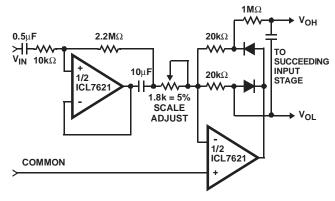

FIGURE 5. AVERAGING AC TO DC CONVERTER FOR A/D CONVERTERS SUCH AS ICL7106, ICL7107, ICL7109, ICL7116, ICL7117

board cleanliness, and supply filtering to avoid hum and noise pickup.

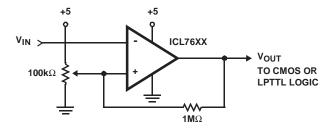

FIGURE 2. LEVEL DETECTOR

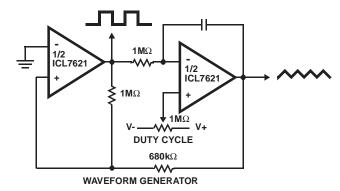

NOTE: Since the output range swings exactly from rail to rail, frequency and duty cycle are virtually independent of power supply variations.

FIGURE 4. TRIANGLE/SQUARE WAVE GENERATOR

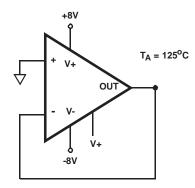

FIGURE 6. BURN-IN AND LIFE TEST CIRCUIT

#### NOTES:

- 4. Small capacitors (25 50pF) may be needed for stability in some cases.

- 5. The low bias currents permit high resistance and low capacitance values to be used to achieve low frequency cutoff.  $f_C = 10$ Hz,  $AV_{CL} = 4$ , Passband ripple = 0.1dB.

FIGURE 7. FIFTH ORDER CHEBYCHEV MULTIPLE FEEDBACK LOW PASS FILTER

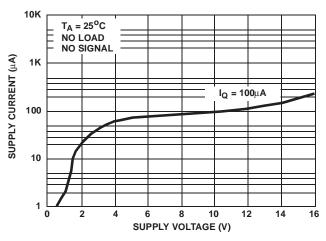

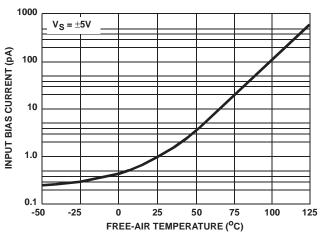

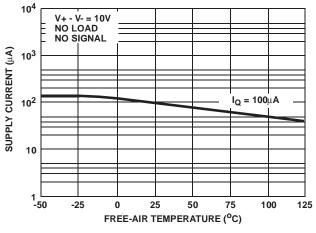

## **Typical Performance Curves**

FIGURE 8. SUPPLY CURRENT PER AMPLIFIER vs SUPPLY VOLTAGE

FIGURE 10. INPUT BIAS CURRENT vs TEMPERATURE

FIGURE 9. SUPPLY CURRENT PER AMPLIFIER vs FREE-AIR TEMPERATURE

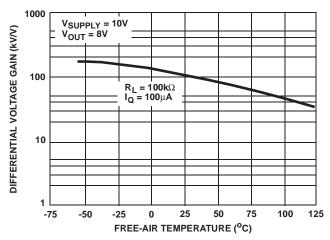

FIGURE 11. LARGE SIGNAL DIFFERENTIAL VOLTAGE GAIN VS FREE-AIR TEMPERATURE

# Typical Performance Curves (Continued)

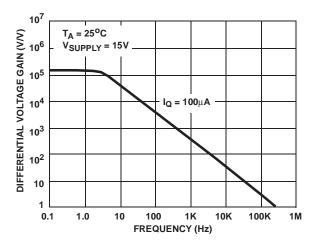

FIGURE 12. LARGE SIGNAL FREQUENCY RESPONSE

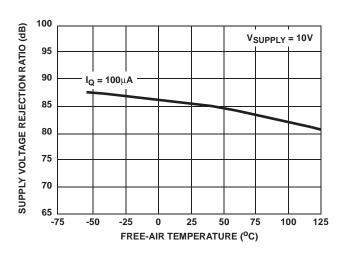

FIGURE 14. POWER SUPPLY REJECTION RATIO vs FREE-AIR TEMPERATURE

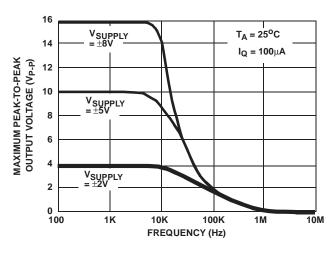

FIGURE 16. OUTPUT VOLTAGE vs FREQUENCY

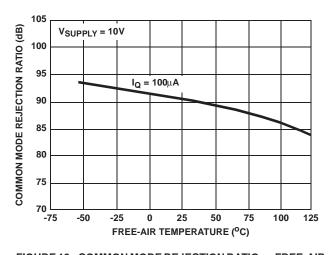

FIGURE 13. COMMON MODE REJECTION RATIO vs FREE-AIR TEMPERATURE

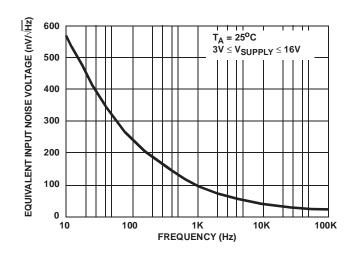

FIGURE 15. EQUIVALENT INPUT NOISE VOLTAGE vs FREQUENCY

FIGURE 17. OUTPUT SINK CURRENT vs SUPPLY VOLTAGE

## Typical Performance Curves (Continued)

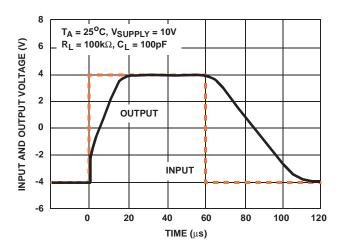

FIGURE 18. VOLTAGE FOLLOWER LARGE SIGNAL PULSE RESPONSE ( $I_Q = 100 \mu A$ )

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at website <a href="https://www.intersil.com/design/quality/iso.asp">www.intersil.com/design/quality/iso.asp</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

NORTH AMERICA Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

ASIA Intersil Ltd. 8F-2, 96, Sec. 1, Chien-kuo North, Taipei, Taiwan 104 Republic of China TEL: 886-2-2515-8508 FAX: 886-2-2515-8369