# **High Performance Communication Buffer**

### **General Description**

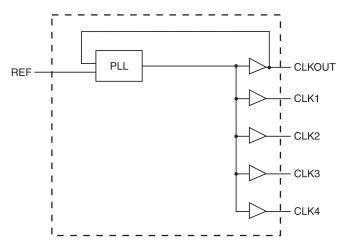

The **ICS91305I** is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the REF input with the CLKOUT signal. It is designed to distribute high speed clocks in communication systems operating at speeds from 25 to 133 MHz.

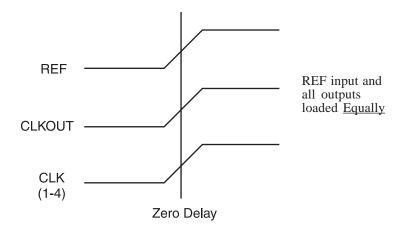

**ICS91305I** is a zero delay buffer that provides synchronization between the input and output. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than +/- 350 pS, the part acts as a zero delay buffer.

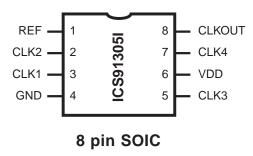

The **ICS91305I** comes in an eight pin 150 mil SOIC package. It has five output clocks. In the absence of REF input, will be in the power down mode. In this mode, the PLL is turned off and the output buffers are pulled low. Power down mode provides the lowest power consumption for a standby condition.

### **Features**

- Zero input output delay

- Frequency range 25 133 MHz (3.3V)

- 5V tolerant input REF

- High loop filter bandwidth ideal for Spread Spectrum applications.

- Less than 200 ps Jitter between outputs

- Skew controlled outputs

- Skew less than 250 ps between outputs

- Available in 8 pin 150 mil SOIC package

- $3.3V \pm 10\%$  operation

- Supports industrial temperature range -40°C to 85°C

## **Block Diagram**

## **Pin Configuration**

# **Pin Descriptions**

| PIN NUMBER | PIN NAME            | TYPE | DESCRIPTION                                          |

|------------|---------------------|------|------------------------------------------------------|

| 1          | REF <sup>2</sup>    | IN   | Input reference frequency, 5V tolerant input.        |

| 2          | CLK2 <sup>3</sup>   | OUT  | Buffered clock output                                |

| 3          | CLK1 <sup>3</sup>   | OUT  | Buffered clock output                                |

| 4          | GND                 | PWR  | Ground                                               |

| 5          | CLK3 <sup>3</sup>   | OUT  | Buffered clock output                                |

| 6          | VDD                 | PWR  | Power Supply (3.3V)                                  |

| 7          | CLK4 <sup>3</sup>   | OUT  | Buffered clock output                                |

| 8          | CLKOUT <sup>3</sup> | OUT  | Buffered clock output. Internal feedback on this pin |

#### Notes:

- 1. Guaranteed by design and characterization. Not subject to 100% test.

- 2. Weak pull-down

- 3. Weak pull-down on all outputs

## **Absolute Maximum Ratings**

Supply Voltage ...... 7.0 V

Logic Inputs . . . . . . . . . . . . GND –0.5 V to  $V_{DD}$  +0.5 V

Ambient Operating Temperature . . . .  $-40^{\circ}$ C to  $+85^{\circ}$ C Storage Temperature . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Electrical Characteristics at 3.3V**

$V_{DD} = 3.0 - 3.6 \text{ V}$ ,  $T_A = 0 - 70^{\circ} \text{ C}$  unless otherwise stated

| DC Characteristics               |                      |                                                            |     |      |       |       |

|----------------------------------|----------------------|------------------------------------------------------------|-----|------|-------|-------|

| PARAMETER                        | SYMBOL               | TEST CONDITIONS MIN                                        |     | TYP  | MAX   | UNITS |

| Input Low Voltage                | $V_{_{\rm I\!L}}$    |                                                            |     |      | 0.8   | V     |

| Input High Voltage               | $V_{_{\mathrm{IH}}}$ |                                                            | 2.0 |      |       | V     |

| Input Low Current                | $I_{_{\rm I\!L}}$    | $V_{IN}=0V$                                                |     | 19   | 100.0 | μΑ    |

| Input High Current               | $I_{_{\mathrm{IH}}}$ | $V_{IN} = V_{DD}$                                          |     | 0.10 | 250.0 | μΑ    |

| Output Low Voltage <sup>1</sup>  | $V_{OL}$             | $I_{OL} = 8mA$                                             |     | 0.25 | 0.4   | V     |

| Output High Voltage <sup>1</sup> | $V_{OH}$             | $I_{OH} = 8mA$                                             | 2.4 | 2.9  |       | V     |

| Power Down Supply<br>Current     | $I_{_{ m DD}}$       | REF = 0 MHz                                                |     | 0.3  | 100.0 | μΑ    |

| Supply Current                   | $I_{_{ m DD}}$       | Unloaded oututs at 66.66 MHz SEL inputs at $V_{DD}$ or GND |     | 30.0 | 80.0  | mA    |

#### Notes:

- 1. Guaranteed by design and characterization. Not subject to 100% test.

- 2. All Skew specifications are mesured with a  $50\Omega$  transmission line, load terminated with  $50\Omega$  to 1.4V.

- 3. Duty cycle measured at 1.4V.

- 4. Skew measured at 1.4V on rising edges. Loading must be equal on outputs.

# **Switching Characteristics**

| PARAMETER                                                          | SYMBOL    | CONDITION                                             | MIN           | TYP | MAX         | UNITS       |

|--------------------------------------------------------------------|-----------|-------------------------------------------------------|---------------|-----|-------------|-------------|

| Output period                                                      | t1        | With CL=30pF 40.00 (25)                               |               |     | 10<br>(133) | ns<br>(MHz) |

| Input period                                                       | t1        | With CL=30pF                                          | 40.00<br>(25) |     | 10<br>(133) | ns<br>(MHz) |

| Duty Cycle <sup>1</sup>                                            | Dt1       | Measured at 1.4V; CL=30pF                             | 40.0          | 50  | 60          | %           |

| Duty Cycle <sup>1</sup>                                            | Dt2       | Measured at VDD/2 Fout <66.6MHz                       | 45            | 50  | 55          | %           |

| Rise Time <sup>1</sup>                                             | tr1       | Measured between 0.8V and 2.0V:<br>CL=30pF            |               | 1.2 | 1.5         | ns          |

| Fall Time <sup>1</sup>                                             | tf1       | Measured between 2.0V and 0.8V;<br>CL=30pF            |               | 1.2 | 1.5         | ns          |

| Delay, REF Rising<br>Edge to CLKOUT<br>Rising Edge <sup>1, 2</sup> | Dr1       | Measured at 1.4V                                      |               | 0   | ±400        | ps          |

| Output to Output<br>Skew <sup>1</sup>                              | Tskew     | All outputs equally loaded, CL=20pF                   |               |     | 300         | ps          |

| Device to Device<br>Skew <sup>1</sup>                              | Tdsk-Tdsk | Measured at VDD/2 on the CLKOUT pins of devices       |               | 0   | 700         | ps          |

| Cycle to Cycle Jitter <sup>1</sup>                                 | Тсус-Тсус | Measured at 66.66 MHz, loaded outputs                 |               |     | 300         | ps          |

| PLL Lock Time <sup>1</sup>                                         | tLOCK     | Stable power supply, valid clock presented on REF pin |               |     | 2.0         | ms          |

| Jitter; Absolute Jitter <sup>1</sup>                               | Tjabs     | @ 10,000 cycles<br>CL=30pF                            | -200          | 70  | 200         | ps          |

| Jitter; 1 - Sigma <sup>1</sup>                                     | Tj1s      | @ 10,000 cycles<br>CL=30pF                            |               | 14  | 60          | ps          |

### Notes:

- 1. Guaranteed by design and characterization. Not subject to 100% test.

- 2. REF input has a threshold voltage of 1.4V

- 3. All parameters expected with loaded outputs

## **Output to Output Skew**

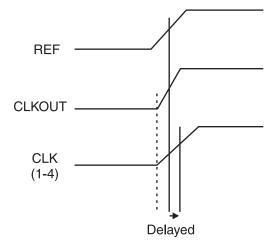

The skew between CLKOUT and the CLK(1-4) outputs is not dynamically adjusted by the PLL. Since CLKOUT is one of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded, zero phase difference will maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must equally loaded.

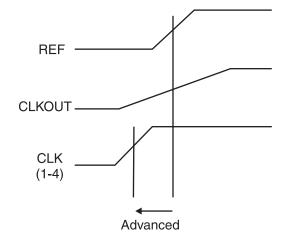

If the CLK(1-4) outputs are less loaded than CLKOUT, CLK(1-4) outputs will lead it; and if the CLK(1-4) is more loaded than CLKOUT, CLK(1-4) will lag the CLKOUT.

Since the CLKOUT and the CLK(1-4) outputs are identical, they all start at the same time, but different loads cause them to have different rise times and different times crossing the measurement thresholds.

REF input and CLK(1-4) outputs loaded equally, with CLKOUT loaded More.

REF input and CLK(1\_4) outputs loaded equally, with CLKOUT loaded <u>Less.</u>

Timing diagrams with different loading configurations

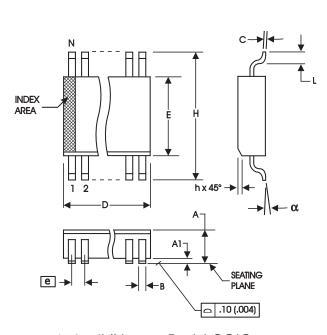

150 mil (Narrow Body) SOIC

| SYMBOL | In Millimeters    |         | In Inches         |       |  |

|--------|-------------------|---------|-------------------|-------|--|

|        | COMMON DIMENSIONS |         | COMMON DIMENSIONS |       |  |

|        | MIN               | MAX     | MIN               | MAX   |  |

| Α      | 1.35              | 1.75    | .0532             | .0688 |  |

| A1     | 0.10              | 0.25    | .0040             | .0098 |  |

| В      | 0.33              | 0.51    | .013              | .020  |  |

| С      | 0.19              | 0.25    | .0075             | .0098 |  |

| D      | SEE VAR           | IATIONS | SEE VARIATIONS    |       |  |

| Е      | 3.80              | 4.0     | .1497             | .1574 |  |

| е      | 1.27 E            | BASIC   | 0.050 BASIC       |       |  |

| Н      | 5.80              | 6.20    | .2284             | .2440 |  |

| h      | 0.25              | 0.50    | .010              | .020  |  |

| L      | 0.40              | 1.27    | .016              | .050  |  |

| N      | SEE VARIATIONS    |         | SEE VARIATIONS    |       |  |

| α      | 0°                | 8°      | 0°                | 8°    |  |

#### **VARIATIONS**

| N | Dm   | nm.  | D (inch) |       |  |

|---|------|------|----------|-------|--|

|   | MIN  | MAX  | MIN      | MAX   |  |

| 8 | 4.80 | 5.00 | .1890    | .1968 |  |

# **Ordering Information**

ICS91305IyM-T

ICS, AV = Standard Device