### **FEATURES**

- Data Retention in the absence of power

- Automatic data protection during power failure

- Data Retention over 10 years

- · Unlimited write cycles

- Conventional SRAM write cycles

- Low power CMOS

- Equal read/write cycle times

- +5Vonly read/write

- Operating voltage range <u>+</u>10%

- Direct replacement for 128K X 8 SRAM or EPROM

- Standard 32 pin DIP JEDEC Pinout

### **Functional Description**

The IM 1245Y–100 is a 1,048,576 bit, fully static NP RAM organized as 128K X 8 using CMOS and an internal lithium energy source.

This 'NO POWER' RAM has all the normal characteristics of a CMOS static RAM with an important benefit of data being retained in the absence of power. Data retention current is so small that a miniature lithium cell contained within the package provides an energy source to preserve data. Protection against data loss has also been incorporated to maintain data integrity during power on/off conditions.

The IM 1245Y–100 RAM can be directly used in place of existing static RAMs. There is no limit to the number of write cycles that can be executed and no additional support circuitry is required for interface to a microprocessor.

#### PIN CONFIGURATION

| NC   | 1  | 32 | Vcc  |

|------|----|----|------|

| A16  | 2  | 31 | A15  |

| A14  | 3  | 30 | NC   |

| A12  | 4  | 29 | WE   |

| Α7   | 5  | 28 | A13  |

| A6   | 6  | 27 | A8   |

| A5   | 7  | 26 | A9   |

| A4   | 8  | 25 | A11  |

| A3   | 9  | 24 | Œ    |

| A2   | 10 | 23 | A10  |

| A1   | 11 | 22 | CE   |

| A0   | 12 | 21 | 1/07 |

| I/O0 | 13 | 20 | 1/06 |

| I/O1 | 14 | 19 | 1/05 |

| 1/02 | 15 | 18 | 1/04 |

| Gnd  | 16 | 17 | I/O3 |

|      |    |    | ı    |

#### **PIN NAMES**

| NC          | No Connection     |

|-------------|-------------------|

| OE          | Output Enable     |

| Gnd         | Ground            |

| I/O0 – I/O7 | Data in/ Data Out |

| Vcc         | Power Supply +5V  |

| WE          | Write Enable      |

| A0 – A16    | Address Inputs    |

| CE          | Chip Enable       |

#### **READ MODE**

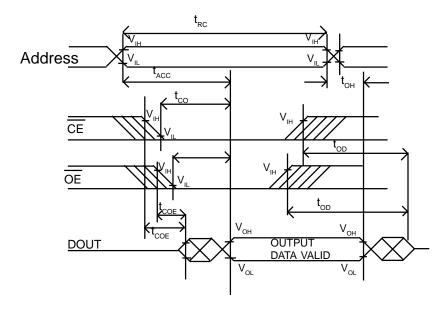

\_\_\_The IM 124 $\underline{5}\underline{Y}$ -100 performs a read cycle whenever WE high and CE low. The unique address specified by the 17 address inputs A0-A16 defines which of the 131,072 bytes of data is to be accessed. Valid data will be available to the eight data output drivers within access time  $t_{ACC}$  after the last address input is stable, provided that CE and  $\overline{OE}$  access times are satisfied. If  $\overline{OE}$  or  $\overline{CE}$  access times are not satisfied, data access will be measured from the limiting parameter ( $t_{CO}$  or  $t_{OE}$ ), rather than address. The state of the eight data I/O lines is controlled by the  $\overline{OE}$  and  $\overline{CE}$  control signals. The data lines may be in an indeterminate state between  $t_{OH}$  and  $t_{AA}$  but the data lines will always have valid data at  $t_{AA}$

### **WRITE MODE**

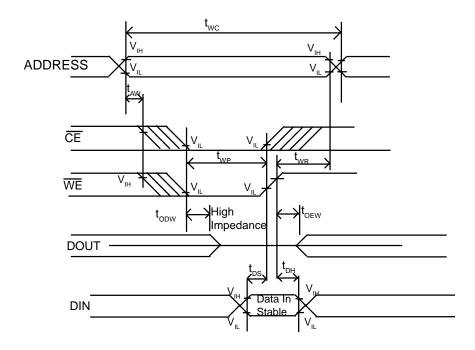

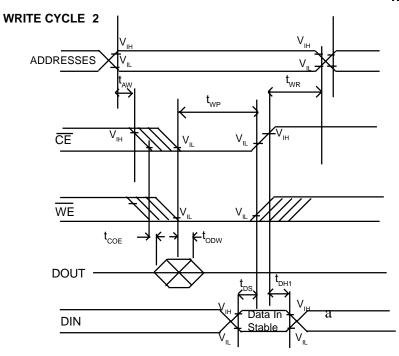

The  $\underline{\text{IM}}$  1245Y-100 is in the write mode whenever  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  inputs are held low. The latter occurring falling edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  determines the start of a write cycle. A write is terminated by the earlier rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ . The address must be held valid throughout the write cycle. WE must return to the high state for a minimum recovery time ( $t_{\text{WR}}$ ) before another Read or Write cycle can be initiated. CE or  $\overline{\text{WE}}$  is high during power on to perfect memory after Vcc reaches Vcc (min) but before the processor stabilizes

### **DATA RETENTION**

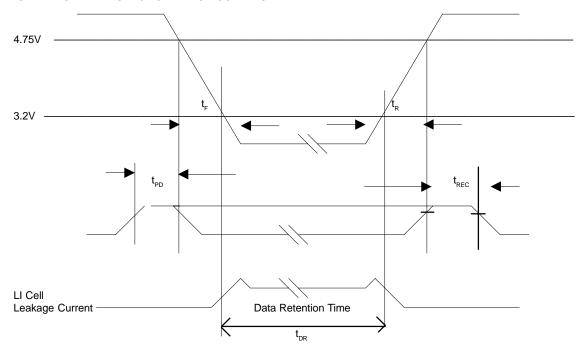

The IM 1245Y-100 provides full functional capability for Vcc greater than 4.5V and write protects at 4.25V. Data is retained in the absence of Vcc without any additional support circuitry. The SRAM constantly monitors Vcc. The moment Vcc decays, the RAM automatically write protects itself. All inputs to the RAM become "don't care" and all outputs are in high impedance-state. As Vcc falls below approximately 3.0V the power switching circuit connects the lithium energy source to RAM to retain data. During power-on, when Vcc rises above approximately 3.0V the power switching circuit connects external Vcc to the RAM and disconnects the lithium energy source. Normal RAM operation can resume after Vcc becomes greater than 4.5V.

### **Maximum Ratings**

Operating Temperature....0°C to 70°C

Storage Temperature.....0°C to 70°C

Soldering Temperature

And Time............260°C for 10 sec

Supply Voltage...........0V to 7.0V

Input Voltage...........-0.5V to 7.0V

Input/ Output Voltage......-0.5V to Vcc + 0.3V

Power Dissipation.....1.0W

### Recommended D.C. Operating Conditions

| Parameter      | Symbol          | Min. | Тур | Max.        | Unit |

|----------------|-----------------|------|-----|-------------|------|

| Supply Voltage | Vcc             | 4.5  | 5.0 | 5.5         | V    |

|                | Gnd             | 0    | •   | 0           | V    |

| Input Voltage  | V <sub>IH</sub> | 2.2  | 3.5 | Vcc<br>+0.3 | V    |

|                | $V_{IL}$        | 0    | ı   | 0.8         | V    |

#### FRESHNESS SEAL AND SHIPPING

The IM1245Y - 100 is shipped from INNOVATIVE MICROTECHONOLOGY INC. with the lithium energy source disconnected, guaranteeing full energy capacity. When Vcc is first applied at a level of greater than 4.5 volts, the lithium energy source is enabled for battery back-up operation.

### **Electrical Characeteristics**

| Parameter                                                                                                         | Description                                                                                                                                                    | Test conditons                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min.                                   | Тур                              | Max                                                 | Unit                                  |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|-----------------------------------------------------|---------------------------------------|

| I <sub>LI</sub> I <sub>OCA</sub> I <sub>VCC</sub> I <sub>LO</sub> V <sub>OH</sub> V <sub>OL</sub> V <sub>TP</sub> | Input Leakage Average operating Current Operating Supply current Output Leakage Vi High level output voltage Low level output voltage Write protection voltage | $ \frac{\text{Vi} = 0 \text{ to Vcc}}{\text{CE}} = \text{V}_{\text{IH}}, \text{I}_{\text{IO}} = \text{0mA} $ $ \frac{\text{CE}}{\text{CE}} = \text{V}_{\text{IL}}, \text{I}_{\text{IO}} = \text{0mA} $ $ \frac{\text{CE}}{\text{CE}} = \text{V}_{\text{IL}}, \text{I}_{\text{IO}} = \text{0mA} $ $ \text{CE} = \text{V}_{\text{IH}} \text{ or Vcc} $ $ \text{(o = Gnd to Vcc)} $ $ \text{I}_{\text{OH}} = \text{-} 1.0 \text{ mA} $ $ \text{I}_{\text{OL}} = 2.1 \text{ mA} $ | -1<br>-<br>-<br>-1<br>2.4<br>-<br>4.25 | -<br>45<br>1<br>-<br>0.2<br>4.37 | 1<br>80<br>3<br>50<br>1<br>Vcc - 0.1<br>0.4<br>4.49 | μΑ<br>μΑ<br>mA<br>mA<br>μΑ<br>1V<br>V |

# Capacitance

| Parameter                                              | Description                                           | Test conditons                             | Min. | Тур         | Max         | Unit           |

|--------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|------|-------------|-------------|----------------|

| C <sub>ADD</sub><br>C <sub>I</sub><br>C <sub>I/O</sub> | Address capacitance Input capacitance I/O capacitance | $V_{ADD} = 0V$<br>Vi = 0V<br>$V_{IO} = 0V$ | -    | 3<br>5<br>6 | 5<br>6<br>7 | pF<br>pF<br>pF |

# Switching Characteristics over the operating range

| Parameter                                                                                                                         | Description                                                                                                                                                          | Min                                  | Max                                 | Unit                       |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|----------------------------|

| t <sub>RC</sub> t <sub>ACC</sub> tOE tCO t <sub>COE</sub> tOD t                                                                   | Read cycle time Address access time Output enable access time E to output valid OE or CE to output valid Output High Z from Deselection Output hold from adds change | 100<br>-<br>-<br>5<br>-<br>5         | -<br>100<br>50<br>100<br>-<br>35    | ns<br>ns<br>ns<br>ns<br>ns |

| t <sub>WC</sub> t <sub>AW</sub> t <sub>WP</sub> t <sub>WR</sub> t <sub>ODW</sub> t <sub>OEW</sub> t <sub>DS</sub> t <sub>DH</sub> | Write cycle time Address setup time Write pulse-width Write recovery time Output High Z from WE Output Active from WE Input data setup time Input data hold time     | 100<br>0<br>75<br>5<br>5<br>40<br>15 | -<br>-<br>-<br>35 ns<br>-<br>-<br>- | ns<br>ns<br>ns<br>ns<br>ns |

## **READ CYCLE**

## **WRITE CYCLE 1**

FIG. D POWER - DOWN/ POWER -ON CONDITION

#### Notes:

- 1. WE is to be high during read cycle.

- During write cycle that is controlled by CE, output buffer is in high impedance state irrespective of whether OE is high or low level.

- 3. During write cycle that is controlled by WE, output buffer is in high impedance state if OE is high.

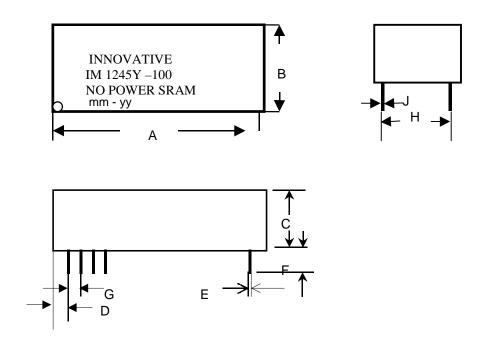

| DIM IN INCHES | MIN.  | MAX.  |

|---------------|-------|-------|

| Α             | 1.72  | 1.74  |

| В             | 0.72  | 0.74  |

| С             | 0.395 | 0.415 |

| D             | 0.09  | 0.12  |

| E             | 0.015 | 0.021 |

| F             | 0.12  | 0.16  |

| G             | 0.09  | 0.11  |

| H             | 0.59  | 0.63  |

| J             | 0.008 | 0.012 |