ICS8430-01 HIGH FREQUENCY SYNTHESIZER

### GENERAL DESCRIPTION

The ICS8430-01 is a general purpose, dual output high frequency synthesizer and a member of the HiPerClockS™ family of High Performance Clocks Solutions from ICS. The VCO operates at a frequency range of 280MHz to

400MHz. The output frequency can be programmed using the serial or parallel interfaces to the configuration logic. With the output configured to divide the VCO frequency by 2 output frequency steps as small as 0.5MHz can be achieved using a 16MHz crystal or reference clock.

### **F**EATURES

- · Fully integrated PLL

- · Dual differential 3.3V LVPECL output

- 23MHz to 400MHz output frequency

- ±25ps peak-to-peak output jitter

- Parallel interface for programming counter and output dividers during power-up

- Serial 3 wire interface

- Selectable crystal oscillator interface and LVCMOS reference input

- · LVCMOS control inputs

- 3.3V supply voltage

- 32 lead low-profile QFP(LQFP), 7mm x 7mm x 1.4mm package body, 0.8mm package lead pitch

- 0°C to 70°C ambient operating temperature

### **BLOCK DIAGRAM**

### VCO\_SEL XTAL SEL REF IN osc XTAL2 ÷ 16 **PLL** PHASE DETECTOR VCO FOUT0 nFOUT0 ÷ M FOUT1 nFOUT1 S LOAD CONFIGURATION S\_DATA **INTERFACE** -TEST S\_CLOCK LOGIC nP\_LOAD M0.W8 NU-N2

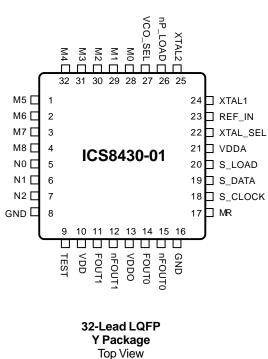

# PIN ASSIGNMENT

The Advance Information presented herein represents a product currently in design or being considered for design. The noted characteristics are design targets. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

ICS8430-01

HIGH FREQUENCY

SYNTHESIZER

#### FUNCTIONAL DESCRIPTION

The ICS8430-01 features a fully integrated PLL and therefore requires no external component for setting the loop bandwidth. A series-resonant, fundamental crystal is used as the input to the on-chip oscillator. The output of the oscillator is divided by 16 prior to the phase detector. With a 16MHz crystal this provides a 1MHz reference frequency. The VCO of the PLL operates over a range of 280MHz to 400MHz. The output of the loop divider is also applied to the phase detector.

The phase detector and the loop filter force the VCO output frequency to be M times the reference frequency by adjusting the VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve lock. The output of the VCO is scaled by a divider prior to being sent to each of the LVPECL output buffers. The divider provides a 50% output duty cycle.

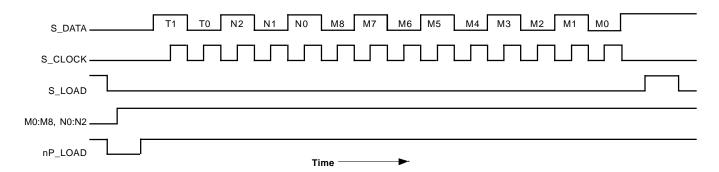

The programmable features of the ICS8430-01 support two input modes and programmable PLL loop divider and output divider. The two input operational modes are parallel and serial. Figure 1 shows the timing diagram for each mode. In parallel mode the nP\_LOAD input is initially LOW. The data on inputs M0 through M8 and N0 through N2 is passed directly to the ripple counter. On the LOW-to-HIGH transition of the nP\_LOAD input the data is latched and the ripple counter remains loaded until the next LOW transition on nP\_LOAD or until a serial event occurs. As a result the M and N bits can be hardwired to set the ripple counter to a specific default state that will automatically occur during power-up. The TEST output is LOW when operating in the parallel input mode. The relationship between the VCO frequency, the crystal frequency and the loop divider is defined as follows:

$$fVCO = \frac{fxtal}{16} \times M$$

The M count and the required values of M0 through M8 are shown in Table4B, Programmable VCO Frequency Function Table. The frequency out is defined as follows:

fout =

$$\frac{\text{fVCO}}{\text{N}} = \frac{\text{fxtal}}{16} \times \frac{\text{M}}{\text{N}}$$

Serial operation occurs when nP\_LOAD is HIGH and S\_LOAD is LOW. The shift register is loaded by sampling the S\_DATA bits with the rising edge of S\_CLOCK. The contents of the shift register are loaded into the ripple counter when S\_LOAD transitions from LOW-to-HIGH. The ripple counter divide values are latched on the HIGH-to-LOW transition of S\_LOAD. If S\_LOAD is held HIGH data at the S\_DATA input is passed directly to the ripple counter on each rising edge of S\_CLOCK. The serial mode can be used to program the M and N bits and test bits T1 and T0. The internal registers T0 and T1 determine the state of the TEST output as follows:

| <u>T1</u> | <u>T0</u> | TEST Output                  |

|-----------|-----------|------------------------------|

| 0         | 0         | LOW                          |

| 0         | 1         | S_Data clocked into register |

| 1         | 0         | Output of M divider          |

| 1         | 1         | CMOS Fout                    |

FIGURE 1. PARALLEL & SERIAL LOAD OPERATIONS

# ICS8430-01 High Frequency Synthesizer

#### TABLE 1. PIN DESCRIPTIONS

| Number                     | Name                         | Ту     | ре       | Description                                                                                                                                                       |

|----------------------------|------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28, 29, 30<br>31, 32, 1, 2 | M0, M1, M2<br>M3, M4, M5, M6 | Input  | Pulldown | M counter/divider inputs. Data latched on LOW-to-HIGH transistion of                                                                                              |

| 3, 4                       | M7, M8                       | Input  | Pullup   | nP_LOAD input. LVCMOS / LVTTL interface levels.                                                                                                                   |

| 5, 7                       | N0, N2                       | Input  | Pulldown | Determines output divider value as defined in Table 3 Function Table. LVCMOS                                                                                      |

| 6                          | N1                           | Input  | Pullup   | / LVTTL interface levels.                                                                                                                                         |

| 8, 16                      | GND                          | Power  |          | Power supply ground pin. Connect to ground.                                                                                                                       |

| 9                          | TEST                         | Output |          | Test output which is ACTIVE in the serial mode of operation. Output driven LOW in parallel mode. LVCMOS interface levels.                                         |

| 10                         | VDD                          | Power  |          | Core power supply pin.                                                                                                                                            |

| 11, 12                     | FOUT1, nFOUT1                | Output |          | Differential output for the synthesizer. 3.3V LVPECL interface levels.                                                                                            |

| 13                         | VDDO                         | Power  |          | Output power supply connection. Connect to 3.3V.                                                                                                                  |

| 14, 15                     | FOUT0, nFOUT0                | Output |          | Differential output for the synthesizer. 3.3V LVPECL interface levels.                                                                                            |

| 17                         | MR                           | Input  | Pulldown | Resets the reference frequency and output dividers. Loads data present at the M bits into counter. LVCMOS / LVTTL interface levels.                               |

| 18                         | S_CLOCK                      | Input  | Pulldown | Clocks in serial data present at S_DATA input into the shift register on the rising edge of S_CLK.                                                                |

| 19                         | S_DATA                       | Input  | Pulldown | Shift register serial input. Data sampled on the rising edge of S_CLK.                                                                                            |

| 20                         | S_LOAD                       | Input  | Pulldown | Controls transition of data from shift register into the ripple counter. LVCMOS / LVTTL interface levels.                                                         |

| 21                         | VDDA                         | Power  |          | Analog power supply pin. Connect to 3.3V.                                                                                                                         |

| 22                         | XTAL_SEL                     | Input  | Pullup   | Selects between crystal or reference inputs as the PLL reference source. LVCMOS / LVTTL interface levels. Selects XTAL inputs when HIGH. Selects REF_IN when LOW. |

| 23                         | REF_IN                       | Input  | Pulldown | Reference clock input. LVCMOS / LVTTL interface levels.                                                                                                           |

| 24, 25                     | XTAL1, XTAL2                 | Input  |          | Crystal oscillator inputs.                                                                                                                                        |

| 26                         | nP_LOAD                      | Input  | Pulldown | Parallel load input. Determines when data present at M8:M0 is loaded into ripple counter. LVCMOS / LVTTL interface levels.                                        |

| 27                         | VCO_SEL                      | Input  | Pullup   | Determines whether synthesizer is in PLL or bypass mode. LVCMOS / LVTTL interface levels.                                                                         |

### TABLE 2. PIN CHARACTERISTICS

| Symbol    | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------|-------------------------|-----------------|---------|---------|---------|-------|

| CIN       | Input Capacitance       |                 |         |         |         | pF    |

| RPULLUP   | Input Pullup Resistor   |                 |         | 51      |         | ΚΩ    |

| RPULLDOWN | Input Pulldown Resistor |                 |         | 51      |         | ΚΩ    |

### TABLE 3. CRYSTAL CHARACTERISTICS

| Parameter                          | Test Conditions     | Min | Тур | Max | Units |

|------------------------------------|---------------------|-----|-----|-----|-------|

| Crystal Cut                        | Mode of Oscillation |     |     |     |       |

| Frequency Tolerance                |                     |     |     |     | ppm   |

| Frequency Stability                |                     |     |     |     | ppm   |

| Drive Level                        |                     |     |     |     | μW    |

| Equivalent Series Resistance (ESR) |                     |     |     |     | Ω     |

| Shunt Capacitiance                 |                     |     |     |     | pF    |

| Series Pin Inductance              |                     |     |     |     | nH    |

| Aging                              |                     |     |     |     | ppm   |

ICS8430-01 HIGH FREQUENCY SYNTHESIZER

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage 4.6V

Inputs -0.5V to VDD+0.5 V

Outputs -0.5V to VDD+0.5V

Ambient Operating Temperature 0°C to 70°C

Storage Temperature -65°C to 150°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any conditions beyond those listed in the *DC Electrical Characteristics* or *AC Electrical Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

TABLE 4A. PARALLEL AND SERIAL MODES FUNCTION TABLE

|    |         |      | IN   | PUTS         |          |        |                                                                                                                   |

|----|---------|------|------|--------------|----------|--------|-------------------------------------------------------------------------------------------------------------------|

| MR | nP_LOAD | M    | N    | S_LOAD       | S_CLOCK  | S_DATA | Conditions                                                                                                        |

| Н  | Х       | Х    | Х    | Х            | Х        | Х      | Reset. M and N counters reset.                                                                                    |

| L  | L       | Data | Data | Х            | Х        | Х      | Data on M and N inputs passed directly to ripple counter. TEST output forced LOW.                                 |

| L  | 1       | Data | Data | Х            | Х        | X      | Data is latched into input registers and remains loaded until next LOW transition or until a serial event occurs. |

| L  | Н       | Х    | Х    | L            | <b>↑</b> | Data   | Serial input mode. Shift register is loaded with data on S_DATA on each rising edge of S_CLOCKt                   |

| L  | Н       | Х    | Х    | <b>↑</b>     | L        | Data   | Contents of the shift register are passed to the ripple counter.                                                  |

| L  | Н       | Х    | Х    | $\downarrow$ | L        | Data   | Ripple counter divide values are latched.                                                                         |

| L  | Н       | Х    | Х    | L            | Х        | Х      | Parallel or serial input do not affect shift registers.                                                           |

TABLE 4B. PROGRAMMABLE VCO FREQUENCY FUNCTION TABLE

| VCO Frequency | M O     | 256 | 128 | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

|---------------|---------|-----|-----|----|----|----|----|----|----|----|

| (MHz)         | M Count | M8  | M7  | М6 | M5 | M4 | М3 | M2 | M1 | MO |

| 250           | 250     | 0   | 1   | 1  | 1  | 1  | 1  | 0  | 1  | 0  |

| 251           | 251     | 0   | 1   | 1  | 1  | 1  | 1  | 0  | 1  | 1  |

| 252           | 252     | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 0  |

| 253           | 253     | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| •             | •       | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| •             | •       | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| 498           | 498     | 1   | 1   | 1  | 1  | 1  | 0  | 0  | 1  | 0  |

| 499           | 499     | 1   | 1   | 1  | 1  | 1  | 0  | 0  | 1  | 1  |

| 500           | 500     | 1   | 1   | 1  | 1  | 1  | 0  | 1  | 0  | 0  |

TABLE 4C. PROGRAMMABLE OUTPUT DIVIDER FUNCTION TABLE

|    | Input |    | N Divider | Output Frequency<br>(MHz) |        |  |

|----|-------|----|-----------|---------------------------|--------|--|

| N2 | N1    | N0 | Value     | Min                       | Max    |  |

| 0  | 0     | 0  | 1         | 280                       | 400    |  |

| 0  | 0     | 1  | 1.5       | 186.66                    | 266.66 |  |

| 0  | 1     | 0  | 2         | 140                       | 200    |  |

| 0  | 1     | 1  | 3         | 93.33                     | 133.33 |  |

| 1  | 0     | 0  | 4         | 70                        | 100    |  |

| 1  | 0     | 1  | 6         | 46.66                     | 66.66  |  |

| 1  | 1     | 0  | 8         | 35                        | 50     |  |

| 1  | 1     | 1  | 12        | 23.33                     | 33.33  |  |

# ICS8430-01 High Frequency Synthesizer

Table 5. DC Electrical Characteristics, VDD = VDDA = VDDO = 3.3V±5%, TA = 0°C TO 70°C

| Symbol                |                                | Parameter                                                        | Test Conditions         | Minimum | Typical | Maximum | Units |

|-----------------------|--------------------------------|------------------------------------------------------------------|-------------------------|---------|---------|---------|-------|

| VDD,<br>VDDA,<br>VDDO | Power Supply Voltage           |                                                                  |                         | 3.135   | 3.3     | 3.465   | V     |

| IDD                   | Quiescent Powe                 | r Supply Current                                                 | VDDx = 3.465V           |         |         | 110     | mA    |

|                       |                                | All except REF_IN, XTAL1, XTAL2                                  | 3.135 ≤ VDDx ≤ 3.465V   | 2       |         | 3.765   | V     |

| VIH                   | Input High<br>Voltage          | REF_IN                                                           | VDDx = 3.465V           | 1.8     |         | 3.8     | V     |

|                       | voltage                        | KEF_IIV                                                          | VDDx = 3.135V           | 1.7     |         | 3.4     | V     |

|                       | land I am                      | All except REF_IN, XTAL1, XTAL2                                  | 3.135 ≤ VDDx ≤ 3.465V   | -0.3    |         | 0.8     | V     |

| VIL                   | Input Low<br>Voltage           | DEE IN                                                           | VDDx = 3.465V           | -0.3    |         | 1.6     | V     |

|                       |                                | REF_IN                                                           | VDDx = 3.135V           | -0.3    |         | 1.5     | V     |

| IIH                   | Input High<br>Current          | M0-M6, N0, N2 MR, S_CLOCK,<br>S_DATA, S_LOAD, REF_IN,<br>nP_LOAD | VDDx = VIN = 3.465V     |         |         | 150     | μA    |

|                       |                                | M7, M8, N1, XTAL_SEL, VCO_SEL                                    | VDDx = VIN = 3.465V     |         |         | 5       | μΑ    |

| IIL                   | Input Low<br>Current           | M0-M6, N0, N2 MR, S_CLOCK,<br>S_DATA, S_LOAD, REF_IN,<br>nP_LOAD | VDDx = 3.465V, VIN = 0V | -150    |         |         | μA    |

|                       |                                | M7, M8, N1, XTAL_SEL, VCO_SEL                                    | VDDx = 3.465V, VIN = 0V | -5      |         |         | μA    |

|                       | Output High                    | FOUT0, nFOUT0, FOUT1, nFOUT1                                     | VDDx = 3.3V             | 2.1     |         |         | V     |

| VOH                   | Voltage;<br>NOTE 1, 2          | TEST                                                             | VDDx = 3.135            | 2.4     |         |         | V     |

| VOL                   | Output Low                     | FOUT0, nFOUT0, FOUT1, nFOUT1                                     | VDDx = 3.3V             |         |         | 1.6     | V     |

| VOL                   | Voltage;<br>NOTE 1, 2          | TEST                                                             | VDDx = 3.135            |         |         | 0.5     | V     |

| VPPO                  | Peak-to-Peak<br>Output Voltage | FOUT0, nFOUT0, FOUT1, nFOUT1                                     | 3.135 ≤ VDDx ≤ 3.465V   | 0.6     |         |         | V     |

NOTE 1: FOUT0, nFOUT1, nFOUT1 outputs terminated with  $50\Omega$  to VDDO-2V.

NOTE 2: These levels are specified for VDDO = 3.3V. Output levels will vary 1:1 with VDDO.

# ICS8430-01 HIGH FREQUENCY SYNTHESIZER

### Table 6. Input Frequency Characteristics, VDD = VDDA = VDDO = 3.3V±5%, TA = 0°C TO 70°C

| Symbol | Parameter                  |         | Test Conditions               | Minimum | Typical | Maximum | Units |

|--------|----------------------------|---------|-------------------------------|---------|---------|---------|-------|

|        |                            | REF     |                               | 10      |         | 25      | MHz   |

| fMAXIN | Maximum Input Frequency    | XTAL    |                               | 10      |         | 25      | MHz   |

|        |                            | S_CLOCK |                               |         |         | TBD     | MHz   |

| tR     | Input Rise Time            | REF     | Measured at 20% to 80% points |         |         | TBD     | ns    |

| tF     | Input Fall Time            | REF     | Measured at 20% to 80% point  |         |         | TBD     | ns    |

| tDC    | Input Reference Duty Cycle | REF     |                               | TBD     |         | TBD     | %     |

### Table 7. AC Characteristics, $VDD = VDDA = VDDO = 3.3V \pm 5\%$ , $TA = 0^{\circ}C$ to $70^{\circ}C$

| Symbol   | Parameter          |                                | Test Conditions               | Minimum | Typical | Maximum | Units |

|----------|--------------------|--------------------------------|-------------------------------|---------|---------|---------|-------|

| FMAX     | Maximum Output F   | requency                       | $3.135 \leq VDDx \leq 3.465V$ | 23      |         | 400     | MHz   |

| tjit(cc) | Peak Cycle-to-Cycl | e Jitter                       |                               |         |         | 50      | ps    |

| tsk(o)   | Output Skew        |                                |                               |         |         | TBD     | ps    |

| tDC      | Output Duty Cycle  |                                |                               | 47      |         | 53      | %     |

| tR       | Output Rise Time   | FOUT0, nFOUT0<br>FOUT1, nFOUT1 | 20% to 80%                    | 300     |         | 800     | ps    |

| tF       | Output Fall Time   | FOUT0, nFOUT0<br>FOUT1, nFOUT1 | 20% to 80%                    | 300     |         | 800     | ps    |

|          | Setup Time         | M, N to nP_LOAD                |                               | TBD     |         |         | ns    |

| tS       |                    | S_DATA to S_CLOCK              |                               | TBD     |         |         | ns    |

|          |                    | S_CLOCK to S_LOAD              |                               | TBD     |         |         | ns    |

|          |                    | M, N to nP_LOAD                |                               | TBD     |         |         | ns    |

| tH       | Hold Time          | S_DATA to S_CLOCK              |                               | TBD     |         |         | ns    |

|          |                    | S_CLOCK to S_LOAD              |                               | TBD     |         |         | ns    |

| tLOCK    | PLL Lock Time      |                                |                               |         |         | TBD     | ms    |

| tPW      | Pulse Width        | nP_LOAD                        |                               |         |         | TBD     | ns    |

| I L VV   | Fuise Width        | S_LOAD                         |                               |         |         | TBD     | ns    |

# ICS8430-01 HIGH FREQUENCY SYNTHESIZER

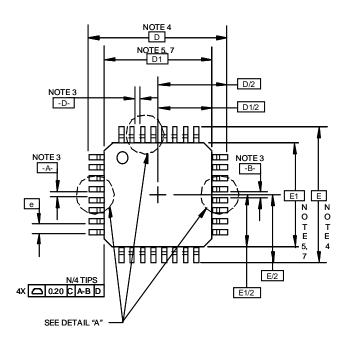

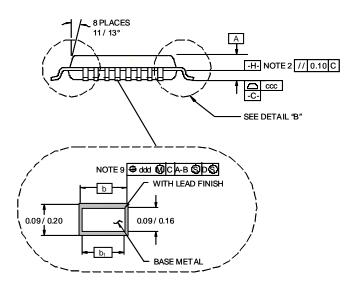

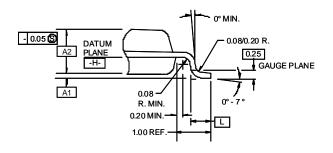

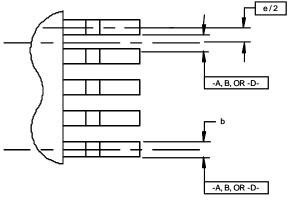

#### PACKAGE OUTLINE AND DIMENSIONS - Y SUFFIX

#### NOTES:

- 1. ALL DIMENSIONS AND TOLERANCING CONFORM TO ANSI Y14.5-1982

- DATUM PLANE -H- LOCATED AT MOLD PARTING

LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- DATUMS A-B AND -D- TO BE DETERMINED AT CENTERLINE BETWEEN LEADS WHERE LEADS EXIT PLASTIC AT DATUM PLANE -H-

- TO BE DETERMINED AT SEATING PLACE -C-

- DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION.

- "N" IS THE TOTAL NUMBER OF TERMINALS.

- THESE DIMENSIONS TO BE DETERMINED AT DATUM PLANE -H-.

PACKAGE TOP DIMENSIONS ARE SMALLER THAN

- BOTTOM DIMENSIONS AND TOP OF PACKAGE WILL NOT OVERHANG BOTTOM OF PACKAGE.

- DIMENSION & DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE b DIMENSION AT MAXIMUM MATERIAL CONDITION.

10. CONTROLLING DIMENSION: MILLIMETER.

- THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MS-026, VARIATION ABA.

- 12. A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE

| S<br>Y<br>M |      | EDEC VARIATIONS IN MIL |      | N<br>O |

|-------------|------|------------------------|------|--------|

| B<br>0      |      | BBA                    |      | T<br>E |

| L           | MIN  | NOM                    | MAX  |        |

| Α           |      |                        | 1.60 |        |

| A1          | 0.05 |                        | 0.15 | 12     |

| A2          | 1.35 | 1.4                    | 1.45 |        |

| D           |      | 9.00 BSC.              |      | 4      |

| D1          |      | 7.00 BSC.              |      | 7, 8   |

| E           |      | 9.00 BSC.              |      | 4      |

| E1          |      | 7.00 BSC.              |      | 7, 8   |

| L           | 0.45 | 0.60                   | 0.75 |        |

| N           |      | 32                     |      |        |

| е           |      | 0.80 BSC.              |      |        |

| b           | 0.30 | 0.37                   | 0.45 |        |

| b1          | 0.30 | 0.35                   | 0.40 | 9      |

| ссс         |      |                        | 0.10 |        |

| ddd         |      |                        | 0.20 |        |

# ICS8430-01 High Frequency Synthesizer

ORDERING INFORMATION

| Part/Order Number | Marking      | Package                       | Count | Temperature |

|-------------------|--------------|-------------------------------|-------|-------------|

| ICS8430AY-01      | ICS8430AY-01 | 32 Lead LQFP                  |       | 0°C to 70°C |

| ICS8430AY-01T     | ICS8430AY-01 | 32 Lead LQFP on Tape and Reel |       | 0°C to 70°C |