# Power Factor Controller + Cool-MOS: BoostSET IC for High Power Factor and low THD

- IC for sinusoidal line-current consumption

- Controller and CoolMOS within one package

- P-DSO-16-10

- Power factor achieves nearly 1

- Controls boost converter as active harmonic filter for low THD

- Start up with very low current consumption

- Zero current detector for discontinuous operation mode

- Output overvoltage protection

- Output undervoltage lockout

- Internal start up timer

- Totem pole output with active shut down

- Internal leading edge blanking LEB

- Very low comparator and multiplier offsets for universal input applications

- High sophisticated amplifier minimizes distortion inteferences caused by MOSFET switching

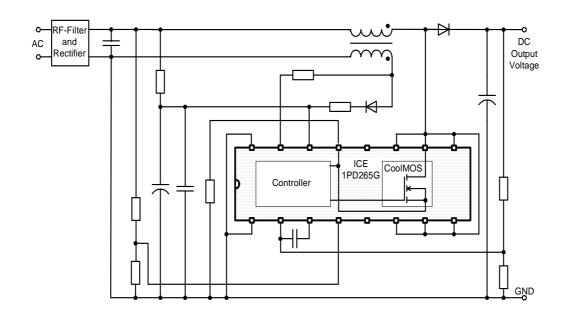

The ICE1PD265G IC controls a boost converter in a way that sinusoidal current is taken from the single phase line supply and stabilized DC voltage is available at the output. CoolMOS and controller are placed together in one package.

This active harmonic filter limits the harmonic currents resulting from the capacitor pulsed charge currents during rectification. The power factor which descibes the ratio between active and apparent power is almost one. Line voltage fluctuations can be compensated very efficiently

| Туре       | Ordering Code | Package     |  |

|------------|---------------|-------------|--|

| ICE1PD265G |               | P-DSO-16-10 |  |

| Infineon Tech | PCI Group | 10.09.01 | 1 |

|---------------|-----------|----------|---|

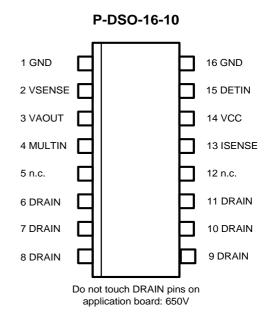

#### **Pin Connections**

| Pin | Symbol | Function                          |

|-----|--------|-----------------------------------|

| 1   | GND    | Ground                            |

| 2   | VSENSE | Voltage amplifier inverting input |

| 3   | VAOUT  | Voltage amplifier output          |

| 4   | MULTIN | Multiplier input                  |

| 5   | n.c.   |                                   |

| 6   | DRAIN  | 650V Drain                        |

| 7   | DRAIN  | 650V Drain                        |

| 8   | DRAIN  | 650V Drain                        |

| 9   | DRAIN  | 650V Drain                        |

| 10  | DRAIN  | 650V Drain                        |

| 11  | DRAIN  | 650V Drain                        |

| 12  | n.c.   |                                   |

| 13  | ISENSE | Current sense input + Source      |

| 14  | VCC    | Positive voltage supply           |

| 15  | DETIN  | Zero current detector input       |

| 16  | GND    | Ground                            |

|     |        |                                   |

## **Pin Description**

## Pin1,16 GND (Ground)

The GND pins are internally connected via the lead frame

## Pin 2 VSENSE (voltage amplifier inverting input)

VSENSE is connected via a resistive divider to the boost converter output. With a capacitor connected to VAOUT the internal error amplifier acts as an integrator.

### Pin 3 VAOUT (voltage amplifier output)

VAOUT is connected internally to the first multiplier input. To prevent overshoot the input voltage is clamped internally at 5V. Input voltage less then 2.2V shuts the gate driver down. If the current flowing into this pin is exceeding an internal threshold the multiplier output voltage is reduced to prevent the MOSFET from overvoltage damage.

#### Pin 4 MULTIN (multipier input)

MULTIN is the second multiplier input and is connected via a resistive divider to the rectifier output voltage.

#### Pin 5, 12

not connected

#### Pin 6,7,8,9,10,11 DRAIN (drain connection of internal CoolMOS)

The DRAIN pins are internally connected via the leadframe. Be aware of 650V input voltage!

|               | 4         |          |   |

|---------------|-----------|----------|---|

| Infineon Tech | PCI Group | 10.09.01 | 2 |

#### Pin 13 ISENSE (current sense input and CoolMOS source)

Controller current sense input and CoolMOS source are internally connected via bonds.

ISENSE should be connected to an external sense resistor controlling the CoolMOS source current. The input is internally clamped at -0.3V to prevent negative input voltage interaction. A leading edge blanking circuitry suppresses voltage spiks when turning the MOSFET on.

#### Pin 14 Vcc (Positive voltage supply)

If Vcc exceeds the turn-on threshold the IC is switched on. When Vcc falls below the turn-off threshold it is switched off and power consumption is very low. An auxilliary winding is charging a capacitor which provides the supply current. A second 100nF ceramic capacitor should be added to Vcc to absorbe supply current spikes required to charge the MOSFET gate capacitance.

### Pin 15 DETIN (Zero current detector input)

DETIN is connected to an auxiliary winding monitoring the zero crossing of the inductor current.

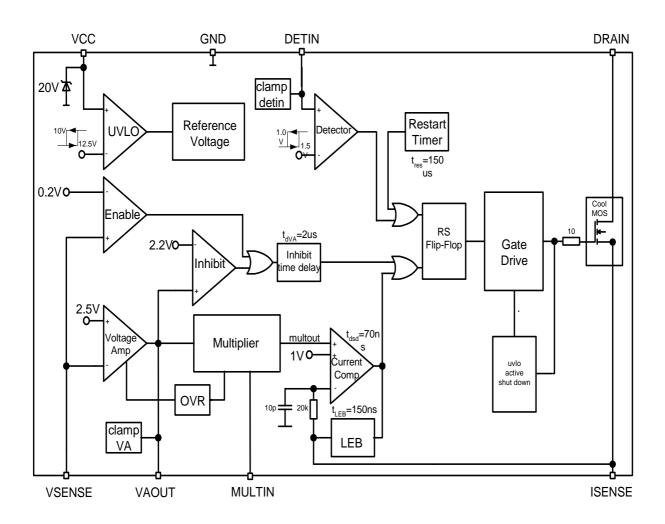

# **Block Diagram**

| Infineon Tech | PCI Group | 10.09.01 | 3 |

|---------------|-----------|----------|---|

# **Functional Description**

### Introduction

Conventional electronic ballasts and switching power supplies are designed with a bridge rectifier and a bulk capacitor. Their disadvantage is that the circuit draws power from the line when the instantaneous AC voltage exceeds the capacitors voltage. This occurs near the line voltage peak and causes a high charge current spike with following characteristics: The apparent power is higher than the real power that means low power factor condition, the current spikes are non sinusoidal with a high content of harmonics causing line noise, the rectified voltage depends on load condition and requires a large bulk capacitor, special efforts in noise suppression are necessary.

With the ICE1PD265G preconverter a sinusoidal current is achieved which varies in direct instantaneous proportional to the input voltage half sine wave and so provides a power factor near 1. This is due to the appearence of almost any complex load like a resistive one at the AC line. The harmonic distortions are reduced and comply with the IEC555 standard requirements.

## **IC Description**

The ICE1PD265G contains a wide bandwidth voltage amplifier used in a feedback loop, an overvoltage regulator, an one quadrant multiplier with a wide linear operating range, a current sense comparator, a zero current detector, a PWM and logic circuitry, a totem-pole MOSFET driver, an internal trimmed voltage reference, a restart timer, an undervoltage lockout circuitry and last not least a CoolMOS transistor.

### **Voltage Amplifier**

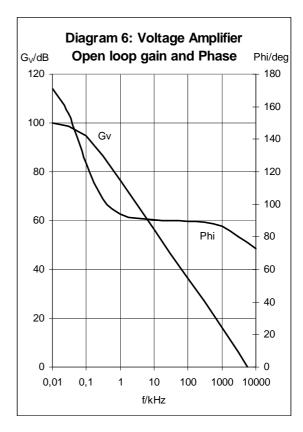

With an external capacitor between VSENSE and VAOUT the voltage amplifier forms an integrator. The integrator monitors the average output voltage over several line cycles. Typically the integrators bandwidth is set below 20 Hz in order to suppress the 100 Hz ripple of the rectified line voltage. The voltage amplifier is internally compensated and has a gain bandwidth of 3 MHz and a phase margin of 80 degrees. The non-inverting input is biased internally at 2.5V. The output is directly connected to the multiplier input.

The gate drive is disabled when VSENSE voltage is less than 0.2 V or VAOUT voltage is less than 2.2 V.

If the MOSFET is placed nearby the controller switching inteferences have to be taken into account. The output of the voltage amplifier is designed in a way to minimize these inteferences.

# **Overvoltage Regulator**

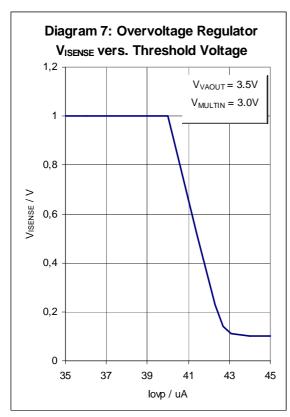

Because of the integrators low bandwidth fast changes of the output voltage can't be regulated whithin an adequate time. Fast output changes occure during initial start-up, sudden load removal, or output arcing. While the integrators differential input voltage remains zero during this fast changes a peak current is flowing through the external capacitor into pin VAOUT. If this current exceeds an internal defined margin the overvoltage regulator circuitry reduces the multiplier output voltage. As a result the on time of the MOSFET is reduced.

| Infineon Tech | PCI Group | 10.09.01 | 4 |

|---------------|-----------|----------|---|

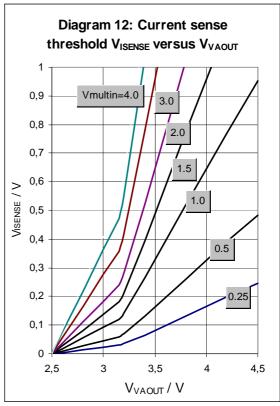

## Multiplier

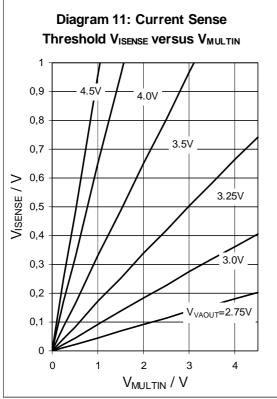

The one quadrant multiplier regulates the gate driver with respect of the DC output voltage and the AC half wave rectified input voltage. Both inputs are designed to achieve good linearity over a wide dynamic range to represent an AC line free from distortion. Special efforts are made to assure universal line applications with respect to a 90 to 270 V AC range.

The multiplier output is internally clamped at 1.0V. So the MOSFET is protected against critical operating during start up.

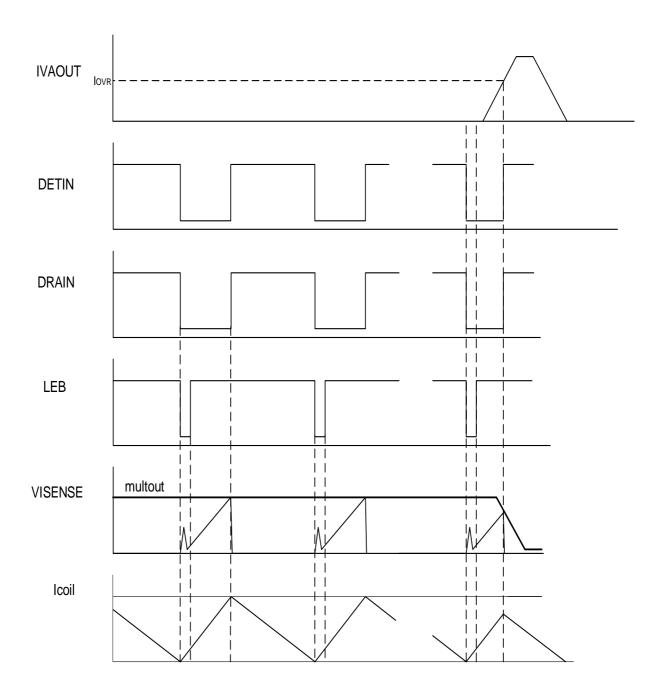

## Current sense comparator, LEB and RS Flip-Flop

An external sense resistor transferes the source current of the MOSFET into a sense voltage. The multiplier output voltage is compared with this sense voltage.

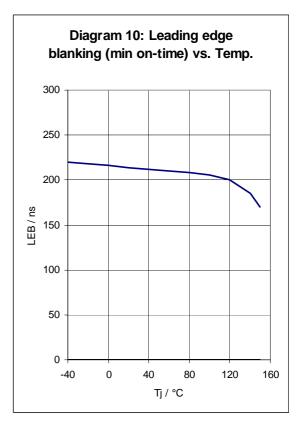

To protect the current comparator input from negative pulses a current source is inserted which sends current out of the ISENSE pin every time when ISENSE is falling below ground potential. The switch-on current peak of the MOSFET is blanked out via a resistor-capacitor circuit with a blanking time of typically 220ns. Therefore better THD is achieved at low load conditions.

The RS Flip-Flop ensures that only one single switch-on and switch-off pulse appears at the gate drive output during a given cycle (double pulse suppression).

#### **Zero Current Detector**

The zero current detector senses the inductor current via an auxiliary winding and ensures that the next on-time of the MOSFET is initiated immediately when the inductor current has reached zero. This diminishes the revers recovery losses of the boost converter diode. The MOSFET is switched off when the voltage drop of the shunt resistor reaches the voltage level of the multipler output. So the boost current waveform has a triangular shape and there are no deadtime gaps between the cycles. This leads to a continuous AC line current limiting the peak current to twice of the average current.

To prevent false tripping the zero current detector is designed as a Schmitt-Trigger with a hysteresis of 0.5V. An internal 5V clamp protects the input from overvoltage breadkdown, a 0.6V clamp prevents substrate injection. An external resistor has to be used in series with the auxiliary winding to limit the current through the clamps.

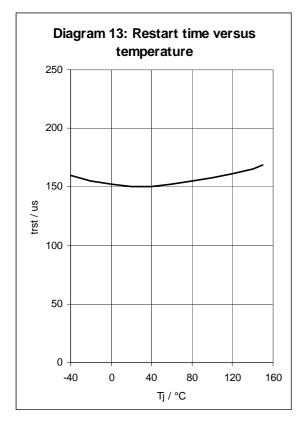

#### **Restart Timer**

If the MOS is off for more than 150us a restart impulse is generated by the restart timer.

| Infineon Tech | PCI Group |  | 10.09.01 | 5 |

|---------------|-----------|--|----------|---|

|---------------|-----------|--|----------|---|

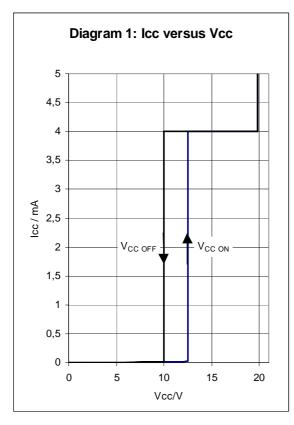

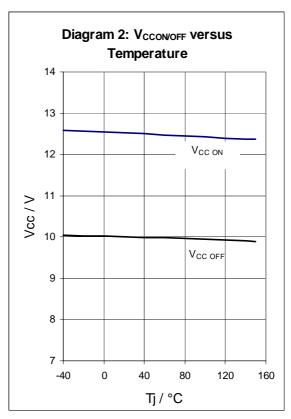

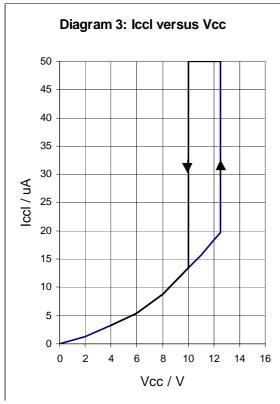

# **Undervoltage Lockout**

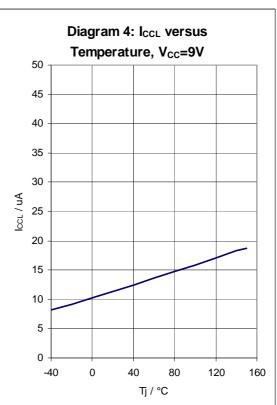

An undervoltage lockout circuitry switches the IC on when Vcc reaches the upper threshold  $V_{CCH}$  and switches the IC off when Vcc is falling below the lower threshold  $V_{CCL}$ . During start up the supply current is less then 100uA.

An internal voltage clamp has been added to protect the IC from Vcc overvoltage condition. When using this clamp special care must be taken on power dissipation.

Start up current is provided by an external start up resistor which is connected from the AC line to the input supply voltage Vcc and a storage capacitor which is connected from Vcc to ground. Be aware that this capacitor is discharged befor the IC is plugged into the application board. Otherwise the IC can be destroyed due to the high capacitor voltage.

Bootstrap power supply is created with the previous mentioned auxiliary winding and a diode (see application circuit).

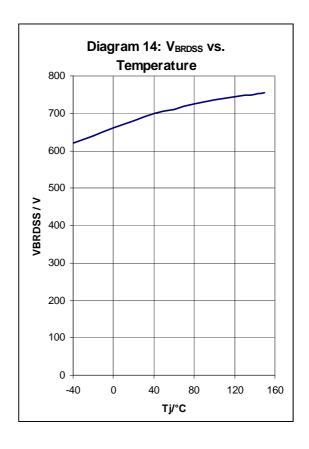

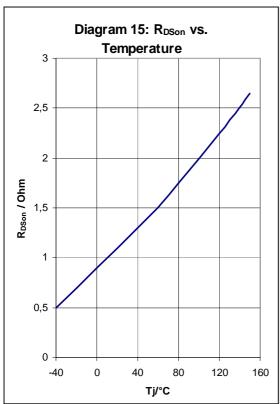

#### CoolMOS

The CoolMOS is designed for very low R<sub>DSon</sub> to reduce power dissipation.

| nfineon Tech PCI Group | 10.09.01 | 6 |

|------------------------|----------|---|

|------------------------|----------|---|

# **Signal Diagrams**

| Infineon Tech | PCI Group | 10.09.01 | 7 |

|---------------|-----------|----------|---|

# Absolute maximum ratings

| Parameter                              | Symbol             | Min  | Max  | Unit     | Remark                                                |

|----------------------------------------|--------------------|------|------|----------|-------------------------------------------------------|

| Supply + Zener Current                 | lcc+lz             | -    | 20   | mA       |                                                       |

| Supply Voltage                         | V <sub>CC</sub>    | -0.3 | Vz   | V        | Vz=Zener Voltage<br>Icc+Iz=20mA                       |

| Voltage at Pin 2,4,13                  |                    | -0.3 | 6.5  | V        |                                                       |

| Current into Pin 3                     | I <sub>VAOUT</sub> | -10  | 30   | mA<br>mA | VAOUT=4V,VSENSE=2.8V<br>VAOUT=0V,VSENSE=2.3V<br>t<1ms |

| Current into Pin 15                    | I <sub>DETIN</sub> | -10  | 10   | mA<br>mA | DETIN > 6V<br>DETIN< 0.4V                             |

| Voltage at Pin 6- 11                   | V <sub>DRAIN</sub> |      | 650  |          | T <sub>J</sub> =115°C                                 |

| Continuous Drain Current               | I <sub>D</sub>     |      | 3.2  | A<br>A   | T <sub>C</sub> =25°C<br>T <sub>C</sub> =100°C         |

| Avalanche Energy                       | E <sub>Ar</sub>    |      | 0.2  | mJ       | repetitive                                            |

| ESD Protection                         |                    |      | 2000 | V        | MIL STD 883C method 3015.6, 100pF,1500Ω               |

| Storage Temperature                    | T <sub>stg</sub>   | -50  | 150  | °C       |                                                       |

| Operating Junction Temperature         | TJ                 | -25  | 150  | °C       |                                                       |

| Thermal Resistance<br>Junction-Ambient | R <sub>thJA</sub>  |      | 120  | K/W      | P-DSO-16-10                                           |

| Infineon Tech PCI Group | 10.09.01 | 8 |

|-------------------------|----------|---|

|-------------------------|----------|---|

# Characteristics

Unless otherwise stated, -40°C<T $_j$  <150 °C,  $V_{CC}$  = 14.5V

| Parameter                             | Symbol               | min. | typ. | max. | Unit | Test Condition                 |

|---------------------------------------|----------------------|------|------|------|------|--------------------------------|

| Start-Up circuit                      | <u> </u>             |      | l .  | l    |      |                                |

| Zener Voltage                         | Vz                   | 18   | 20   | 22   | V    | lcc+lz=18mA                    |

| Start-up supply current               | I <sub>CCL</sub>     |      | 20   | 100  | uA   | Vcc=10V                        |

| Operating supply current              | Іссн                 |      | 4    | 6    | mA   | Output low                     |

| Vcc Turn-ON threshold                 | V <sub>CC</sub> ON   | 12   | 12.5 | 13   | V    |                                |

| Vcc Turn-OFF threshold                | V <sub>CC OFF</sub>  | 9.5  | 10   | 10.5 | V    |                                |

| Vcc Hysteresis                        | V <sub>CCHY</sub>    |      | 2.5  |      |      |                                |

| Voltage Amplifier                     |                      |      |      | •    | 1    |                                |

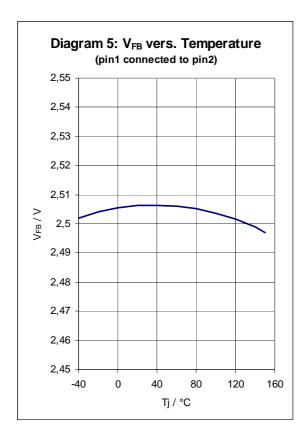

| Voltage feedback Input<br>Threshold   | V <sub>FB</sub>      | 2.45 | 2.5  | 2.55 | V    | Pin1 connected with Pin2       |

| Line regulation                       | V <sub>FBLR</sub>    |      | 2    | 5    | mV   | V <sub>CC</sub> =12V to 16V    |

| Open Loop Voltage Gain <sup>1</sup> ) | G <sub>V</sub>       |      | 100  |      | dB   |                                |

| Unity Gain Bandwidth <sup>1</sup> )   | B <sub>W</sub>       |      | 5    |      | MHz  |                                |

| Phase Margin <sup>1)</sup>            | М                    |      | 80   |      | Degr |                                |

| Bias current VSENSE                   | I <sub>BVSENSE</sub> | -1.0 | -0.3 |      | uA   |                                |

| Enable Threshold                      | V <sub>VSENSEE</sub> |      | 0.2  |      | V    |                                |

| Inhibit Threshold Voltage             | V <sub>VAOUTI</sub>  |      | 2.2  |      | V    | V <sub>ISENSE</sub> = -0.1V    |

| Inhibit Time Delay                    | t <sub>dVA</sub>     |      | 3    |      | us   | V <sub>ISENSE</sub> = -0.1V    |

| Output Current Source                 | I <sub>VAOUTH</sub>  |      | -6   |      | mA   | VAOUT=0V<br>VSENSE=2.3V,t<1ms  |

| Output Current Sink                   | I <sub>VAOUTL</sub>  |      | 30   |      | mA   | VAOUT=4V<br>VSENSE=2.8V, t<1ms |

| Upper Clamp Voltage                   | V <sub>VAOUTH</sub>  |      | 5.4  |      | V    | VSENSE=2.3V, I= -0.2mA         |

| Lower Clamp Voltage                   | V <sub>VAOUTL</sub>  |      | 1.1  |      | V    | VSENSE=2.8V, I=0.5mA           |

| Overvoltage Regulato                  | r                    |      | •    | •    | •    |                                |

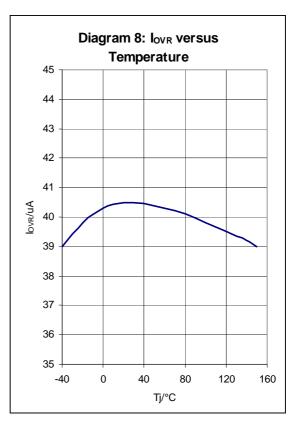

| Threshold Current                     | I <sub>OVR</sub>     | 35   | 40   | 45   | uA   | Tj=25°C                        |

| 1) not tested, guaranteed by design   |                      |      |      |      |      |                                |

| Infineon Tech PCI Group | 10.09.01 | 9 |

|-------------------------|----------|---|

|-------------------------|----------|---|

| Parameter                                      | Symbol                                | min. | typ.                                           | max. | Unit     | Test Condition                                                             |

|------------------------------------------------|---------------------------------------|------|------------------------------------------------|------|----------|----------------------------------------------------------------------------|

| <b>Current Comparator</b>                      |                                       |      |                                                |      |          |                                                                            |

| Input Bias Current                             | IBISENSE                              | -1   |                                                |      | uA       |                                                                            |

| Input Offset Voltage                           | VISENSEO<br>VISENSEO                  |      | 150<br>20                                      |      | mV<br>mV | V <sub>MULTIN</sub> =0V, VAOUT=2.4V<br>V <sub>MULTIN</sub> =0V, VAOUT>2.8V |

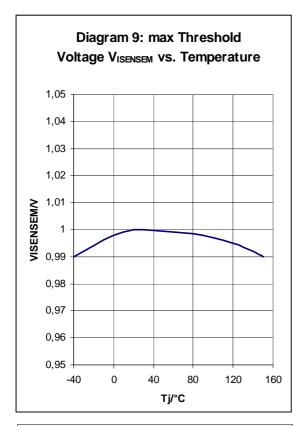

| Max Threshold Voltage                          | V <sub>ISENSEM</sub>                  | 0.95 | 1.0                                            | 1.05 | V        |                                                                            |

| Threshold at OVR                               | V <sub>ISENOVR</sub>                  |      | 0.05                                           |      | V        | I <sub>OVR</sub> =50uA                                                     |

| Shut Down Delay                                | t <sub>dISG</sub>                     |      | 100                                            |      | ns       |                                                                            |

| Leading Edge Blanking                          | t <sub>LEB</sub>                      |      | 220                                            |      | ns       |                                                                            |

| Detector                                       |                                       |      |                                                |      |          |                                                                            |

| Upper threshold voltage                        | V <sub>DETINU</sub>                   |      | 1.5                                            |      | V        |                                                                            |

| Lower threshold voltage                        | V <sub>DETINL</sub>                   |      | 1                                              |      | V        |                                                                            |

| Hysteresis                                     | V <sub>DETINHY</sub>                  |      | 0.5                                            |      | V        |                                                                            |

| Input current                                  | I <sub>BDETIN</sub>                   | -1   |                                                |      | uA       |                                                                            |

| Input clamp voltage<br>High state<br>Low state | V <sub>DETINHC</sub>                  |      | 5<br>0.5                                       |      |          | I <sub>DETIN</sub> =5mA<br>I <sub>DETIN</sub> =-5mA                        |

| Multiplier                                     |                                       |      |                                                |      | •        |                                                                            |

| Input bias current                             | I <sub>BMULTIN</sub>                  | -1   |                                                |      | uA       |                                                                            |

| Dynamic voltage range<br>MULTIN                | V <sub>MULTIN</sub>                   |      | 0 to 4                                         |      | V        | V <sub>VAOUT</sub> =2.75V                                                  |

| Dynamic voltage range<br>VAOUT                 | V <sub>VAOUT</sub>                    |      | V <sub>FB</sub> to<br>V <sub>FB</sub> +1.<br>5 |      |          | V <sub>MULTIN</sub> =1V                                                    |

| Multiplier Gain                                | K <sub>low</sub><br>K <sub>high</sub> |      | 0.18<br>0.56                                   |      | V<br>V   | V <sub>VAOUT</sub> <3V<br>V <sub>VAOUT</sub> >3.5V                         |

| Restart Timer                                  |                                       |      |                                                |      |          |                                                                            |

| restart time                                   | t <sub>RES</sub>                      |      | 150                                            |      | us       |                                                                            |

| Infineon Tech | PCI Group | 10.09.01 | 10 |

|---------------|-----------|----------|----|

| Parameter                       | Symbol                                 | min.       | typ.     | max.       | Unit       | Test Condition                                                                        |

|---------------------------------|----------------------------------------|------------|----------|------------|------------|---------------------------------------------------------------------------------------|

| CoolMOS                         | •                                      | <u> </u>   | <u> </u> |            | <u> </u>   |                                                                                       |

| Drain source breakdown voltage  | V <sub>BRDSS</sub>                     | 600<br>650 |          |            | V<br>V     | T <sub>J</sub> =25°C<br>T <sub>J</sub> =115°C                                         |

| Drain source on-resistance      | R <sub>DSon</sub>                      |            | 1.1      | 1.4<br>3.8 | Ohm<br>Ohm | T <sub>j</sub> =25°C<br>T <sub>j</sub> =150°C                                         |

| Zero gate voltage drain current | IDSS                                   |            | 0.5      | 1<br>70    | uA<br>uA   | U <sub>GS</sub> =0V, T <sub>j</sub> =25°<br>U <sub>GS</sub> =0V, T <sub>j</sub> =150° |

| Output capacitance 1)           | C <sub>OSS</sub>                       |            | 150      |            | pF         | V <sub>DS</sub> =25V, f=1MHz                                                          |

| Rise time<br>Fall time          | t <sub>rise</sub><br>t <sub>fall</sub> |            | 30<br>50 |            | ns<br>ns   |                                                                                       |

| 1) not tested, guaranteed by    | y design                               |            | •        | •          |            |                                                                                       |

| Infineon Tech PCI Group |  | 10.09.01 | 11 |

|-------------------------|--|----------|----|

|-------------------------|--|----------|----|

# **Electrical Diagrams**

|  | Infineon Tech | PCI Group |  | 10.09.01 | 12 |

|--|---------------|-----------|--|----------|----|

|--|---------------|-----------|--|----------|----|

| Infineon Tech PCI Group | 10.09.01 | 13 |

|-------------------------|----------|----|

|-------------------------|----------|----|

| Infineon Tech PCI Group |  | 10.09.01 | 15 |  |

|-------------------------|--|----------|----|--|

|-------------------------|--|----------|----|--|

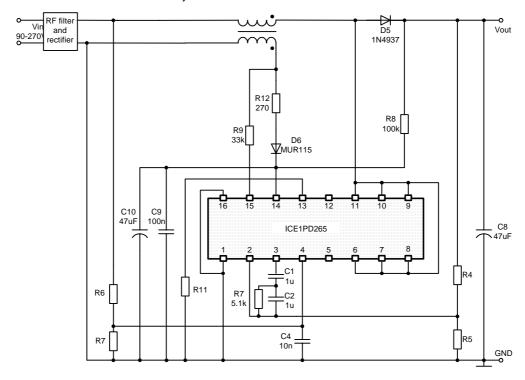

Application circuit: R<sub>DSON</sub>=1.1 Ohm Pout=80W, Vin= 180 - 270V AC Pout=34W, Vin= 90 - 270 V AC