# International TOR Rectifier

# IR2520D(S)

# ADAPTIVE BALLAST CONTROL IC

#### **Features**

- 600V Half Bridge Driver

- Integrated Bootstrap Diode

- Adaptive zero-voltage switching (ZVS)

- Internal Crest Factor Over-Current Protection

- 0 to 5VDC Voltage Controlled Oscillator

- Programmable minimum frequency

- Micropower Startup Current (150uA)

- Internal 15.6V zener clamp on Vcc

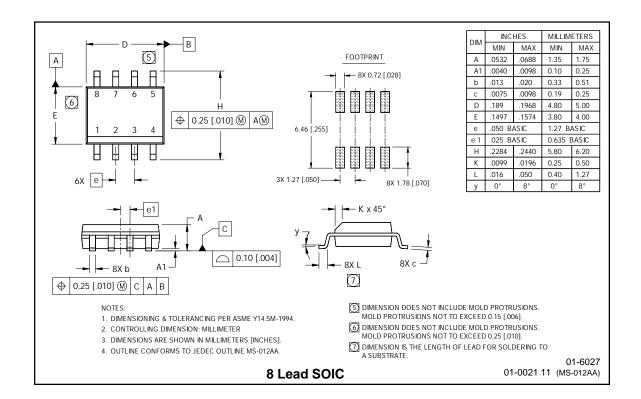

- Small DIP8/SO8 Package

#### **Packages**

### **Description**

The IR2520D is a complete adaptive ballast controller and 600V half-bridge driver integrated into a single IC for fluorescent lighting applications. The IC includes adaptive zero-voltage switching (ZVS), internal crest factor over-current protection, as well as an integrated bootstrap diode. The heart of this IC is a voltage controlled oscillator with externally programmable minimum frequency. All of the necessary ballast features are integrated in a small 8-pin DIP or SOIC package.

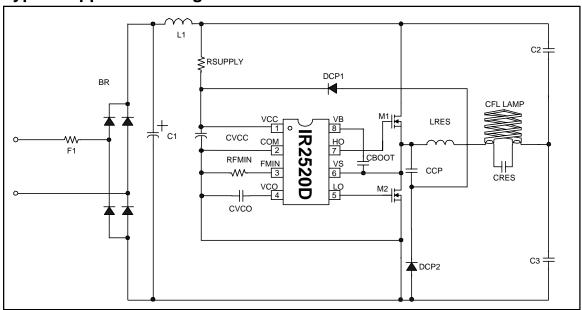

# **Typical Application Diagram**

Please note that this data sheet contains advance information which could change before product is released to production.

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                                                              |             | Min.                  | Max.                  | Units |

|---------------------|-----------------------------------------------------------------------------------------|-------------|-----------------------|-----------------------|-------|

| V <sub>B</sub>      | High side floating supply voltage                                                       |             | -0.3                  | 625                   |       |

| Vs                  | High side floating supply offset voltage                                                |             | V <sub>B</sub> - 25   | V <sub>B</sub> + 0.3  | Ţ,    |

| V <sub>HO</sub>     | High side floating output voltage                                                       |             | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3  | V     |

| V <sub>LO</sub>     | Low side output voltage                                                                 | -0.3        | V <sub>CC</sub> + 0.3 |                       |       |

| I <sub>OMAX</sub>   | Maximum allowable output current (HO,LO) due to external power transistor miller effect |             | -500                  | 500                   | mA    |

| V <sub>VCO</sub>    | Voltage controlled oscillator input voltage                                             |             | -0.3                  | V <sub>CC</sub> + 0.3 | V     |

| Icc                 | Supply current (Note 1)                                                                 |             | -20                   | 20                    | mA    |

| dV <sub>S</sub> /dt | Allowable offset voltage slew rate                                                      |             | -50                   | 50                    | V/ns  |

| PD                  | Package power dissipation @ T <sub>A</sub> ≤ +25°C                                      | 8-Lead PDIP | _                     | 1                     |       |

|                     | PD=(T <sub>JMAX</sub> -T <sub>A</sub> )Rth <sub>JA</sub>                                | 8-Lead SOIC | _                     | 0.625                 | W     |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient                                                 | 8-Lead PDIP | _                     | 125                   |       |

|                     |                                                                                         | 8-Lead SOIC | _                     | 200                   | °C/W  |

| TJ                  | Junction temperature                                                                    |             | -55                   | 150                   |       |

| T <sub>S</sub>      | Storage temperature                                                                     |             | -55                   | 150                   | °C    |

| TL                  | Lead temperature (soldering, 10 seconds)                                                |             | _                     | 300                   |       |

Note 1: This IC contains a zener clamp structure between the chip VCC and COM, which has a nominal breakdown voltage of 15.6V. Please note that this supply pin should not be driven by a DC, low impedance power source greater than the VCLAMP specified in the Electrical Characteristics section.

# **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol            | Definition                                            | Min.                  | Max.   | Units |

|-------------------|-------------------------------------------------------|-----------------------|--------|-------|

| V <sub>BS</sub>   | High side floating supply voltage                     | V <sub>CC</sub> - 0.7 | VCLAMP |       |

| ٧s                | Steady state high side floating supply offset voltage | -1                    | 600    | V     |

| Vcc               | Supply voltage                                        | Vccuv+                | VCLAMP | 1     |

| Icc               | Supply current                                        | Note 2                | 10     | mA    |

| R <sub>FMIN</sub> | Minimum frequency setting resistance                  | 10                    | 100    | kΩ    |

| V <sub>VCO</sub>  | VCO pin voltage                                       | 0                     | 5      | V     |

| TJ                | Junction temperature                                  | -25                   | 125    | °C    |

Note 2: Enough current should be supplied into the VCC pin to keep the internal 15.6V zener clamp diode on this pin regulating its voltage, VCLAMP.

# **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V$ ,  $C_{LO} = C_{HO} = 1000 pF$  and  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol                | Definition                                                                       | Min. | Тур.     | Max. | Units | Test Conditions                           |

|-----------------------|----------------------------------------------------------------------------------|------|----------|------|-------|-------------------------------------------|

| Supply (              | Characteristics                                                                  |      |          |      |       |                                           |

| V <sub>CCUV+</sub>    | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage positive going threshold | _    | 13.2     | _    |       | V <sub>CC</sub> rising from OV            |

| V <sub>CCUV</sub> -   | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage negative going threshold | _    | 10.5     | _    | V     |                                           |

| V <sub>UVHYS</sub>    | V <sub>CC</sub> supply undervoltage lockout hysteresis                           | _    | 2.7      | _    |       |                                           |

| IQCCUV                | UVLO quiescent current                                                           | 50   | 120      | 200  |       | V <sub>CC</sub> = 11V                     |

| IQCCFLT               | Fault mode quiescent current                                                     | _    | 180      | _    | μΑ    |                                           |

| IQCC                  | Quiescent V <sub>CC</sub> supply current                                         | _    | 1.8      | _    | mA    | V <sub>CC</sub> = 14V                     |

| I <sub>CC50k</sub>    | Current, f = 50kHz                                                               | _    | 1.8      | _    | IIIA  |                                           |

| VCLAMP                | V <sub>CC</sub> Zener clamp voltage                                              | 14.5 | 15.6     | 16.5 | V     | I <sub>CC</sub> = 10mA                    |

| Floating              | Supply Characteristics                                                           |      |          |      |       |                                           |

| I <sub>QBS</sub> 0    | Quiescent V <sub>BS</sub> supply current                                         | -1   | 0        | 5    |       | V <sub>HO</sub> = V <sub>S</sub>          |

| I <sub>QBS</sub> 1    | Quiescent V <sub>BS</sub> supply current                                         | _    | 28       | _    | μΑ    | V <sub>HO</sub> = V <sub>B</sub>          |

| V <sub>BSMIN</sub>    | Minimum required V <sub>BS</sub> voltage for proper HO                           | _    | 2.5      | _    | V     |                                           |

| ILK                   | Offset supply leakage current                                                    | _    | _        | 50   | μΑ    | V <sub>B</sub> = V <sub>S</sub> = 600V    |

| Oscillato             | or I/O Characteristics                                                           | •    | •        | •    | •     | •                                         |

| F <sub>VCO(min)</sub> | Minimum oscillator frequency                                                     | 1 –  | 35       | _    | 1.11= | V <sub>CO</sub> =5V,R <sub>FMIN=82K</sub> |

| F <sub>VCO(max)</sub> | Maximum oscillator frequency                                                     | _    | 100      | _    | kHz   | V <sub>CO</sub> =0V,R <sub>FMIN=82K</sub> |

| D                     | Oscillator duty cycle                                                            | _    | 50       | _    | %     |                                           |

| T <sub>DLO</sub>      | LO output deadtime                                                               | T —  | 1.5      | -    |       |                                           |

| T <sub>DHO</sub>      | HO output deadtime                                                               | _    | 1.5      | _    | μS    |                                           |

| I <sub>VCOPH</sub>    | Preheat mode & frequency sweep mode                                              | _    | 1.0      | _    | ^     |                                           |

| IVCOADPT              | Adaptive mode VCO lead changing current                                          | _    | 1.0      | _    | μΑ    |                                           |

| V <sub>V</sub> COFLT  | Fault mode & UVLO mode VCO lead voltage                                          | _    | 0        | _    | V     |                                           |

| Gate Dri              | ver Output Characteristics                                                       |      |          |      |       |                                           |

| V <sub>OL</sub>       | Low level output voltage (HO or LO)                                              | T —  | _        | 100  |       |                                           |

| V <sub>HL</sub>       | High level output voltage (HO or LO)                                             | †-   | _        | 100  | mV    |                                           |

| T <sub>RISE</sub>     | Turn on rise time                                                                | †-   | _        | 150  | m)/   |                                           |

| T <sub>FALL</sub>     | Turn off fall time                                                               | 1_   | <u> </u> | 100  | mV    |                                           |

# **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V$ ,  $C_{LO} = C_{HO} = 1000 pF$  and  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol                                    | Definition                                | Min. | Тур. | Max. | Units | Test Conditions |

|-------------------------------------------|-------------------------------------------|------|------|------|-------|-----------------|

| Protection Characteristics                |                                           |      |      |      |       |                 |

| V <sub>CSCF</sub>                         | Crest factor peak-to-average fault factor | _    | 3    | _    |       |                 |

| Minimum Frequency Setting Characteristics |                                           |      |      |      |       |                 |

| V <sub>FMIN</sub>                         | FMIN lead voltge during normal operation  | _    | 5.1  | _    | V     |                 |

| V <sub>FMINFLT</sub>                      | FMIN lead voltge during fault mode        | _    | 0.0  |      | V     |                 |

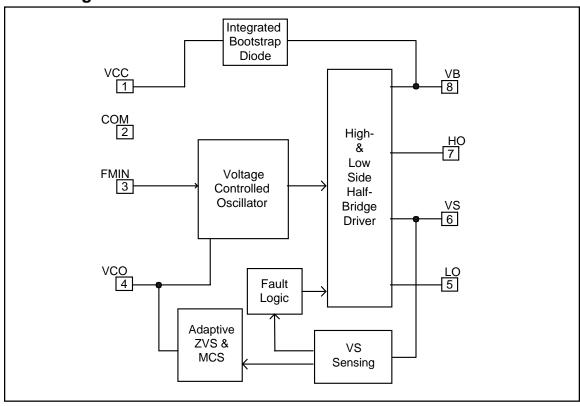

# **Block Diagram**

# **Lead Definitions**

# **Lead Assignments**

|        |                                       | -                      |

|--------|---------------------------------------|------------------------|

| Symbol | Description                           |                        |

| Vcc    | Supply voltage                        | VCC 11 0 8 VB          |

| COM    | IC power and signal ground            | 7 7 7                  |

| FMIN   | Minimum frequency setting             | COM 2 <b>2</b> 7 HO    |

| VCO    | Voltage controlled oscillator input   | 20                     |

| LO     | Low side gate driver output           | COM 2 7 HO FMIN 3 6 VS |

| Vs     | High side floating return             | VCO 4 9 5 LO           |

| НО     | High side gate driver output          | 700 [4]                |

| VB     | High side gate driver floating supply |                        |

#### **Functional Description**

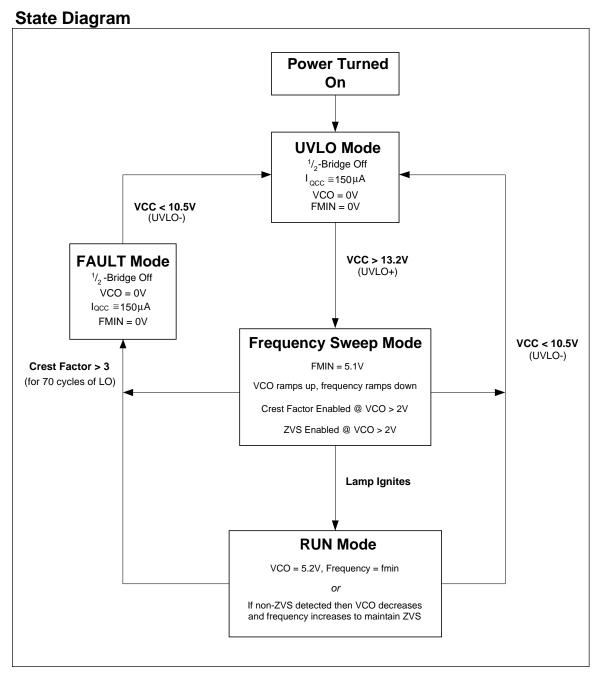

#### Under-voltage Lock-Out Mode

The under-voltage lockout mode (UVLO) is defined as the state the IR2520D is in when VCC is below the turn-on threshold of the IC. The IR2520D under voltage lock-out is designed to maintain an ultra low supply current (<200uA), and to guarantee that the IR2520D is fully functional before the high and low side output drivers are activated.

The start-up capacitor,  $C_{_{VCC}}$ , is charged by current through supply resistor,  $R_{_{SUPPLY}}$ , minus the start-up current drawn by the IR2520D. This resistor is chosen to provide sufficient current to supply the IR2520D from the DC bus.  $C_{_{VCC}}$  should be large enough to hold the voltage at Vcc above the UVLO threshold for one half cycle of the line voltage as it will only be charged at the peak. Once the capacitor voltage on  $V_{_{CC}}$  reaches the start-up threshold, the IR2520D turns on and then HO and LO start oscillating.

An internal bootstrap diode between Vcc and VB and external supply capacitor,  $C_{\text{BOOT}},$  determine the supply voltage for the high side driver circuitry. An external charge pump circuit consisting of a capacitor,  $C_{\text{CP}}$  and two diodes,  $D_{\text{CP}},$  and  $D_{\text{CP}},$  supplies the voltage for the low side driver circuitry. To guarantee that the high-side supply is charged up before the first pulse on pin HO, the first pulse from the output drivers comes from the LO pin. LO may oscillate several times until VB-VS exceeds UVBS+ (9 Volts) and the high-side driver is enabled.

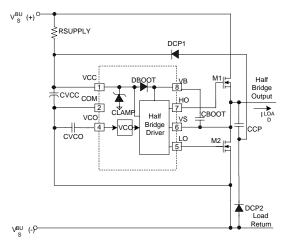

Figure 1, Start-up circuitry

During UVLO mode, the high and low-side driver outputs, HO and LO, are both low and pin VCO is pulled down to COM for resetting the starting frequency to the maximum.

#### Frequency Sweep Mode

When VCC exceeds UVLO+ threshold, the IR2520D enters frequency sweep mode. An internal current source charges the external capacitor on pin VCO,  $C_{vco}$ , and the voltage on pin VCO starts ramping up linearly. The frequency ramps down towards the resonance frequency of the high-Q ballast output stage causing the lamp voltage and load current to increase. When the voltage on pin VCO exceeds 2V, the crest factor detection and zero-voltage switching (ZVS) are both enabled. The voltage on pin VCO continues to increase and the frequency keeps decreasing until the lamp ignites, or, the internal crest factor threshold is reached (see Fault Mode section). If the lamp ignites successfully, the voltage on pin VCO continues to increase until it internally limits at 5.2V. The frequency stops decreasing and stays at the minimum frequency as programmed by an external resistor, RFMIN, on pin FMIN. The minimum frequency should be set below the high-Q resonance frequency of the ballast output stage to ensure that the frequency ramps through resonance for lamp ignition. The desired preheat time can be set by adjusting the slope of the VCO ramp with the external capacitor, C<sub>vco</sub>.

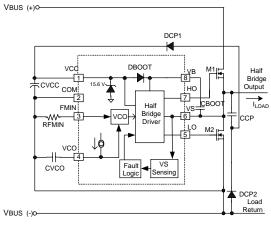

Figure 2, Frequency sweep circuitry

# IR2520D(S)

#### Run Mode

The frequency decreases during the frequency sweep mode until the lamp ignites and the ballast output stage becomes a low-Q RCL circuit. The frequency then deceases further until the VCO pin voltage limits at 5.2V and the minimum frequency is reached. The resonant inductor, resonant capacitor, DC bus voltage and minimum frequency determine the running lamp power. The IC stays at this minimum frequency unless non-zero-voltage switching (non-ZVS) is detected at the VS pin. If the voltage has not slewed entirely to COM during the deadtime such that there is voltage across the external low-side switch before LO turns-on, then the system is operating too close to resonance and destructive non-ZVS capacitive mode switching occurs. To correct for this, a pulse of current is sinked from the VCO pin to discharge the external capacitor,  $\mathbf{C}_{\text{\tiny VCO}}\text{,}$  slightly causing the frequency to increase. The VCO capacitor then charges up during the rest of the cycle slowly due to an internal current source. The frequency is therefore trying to decrease towards resonance by charging the VCO capacitor and the adaptive ZVS circuit "nudges" the frequency back up slightly above resonance when non-ZVS occurs. The circuit then remains in this closed-loop adaptive ZVS mode during running and maintains ZVS operation with changing line conditions, component tolerance variations and lamp/load variations. The 600V fabrication process used in the development of this IC allows for the VS pin to be accurately measured with an internal high-voltage MOSFET for zero volts during the nonoverlapping deadtime, while withstanding the high DC bus voltage during other portions of the switching cycle when the high-side MOSFET is turned on and VS is at the DC bus potential.

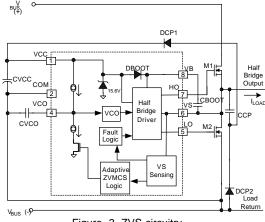

Figure 3, ZVS circuitry

#### Fault Mode

Should a lamp non-strike condition occur where the filaments are intact but the lamp does not ignite, the lamp voltage and output stage current will increase during the ignition ramp until the resonant inductor saturates or capacitive mode switching occurs. To detect this, the  $\overset{\cdot}{\text{IC}}$  performs a measurement of the VS pin during the on-time of the LO pin. The voltage at the VS pin during the on-time of pin LO is determined by the current flowing through the on-resistance (RDSon) of the external low-side MOSFET. The RDSon of the external low-side MOSFET therefore serves as the current-sensing resistor and VS serves as the current sensing pin on the IC. Sensing the half-bridge current in this way eliminates the need for an external current-sensing resistor and an additional current-sensing pin on the IC. An internal high-voltage MOSFET is turned on when VS is low (when the external low-side MOSFET is 'on') for performing the current sensing, and is turned off during the rest of the switching cycle for withstanding the high-voltage when VS is equal to the DC bus voltage (when the external high-side MOSFET is 'on'). Since the RDSon has a positive temperature coefficient, the IC performs an internal crest factor measurement for detecting excessive dangerous currents or inductor saturation which can occur during a lamp non-strike fault condition. Performing the crest factor measurement provides a relative current measurement which cancels temperature and/or tolerance variations of the RDSon of the external low-side half-bridge MOSFET. Should the peak current during the on-time of LO exceed a threshold of 3 times the average current for approximately 70 switching cycles of LO, the IC will enter Fault Mode and both gate driver outputs will be latched 'low'. To reset the IC back to frequency sweep mode VCC must be recycled below and above the internal UVLO thresholds.

Should an open filament lamp fault occur, hard-switching will occur at the half-bridge. The crest factor circuit will detect this condition as well and after approximately 70 cycles of the fault occurance the IC will enter Fault Mode and both gate driver outputs will be latched 'low'. To reset the IC back to frequency sweep mode VCC must be recycled below and above the internal UVLO thresholds

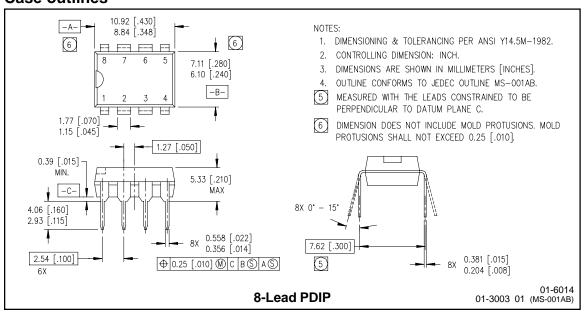

#### **Case outlines**

# International TOR Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 3/19/2003