# PowerPC 740 and PowerPC 750 Microprocessor Datasheet

CMOS 0.20  $\mu$ m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

Version 1.1

10/9/2001

**IBM Microelectronics Division**

#### **Notices**

Before using this information and the product it supports, be sure to read the general information on the back cover of this book.

#### **Trademarks**

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

IBM IBM Logo PowerPC AIX PowerPC 750 PowerPC 740

Other company, product, and service names may be trademarks or service marks of others.

This document contains information on a new product under development by IBM. IBM reserves the right to change or discontinue this product without notice.

© International Business Machines Corporation 2001. All rights reserved.

# **Table of Contents**

| Pretace                                                   | 4  |

|-----------------------------------------------------------|----|

| New Features for dd3.x                                    | 4  |

| Overview                                                  | 5  |

| Features                                                  | 6  |

| General Parameters                                        | _  |

| Electrical and Thermal Characteristics                    | 9  |

| DC Electrical Characteristics                             | 9  |

| AC Electrical Characteristics                             | 13 |

| Clock AC Specifications                                   |    |

| 60x Bus Input AC Specifications                           | 14 |

| 60x Bus Output AC Specifications                          | 16 |

| L2 Clock AC Specifications                                | 18 |

| L2 Bus Input AC Specifications                            | 20 |

| L2 Bus Output AC Specifications                           |    |

| IEEE 1149.1 AC Timing Specifications                      | 22 |

| PowerPC 740 Microprocessor Pin Assignments                |    |

| PowerPC 740 Microprocessor Pinout Listings                | 25 |

| PowerPC 740 Package                                       |    |

| Mechanical Dimensions of the PowerPC 740 255 CBGA Package | 29 |

| PowerPC 750 Microprocessor Pin Assignments                |    |

| PowerPC 750 Package                                       |    |

| Mechanical Dimensions of the PowerPC 750 360 CBGA Package |    |

| System Design Information                                 | 36 |

| PLL Configuration                                         |    |

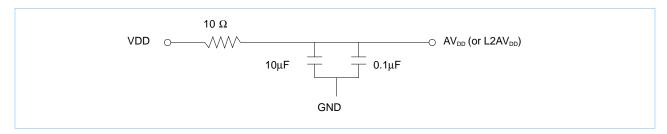

| PLL Power Supply Filtering                                |    |

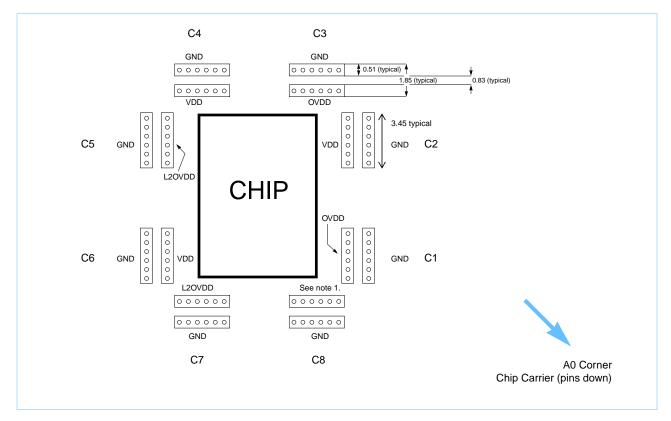

| Decoupling Recommendations                                | 37 |

| Connection Recommendations                                | 37 |

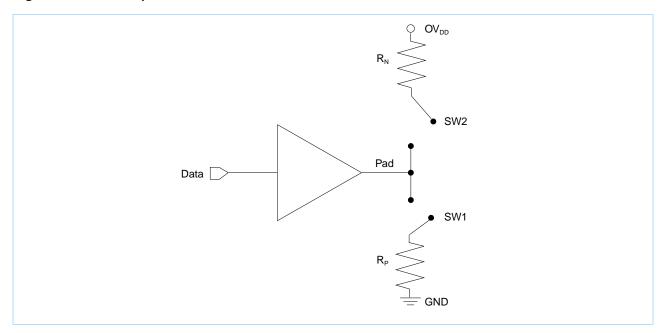

| Output Buffer DC Impedance                                | 38 |

| Pull-up Resistor Requirements                             | 39 |

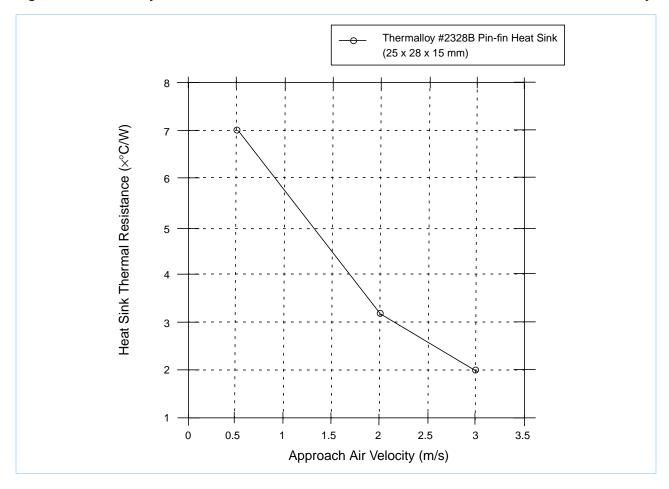

| Thermal Management Information                            | 40 |

| Internal Package Conduction Resistance                    | 41 |

| Heat Sink Selection Example                               | 44 |

| Ordering Information                                      | 46 |

#### **Preface**

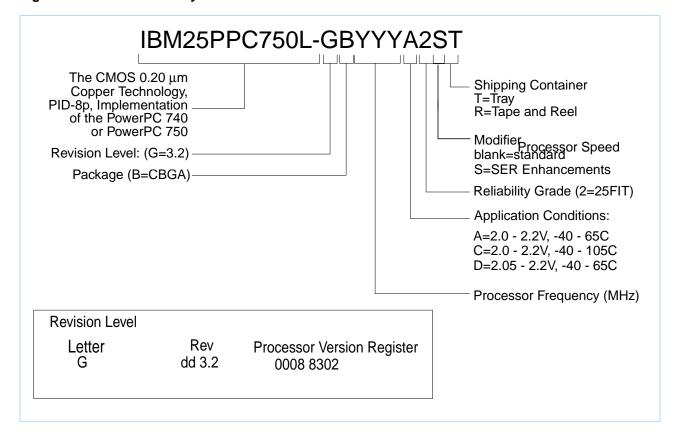

The PowerPC 740<sup>TM</sup> and PowerPC 750<sup>TM</sup> are members of the PowerPC<sup>TM</sup> family of reduced instruction set computer (RISC) microprocessors. The PPC740L and PPC750L microprocessors are the PID-8p implementations of the PowerPC 740 and PowerPC 750 in IBM CMOS 7S 0.20 μm copper technology. They are referred to in the body of this document as "740" and "750."

Information in this document does not apply to implementations of the PowerPC 740 and PowerPC 750 in other technologies, such as the PID-8t.

The information in this document is also specific to revision level dd3.2 of the (PID-8p) PPC740L and PPC750L, and does not apply to previous revisions.

This document is generally written in terms of the 750. Unless otherwise noted, information that applies to the 750 also applies to the 740. Exceptions are detailed. The 740 die is identical to the 750 die, but the 740 package and pinout are different, in that the 740 does not pin out the L2 interface.

The 740 uses the same die as the 750, but the 740 does not pin out the L2 cache interface.

#### New Features for dd3.x

- Selectable I/O voltages on 60X bus and L2 bus. See Table, "Recommended Operating Conditions," on page 9. Older revs must leave these pins "no connect" or "tied high" for 3.3v I/Os. Ac timings are the same for all I/O voltages modes unless otherwise noted.

- 60X bus to core frequency now also supports the 10x ratio. See Table, "PLL Configuration," on page 38.

- Extra output hold on the 60x bus by L2\_TSTCLK pin tied low is no longer available. The L2\_TSTCLK pin

must now be tied to OV<sub>DD</sub> for normal operation. See Table , "60X Bus Output AC Timing Specifications for

the 750<sup>1</sup>," on page 16.

## **Overview**

The 750 is targeted for high performance, low power systems and supports the following power management features: doze, nap, sleep, and dynamic power management. The 750 consists of a processor core and an internal L2 Tag combined with a dedicated L2 cache interface and a 60x bus. The L2 cache is not available with the 740.

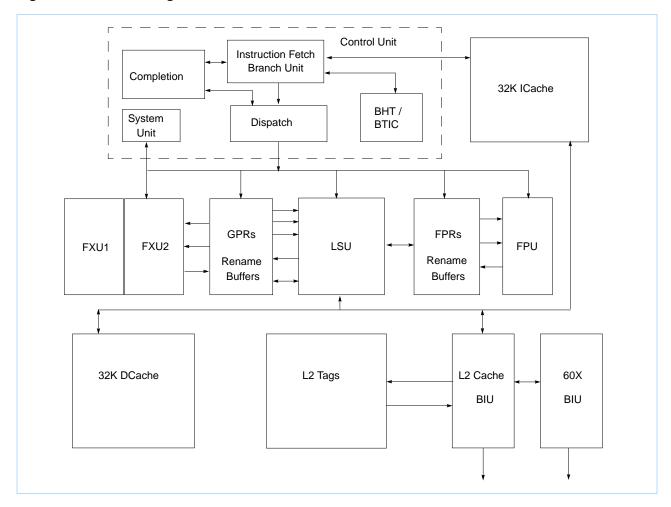

Figure 1 shows a block diagram of the 750.

Figure 1. 750 Block Diagram

#### **Features**

This section summarizes features of the implementation of the PowerPC 750 architecture. For details, see the *PowerPC 740 and PowerPC750 User's Manual*.

- · Branch processing unit

- Four instructions fetched per clock.

- One branch processed per cycle (plus resolving 2 speculations).

- Up to 1 speculative stream in execution, 1 additional speculative stream in fetch.

- 512-entry branch history table (BHT) for dynamic prediction.

- 64-entry, 4-way set associative branch target instruction cache (BTIC) for eliminating branch delay slots.

#### · Dispatch unit

- Full hardware detection of dependencies (resolved in the execution units).

- Dispatch two instructions to six independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, or floating-point).

- Serialization control (predispatch, postdispatch, execution, serialization).

#### Decode

- Register file access.

- Forwarding control.

- Partial instruction decode.

#### Load/store unit

- One cycle load or store cache access (byte, half word, word, double word).

- Effective address generation.

- Hits under misses (one outstanding miss).

- Single-cycle misaligned access within double word boundary.

- Alignment, zero padding, sign extend for integer register file.

- Floating-point internal format conversion (alignment, normalization).

- Sequencing for load/store multiples and string operations.

- Store gathering.

- Cache and TLB instructions.

- Big and little-endian byte addressing supported.

- Misaligned little-endian support in hardware.

#### · Fixed-point units

- Fixed-point unit 1 (FXU1); multiply, divide, shift, rotate, arithmetic, logical.

- Fixed-point unit 2 (FXU2); shift, rotate, arithmetic, logical.

- Single-cycle arithmetic, shift, rotate, logical.

- Multiply and divide support (multi-cycle).

- Early out multiply.

#### Floating-point unit

- Support for IEEE-754 standard single- and double-precision floating-point arithmetic.

- 3 cycle latency, 1 cycle throughput, single-precision multiply-add.

- 3 cycle latency, 1 cycle throughput, double-precision add.

- 4 cycle latency, 2 cycle throughput, double-precision multiply-add.

- Hardware support for divide.

- Hardware support for denormalized numbers.

- Time deterministic non-IEEE mode.

#### · System unit

- Executes CR logical instructions and miscellaneous system instructions.

- Special register transfer instructions.

#### Cache structure

- 32K, 32-byte line, 8-way set associative instruction cache.

- 32K, 32-byte line, 8-way set associative data cache.

- Single-cycle cache access.

- Pseudo-LRU replacement.

- Copy-back or write-through data cache (on a page per page basis).

- Supports all PowerPC memory coherency modes.

- Non-blocking instruction and data cache (one outstanding miss under hits).

- No snooping of instruction cache.

#### Memory management unit

- 128 entry, 2-way set associative instruction TLB.

- 128 entry, 2-way set associative data TLB.

- Hardware reload for TLB's.

- 4 instruction BAT's and 4 data BATs.

- Virtual memory support for up to 4 exabytes (2<sup>52</sup>) virtual memory.

- Real memory support for up to 4 gigabytes (2<sup>32</sup>) of physical memory.

#### Level 2 (L2) cache interface (Not available on the 740)

- Internal L2 cache controller and 4K-entry tags; external data SRAMs.

- 256K, 512K, and 1 Mbyte 2-way set associative L2 cache support.

- Copy-back or write-through data cache (on a page basis, or for all L2).

- 64-byte (256K/512K) and 128-byte (I-Mbyte) sectored line size.

- Supports flow-through (reg-buf) synchronous burst SRAMs, pipelined (reg-reg) synchronous burst SRAMs, and pipelined (reg-reg) late-write synchronous burst SRAMs with optional parity checking.

- Supports Core-to-L2 frequency divisors of ÷1, ÷1.5, ÷2, ÷2.5, and ÷3. The 750 supports the L2 frequency range specified in Section "L2 Clock AC Specifications," on page 18. For higher L2 frequencies, please contact ppcsupp@us.ibm.com.

#### Bus interface

- Compatible with 60x processor interface.

- 32-bit address bus with optional parity checking.

- 64-bit data bus (can be operated in 32-bit data bus mode) with optional parity checking.

- Bus-to-core frequency multipliers from 2x to 10x. See the Table, "PLL Configuration," on page 38.

#### Integrated power management

- Low-power 2.0/3.3V design.

- Three static power saving modes: doze, nap, and sleep.

- Automatic dynamic power reduction when internal functional units are idle.

#### Integrated Thermal Management Assist Unit

- On-chip thermal sensor and control logic.

- Thermal Management Interrupts for software regulation of junction temperature.

#### Testability

- JTAG interface.

10/9/2001 Version 1.1 Page 7

## **General Parameters**

The following list provides a summary of the general parameters of the 750.

Technology 0.20µm CMOS (general lithography), six-layer copper metallization

$0.12 \pm 0.04 \mu m~L_{\textrm{\tiny eff}}$

Die Size 5.14mm x 7.78mm (40mm<sup>2</sup>)

Transistor count 6.35 million

Logic design Fully-static

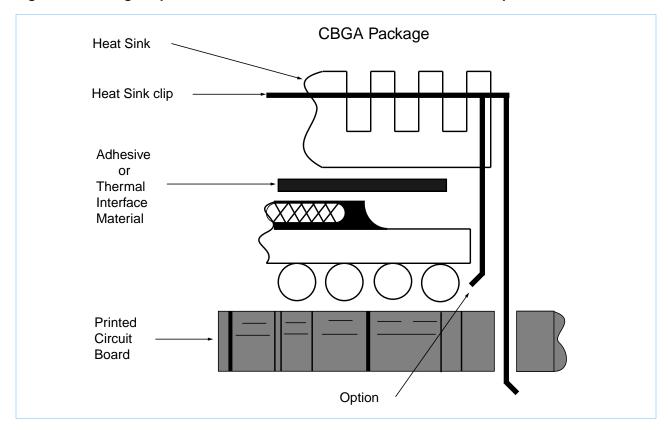

Package 740: Surface mount 21x21mm, 255-lead ceramic ball grid array (CBGA)

750: Surface mount 25x25mm, 360-lead ceramic ball grid array (CBGA)

PPC 740/PPC 750 core

power supply 2V Nominal (see Application Conditions)

I/O power supply 3.3V 2.5V, or 1.8V (Nominal Selectable)

## **Electrical and Thermal Characteristics**

#### **DC Electrical Characteristics**

The 750 60x bus power supply can be either 3.3V, 2.5V, or 1.8V nominal; likewise, the L2 power supply can be either 3.3V, 2.5V, or 1.8V nominal. See the pinout listing for more information

#### **Absolute Maximum Ratings** See Notes

| Characteristic            | Symbol                | Value        | Unit |

|---------------------------|-----------------------|--------------|------|

| Core supply voltage       | $V_{	t DD}$           | -0.3 to 2.15 | V    |

| PLL supply voltage        | $AV_{\mathtt{DD}}$    | -0.3 to 2.15 | V    |

| L2 DLL supply voltage     | L2AV <sub>DD</sub>    | -0.3 to 2.15 | V    |

| 60x bus supply voltage    | $OV_{DD(3.3V)}$       | -0.3 to 3.6  | V    |

|                           | $OV_{DD(2.5V)}$       | -0.3 to 2.8  |      |

|                           | $OV_{DD(1.8V)}$       | -0.3 to 2.1  |      |

| L2 bus supply voltage     | L2OV <sub>DD</sub>    | -0.3 to 3.6  | V    |

| nput voltage              | $V_{IN(3.3V)}$        | -0.3 to 3.6  | V    |

|                           | V <sub>IN(2.5V)</sub> | -0.3 to 2.8  |      |

|                           | $V_{IN(1.8V)}$        | -0.3 to 2.1  |      |

| Storage temperature range | T <sub>STG</sub>      | -55 to 150   | °C   |

#### Note:

- Functional and tested operating conditions are given in Table "Recommended Operating Conditions," below. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. **Caution:** V<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3V at any time, including during power-on reset. This is a DC specification only. V<sub>IN</sub> overshoot transients up to OV<sub>DD</sub>+1V, and undershoots down to GND-1V (both measured with the 740 in the circuit) are allowed for up to 5ns.

- Caution: OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub> by more than 2.0V at any time during normal operation. On power up and power down, OV<sub>DD</sub> is allowed to exceed V<sub>DD</sub>/AV<sub>DD</sub> by up to 3.3V for up to 20 ms, or by up to 2.5V for 40 ms. Excursions beyond 40 ms or 3.3V are not allowed.

- 4. Caution: V<sub>DD</sub>/AV<sub>DD</sub> must not exceed OV<sub>DD</sub> by more than 0.4V during normal operation. On power up and power down, V<sub>DD</sub>/AV<sub>DD</sub> is allowed to exceed OV<sub>DD</sub> by up to 1.0V for up to 20 ms, or by up to 0.7V for 40 ms. Excursions beyond 40 ms or 1.0V are not allowed.

#### **Recommended Operating Conditions**

| Characteristic                                | Symbol                   | Value          | Unit | Notes |

|-----------------------------------------------|--------------------------|----------------|------|-------|

| Core supply voltage                           | V <sub>DD</sub>          | 2.0 nominal    | V    | 1, 2  |

| PLL supply voltage                            | $AV_{\mathtt{DD}}$       | $V_{DD}$       | V    | 1     |

| L2DLL supply voltage                          | L2AV <sub>DD</sub>       | $V_{DD}$       | V    | 1     |

| 60x bus supply voltage, pin W1 tied high      | OV <sub>DD(3.3V)</sub>   | 3.135 to 3.465 | V    | 1     |

| 60x bus supply voltage pin W1 tied to HRESET  | OV <sub>DD(2.5V)</sub>   | 2.375 to 2.625 | V    | 1     |

| 60x bus supply voltage, pin W1 tied to GND    | $OV_{DD(1.8V)}$          | 1.71 to 1.89   | V    | 1     |

| L2 bus supply voltage, pin A19 tied high      | L2OV <sub>DD(3.3V)</sub> | 3.135 to 3.465 | V    | 1     |

| L2 bus supply voltage, pin A19 tied to HRESET | L2OV <sub>DD(2.5V)</sub> | 2.375 to 2.625 | V    | 1     |

- 1. These are recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2. V<sub>DD</sub> and T<sub>J</sub> are specified by the Application Conditions designator in the part number. See the Part Number Key on Page 43 for more information.

# PowerPC 740 and PowerPC 750 Microprocessor CMOS 0.20 $\mu$ m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

#### **Recommended Operating Conditions**

| Characteristic                                              | Symbol                   | Value                     | Unit | Notes |

|-------------------------------------------------------------|--------------------------|---------------------------|------|-------|

| L2 bus supply voltage, pin A19 tied to GND                  | L2OV <sub>DD(1.8V)</sub> | 1.71 to 1.89              | V    | 1     |

| Input voltage (Under AC conditions, inputs must go rail-to- | V <sub>IN(60X)</sub>     | GND to OV <sub>DD</sub>   | V    | 1     |

| rail for maximum AC timing performance.)                    | $V_{IN(L2)}$             | GND to L2OV <sub>DD</sub> | V    | 1     |

| Die-junction temperature                                    | TJ                       | -40 to 105                | °C   | 1, 2  |

#### Note:

- 1. These are recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2.  $V_{DD}$  and  $T_J$  are specified by the Application Conditions designator in the part number. See the Part Number Key on Page 43 for more information.

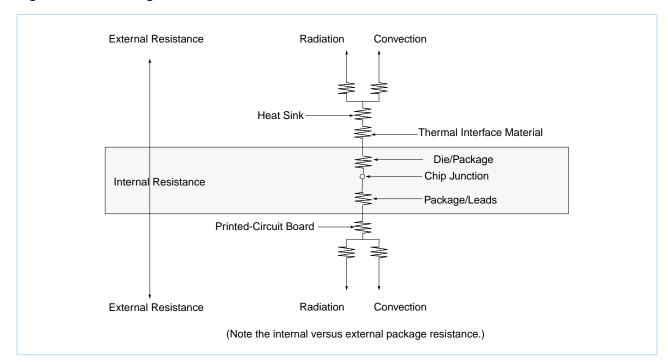

# Package Thermal Characteristics<sup>1</sup>

| Characteristic                                                    | Symbol                | 740                    | 750                    | Unit            |

|-------------------------------------------------------------------|-----------------------|------------------------|------------------------|-----------------|

| Thermal resistance, junction-to-case (top surface of die) typical | $\theta_{	extsf{JC}}$ | 0.03                   | 0.03                   | °C/W            |

| Thermal resistance, junction-to-balls, typical                    | $\theta_{JB}$         | 3.8 - 7.1 <sup>2</sup> | 3.8 - 7.6 <sup>2</sup> | °C/W            |

| Thermal resistance, junction-to-ambient, at air-                  | 50 FPM                | 16.0                   | 15.1                   | °C/W            |

| flow, no heat sink, typical                                       | 100 FPM               | 15.4                   | 16.4                   | °C/W            |

|                                                                   | 150 FPM               | 14.9                   | 14.2                   | °C/W            |

|                                                                   | 200 FPM               | 14.4                   | 13.7                   | °C/W            |

| Package Size                                                      |                       | 21 x 21                | 25 x 25                | mm <sup>2</sup> |

| Die Size                                                          |                       | 5.12 x 7.78            | 5.12 x 7.78            | mm <sup>2</sup> |

#### Note:

- 1. Refer to Section "Thermal Management Information," on page 42 for more information about thermal management.

- 3.8 °C/W is theoretical θ<sub>jg</sub> mounted to infinite heat sink. The larger number applies to module mounted to a 1.8 mm thick, 2P card using 1 oz. copper power/gnd planes, with effective area for heat transfer of 75mm x 75mm.

The 750 incorporates a thermal management assist unit (TAU) composed of a thermal sensor, digital-to-analog converter, comparator, control logic, and dedicated special-purpose registers (SPRs). See the *PowerPC 740 and PowerPC 750 User's Manual* for more information on the use of this feature. Specifications for the thermal sensor portion of the TAU are found in the table below.

#### **Thermal Sensor Specifications**

See System Design Section.

#### **DC Electrical Specifications**

See Section "Recommended Operating Conditions," on page 9, for operating conditions.

| Characteristic                                            | Symbol                  | Min  | Max   | Unit | Notes |

|-----------------------------------------------------------|-------------------------|------|-------|------|-------|

| Input high voltage (all inputs except SYSCLK)             | V <sub>IH(3.3V)</sub>   | 2.0  | 3.465 | V    | 1,2   |

|                                                           | V <sub>IH(2.5V)</sub>   | 1.75 | 2.625 |      |       |

|                                                           | V <sub>IH()1.8V</sub>   | 1.4  | 1.89  |      |       |

| Input low voltage (all inputs except SYSCLK)              | V <sub>IL(3.3V)</sub>   | GND  | 0.8   | V    |       |

|                                                           | V <sub>IL(2.5V)</sub>   | GND  | 0.7   |      |       |

|                                                           | V <sub>IL()1.8V</sub>   | GND  | 0.5   |      |       |

| SYSCLK input high voltage                                 | CV <sub>IH(3.3V)</sub>  | 2.0  | 3.465 | V    | 1, 4  |

|                                                           | CV <sub>IH(2.5V)</sub>  | 2.0  | 2.625 |      |       |

|                                                           | CV <sub>IH(1.8V)</sub>  | 1.5  | 1.89  |      |       |

| SYSCLK input low voltage                                  | CV <sub>IL</sub>        | -    | 0.4   | V    | 4     |

| Input leakage current, V <sub>IN</sub> = OV <sub>DD</sub> | I <sub>IN</sub>         | _    | 20    | μΑ   | 1,2   |

| Hi-Z (off state) leakage current, Vin = OV <sub>DD</sub>  | I <sub>TSI</sub>        | _    | 20    | μΑ   | 1,2   |

| Output high voltage, I <sub>OH</sub> = -6mA               | V <sub>OH(3.3V)</sub>   | 2.4  | -     | V    |       |

| Output high voltage, I <sub>OH</sub> = -6mA               | V <sub>OH((2.5V))</sub> | 1.9  | -     | V    |       |

| Output high voltage, I <sub>OH</sub> = -3mA               | V <sub>OH(1.8V)</sub>   | 1.4  | -     | V    |       |

| Output low voltage, I <sub>OL</sub> = 6mA                 | V <sub>oL</sub>         | _    | 0.4   | V    |       |

| Capacitance, V <sub>IN</sub> =0 V, f = 1MHz               | C <sub>IN</sub>         | _    | 5.0   | pF   | 2,3   |

<sup>1.</sup> For 60x bus signals, the reference is  $OV_{DD}$ , while  $L2OV_{DD}$  is the reference for the L2 bus signals.

JTAG port signal levels are controlled by the BVSEL pin and are the same as those shown for the 60x bus. LSSD\_MODE, L1\_TSTCLK, and L2TSTCLK receiver voltage levels are those shown for OVdd = 1.8V nominal, regardless of BVSEL. JTAG, LSSD\_MODE, L1\_TSTCLK, and L2TSTCLK values in this table are guaranteed by design and characterization, and are not tested.

<sup>3.</sup> Capacitance values are guaranteed by design and characterization, and are not tested.

<sup>4.</sup> SYSCLK input high and low voltage: I/O timings are measured using a "rail to rail" SYSCLK; I/O timing may be less favorable if SYSCLK does not travel from GND to OV<sub>DD</sub>.

#### PowerPC 740 and PowerPC 750 Microprocessor CMOS 0.20 $\mu$ m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

#### Power Consumption for 740 and 750

See Table "Recommended Operating Conditions," on page 9, for operating conditions

|              |                   | Actual Processor CPU Frequency |     |     |     |     |     |     |        | Unit   | Notes |    |       |

|--------------|-------------------|--------------------------------|-----|-----|-----|-----|-----|-----|--------|--------|-------|----|-------|

|              | 300               | 333                            | 350 | 366 | 375 | 400 | 433 | 466 | 500(A) | 500(C) | 533   |    |       |

| Full-On Mode | -<br>Full-On Mode |                                |     |     |     |     |     |     |        |        |       |    |       |

| Typical      | 3.7               | 4.0                            | 4.1 | 4.3 | 4.4 | 4.5 | 5.0 | 5.5 | 6.0    |        |       | W  | 1,3,4 |

| Maximum      | 4.5               | 5.0                            | 5.2 | 5.5 | 5.7 | 6.0 | 6.3 | 6.8 | 7.5    |        |       | W  | 1,2,4 |

| Doze Mode    |                   |                                |     |     |     |     |     |     |        |        |       |    |       |

| Maximum      | 1.7               | 1.7                            | 1.7 | 1.8 | 1.8 | 1.9 | 2.1 | 2.2 | 2.3    |        |       | W  | 1,2,4 |

| Nap Mode     |                   |                                |     |     | ,   | ,   |     |     |        |        |       |    | ,     |

| Maximum      | 250               | 250                            | 250 | 250 | 250 | 250 | 250 | 250 | 250    |        |       | mW | 1, 4  |

| Sleep Mode   |                   |                                |     |     |     |     |     |     |        |        |       |    |       |

| Maximum      | TBD               | TBD                            | TBD | TBD | TBD | TBD | TBD | TBD | TBD    |        |       | mW | 1, 4  |

- Note:

1. These values apply for all valid 60x bus and L2 bus ratios. The values do not include I/O Supply Power (OV<sub>DD</sub> and L2OV<sub>DD</sub>) or PLL/DLL supply power (AV<sub>DD</sub> and L2AV<sub>DD</sub>). OV<sub>DD</sub> and L2OV<sub>DD</sub> power is system dependent, but is typically <10% of V<sub>DD</sub> power. Worst case power consumption for AV<sub>DD</sub> = 15mW and L2AV<sub>DD</sub> = 15mW.

2. Maximum power is shown for a system executing worst case benchmark sequences at:

V<sub>DD</sub> = AV<sub>DD</sub> = L2AV<sub>DD</sub> = 2.1V (300 through 500 MHz);

V<sub>DD</sub> = AV<sub>DD</sub> = L2AV<sub>DD</sub> = 2.15V (533 MHz);

OV<sub>DD</sub> = L2OV<sub>DD</sub> = 3.3V;

T<sub>1</sub> = 65 °C

Maximum power at 85 °C can be derived by adding 0.1 W to the maximum power shown at 65 °C. Maximum power at 105 °C can be derived by adding the adding the state of the state

- - - Maximum power at 85 °C can be derived by adding 0.1 W to the maximum power shown at 65 °C. Maximum power at 105 °C can be derived by adding 0.3 W to the maximum power shown at 65 °C.

- Ing 0.3 W to the maximum power shown at 65 °C.

3. Typical power is an average value shown for a system executing typical applications and benchmark sequences at:

V<sub>DD</sub> = AV<sub>DD</sub> = L2AV<sub>DD</sub> = 2.0V (300 through 400 MHz);

V<sub>DD</sub> = AV<sub>DD</sub> = L2AV<sub>DD</sub> = 2.05V (433 through 500 MHz);

V<sub>DD</sub> = AV<sub>DD</sub> = L2AV<sub>DD</sub> = 2.1V (533 MHz);

OV<sub>DD</sub> = L2OV<sub>DD</sub> = 3.3V;

T<sub>j</sub> = 45 °C.

- 4. Guaranteed by design and characterization, and is not tested.

A. 500 MHz using the 500A part.

C. 500 MHz using the 500C part.

#### AC Electrical Characteristics

This section provides the AC electrical characteristics for the 750. After fabrication, parts are sorted by maximum processor core frequency as shown in the Section "Clock AC Specifications," on page 13, and tested for conformance to the AC specifications for that frequency. Parts are sold by maximum processor core frequency, subject to the specified application conditions; see Section "Ordering Information," on page 48. Unless otherwise noted, all timings apply for all I/O supply voltages.

## **Clock AC Specifications**

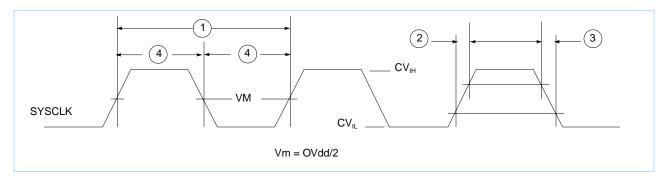

The following table provides the clock AC timing specifications as defined in Figure 2.

## **Clock AC Timing Specifications**

See Table "Recommended Operating Conditions," on page 9, for operating conditions.

| Num | Characteristic                   | Fmax | Fmax = 300-375MHz           |     | ax ≥ 400MHz                 | Unit | Notes |

|-----|----------------------------------|------|-----------------------------|-----|-----------------------------|------|-------|

|     |                                  | Min  | Max                         | Min | Max                         |      |       |

|     | Processor frequency              | TBD  | As specified by part number | 250 | As specified by part number | MHz  | 6     |

|     | SYSCLK frequency                 | 25   | 100                         | 31  | 100                         | MHz  | 1     |

| 1   | SYSCLK cycle time                | 10   | 40                          | 10  | 32                          | ns   |       |

| 2,3 | SYSCLK rise and fall time        | _    | 1.0                         | _   | 1.0                         | ns   | 2,3   |

| 4   | SYSCLK duty cycle measured at Vm | 40   | 60                          | 40  | 60                          | %    | 3     |

|     | SYSCLK jitter                    | _    | ±150                        | _   | ±150                        | ps   | 4,3   |

|     | Internal PLL relock time         | -    | 100                         | -   | 100                         | μs   | 5     |

#### Note:

- Caution: The SYSCLK frequency and the PLL\_CFG[0:3] settings must be chosen such that the resulting SYSCLK (bus) frequency, and CPU (core) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:3] signal description in Section "PLL Configuration," on page 38 for valid PLL\_CFG[0:3] settings. Bus operation above 100 MHz is possible, but requires careful timing analysis. Contact IRM for details

- 2. Rise and fall times for the SYSCLK input are measured from 0.5 to 1.5V.

- 3. Timing is guaranteed by design and characterization, and is not tested.

- 4. The total input jitter (short term and long term combined) must be under ±150ps. Contact IBM for operation with Spread Spectrum clocks or clocks with more than ± 150 ps total jitter.

- 5. Relock timing is guaranteed by design and characterization, and is not tested. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

- 6. Under certain conditions, operation at core frequencies below those stated is possible. Contact IBM for details.

Figure 2. SYSCLK Input Timing Diagram

10/9/2001 Version 1.1 Page 13

## 60x Bus Input AC Specifications

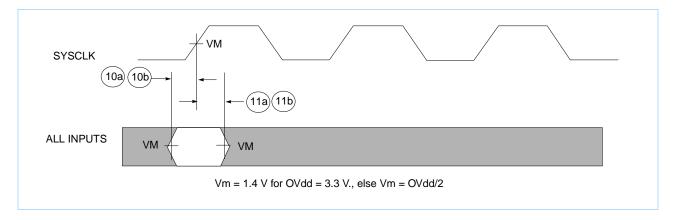

The following table provides the 60X bus input AC timing specifications for the 750 as defined in Figure 3 and Figure 4. Input timing specifications for the L2 bus are provided in Section, "L2 Bus Input AC Specifications" on page 20.

#### 60X Bus Input Timing Specifications<sup>1</sup>

See Table "Recommended Operating Conditions," on page 9, for operating conditions.

| Num | Characteristic                                                        | All Freq | uencies      | Unit                | Notes   |

|-----|-----------------------------------------------------------------------|----------|--------------|---------------------|---------|

|     |                                                                       | Minimum  | Maximum      |                     |         |

| 10a | Address/Data/Transfer Attribute Inputs Valid to SYSCLK (Input Setup)  | 2.5      | <del></del>  | ns                  | 2       |

| 10b | All Other Inputs Valid to SYSCLK (Input Setup)                        | 2.5      | _            | ns                  | 3       |

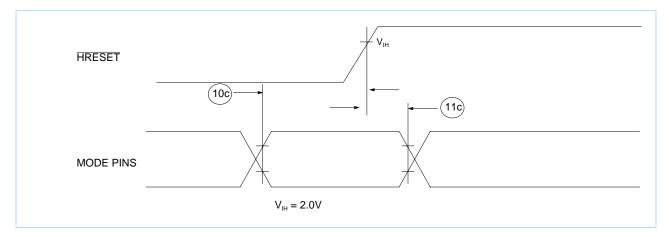

| 10c | Mode Select Input Setup to HRESET (DRTRY, TLBISYNC)                   | 8        | <del>_</del> | t <sub>sysclk</sub> | 4,5,6,7 |

| 11a | SYSCLK to Address/Data/Transfer Attribute Inputs Invalid (Input Hold) | 0.6      | _            | ns                  | 2       |

| 11b | SYSCLK to All Other Inputs Invalid (Input Hold)                       | 0.6      | _            | ns                  | 3       |

| 11c | HRESET to mode select input hold (DRTRY, TLBISYNC)                    | 0        | _            | ns                  | 4,6,7   |

- 1. Input specifications are measured from the Vm of the signal in question to the Vm of the rising edge of the input SYSCLK. Input and output timings are measured at the pin (see Figure 3).

- 2. Address/Data Transfer Attribute inputs are composed of the following-A[0:31], AP[0:3], TT[0:4], TBST, TSIZ[0:2], GBL, DH[0:31], DL[0:31], DP[0:7].

- 3. All other signal inputs are composed of the following–TS, ABB, DBB, ARTRY, BG, AACK, DBG, DBWO, TA, DRTRY, TEA, DBDIS, TBEN, QACK, TLBISYNC.

- 4. The setup and hold time is with respect to the rising edge of HRESET (see Figure 4).

- t<sub>SYSCLK</sub>, is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 6. These values are guaranteed by design, and are not tested.

- 7. This specification is for configuration mode select only. Also note that the HRESET must be held asserted for a **minimum of 255 bus clocks** after the PLL re-lock time during the power-on reset sequence.

Figure 3. Input Timing Diagram

Figure 4. Mode Select Input Timing Diagram

10/9/2001 Version 1.1 Page 15

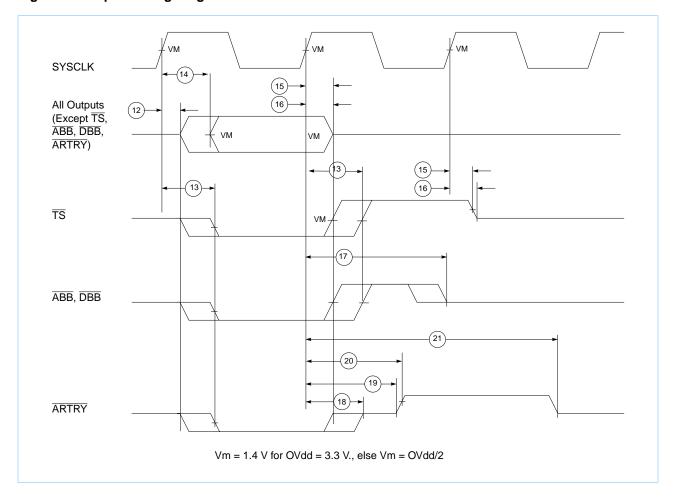

# 60x Bus Output AC Specifications

The following table provides the 60x bus output AC timing specifications for the 750 as defined in Figure 5. Output timing specification for the L2 bus are provided in the Section "L2 Bus Output AC Specifications," on page 21.

#### 60X Bus Output AC Timing Specifications for the 7501

See Table "Recommended Operating Conditions," on page 9 for operating conditions,  $C_L = 50 pF^2$

| Num | Characteristic                                                                                                     | All Freq                      | uencies | Unit                | Notes   |

|-----|--------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|---------------------|---------|

|     |                                                                                                                    | Minimum                       | Maximum |                     |         |

| 12  | SYSCLK to Output Driven (Output Enable Time)                                                                       | 0.5                           |         | ns                  | 8       |

| 13  | SYSCLK to Output Valid (TS, ABB, ARTRY, DBB, and TBST)                                                             | -                             | 4.5     | ns                  | 5       |

| 14  | SYSCLK to all other Output Valid (all except TS, ABB, ARTRY, DBB, and TBST)                                        | _                             | 5.0     | ns                  | 5       |

| 15  | SYSCLK to Output Invalid (Output Hold)                                                                             | 1.0                           |         | ns                  | 3, 8, 9 |

| 16  | SYSCLK to Output High Impedance (all signals except $\overline{ABB}$ , $\overline{ARTRY}$ , and $\overline{DBB}$ ) | _                             | 6.0     | ns                  | 8       |

| 17  | SYSCLK to ABB and DBB high impedance after precharge                                                               | -                             | 1.0     | t <sub>sysclk</sub> | 4, 6, 8 |

| 18  | SYSCLK to ARTRY high impedance before precharge                                                                    | -                             | 5.5     | ns                  | 8       |

| 19  | SYSCLK to ARTRY precharge enable                                                                                   | 0.2×t <sub>SYSCLK</sub> + 1.0 |         | ns                  | 3, 4, 7 |

| 20  | Maximum delay to ARTRY precharge                                                                                   |                               | 1       | t <sub>SYSCLK</sub> | 4, 7    |

| 21  | SYSCLK to ARTRY high impedance after precharge                                                                     |                               | 2       | t <sub>sysclk</sub> | 4, 7, 8 |

- 1. All output specifications are measured from Vm of the rising edge of SYSCLK to Vm of the signal in question. Both input and output timings are measured at the pin.

- 2. All maximum timing specifications assume  $C_L = 50 pF$ .

- 3. This minimum parameter assumes CL = 0pF.

- 4. t<sub>SYSCLK</sub> is the period of the external bus clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration of the parameter in question.

- 5. This footnote has been deleted.

- 6. Nominal precharge width for  $\overline{ABB}$  and  $\overline{DBB}$  is 0.5  $t_{SYSCLK}$ .

- 7. Nominal precharge width for  $\overline{\text{ARTRY}}$  is 1.0  $t_{\text{SYSCLK}}$ .

- 8. Guaranteed by design and characterization, and not tested.

- Connecting L2\_TSTCLK to GND no longer provides additional Output Hold. For new designs, L2\_TSTCLK should be pulled up to OVdd, but it can be left connected to GND in Legacy systems.

Figure 5. Output Timing Diagram

PowerPC 740 and PowerPC 750 Microprocessor CMOS 0.20  $\mu$ m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

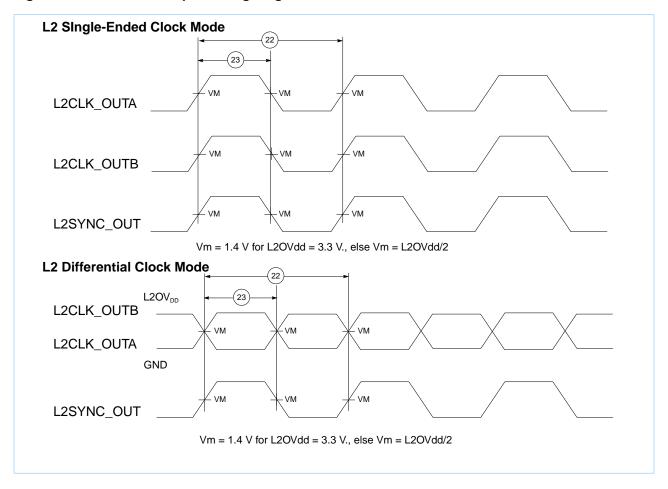

#### L2 Clock AC Specifications

The following table provides the L2CLK output AC timing specifications for the 750 as defined in Figure 6.

#### **L2CLK Output AC Timing Specifications**

See Table "Recommended Operating Conditions," on page 9, for operating conditions.

| Num | Characteristic           | Min | Max  | Unit  | Notes |

|-----|--------------------------|-----|------|-------|-------|

|     | L2CLK frequency          | 80  | 250  | MHz   | 1, 5  |

| 22  | L2CLK cycle time         | 4.0 | 12.5 | ns    |       |

| 23  | L2CLK duty cycle         | 5   | 0    | %     | 2     |

|     | Internal DLL-relock time | 640 | _    | L2CLK | 4     |

|     | L2CLK jitter             |     | ±150 | ps    | 3, 6  |

|     | L2CLK skew               |     | 0    | ps    | 7     |

- L2CLK outputs are L2CLKOUTA, L2CLKOUTB and L2SYNC\_OUT pins. The internal design supports higher L2CLK frequencies. Consult IBM PowerPC Application Engineering (ppcsupp@us.ibm.com) before operating the L2 SRAMs above 250 MHz. The L2CLK frequency to core frequency settings must be chosen such that the resulting L2CLK frequency and core frequency do not exceed their respective maximum or minimum operating frequencies. L2CLKOUTA and L2CLKOUTB must have equal loading.

- 2. The nominal duty cycle of the L2CLK is 50% measured at midpoint voltage.

- 3. The major component of L2CLK jitter is passed through from SYSCLK. While SYSCLK jitter is less then ±150 ps, L2CLK jitter is also less than ±150 ps. SYSCLK jitter in excess of ±150 ps causes L2CLK jitter to exceed ±150 ps.

- 4. The DLL re-lock time is specified in terms of L2CLKs. The number in the table must be multiplied by the period of L2CLK to compute the actual time duration in nanoseconds. Re-lock timing is guaranteed by design and characterization, and is not tested.

- 5. The L2CR [L2SL] bit should be set for L2CLK frequencies less than 110MHz.

- 6. Guaranteed by design and characterization, not tested

- 7. Skew between the L2 output clocks is included in the other timing specs.

Figure 6. L2CLK\_OUT Output Timing Diagram

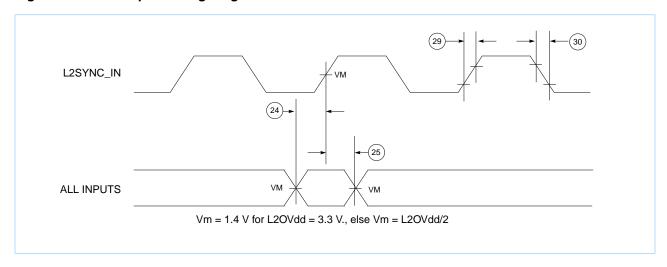

# **L2 Bus Input AC Specifications**

Some specifications are shown in the following table as a Function of Maximum Core Frequency (Fmax). These specifications refer to the effective Fmax of the part after derating for application conditions. For example, a nominal 450 MHz part running at application conditions that derate its Fmax to 400 MHz will meet or exceed the specifications shown for Fmax = 400 MHz.

#### L2 Bus Input Interface AC Timing Specifications

See Table "Recommended Operating Conditions," on page 9, for operating conditions.

| Num   | Characteristic                                                     | Min | Max | Unit | Notes |

|-------|--------------------------------------------------------------------|-----|-----|------|-------|

| 29,30 | L2SYNC_IN rise and fall time                                       | _   | 1.0 | ns   | 2,3   |

| 24    | Data and parity input setup to L2SYNC_IN, Fmax up through 375 MHz. | 1.5 | _   | ns   | 1     |

| 24    | Data and parity input setup to L2SYNC_IN, Fmax = 400 MHz.          | 1.4 | _   | ns   | 1     |

| 24    | Data and parity input setup to L2SYNC_IN, Fmax = 433 and 450 MHz.  | 1.1 | _   | ns   | 1     |

| 24    | Data and parity input setup to L2SYNC_IN, Fmax = 466 and 500 MHz.  | 1.0 | _   | ns   | 1     |

| 25    | L2SYNC_IN to data and parity input hold                            | 0.5 | _   | ns   | 1     |

Figure 7. L2 Bus Input Timing Diagrams

<sup>1.</sup> All input specifications are measured from the Vm of the signal in question to the Vm of the rising edge of the input L2SYNC\_IN. Input timings are measured at the pins (see Figure 7).

<sup>2.</sup> Rise and fall times for the L2SYNC\_IN input are measured from 0.5 to 1.5V.

<sup>3.</sup> Guaranteed by design and characterization, and not tested.

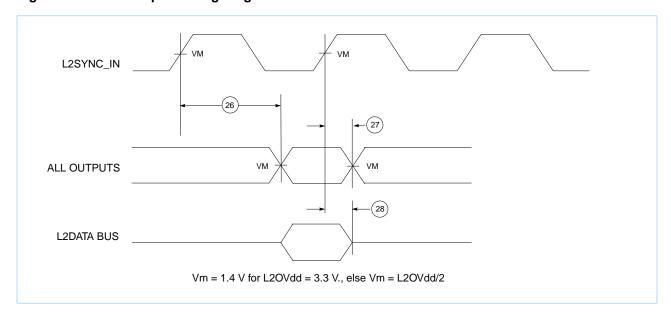

# **L2 Bus Output AC Specifications**

#### L2 Bus Output Interface AC Timing Specifications<sup>1</sup>

See Table "Recommended Operating Conditions," on page 9 for operating conditions,  $C_L = 20 pF^3$

| Num | Characteristic                                                   | L2CR[14:15] is equivalent to: |                 |     |     |                  |                  | Unit             | Notes            |    |     |

|-----|------------------------------------------------------------------|-------------------------------|-----------------|-----|-----|------------------|------------------|------------------|------------------|----|-----|

|     |                                                                  |                               | 00 <sup>2</sup> |     | 01  |                  | 10               |                  | 11               |    |     |

|     |                                                                  | Min                           | Max             | Min | Max | Min              | Max              | Min              | Max              |    |     |

| 26  | L2SYNC_IN to output valid, Fmax <sup>7</sup> up through 375 MHz. | _                             | 3.2             | _   | 3.7 | _                | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | ns |     |

| 26  | L2SYNC_IN to output valid, Fmax = 400 MHz.                       | _                             | 3.0             | _   | 3.5 | _                | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | ns |     |

| 26  | L2SYNC_IN to output valid, Fmax = 433 and 450 MHz.               | _                             | 2.6             | _   | 3.1 | _                | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | ns |     |

| 26  | L2SYNC_IN to output valid, Fmax = 466 and 500 MHz.               | _                             | 2.4             | _   | 2.9 | _                | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | ns |     |

| 27  | L2SYNC_IN to output hold                                         | 0.5                           | _               | 1.0 | _   | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | _                | ns | 4,6 |

| 28  | L2SYNC_IN to high impedance                                      | _                             | 3.5             | _   | 4.0 | _                | Rsv <sup>5</sup> | _                | Rsv <sup>5</sup> | ns | 6   |

- 1. All outputs are measured from the Vm of the rising edge of L2SYNC\_IN to the Vm of the signal in question. The output timings are measured at the pins (see Figure 8).

- The outputs are valid for both single-ended and differential L2CLK modes. For flow-through and pipelined reg-reg synchronous burst SRAMs, L2CR[14:15] = 00 is recommended. For pipelined late-write synchronous burst SRAMs, L2CR[14:15] = 01 is recommended.

- 3. All maximum timing specifications assume CL = 20pF.

- 4. This measurement assumes CL= 5pF.

- Reserved for future use.

- 6. Guaranteed by design and characterization, and not tested.

- Specifications are shown as a Function of Maximum Core Frequency (Fmax). They refer to the effective Fmax of the part after derating for application conditions. For example, a nominal 450 MHz part running at application conditions that derate its Fmax to 400 MHz will meet or exceed the specifications shown for Fmax = 400 MHz.

Figure 8. L2 Bus Output Timing Diagrams

# **IEEE 1149.1 AC Timing Specifications**

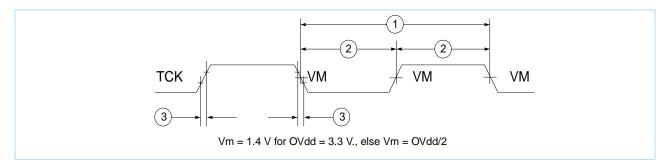

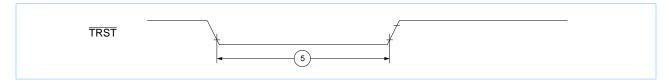

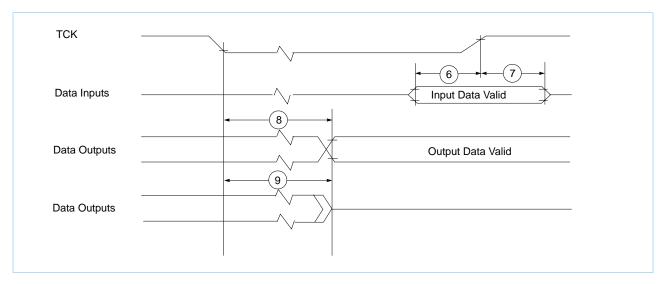

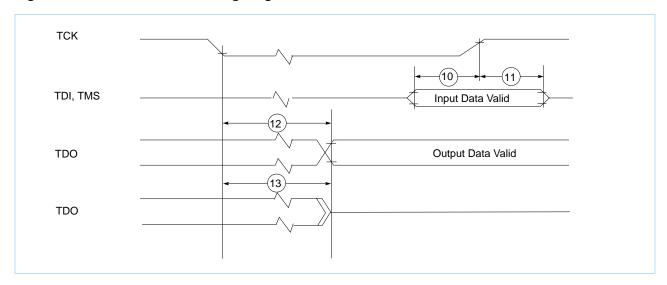

The table below provides the IEEE 1149.1 (JTAG) AC timing specifications as defined in Figure 9, Figure 10, Figure 11, and Figure 12. The five JTAG signals are; TDI, TDO, TMS, TCK, and TRST.

#### JTAG AC Timing Specifications (Independent of SYSCLK)

See Table "Recommended Operating Conditions," on page 9 for operating conditions,  $C_L = 50 pF$ .

| Num | Characteristic                         | Min | Max | Unit | Notes |

|-----|----------------------------------------|-----|-----|------|-------|

|     | TCK frequency of operation             | 0   | 25  | MHz  |       |

| 1   | TCK cycle time                         | 40  | _   | ns   |       |

| 2   | TCK clock pulse width measured at 1.4V | 15  | _   | ns   |       |

| 3   | TCK rise and fall times                | 0   | 2   | ns   | 4     |

| 4   | spec obsolete, intentionally omitted   |     |     |      |       |

| 5   | TRST assert time                       | 25  | _   | ns   | 1     |

| 6   | Boundary-scan input data setup time    | 4   | _   | ns   | 2     |

| 7   | Boundary-scan input data hold time     | 16  | _   | ns   | 2     |

| 8   | TCK to output data valid               | 4   | 20  | ns   | 3, 5  |

| 9   | TCK to output high impedance           | 3   | 19  | ns   | 3, 4  |

| 10  | TMS, TDI data setup time               | 0   | _   | ns   |       |

| 11  | TMS, TDI data hold time                | 16  | _   | ns   |       |

| 12  | TCK to TDO data valid                  | 2.5 | 12  | ns   | 5     |

| 13  | TCK to TDO high impedance              | 3   | 9   | ns   | 4     |

- 1. TRST is an asynchronous level sensitive signal. Guaranteed by design.

- 2. Non-JTAG signal input timing with respect to TCK.

- 3. Non-JTAG signal output timing with respect to TCK.

- 4. Guaranteed by characterization and not tested.

- 5. Minimum spec guaranteed by characterization and not tested.

Figure 9. JTAG Clock Input Timing Diagram

Figure 10. TRST Timing Diagram

Figure 11. Boundary-Scan Timing Diagram

Figure 12. Test Access Port Timing Diagram

10/9/2001 Version 1.1 Page 23

# **PowerPC 740 Microprocessor Pin Assignments**

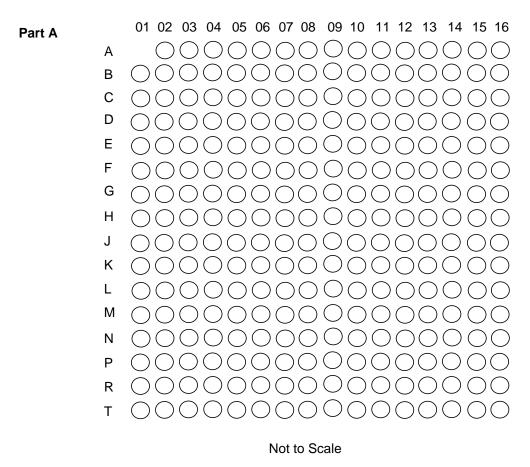

The following sections contain the pinout diagrams for the PowerPC 740, a 255 pin ceramic ball grid array (BGA) package.

Figure 13 (in part A) shows the pinout of the PPC 740, a 255 pin Ceramic Ball Grid Array (CBGA) package as viewed from the top surface. Part B shows the side profile.

Figure 13. Pinout of the PowerPC 740 BGA Package as Viewed from the Top Surface

# **PowerPC 740 Microprocessor Pinout Listings**

#### Pinout Listing for the PowerPC 740 255 CBGA Package

| Signal Name        | Pin Number                                                                                                                                                                                             | Active | I/O    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| A[0:31]            | C16, E04, D13, F02, D14, G01, D15, E02, D16, D04, E13, G02, E15, H01, E16, H02, F13, J01, F14, J02, F15, H03, F16, F04, G13, K01, G15, K02, H16, M01, J15, P01                                         | High   | I/O    |

| AACK               | L02                                                                                                                                                                                                    | Low    | Input  |

| ĀBB                | K04                                                                                                                                                                                                    | Low    | I/O    |

| AP[0:3]            | C01, B04, B03, B02                                                                                                                                                                                     | High   | I/O    |

| ARTRY              | J04                                                                                                                                                                                                    | Low    | I/O    |

| AVDD               | A10                                                                                                                                                                                                    | _      | _      |

| BG                 | L01                                                                                                                                                                                                    | Low    | Input  |

| BR                 | B06                                                                                                                                                                                                    | Low    | Output |

| BVSEL <sup>1</sup> | H04                                                                                                                                                                                                    |        | Input  |

| CI                 | E01                                                                                                                                                                                                    | Low    | Output |

| CKSTP_IN           | D08                                                                                                                                                                                                    | Low    | Input  |

| CKSTP_OUT          | A06                                                                                                                                                                                                    | Low    | Output |

| CLK_OUT            | D07                                                                                                                                                                                                    | _      | Output |

| DBB                | J14                                                                                                                                                                                                    | Low    | I/O    |

| DBG                | N01                                                                                                                                                                                                    | Low    | Input  |

| DBDIS              | H15                                                                                                                                                                                                    | Low    | Input  |

| DBWO               | G04                                                                                                                                                                                                    | Low    | Input  |

| DH[0:31]           | P14, T16, R15, T15, R13, R12, P11, N11, R11, T12, T11, R10, P09, N09, T10, R09, T09, P08, N08, R08, T08, N07, R07, T07, P06, N06, R06, T06, R05, N05, T05, T04                                         | High   | I/O    |

| DL[0:31]           | K13, K15, K16, L16, L15, L13, L14, M16, M15, M13, N16, N15, N13, N14, P16, P15, R16, R14, T14, N10, P13, N12, T13, P03, N03, N04, R03, T01, T02, P04, T03, R04                                         | High   | I/O    |

| DP[0:7]            | M02, L03, N02, L04, R01, P02, M04, R02                                                                                                                                                                 | High   | I/O    |

| DRTRY              | G16                                                                                                                                                                                                    | Low    | Input  |

| GBL                | F01                                                                                                                                                                                                    | Low    | I/O    |

| GND                | C05, C12, E03, E06, E08, E09, E11, E14, F05, F07, F10, F12, G06, G08, G09, G11, H05, H07, H10, H12, J05, J07, J10, J12, K06, K08, K09, K11, L05, L07, L10, L12, M03, M06, M08, M09, M11, M14, P05, P12 | _      | _      |

# PowerPC 740 and PowerPC 750 Microprocessor CMOS 0.20 $\mu m$ Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

# Pinout Listing for the PowerPC 740 255 CBGA Package (cont.)

| Signal Name            | Pin Number                                                                                    | Active | I/O    |

|------------------------|-----------------------------------------------------------------------------------------------|--------|--------|

| HRESET                 | A07                                                                                           | Low    | Input  |

| ĪNT                    | B15                                                                                           | Low    | Input  |

| L1_TSTCLK <sup>2</sup> | D11                                                                                           | High   | Input  |

| L2_TSTCLK <sup>2</sup> | D12                                                                                           | High   | Input  |

| LSSD_MODE 2            | B10                                                                                           | Low    | Input  |

| MCP                    | C13                                                                                           | Low    | Input  |

| NC (No-Connect)        | B07, B08, C03, C06, C08, D05, D06, J16, A04, A05, A02, A03, B01, B05                          | _      | _      |

| OVDD                   | C07, E05, E07, E10, E12, G03, G05, G12, G14, K03, K05, K12, K14, M05, M07, M10, M12, P07, P10 | _      | _      |

| PLL_CFG[0:3]           | A08, B09, A09, D09                                                                            | High   | Input  |

| QACK                   | D03                                                                                           | Low    | Input  |

| QREQ                   | J03                                                                                           | Low    | Output |

| RSRV                   | D01                                                                                           | Low    | Output |

| SMI                    | A16                                                                                           | Low    | Input  |

| SRESET                 | B14                                                                                           | Low    | Input  |

| SYSCLK                 | C09                                                                                           | _      | Input  |

| TA                     | H14                                                                                           | Low    | Input  |

| TBEN                   | C02                                                                                           | High   | Input  |

| TBST                   | A14                                                                                           | Low    | I/O    |

| TCK                    | C11                                                                                           | High   | Input  |

| TDI                    | A11                                                                                           | High   | Input  |

| TDO                    | A12                                                                                           | High   | Output |

| TEA                    | H13                                                                                           | Low    | Input  |

| TLBISYNC               | C04                                                                                           | Low    | Input  |

| TMS                    | B11                                                                                           | High   | Input  |

| TRST                   | C10                                                                                           | Low    | Input  |

| TS                     | J13                                                                                           | Low    | I/O    |

| TSIZ[0:2]              | A13, D10, B12,                                                                                | High   | Output |

| TT[0:4]                | B13, A15, B16, C14, C15                                                                       | High   | I/O    |

| WT                     | D02                                                                                           | Low    | Output |

#### Pinout Listing for the PowerPC 740 255 CBGA Package (cont.)

| Signal Name          | Pin Number                                                                                         | Active | I/O    |

|----------------------|----------------------------------------------------------------------------------------------------|--------|--------|

| VDD <sup>3</sup>     | F06, F08, F09, F11, G07, G10, H06, H08, H09, H11, J06, J08, J09, J11, K07, K10, L06, L08, L09, L11 | _      | _      |

| VOLTDET <sup>4</sup> | F03                                                                                                | Low    | Output |

#### Note:

#### 1. BVSEL Function

| Unconnected or Pulled to OVdd (3.3V nominal) | OVdd = 3.3 V nominal |

|----------------------------------------------|----------------------|

| Connected to HRESET                          | OVdd = 2.5 V nominal |

| Connected to GND                             | OVdd = 1.8 V nominal |

If BVSEL is connected to GND with a series resistor, the resistor value must be 10  $\Omega$  or less.

- 2. These are test signals for factory use only and must be pulled up to OVdd for normal operation.

- 3. OVdd inputs supply power to the I/O drivers and Vdd inputs supply power to the processor core.

- 4. Internally tied to GND in the 255 CBGA package. This is NOT a supply pin.

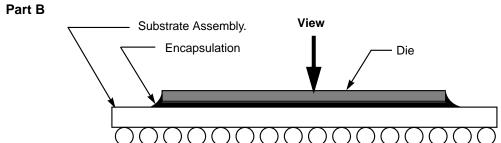

# PowerPC 740 Package

Package Type Ceramic Ball Grid Array (CBGA)

Package outline 21 x 21mm

Interconnects 255 (16 x 16 ball array - 1)

Pitch 1.27mm (50mil)

Minimum module height 2.45mm

Maximum module height 3.00mm

Ball diameter 0.89mm (35mil)

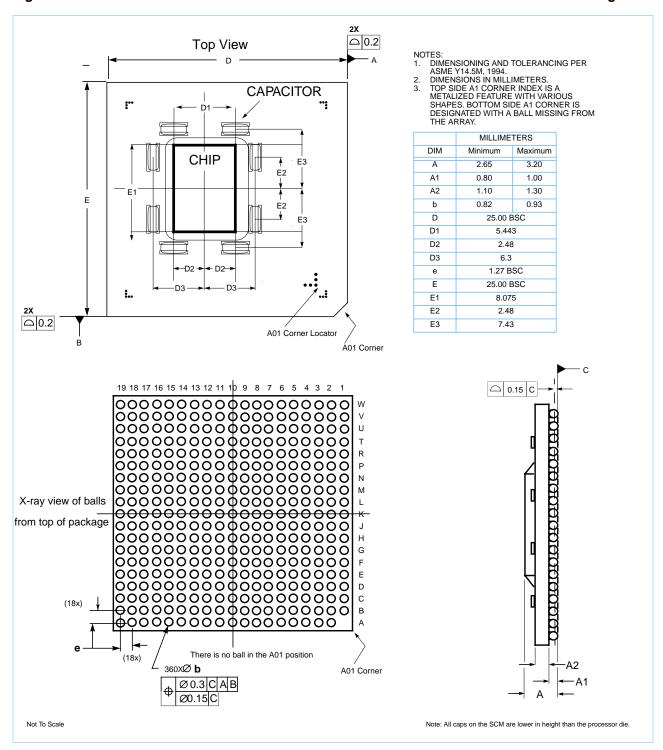

# Mechanical Dimensions of the PowerPC 740 255 CBGA Package

Figure 14. Mechanical Dimensions and Bottom Surface Nomenclature of the 255 CBGA **Package**

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. DIMENSIONS IN MILLIMETERS.

- DIMENSIONS IN MILLINE TERS.

TOP SIDE A1 CORNER INDEX IS A

METALIZED FEATURE WITH VARIOUS

SHAPES. BOTTOM SIDE A1 CORNER IS

DESIGNATED WITH A BALL MISSING FROM

|            | MILLIME | TERS |               |

|------------|---------|------|---------------|

| DIM        | MIN     | MAX  |               |

| Α          | 2.45    | 3.00 |               |

| <b>A</b> 1 | 0.80    | 1.00 |               |

| A2         | 0.90    | 1.10 |               |

| b          | 0.82    | 0.93 |               |

| D          | 21.00   | BSC  |               |

| D1         | 5.443   |      |               |

| е          |         | BSC  |               |

| Е          |         | BSC  |               |

| E1         | 8.075   | BSC  | C             |

|            |         | 0.15 | C             |

|            |         | 0.10 | <u> </u>      |

|            |         |      | $\Box$ \      |

|            |         |      | ΙĽ            |

|            |         |      | 1 D           |

|            |         |      | 1 H3          |

|            |         |      | <i>l</i> 🛱    |

|            |         | - 4  | 4 14          |

|            |         |      |               |

|            |         |      | 1 Fl          |

|            |         |      | 1 🖽           |

|            |         |      | 1 D           |

|            |         |      | 1 H           |

|            |         |      | 1 🖺           |

|            |         |      | 1 (2)         |

|            |         |      | 1 h           |

|            |         |      | 💢             |

|            |         |      | Iβ            |

|            |         | I    | I <b>I</b> '' |

|            |         | Ļ    | <b>∃</b> 🛱    |

|            |         |      | <b>V</b> P4   |

|            |         |      | 1 b'          |

|            |         |      | 🛱             |

|            |         |      | I HA          |

|            |         |      | l bi          |

|            |         |      | $\Box$        |

|            |         |      |               |

|            |         | _ l, | J L A2        |

|            |         | T    | AZ            |

|            |         |      | →   ← A1      |

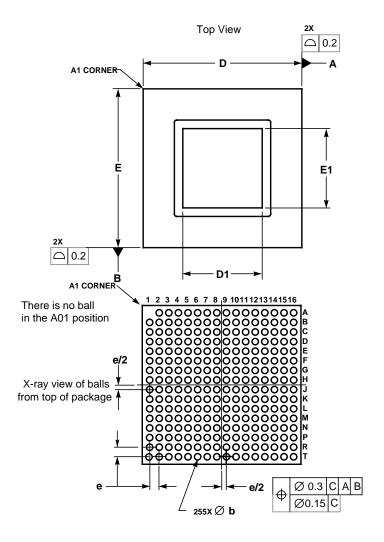

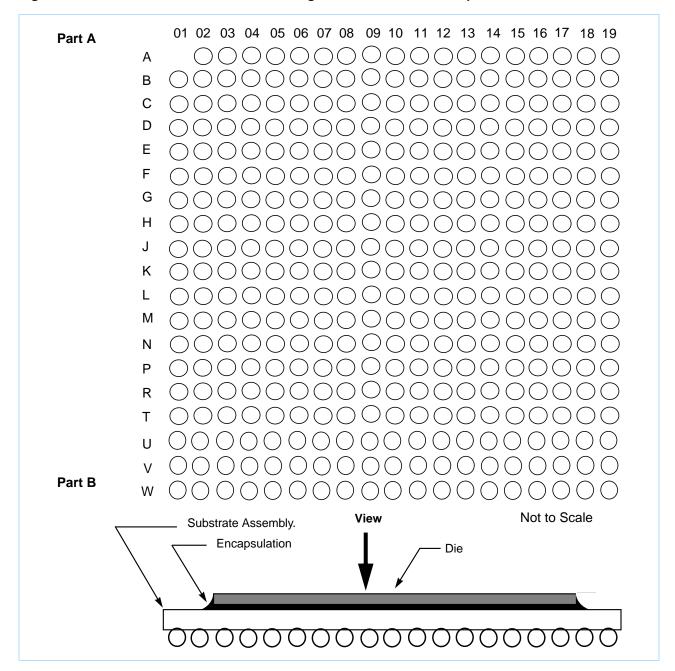

# **PowerPC 750 Microprocessor Pin Assignments**

The following sections contain the pinout diagrams for the PowerPC 750 ceramic ball grid array 360 CBGA packages.

Figure 15 (in part A) shows the pinout of the 360 CBGA package as viewed from the top surface. Part B shows the side profile of the 360 CBGA package to indicate the direction of the top surface view.

Figure 15. Pinout of the 750 360 CBGA Package as Viewed from the Top Surface

# Pinout Listing for the PowerPC 750 360 CBGA package

| Signal Name            | Pin Number                                                                                                                                                                                                                     | Active | I/O    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| A[0:31]                | A13, D2, H11, C1, B13, F2, C13, E5, D13, G7, F12, G3, G6, H2, E2, L3, G5, L4, G4, J4, H7, E1, G2, F3, J7, M3, H3, J2, J6, K3, K2, L2                                                                                           | High   | I/O    |

| AACK                   | N3                                                                                                                                                                                                                             | Low    | Input  |

| ABB                    | L7                                                                                                                                                                                                                             | Low    | I/O    |

| AP[0:3]                | C4, C5, C6, C7                                                                                                                                                                                                                 | High   | I/O    |

| ARTRY                  | L6                                                                                                                                                                                                                             | Low    | I/O    |

| AVDD <sup>1</sup>      | A8                                                                                                                                                                                                                             | _      | _      |

| BG                     | H1                                                                                                                                                                                                                             | Low    | Input  |

| BR                     | E7                                                                                                                                                                                                                             | Low    | Output |

| BVSEL <sup>2</sup>     | W01 <sup>2</sup>                                                                                                                                                                                                               | _      | Input  |

| CKSTP_OUT              | D7                                                                                                                                                                                                                             | Low    | Output |

| CI                     | C2                                                                                                                                                                                                                             | Low    | Output |

| CKSTP_IN               | B8                                                                                                                                                                                                                             | Low    | Input  |

| CLKOUT                 | E3                                                                                                                                                                                                                             | _      | Output |

| DBB                    | K5                                                                                                                                                                                                                             | Low    | I/O    |

| DBDIS                  | G1                                                                                                                                                                                                                             | Low    | Input  |

| DBG                    | K1                                                                                                                                                                                                                             | Low    | Input  |

| DBWO                   | D1                                                                                                                                                                                                                             | Low    | Input  |

| DH[0:31]               | W12, W11, V11, T9, W10, U9, U10, M11, M9, P8, W7, P9, W9, R10, W6, V7, V6, U8, V9, T7, U7, R7, U6, W5, U5, W4, P7, V5, V4, W3, U4, R5                                                                                          | High   | I/O    |

| DL[0:31]               | M6, P3, N4, N5, R3, M7, T2, N6, U2, N7, P11, V13, U12, P12, T13, W13, U13, V10, W8, T11, U11, V12, V8, T1, P1, V1, U1, N1, R2, V3, U3, W2                                                                                      | High   | I/O    |

| DP[0:7]                | L1, P2, M2, V2, M1, N2, T3, R1                                                                                                                                                                                                 | High   | I/O    |

| DRTRY                  | H6                                                                                                                                                                                                                             | Low    | Input  |

| GBL                    | B1                                                                                                                                                                                                                             | Low    | I/O    |

| GND                    | D10, D14, D16, D4, D6, E12, E8, F4, F6, F10, F14, F16, G9, G11, H5, H8, H10, H12, H15, J9, J11, K4, K6, K8, K10, K12, K14, K16, L9, L11, M5, M8, M10, M12, M15, N9, N11, P4, P6, P10, P14, P16, R8, R12, T4, T6, T10, T14, T16 | _      | _      |

| HRESET                 | B6                                                                                                                                                                                                                             | Low    | Input  |

| INT                    | C11                                                                                                                                                                                                                            | Low    | Input  |

| L1_TSTCLK <sup>3</sup> | F8                                                                                                                                                                                                                             | High   | Input  |

| L2ADDR[0:16]           | L17, L18, L19, M19, K18, K17, K15, J19, J18, J17, J16, H18, H17, J14, J13, H19, G18                                                                                                                                            | High   | Output |

| L2AVDD                 | L13                                                                                                                                                                                                                            | _      | _      |

| L2CE                   | P17                                                                                                                                                                                                                            | Low    | Output |

| L2CLKOUTA              | N15                                                                                                                                                                                                                            | _      | Output |

# PowerPC 740 and PowerPC 750 Microprocessor CMOS 0.20 $\mu m$ Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

# Pinout Listing for the PowerPC 750 360 CBGA package (cont.)

| Signal Name            | Pin Number                                                                                                                                                                                                                                                                                                                     | Active | I/O    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| L2CLKOUTB              | L16                                                                                                                                                                                                                                                                                                                            | _      | Output |

| L2DATA[0:63]           | U14, R13, W14, W15, V15, U15, W16, V16, W17, V17, U17, W18, V18, U18, V19, U19, T18, T17, R19, R18, R17, R15, P19, P18, P13, N14, N13, N19, N17, M17, M13, M18, H13, G19, G16, G15, G14, G13, F19, F18, F13, E19, E18, E17, E15, D19, D18, D17, C18, C17, B19, B18, B17, A18, A17, A16, B16, C16, A14, A15, C15, B14, C14, E13 | High   | I/O    |

| L2DP[0:7]              | V14, U16, T19, N18, H14, F17, C19, B15                                                                                                                                                                                                                                                                                         | High   | I/O    |

| L2OVDD                 | D15, E14, E16, H16, J15, L15, M16, P15, R14, R16, T15, F15                                                                                                                                                                                                                                                                     | _      | _      |

| L2SYNC_IN              | L14                                                                                                                                                                                                                                                                                                                            | _      | Input  |

| L2SYNC_OUT             | M14                                                                                                                                                                                                                                                                                                                            | _      | Output |

| L2_TSTCLK <sup>3</sup> | F7                                                                                                                                                                                                                                                                                                                             | High   | Input  |

| L2VSEL                 | A19 <sup>2</sup>                                                                                                                                                                                                                                                                                                               | _      | Input  |

| L2WE                   | N16                                                                                                                                                                                                                                                                                                                            | Low    | Output |

| L2ZZ                   | G17                                                                                                                                                                                                                                                                                                                            | High   | Output |

| LSSD_MODE <sup>3</sup> | F9                                                                                                                                                                                                                                                                                                                             | Low    | Input  |

| MCP                    | B11                                                                                                                                                                                                                                                                                                                            | Low    | Input  |

| NC (No-Connect)        | B3, B4, B5, W19, K9, K11 <sup>4</sup> , K19 <sup>4</sup>                                                                                                                                                                                                                                                                       | _      | _      |

| OVDD <sup>2</sup>      | D5, D8, D12, E4, E6, E9, E11, F5, H4, J5, L5, M4, P5, R4, R6, R9, R11, T5, T8, T12                                                                                                                                                                                                                                             | _      | _      |

| PLL_CFG[0:3]           | A4, A5, A6, A7                                                                                                                                                                                                                                                                                                                 | High   | Input  |

| QACK                   | B2                                                                                                                                                                                                                                                                                                                             | Low    | Input  |