Windows® CE Intelligent Peripheral Controller

**Preliminary Specification V0.3**

Copyright © 1998 ITE, Inc.

This is Preliminary document release. All specifications are subject to change without notice. The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE, Inc. for the latest document(s).

All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

Phone: (408) 980-8168

**Fax:** (408) 980-9232

ITE, IT8101E and IT8101F is a trademark of ITE, Inc.

Intel, Pentium, and MMX are claimed as trademarks by Intel Corp. Cyrix, M1, and SLiC/MP are claimed as trademarks by Cyrix Corp. AMD, AMD-K5, and AMD-K6 are claimed as trademarks by Advanced Micro Devices, Inc. Microsoft and Windows are claimed as trademarks by Microsoft Corporation. PCI is claimed as a trademark by the PCI Special Interest Group. IrDA is claimed as a trademark by the Infrared Data Association. All other trademarks are claimed by their respective owners.

All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE (USA) Inc. Marketing Department 2710 Walsh Avenue Santa Clara, CA 95051 U.S.A.

ITE (USA) Inc. Phone: (512) 388-7880 Eastern U.S.A. Sales Office Fax: (512) 388-3108

896 Summit St., #105 Round Rock, TX 78664

U.S.A.

ITE, Inc. Phone: (02) 2707-9589

Marketing Department Fax: (02) 2703-3889, 2708-3186 15F. No. 376. Jen-Ai Road. Sec. 4.

Taipei, Taiwan 106, R.O.C.

If you have any marketing or sales questions, please contact:

David Lin, at ITE U.S.A: E-mail: david.lin@iteusa.com, Tel: (408) 980-8168 X238, Fax: (408) 980-9232

Don Gardenhire, at ITE Eastern USA Office: E-mail: don.gardenhire@iteusa.com

Tel: (512) 388-7880, Fax: (512) 388-3108

Jet Huang, at ITE Taiwan: E-mail jet.huang@ite.com.tw, Tel: 886-2-27079589 X6078, Fax: 886-2-27038389

To find out more about ITE, visit our World Wide Web at:

http://www.iteusa.com http://www.ite.com.tw

# **Revision** History V0.2 – V0.3

Note: Words in bold lettering in the revisions below indicate the changes. The revisions will also be marked in bold lettering for easy reference.

| Section | Revision                                                                                                                                                                                                                                                                                                                        | Page No. |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1       | Changed the feature descriptions of 1.3 and 1.4.                                                                                                                                                                                                                                                                                | 1        |

| 3       | Deleted the block Miniature Interface from Figure 3-1.                                                                                                                                                                                                                                                                          | 3        |

| 4       | Changed the description of <b>Table 4-3</b> .                                                                                                                                                                                                                                                                                   | 10       |

|         | Changed the description of <b>Table 4-11</b> .                                                                                                                                                                                                                                                                                  | 16       |

| 5       | Added max. to the Resolution column of Table 5-1. LCD Mode                                                                                                                                                                                                                                                                      | 19       |

|         | Changed the bits 6, 3-1 of BITBLTOMDE                                                                                                                                                                                                                                                                                           | 58       |

| 6       | Deleted " Physical Area 5 and 2 (MCC) " from Table 6-1. PC Card Controller Register                                                                                                                                                                                                                                             | 65       |

|         | <ul> <li>Deleted Section 6.5.11 Miniature Card Interface Status Register (MCCISR),</li> <li>6.5.12 Miniature Card General Control Register (MCCGCR),</li> <li>6.5.13 Miniature Card Status Change Register (MCCSCR),</li> <li>and</li> <li>6.5.14 Miniature Card Status Change Interrupt Enable Register (MCCSCIER).</li> </ul> | 79       |

|         | Deleted section 6.6 Miniature Card I <sup>2</sup> C Host Controller                                                                                                                                                                                                                                                             | 84       |

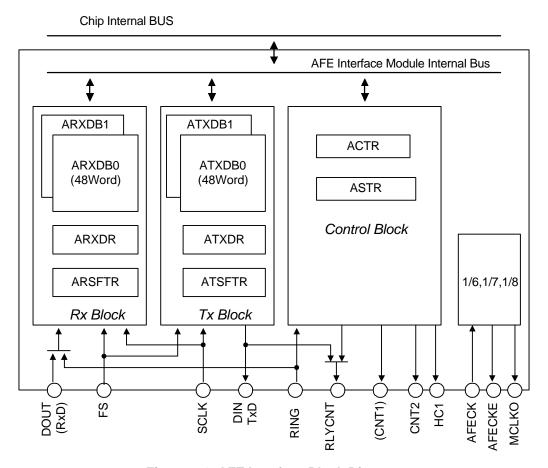

| 7       | Changed Figure 7-1. AFE Interface Block Diagram                                                                                                                                                                                                                                                                                 | 81       |

|         | Changed Table 7-2. Registers of AFE Interface                                                                                                                                                                                                                                                                                   | 82       |

|         | Changed the title of section 7.2.1 Control Register (CTR) to AFE Control Register (ACTR), and all CTR were replaced by ACTR.                                                                                                                                                                                                    |          |

|         | <ul> <li>Changed the title of section 7.2.2 Status Register (STR) to AFE Status Register (ASTR), and all STR were replaced by ASTR. Also changed the description of bits 14, 3 and 2.</li> </ul>                                                                                                                                | 84       |

|         | Changed the title of section 7.2.3 Transmit Data Register (TXDR) to AFE     Transmit Data Register (ATXDR), and all TXDR were replaced by ATXDR.                                                                                                                                                                                | 86       |

|         | <ul> <li>Changed the title of section 7.2.4 Receive Data Register (RXDR) to AFE<br/>Receive Data Register (ARXDR), and all RXDR were replaced by ARXDR.</li> </ul>                                                                                                                                                              |          |

|         | <ul> <li>Changed the title of section 7.2.5 Transmit Data Buffers (TXDB0,1) to AFE         Transmit Data Buffers (ATXDB0,1), and all TXDB0 and 1 were replaced by             ATXDB0 and 1.     </li> </ul>                                                                                                                     | 87       |

|         | Changed the title of section 7.2.6 Transmit Shift Register (TSFTR) to AFE     Transmit Shift Register (ATSFTR), and all TSFTR were replaced by ATSFTR.                                                                                                                                                                          |          |

|         | <ul> <li>Changed the title of section 7.2.7 Receive Data Buffers (RXDB0,1) to AFE<br/>Receive Data Buffers (ARXDB0,1), and all RXDB0 and 1 were replaced by<br/>ARXDB0 and 1.</li> </ul>                                                                                                                                        |          |

|         | Changed the title of section 7.2.8 Receive Shift Register (RSFTR) to AFE     Receive Shift Register (ARSFTR), and all RSFTR were replaced by ARSFTR.                                                                                                                                                                            |          |

|         | Added a paragraph The procedure required toin Figures 7.4/7.5.                                                                                                                                                                                                                                                                  | 91       |

|         | Added a sentence Receiving data requiresand SCLK. to section 7.7.2.                                                                                                                                                                                                                                                             | 92       |

## Revision History V0.2 - V0.3 (cont'd)

| Section | Revision                                                                                                                                                  | Page No. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 8       | Changed Table 8-1. The List of I/O Port Pin Function Configurations.                                                                                      | 93       |

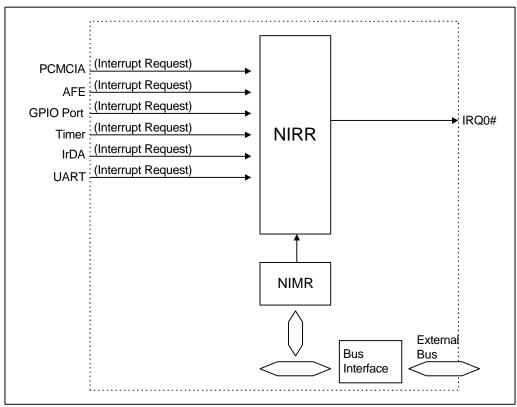

| 9       | Deleted LCDC, Miniature card and I2C form section 9.1 Overview.                                                                                           | 98       |

|         | Deleted LCDC, Miniature and I2C form Figure 9-1. Block Diagram of the Interrupt Controller.                                                               |          |

|         | Changed the R/W column of Interrupt Request register to R.                                                                                                | 100      |

|         | Deleted LCD Controller (LCDC) and I <sup>2</sup> C form the list of section 9.2.1.                                                                        |          |

|         | Deleted LCDC, Miniature card and I <sup>2</sup> C from the description of section 9.3.                                                                    | 100      |

|         | Changed bits 15, 8 and 7 of section 9.3 to reserved, and all R/O were changed to R.                                                                       |          |

|         | Deleted LCDC, Miniature card and I2C from the description of section 9.4.                                                                                 | 101      |

|         | Changed bits 15, 8 and 7 of section 9.3 to reserved.                                                                                                      |          |

| 10      | Added Access Size: 16 bits to Address: H'10000000, and changed the descriptions of bits 15-9.                                                             | 103      |

|         | Added Access Size: 16 bits to Address: H'10000002. Changed the bit name of bit 10 from "SF_decode" to "" Changed the descriptions of bits 13-8, 6,4, 1-0. | 104      |

|         | Added Access Size: 16 bits to Address: H'10000004, and changed the description of bit 4.                                                                  | 106      |

| 11      | Deleted as MODE=00/10 from descriptions of 11.1.3 Pin Configuration.                                                                                      | 110      |

|         | Changed the tile of section 11.2.8 TIMR: Timer Interrupt Mask Register to TIMR: Timer Interrupt Enable Register.                                          | 115      |

|         | Changed the name of bits 1: TMU1M and 0: TMU0M to TMU1E and TMU0E.                                                                                        |          |

|         | Changed the ID[15:0] of Figure 11-3.                                                                                                                      | 117      |

| 12      | Replaced Figure 12-1 Functional Block Diagram of FIR with a new one.                                                                                      | 120      |

|         | Added 2 lines to the end of Table 12-1. Summary of FIR Controller Registers.                                                                              | 122      |

|         | Added register name list table to every section in 12.2.3 Register Description                                                                            | 123      |

|         | Added a new section (25) FIR Configuration register to the end of 12.2.3     Register Description.                                                        | 138      |

| 13      | Added a register table in section (4) Divisor Latches                                                                                                     | 144      |

|         | MCR were all replaced by UMCR in Table 13-4. Modem Control Register Bits.                                                                                 | 146      |

|         | Added section 13.9 Caution to the end of this chapter.                                                                                                    | 151      |

| 15      | • Changed the Min. and Max value of <b>Table 15-1</b> , <b>15-2</b> , <b>15-3</b> , <b>15-4</b> , <b>15-5</b> and <b>15-6</b>                             | 153      |

|         | Replaced Table 15-8, 15-9 and 15-10 with new tables.                                                                                                      | 156      |

|         | Added Table 15-11, 15-12 and 15-13.                                                                                                                       | 157      |

|         | In Figure 15-18, changed tCAS to tCAS1 and tCAS2     In Figure 15-19, changed tCSB to tCSR                                                                | 167      |

|         | Replaced Figure 15-22 with a new one.                                                                                                                     | 169      |

# **CONTENTS**

|        |                                                           | age  |

|--------|-----------------------------------------------------------|------|

|        | atures                                                    |      |

| 1.1    | CPU Interface                                             |      |

| 1.2    | LCD Controller                                            |      |

| 1.3    | PCMCIA Controller                                         |      |

| 1.4    | AFE Interface                                             |      |

| 1.5    | GPIO Function                                             |      |

| 1.6    | Interrupt                                                 |      |

| 1.7    | Power Management                                          |      |

| 1.8    | Timer                                                     | 1    |

| 1.9    | lrDA                                                      |      |

| 1.10   | UART                                                      |      |

| 1.11   | Package                                                   |      |

| 2. Ge  | neral Description                                         | 1    |

| 3. Pin | Configuration and Block Diagram                           | 2    |

| 3.1    | Pin Configuration                                         | 2    |

| 3.2    | Block Diagram                                             | 3    |

| 3.3    | Physical Address Space Map                                | 4    |

| 3.4    | SH7709 CPU Interface Access Timing                        | 5    |

| 4. IT8 | 101E and IT8101F Pin Descriptions                         | 6    |

| 5. Co  | lor LCD Controller                                        | .19  |

| 5.1    | Overview                                                  | 19   |

| 5.1    | .1 Features                                               | 19   |

| 5.1    | .2 Display Capabilities                                   | . 19 |

| 5.1    | .3 Hardware Acceleration                                  | . 20 |

| 5.1    | .4 System BUS I/F                                         | . 22 |

| 5.1    | .5 Display Memory I/F                                     | . 23 |

| 5.2    | LCD Controller Control Register                           | . 23 |

| 5.2    | .1 Base Address Register                                  | . 23 |

| 5.2    |                                                           |      |

| 5.2    | .3 LCDC Control Register                                  | . 25 |

| 5.3    | LCD Register                                              | .31  |

| 5.3    | .1 LCD Display Register                                   | .31  |

| 5.3    | .2 LCD Display Register 2                                 | .31  |

| 5.3    | .3 LCD Number of Characters in Horizontal Register        | . 32 |

| 5.3    | .4 Start Position of Horizontal Register                  | 33   |

| 5.3    | .5 Total Vertical Lines Register                          | .34  |

| 5.3    | .6 Display Vertical Lines Register                        | 34   |

| 5.3    | .7 Vertical Synchronization Position Register             | . 35 |

| 5.3    | .8 LCD Display Register 3                                 | 35   |

| 5.4    | CRT Control Register                                      |      |

| 5.4    | .1 CRTC Total Vertical Lines Register                     | 39   |

| 5.4    |                                                           |      |

| 5.4    |                                                           |      |

| 5.5    | Palette Register                                          |      |

| 5.6    | Acceleration Common Registers                             |      |

| 5.7    | Line Drawing Registers                                    |      |

| 5.8    | BitBLT Registers                                          |      |

| 5.9    | FRC Registers                                             |      |

|        | Card Controller (PCC) and Miniature Card Controller (MCC) |      |

| 6.1    | Overview                                                  |      |

| 6.2    | Features                                                  |      |

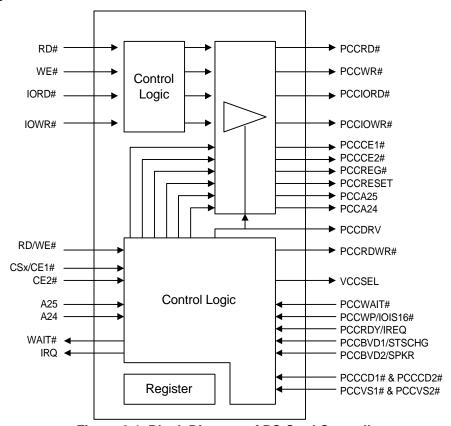

| 6.3    | Block Diagram                                             |      |

| 6.4    | Register Configuration                                    |      |

| 6.5    | Register Descriptions                                     |      |

| 6.5    | /                                                         |      |

| 6.5    | .2 PCC0 General Control Register (PCC0GCR)                | . 67 |

| 6.5.3            | PCC0 Card Status Register (PCC0CSCR)                                               | 69       |

|------------------|------------------------------------------------------------------------------------|----------|

| 6.5.4            |                                                                                    |          |

| 6.5.5            | PCC0 Software Control Register (PCC0SCR)                                           |          |

| 6.5.6            | PCC1 Interface Status Register (PCC1ISR)                                           |          |

| 6.5.7            | PCC1 General Control Register (PCC1GCR)PCC1 Card Status Change Register (PCC1CSCR) |          |

| 6.5.8            |                                                                                    |          |

| 6.5.9            | PCC1 Card Change Interrupt Enable Register (PCC1CSCIER)                            |          |

| 6.5.10<br>6.5.11 | PCC1 Software Control Register (PCC1SCR)                                           |          |

| 6.5.11           | · · · · · · · · · · · · · · · · · · ·                                              |          |

|                  | nterface                                                                           |          |

|                  | verview                                                                            |          |

| 7.1 0            | Features                                                                           |          |

| 7.1.1            | Block Diagram                                                                      |          |

|                  | egister Description                                                                |          |

| 7.2.1            | AFE Control Register (ACTR)                                                        |          |

| 7.2.1            | AFE Status Register (ASTR)                                                         |          |

| 7.2.3            | AFE Transmit Data Register (ATXDR)                                                 |          |

| 7.2.4            | AFE Receive Data Register (ARXDR)                                                  |          |

| 7.2.5            | AFE Transmit Data Buffers (ATXDB0,1)                                               |          |

| 7.2.6            | AFE Transmit Shift Register (ATSFTR)                                               |          |

| 7.2.7            | AFE Receive Data Buffers (ARXDB0,1)                                                |          |

| 7.2.8            | AFE Receive Shift Register (ARSFTR)                                                | 87<br>87 |

|                  | ata Transfer                                                                       |          |

| 7.3.1            | Data Transmit                                                                      |          |

| 7.3.2            | Data Receive                                                                       |          |

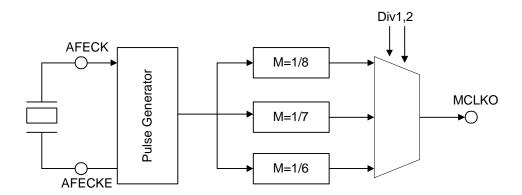

|                  | ivider                                                                             |          |

|                  | xternal Chip Control Signal                                                        |          |

|                  | terrupt                                                                            |          |

| 7.7 H            | ow to Use the Special Pin (RLYCNT, RING)                                           | 92       |

| 7.7.1            |                                                                                    |          |

| 7.7.2            | How to Use the RING Pin                                                            | 92       |

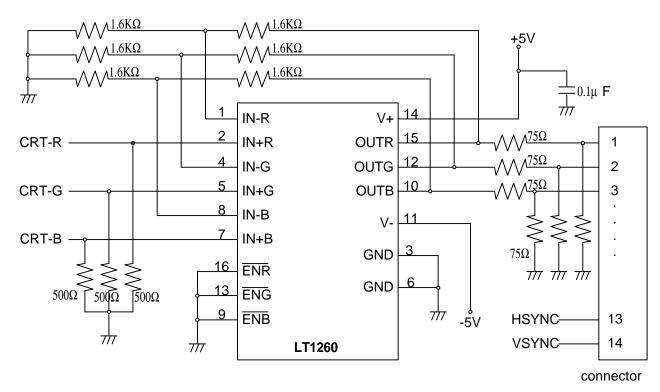

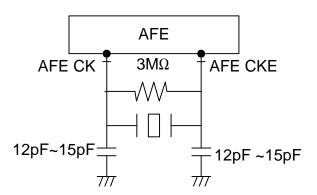

| 7.8 At           | ttachment                                                                          | 92       |

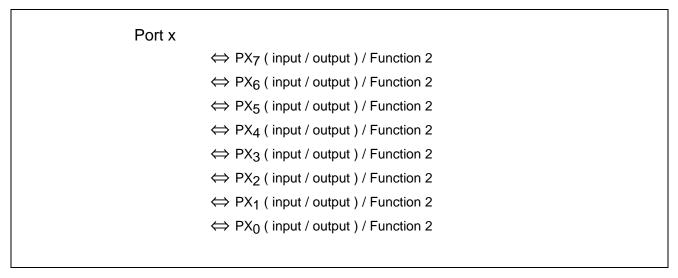

| 8. Pin Fເ        | unction Controller & I/O Port                                                      | 93       |

| 8.1 O            | verview                                                                            | 93       |

| 8.1.1            | Features                                                                           | 93       |

|                  | egister Configuration                                                              |          |

|                  | egister Descriptions                                                               |          |

| 8.3.1            | Port x (A to D) Data Register (GPADR to GPDDR)                                     | 96       |

| 8.3.2            | Port Control Register (GPACR to GPDCR)                                             |          |

| 8.3.3            | Port Interrupt Control Register (GPAICR - GPDICR)                                  |          |

| 8.3.4            | Port Interrupt Status Register (GPAISR - GPDISR)                                   |          |

|                  | upt Controller (INTC)                                                              |          |

|                  | verview                                                                            |          |

| 9.1.1            | Features                                                                           |          |

| 9.1.2            | Block Diagram                                                                      |          |

| 9.1.3            | Pin Configuration                                                                  |          |

| 9.1.4            | Register Configuration                                                             |          |

|                  | terrupt Sources                                                                    |          |

| 9.2.1            | On-Chip Module Interrupt                                                           | 99       |

| 9.2.2            | Interrupt Exception Processing and Priority                                        |          |

|                  | IRR: Interrupt Request Register                                                    |          |

|                  | IMR: Interrupt Mask Register                                                       |          |

| 9.5 Pc           | ower-on RESET Requirement                                                          | 102      |

| 9.6<br><b>10.</b>                                                                                                                                                                | Special Register Programming Sequence  Standby Mode and System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                                                                                                                                                  | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                               |

| Toblo                                                                                                                                                                            | 4.1. Cignal Names ( by nin numbers in alphabetical order )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                            |

|                                                                                                                                                                                  | <ul><li>4-1. Signal Names (by pin numbers in alphabetical order)</li><li>4-2. Signal Names (by symbols in alphabetical order)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                                                                                                                                                                                  | 4-3. Pin Descriptions of Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

|                                                                                                                                                                                  | 4-4. Pin Descriptions of SH7709 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |

|                                                                                                                                                                                  | 4-5. Pin Descriptions of Port B, Port A and I/O Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                  | 4-6. Pin Descriptions of AFE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                  | 4-7. Pin Descriptions of LCD Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                  | 4-8. Pin Descriptions of Frame Memory (DRAM) Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|                                                                                                                                                                                  | 4-10. Pin Descriptions of PCMCIA Card 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

|                                                                                                                                                                                  | 4-11. Pin Descriptions of PCMCIA Card 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| Table                                                                                                                                                                            | 4-12. Pin Descriptions of I/O Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                              |

|                                                                                                                                                                                  | 5-1. LCD Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|                                                                                                                                                                                  | 5-2. CRT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|                                                                                                                                                                                  | 5-3. Definition of Supported Raster-Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|                                                                                                                                                                                  | 6-1. PC Card Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |

| Table                                                                                                                                                                            | 7-1. Pin Function of AFE Interface Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81                              |

|                                                                                                                                                                                  | 7-2. Registers of AFE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                 |

|                                                                                                                                                                                  | 8-1. The List of I/O Port Pin Function Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

|                                                                                                                                                                                  | 8-2. The List of Register Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |

| rabie                                                                                                                                                                            | 8-3. READ/WRITE Operation of the Port x (A to D) Data Register (GPADR to GPDDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                              |

| Table                                                                                                                                                                            | 8-4 The Definitions of Control Rits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                              |

| Table                                                                                                                                                                            | 8-4. The Definitions of Control Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97                              |

| Table                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97                              |

| Table                                                                                                                                                                            | 8-4. The Definitions of Control Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |

|                                                                                                                                                                                  | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                            |

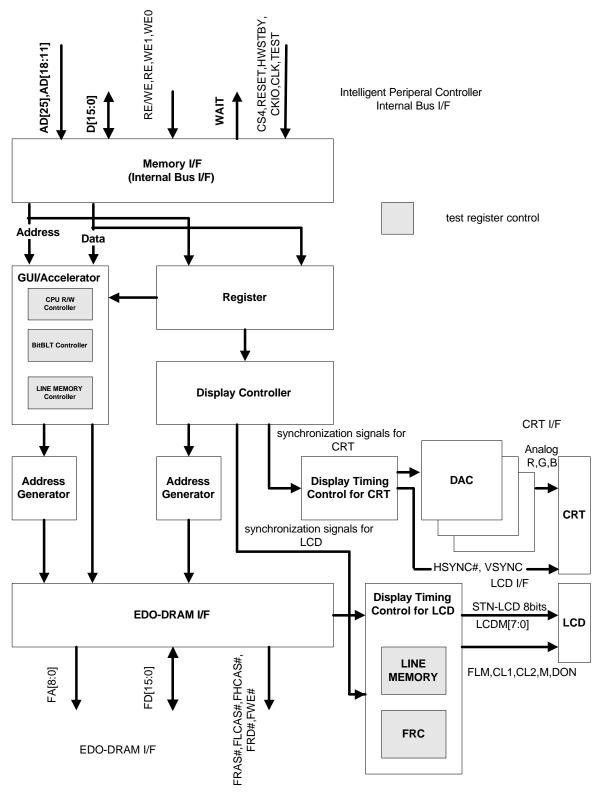

| Figure                                                                                                                                                                           | FIGURES  3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Page</b><br>3                |

| Figure<br>Figure                                                                                                                                                                 | FIGURES  9.3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Page</b><br>3                |

| Figure<br>Figure<br>Figure                                                                                                                                                       | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Page</b><br>3<br>4           |

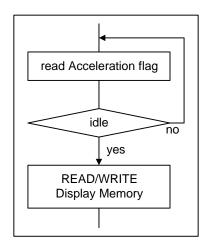

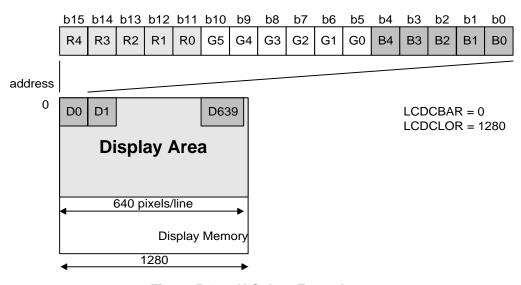

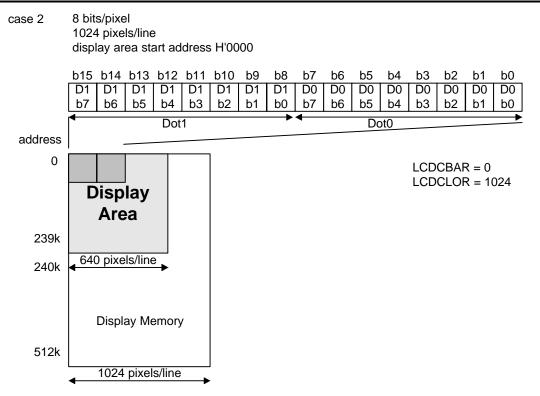

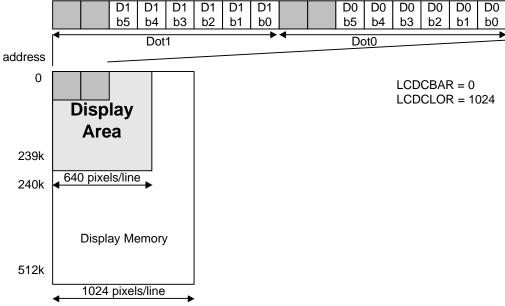

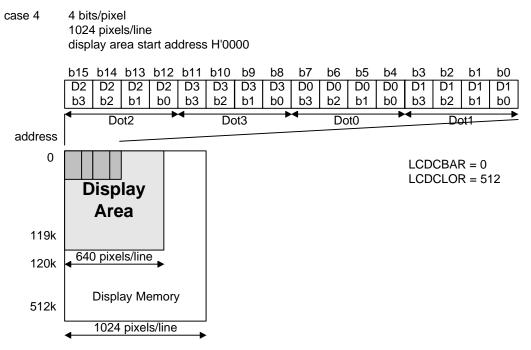

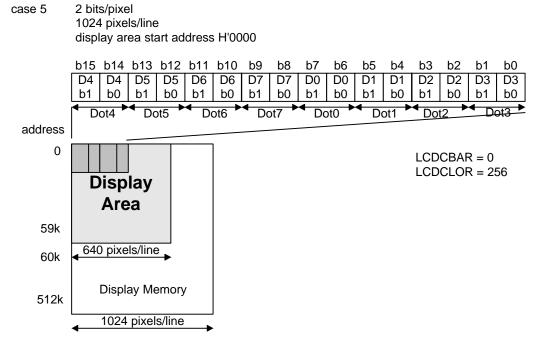

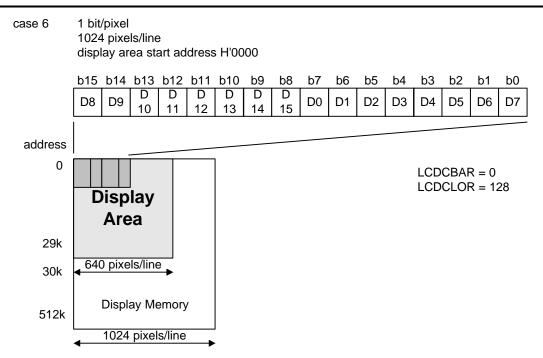

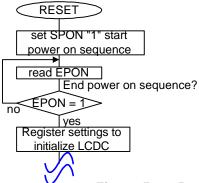

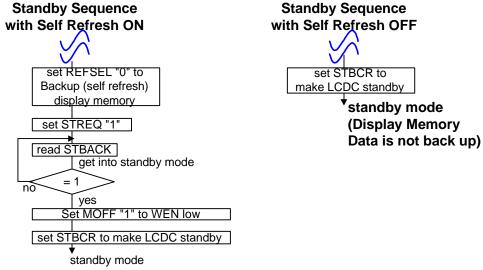

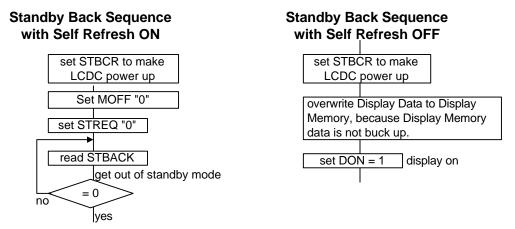

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                                   | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle 5 5-1. LCDC Register & Display Memory Allocation 2 5-2. Flow Chart for CPU Access Display Memory                                                                                                                                                                                                                                                                                                                                                                                                | <b>Page</b><br>4<br>5<br>22     |

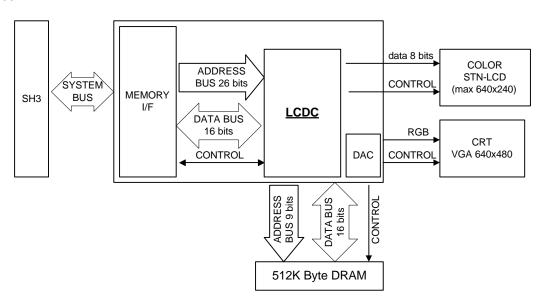

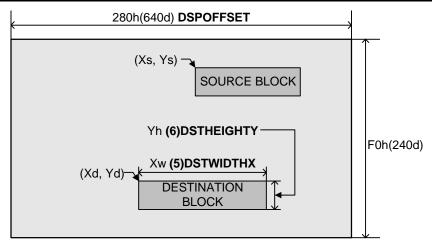

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                                         | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle 3 5-1. LCDC Register & Display Memory Allocation 2 5-2. Flow Chart for CPU Access Display Memory 3 5-3. LCD System Block Diagram                                                                                                                                                                                                                                                                                                                                                                | Page352222                      |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                               | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page345222223                   |

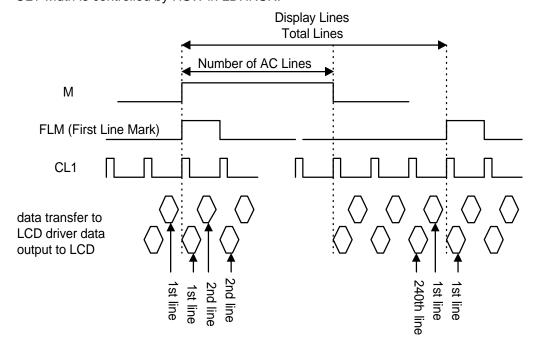

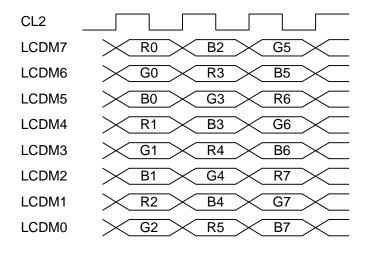

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                               | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page34522222326                 |

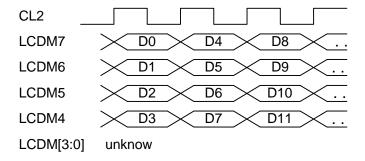

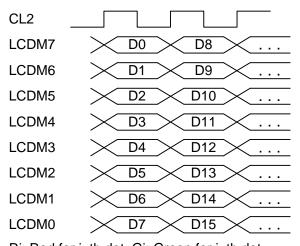

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                                     | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page34522232627                 |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                           | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle 2 5-1. LCDC Register & Display Memory Allocation 2 5-2. Flow Chart for CPU Access Display Memory 3 5-3. LCD System Block Diagram 3 5-4. 64K Colors Example 3 5-5. 256/256K Colors Example 3 5-6. 64 Gray Scales Example 3 5-7. 16 Gray Scales Example                                                                                                                                                                                                                                           | Page3452223262728               |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                                           | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page345222326272728             |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                       | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle 5 5-1. LCDC Register & Display Memory Allocation 5 5-2. Flow Chart for CPU Access Display Memory 6 5-3. LCD System Block Diagram 6 5-4. 64K Colors Example 6 5-5. 256/256K Colors Example 6 5-6. 64 Gray Scales Example 6 5-7. 16 Gray Scales Example 6 5-8. 4 Gray Scales Example 6 5-9. 2 Gray Scales Example 6 6-1. Block Diagram of PC Card Controller                                                                                                                                      | Page3452223262727282829         |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                             | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page3452223262727282829481      |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                   | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram 2 3-2. IT8101 and IT8101F Physical Address Space Map 3 3-3. Basic Bus Cycle 2 5-1. LCDC Register & Display Memory Allocation 2 5-2. Flow Chart for CPU Access Display Memory 2 5-3. LCD System Block Diagram 2 5-4. 64K Colors Example 3 5-5. 256/256K Colors Example 3 5-6. 64 Gray Scales Example 3 5-7. 16 Gray Scales Example 3 5-8. 4 Gray Scales Example 3 5-9. 2 Gray Scales Example 3 6-1. Block Diagram of PC Card Controller 3 7-1. AFE Interface Block Diagram 3 7-2. Divider Configuration                                                                      | Page3452223262727282948189      |

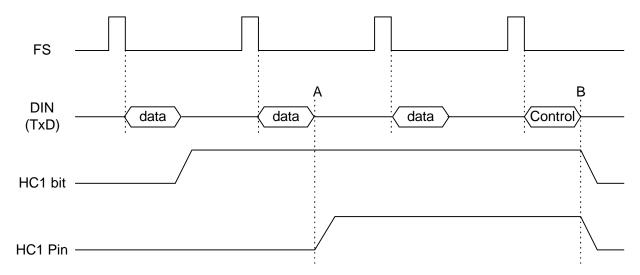

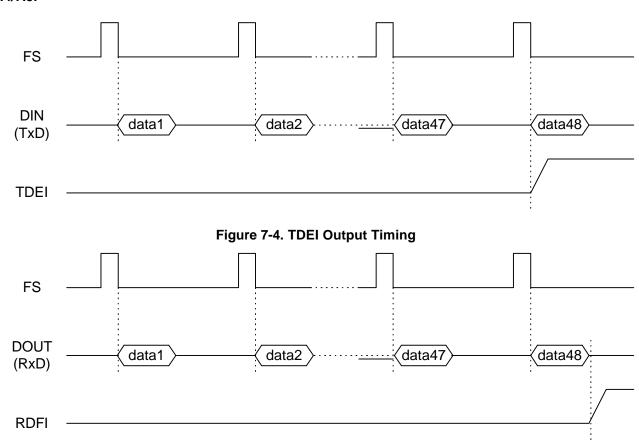

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                                         | FIGURES  2.3-1. IT8101E and IT8101F Block Diagram 2.3-2. IT8101 and IT8101F Physical Address Space Map 2.3-3. Basic Bus Cycle 2.5-1. LCDC Register & Display Memory Allocation 2.5-2. Flow Chart for CPU Access Display Memory 2.5-3. LCD System Block Diagram 2.5-4. 64K Colors Example 2.5-5. 256/256K Colors Example 2.5-6. 64 Gray Scales Example 2.5-7. 16 Gray Scales Example 2.5-8. 4 Gray Scales Example 2.5-9. 2 Gray Scales Example 2.5-9. 2 Gray Scales Example 2.6-1. Block Diagram of PC Card Controller 2.7-1. AFE Interface Block Diagram 2.7-2. Divider Configuration 2.7-3. HC1 Pin and Control Data Outputs | Page34522232627272829298189     |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                               | FIGURES  9.3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page3452223262727282929818990   |

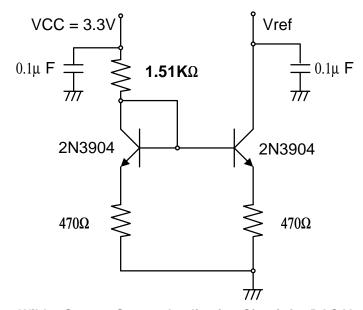

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure                     | FIGURES  2 3-1. IT8101E and IT8101F Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page345222326272728282964818990 |

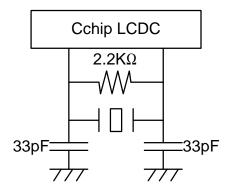

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure | FIGURES  2.3-1. IT8101E and IT8101F Block Diagram 2.3-2. IT8101 and IT8101F Physical Address Space Map 2.3-3. Basic Bus Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page345222326272828298189909191 |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure | FIGURES  2.3-1. IT8101E and IT8101F Block Diagram 2.3-2. IT8101 and IT8101F Physical Address Space Map 2.3-3. Basic Bus Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page345222326272828298189909191 |

Preliminary V0.3

## Windows® CE Intelligent Peripheral Controller

Specifications subject to Change without Notice

ITPA-PN-97034 Alan, Nov. 15, 1997

#### 1. Features

#### 1.1 CPU Interface

- Supports Hitachi SH7709 CPU Interface

- 3.3 V

#### 1.2 LCD Controller

- Color/Monochrome STN-LCD direct interface

- 64, 16, 4, 2 gray scales

- 256/256K and 64K colors

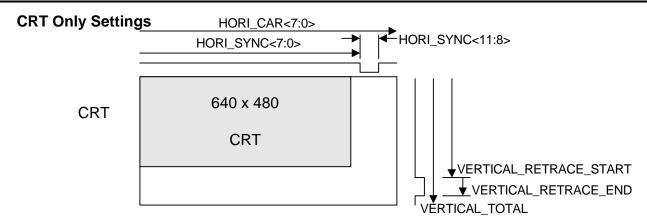

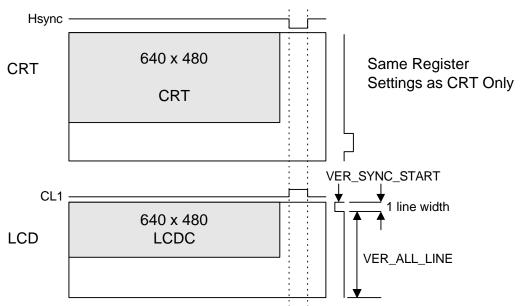

- Supports CRT interface (VESA VGA)

- Display resolution 640 x 240 for LCD, 640 x 480 for CRT

- Supports CRT and LCD simultaneous display

- Ten (10) types of BitBLT hardware acceleration

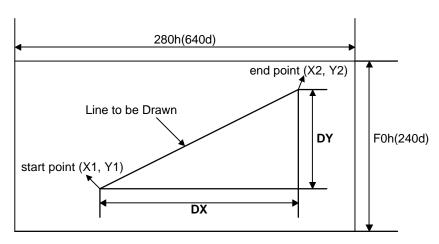

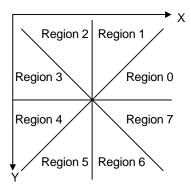

- Solid line drawing based upon Bresenham Parameter

- Rectangular solid color fill function

- Supports 256KX16 bit EDO-DRAM

- 4/8 bit display interface

- Supports STANDBY Mode

#### 1.3 PCMCIA Controller

- PCMCIA PC card standard v2.1 compliant

- Miniature card spec. v1.1 compliant

- Supports PCMCIA memory and IO card at area 6

- Supports PCMCIA memory card at area 5.

#### 1.4 AFE Interface

- Supports SGS-THOMSON STL7550 interface

- Supports STANDBY Mode

### 1.5 GPIO Function

- GPIO pins can be programmable Input, Output or Interrupt input pins.

- Internal pull-up resistor ON/OFF control

- Interrupt events can be independently generated or masked on each I/O pin.

Power down control by software (input gated and output floating)

#### 1.6 Interrupt

- Only one external interrupt output pin is used for SH7709 External interrupt input.

- The priority order of interrupt request lines is determined by software.

- Module interrupts can be masked on/off.

#### 1.7 Power Management

- Supports STANDBY Mode for each module.

- AFE, LCD, UART clock input can be stopped.

- IrDA clock input can be gated.

- The CPU input signals can be gated.

#### 1.8 Timer

- 2-channel 16-bit timer with prescale (1, 1/4, 1/8, 1/16)

- Supports STANDBY Mode

#### 1.9 IrDA

- Supports HP SIR or ASKIR infrared interface

- Supports MIR and FIR

- Provides DMA channel mode for FIR

#### 1.10 **UART**

■ Standard 16550 compatible

#### 1.11 Package

IT8101E: 208-pin LQFPIT8101F: 208-pin PQFP

### 2. General Description

This Controller LSI, directly connected to SH7709, integrates a color LCD controller, a PCMCIA controller, an analog front end (AFE) interface, an

I/O port, a timer, the UART, etc. This chip architecture features two-chip solution for PDA/HPC with a color LCD.

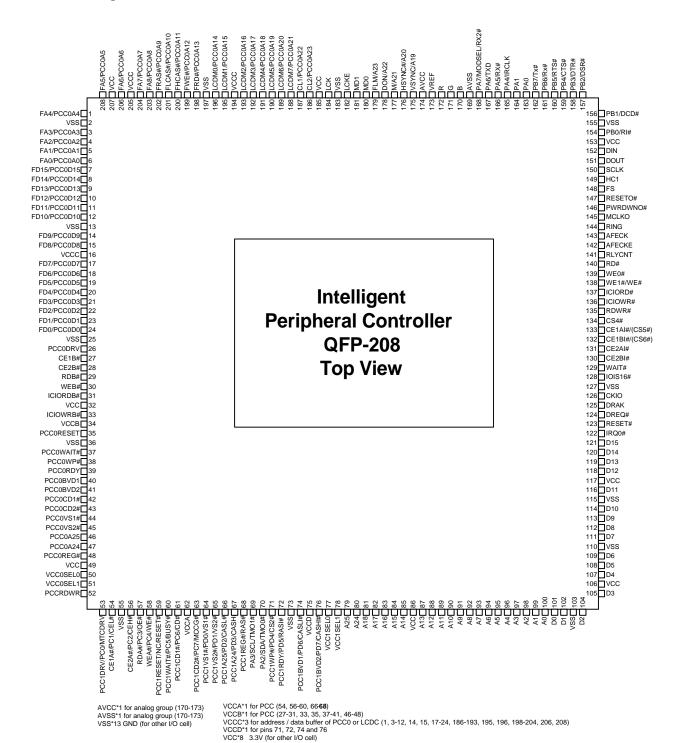

### 3. Pin Configuration and Block Diagram

### 3.1 Pin Configuration

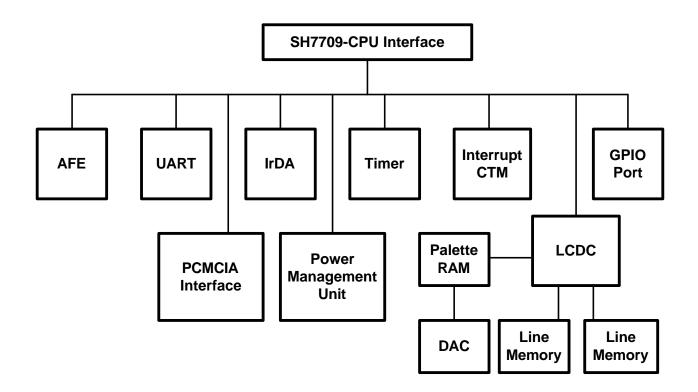

### 3.2 Block Diagram

Figure 3-1. IT8101E and IT8101F Block Diagram

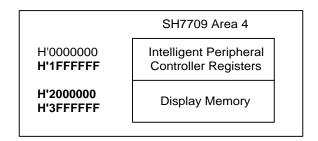

### 3.3 Physical Address Space Map

This LSI is directly connected to SH7709 on Area 4 (Fig3-2). SH7709 can access the internal registers on the Intelligent Peripheral Controller. Frame memory is accessed on Area 4.

| Area 0: H'00000000 | Ordinary memory /<br>Burst ROM          |                                                                                   |

|--------------------|-----------------------------------------|-----------------------------------------------------------------------------------|

| Area 1: H'04000000 | Internal I/O                            |                                                                                   |

| Area 2: H'08000000 | Ordinary memory /<br>SDRAM, DRAM        | Only DRAM with a 16-bit bus can be connected to area 2.                           |

| Area 3: H'0C000000 | Ordinary memory /<br>SDRAM, DRAM, PSRAM |                                                                                   |

| Area 4: H'10000000 | Intelligent Peripheral Controller       | Internal Registers of Intelligent Peripheral Controller and Frame memory (C-LCDC) |

| Area 5: H'14000000 | Ordinary memory /<br>Burst ROM / PCMCIA | The PCMCIA interface is only dedicated for the memory card.                       |

| Area 6: H'18000000 | Ordinary memory /<br>Burst ROM / PCMCIA | The PCMCIA interface is shared by the memory card and I/O card.                   |

Figure 3-2. IT8101 and IT8101F Physical Address Space Map

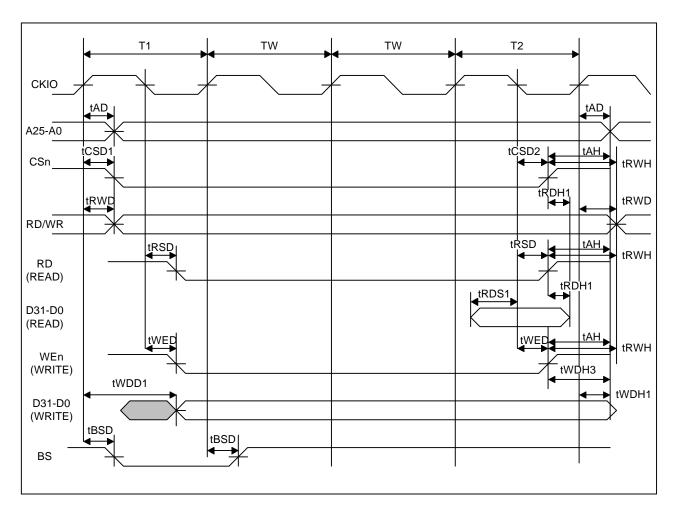

### 3.4 SH7709 CPU Interface Access Timing

Figure 3-3. Basic Bus Cycle

## 4. IT8101E and IT8101F Pin Descriptions

The Intelligent Peripheral Controller comes in two packages: 208-pin LQFP (Low Profile Quad Flat Package) for IT8101E and 208 PQFP (Plastic Quad Flat Package) for IT8101F. The controller comprises three (3) categories: 179 signal balls, fifteen (15) power balls and fourteen (14) ground balls.

Table 4-1. Signal Names (by pin numbers in alphabetical order)

| Pin | Signal       | Pin | Signal     | Pin | Signal                  | Pin | Signal                  |

|-----|--------------|-----|------------|-----|-------------------------|-----|-------------------------|

| 1   | FA4/PCC0A4   | 22  | FD2/PCC0D2 | 43  | PCC0CD2#                | 64  | PCC1VS1#/PD0/<br>VS1#   |

| 2   | VSS          | 23  | FD1/PCC0D1 | 44  | PCC0VS1#                | 65  | PCC1VS2#/PD1/<br>VS2#   |

| 3   | FA3/PCC0A3   | 24  | FD0/PCC0D0 | 45  | PCC0VS2#                | 66  | PCC1A25/PD2/<br>CASL#   |

| 4   | FA2/PCC0A2   | 25  | VSS        | 46  | PCC0A25                 | 67  | PCC1A24/PD3/<br>CASH#   |

| 5   | FA1/PCC0A1   | 26  | PCC0DRV    | 47  | PCC0A24                 | 68  | PCC1REG#/RAS#           |

| 6   | FA0/PCC0A0   | 27  | CE1B#      | 48  | PCC0REG#                | 69  | PA3/SCL/TMO1#           |

| 7   | FD15/PCC0D15 | 28  | CE2B#      | 49  | VCC                     | 70  | PA2/SDA/TMO0#           |

| 8   | FD14/PCC0D14 | 29  | RDB#       | 50  | VCC0SEL0                | 71  | PCC1WP#/PD4/<br>CS2#    |

| 9   | FD13/PCC0D13 | 30  | WEB#       | 51  | VCC0SEL1                | 72  | PCC1RDY/PD5/<br>RASI#   |

| 10  | FD12/PCC0D12 | 31  | ICIORDB#   | 52  | PCCRDWR                 | 73  | VSS                     |

| 11  | FD11/PCC0D11 | 32  | VCC        | 53  | PCC1DRV/PC0/<br>MTCDRV  | 74  | PCC1BVD1/PD6/<br>CASLI# |

| 12  | FD10/PCC0D10 | 33  | ICIOWRB#   | 54  | CE1A#/PC1/CEL#          | 75  | VCCD                    |

| 13  | VSS          | 34  | VCCB       | 55  | VSS                     | 76  | PCC1BVD2/PD7/<br>CASHI# |

| 14  | FD9/PCC0D9   | 35  | PCC0RESET  | 56  | CE2A#/PC2/CEH#          | 77  | VCC1SEL0                |

| 15  | FD8/PCC0D8   | 36  | VSS        | 57  | RDA#/PC3/OE#            | 78  | VCC1SEL1                |

| 16  | VCCC         | 37  | PCC0WAIT#  | 58  | WEA#/PC4/WE#            | 79  | A25                     |

| 17  | FD7/PCC0D7   | 38  | PCC0WP#    | 59  | PCC1RESET/NC/<br>RESET# | 80  | A24                     |

| 18  | FD6/PCC0D6   | 39  | PCC0RDY    | 60  | PCC1WAIT#/PC5/<br>BUSY# | 81  | A18                     |

| 19  | FD5/PCC0D5   | 40  | PCC0BVD1   | 61  | PCC1CD1#/PC6/<br>CD#    | 82  | A17                     |

| 20  | FD4/PCC0D4   | 41  | PCC0BVD2   | 62  | VCCA                    | 83  | A16                     |

| 21  | FD3/PCC0D3   | 42  | PCC0CD1#   | 63  | PCC1CD2#/PC7/<br>MCCG#  | 84  | A15                     |

Table 4-1. Signal Names (by pin numbers in alphabetical order ) [cont'd]

| Pin | Signal | Pin | Signal        | Pin | Signal              | Pin | Signal             |

|-----|--------|-----|---------------|-----|---------------------|-----|--------------------|

| 85  | A14    | 116 | D11           | 147 | RESETO#             | 178 | DON/A22            |

| 86  | VCC    | 117 | VCC           | 148 | FS                  | 179 | FLM/A23            |

| 87  | A13    | 118 | D12           | 149 | HC1                 | 180 | MD0                |

| 88  | A12    | 119 | D13           | 150 | SCLK                | 181 | MD1                |

| 89  | A11    | 120 | D14           | 151 | DOUT                | 182 | LCKE               |

| 90  | A10    | 121 | D15           | 152 | DIN                 | 183 | VSS                |

| 91  | A9     | 122 | IRQ0#         | 153 | VCC                 | 184 | LCK                |

| 92  | A8     | 123 | RESET#        | 154 | PB0/RI#             | 185 | VCC                |

| 93  | A7     | 124 | DREQ#         | 155 | VSS                 | 186 | CL2/PCC0A23        |

| 94  | A6     | 125 | DRAK          | 156 | PB1/DCD#            | 187 | CL1/PCC0A22        |

| 95  | A5     | 126 | CKIO          | 157 | PB2/DSR#            | 188 | LCDM7/PCC0A21      |

| 96  | A4     | 127 | VSS           | 158 | PB3/DTR#            | 189 | LCDM6/PCC0A20      |

| 97  | A3     | 128 | IOIS16#       | 159 | PB4/CTS#            | 190 | LCDM5/PCC0A19      |

| 98  | A2     | 129 | WAIT#         | 160 | PB5/RTS#            | 191 | LCDM4/PCC0A18      |

| 99  | A1     | 130 | CE2BI#        | 161 | PB6/Rx#             | 192 | LCDM3/PCC0A17      |

| 100 | A0     | 131 | CE2AI#        | 162 | PB7/Tx#             | 193 | LCDM2/PCC0A16      |

| 101 | D0     | 132 | CE1BI#/(CS6#) | 163 | PA0                 | 194 | VCCC               |

| 102 | D1     | 133 | CE1AI#/(CS5#) | 164 | PA1                 | 195 | LCDM1/PCC0A15      |

| 103 | VSS    | 134 | CS4#          | 165 | PA4/IRCLK           | 196 | LCDM0/PCC0A14      |

| 104 | D2     | 135 | RDWR#         | 166 | PA5/RX#             | 197 | VSS                |

| 105 | D3     | 136 | ICIOWR#       | 167 | PA6/TXD             | 198 | FRD#/PCC0A13       |

| 106 | VCC    | 137 | ICIORD#       | 168 | PA7/MODSEL/<br>RX2# | 199 | FWE#/PCC0A12       |

| 107 | D4     | 138 | WE1#/WE#      | 169 | AVSS                | 200 | FHCAS#/<br>PCC0A11 |

| 108 | D5     | 139 | WE0#          | 170 | В                   | 201 | FLCAS#/<br>PCC0A10 |

| 109 | D6     | 140 | RD#           | 171 | G                   | 202 | FRAS#/PCC0A9       |

| 110 | VSS    | 141 | RLYCNT        | 172 | R                   | 203 | FA8/PCC0A8         |

| 111 | D7     | 142 | AFECKE        | 173 | VREF                | 204 | FA7/PCC0A7         |

| 112 | D8     | 143 | AFECK         | 174 | AVCC                | 205 | VCCC               |

| 113 | D9     | 144 | RING          | 175 | VSYNC/A19           | 206 | FA6/PCC0A6         |

| 114 | D10    | 145 | MCLKO         | 176 | HSYNC#/A20          | 207 | VCC                |

| 115 | VSS    | 146 | PWRDWNO#      | 177 | M/A21               | 208 | FA5/PCC0A5         |

Table 4-2. Signal Names (by symbols in alphabetical order)

| Signal             | Pin      | Signal      | Pin | Signal             | Pin | Signal              | Pin |

|--------------------|----------|-------------|-----|--------------------|-----|---------------------|-----|

| A0                 | 100      | CE2AI#      | 131 | FA3/PCC0A3         | 3   | HSYNC#/A20          | 176 |

| A1                 | 99 CE2B# |             | 28  | FA4/PCC0A4         | 1   | ICIORD#             | 137 |

| A2                 | 98       | CE2BI#      | 130 | FA5/PCC0A5         | 208 | ICIORDB#            | 31  |

| A3                 | 97       | CL1/PCC0A22 | 187 | FA6/PCC0A6         | 206 | ICIOWR#             | 136 |

| A4                 | 96       | CL2/PCC0A23 | 186 | FA7/PCC0A7         | 204 | ICIOWRB#            | 33  |

| A5                 | 95       | CKIO        | 126 | FA8/PCC0A8         | 203 | IOIS16#             | 128 |

| A6                 | 94       | CS4#        | 134 | FD0/PCC0D0         | 24  | IRQ0#               | 122 |

| A7                 | 93       | D0          | 101 | FD1/PCC0D1         | 23  | LCDM0/PC0A14        | 196 |

| A8                 | 92       | D1          | 102 | FD2/PCC0D2         | 22  | LCDM1/PC0A15        | 195 |

| A9                 | 91       | D2          | 104 | FD3/PCC0D3         | 21  | LCDM2/PC0A16        | 193 |

| A10                | 90       | D3          | 105 | FD4/PCC0D4         | 20  | LCDM3/PC0A17        | 192 |

| A11                | 89       | D4          | 107 | FD5/PCC0D5         | 19  | LCDM4/PC0A18        | 191 |

| A12                | 88       | D5          | 108 | FD6/PCC0D6         | 18  | LCDM5/PC0A19        | 190 |

| A13                | 87       | D6          | 109 | FD7/PCC0D7         | 17  | LCDM6/PC0A20        | 189 |

| A14                | 85       | D7          | 111 | FD8/PCC0D8         | 15  | LCDM7/PC0A21        | 188 |

| A15                | 84       | D8          | 112 | FD9/PCC0D9         | 14  | LCK                 | 184 |

| A16                | 83       | D9          | 113 | FD10/PCC0D10       | 12  | LCKE                | 182 |

| A17                | 82       | D10         | 114 | FD11/PCC0D11       | 11  | M/A21               | 177 |

| A18                | 81       | D11         | 116 | FD12/PCC0D12       | 10  | MCLKO               | 145 |

| A24                | 80       | D12         | 118 | FD13/PCC0D13       | 9   | MD0                 | 180 |

| A25                | 79       | D13         | 119 | FD14/PCC0D14       | 8   | MD1                 | 181 |

| AFECK              | 143      | D14         | 120 | FD15/PCC0D15       | 7   | PA0                 | 163 |

| AFECKE             | 142      | D15         | 121 | FHCAS#/<br>PCC0A11 | 200 | PA1                 | 164 |

| AVCC               | 174      | DIN         | 152 | FLCAS#/<br>PCC0A10 | 201 | PA2/SDA/<br>TMO0#   | 70  |

| AVSS               | 169      | DOUT        | 151 | FLM/A23            | 179 | PA3/SCL/TMO1#       | 69  |

| В                  | 170      | DRAK        | 125 | FRAS#/PCC0A9       | 202 | PA4/IRCLK           | 165 |

| CE1A#/PC1/CEL#     | 54       | DREQ#       | 124 | FRD#/PCC0A13       | 198 | PA5/RX#             | 166 |

| CE1AI#/(CS5#)      | 133      | DON/A22     | 178 | FS                 | 148 | PA6/TXD             | 167 |