**Approved Product**

#### **PRODUCT FEATURES**

- Supports PPC603 and PPC604 Processors.

- 5 CPU clocks

- Up to 12 SDRAM clocks for 3 DIMMs.

- 8 PCI synchronous clocks.

- Optional common or mixed supply mode:

- (VDD = VDDS = VDDC = 3.3V) or

- (VDD = VDDS =3.3V, VDDC = 2.5V)

- < 250ps skew among CPU or SDRAM clocks.</li>

- < 250ps skew among PCI clocks.</p>

- 2 Buffered reference clocks

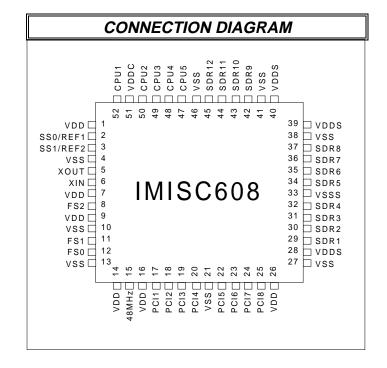

- 52-pin QFP package

| BLOCK DIAGRAM |                      |                                                                                         |  |  |  |  |

|---------------|----------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| XIN           | REF<br>PLL           | REF(1:2) /SS (0:1)  48M VDDC                                                            |  |  |  |  |

| FS(0:2)       | PLL<br>Clock<br>Gen. | B $\rightarrow$ CPU(1:5)  VDDS  B $\rightarrow$ SDR(1:12)  dly B $\rightarrow$ PCI(1:8) |  |  |  |  |

|               |                      | $\frac{\text{PCI}(1:8)}{\text{PDD}}$                                                    |  |  |  |  |

|     | FREQUENCY TABLE (in MHz) |     |           |           |  |  |  |  |

|-----|--------------------------|-----|-----------|-----------|--|--|--|--|

| FS2 | FS1                      | FS0 | CPU (1:8) | PCI (1:8) |  |  |  |  |

| 0   | 0                        | 0   | XIN/2*    | XIN/4     |  |  |  |  |

| 0   | 0                        | 1   | 70.00     | 35.00     |  |  |  |  |

| 0   | 1                        | 0   | 78.75     | 31.50     |  |  |  |  |

| 0   | 1                        | 1   | Tri-state | Tri-state |  |  |  |  |

| 1   | 0                        | 0   | 75.17     | 30.07     |  |  |  |  |

| 1   | 0                        | 1   | 60.14     | 30.07     |  |  |  |  |

| 1   | 1                        | 0   | 66.82     | 33.41     |  |  |  |  |

| 1   | 1                        | 1   | 83.30     | 33.32     |  |  |  |  |

Notes: \*Test Mode (all fixed clocks = XIN)

**Approved Product**

|                                                               | PIN DESCRIPTION |      |     |              |                                                                                                                                                                  |  |  |

|---------------------------------------------------------------|-----------------|------|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN<br>No.                                                    | Pin<br>Name     | PWR  | I/O | TYPE         | Description                                                                                                                                                      |  |  |

| 6                                                             | Xin             | VDD  | I   | OSC1<br>Rext | On-chip reference oscillator input pin. Requires either an external parallel resonant crystal (nominally 14.318 MHz) or externally generated reference signal    |  |  |

| 5                                                             | Xout            | VDD  | 0   | OSC1<br>Rext | On-chip reference oscillator output pin. Drives an external parallel resonant crystal when an externally generated reference signal is used, is left unconnected |  |  |

| 12, 11, 8                                                     | FS(0:2)         |      | I   | PAD          | Frequency select input pins. See frequency select table. These pins have internal pull-up resistors.                                                             |  |  |

| 52, 50,<br>49, 48                                             | CPU(1:4)        | VDDC | 0   | TB4          | Clock outputs. CPU frequency table specified.                                                                                                                    |  |  |

| 47                                                            | CPU5            | VDDC | 0   | TB4LB        | High drive CPU output clock.                                                                                                                                     |  |  |

| 29, 30,<br>31, 32,<br>34, 35,<br>36, 37,<br>42, 43,<br>44, 45 | SDR(1:12)       | VDDS | 0   | TB4          | Synchronous Dynamic RAM clock outputs.                                                                                                                           |  |  |

| 17, 18,<br>19, 20,<br>22, 23,<br>24, 25                       | PCI(1:8)        | VDD  | 0   | TB4          | PCI Bus clock outputs.                                                                                                                                           |  |  |

| 4, 10, 13,<br>21, 27,<br>33, 38,<br>41, 46                    | Vss             |      | Р   | PWR          | Ground pins for the device.                                                                                                                                      |  |  |

| 1, 7, 9,<br>14, 16,<br>26                                     | Vdd             |      | Р   | PWR          | Power supply pins for analog circuit , Fixed clocks, PCI clocks and core logic                                                                                   |  |  |

| 51                                                            | VddC            |      | Р   | PWR          | 3.3 or 2.5 volt power supply pins for CPU clock output buffers pins.                                                                                             |  |  |

| 28, 39,<br>40                                                 | VddS            |      | Р   | PWR          | 3.3 volt power supply pins for SDRAM clock output buffers pins.                                                                                                  |  |  |

| 2, 3                                                          | REF(1:2)        | VDD  | 0   | TB4          | Buffered output of on-chip reference oscillator. This pin is bidirectional.                                                                                      |  |  |

| 15                                                            | 48MHz           | VDD  | 0   | TB4          | 48 Mhz fixed frequency clock output for USB.                                                                                                                     |  |  |

**NOTE**: An external resistor must be connected between the Xin (pin 6) and Xout (pin 5) pins to insure oscilator startup. The value of this must be between 200 and 500 Kohms.

### **Approved Product**

#### **MAXIMUM RATINGS**

Voltage Relative to VSS:

Voltage Relative to VDD:

Storage Temperature:

Operating Temperature:

Maximum Power Supply:

-0.3V

0.3V

0.3V

0.3V

0.3V

0.3V

0.3V

7V

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

| ELECTRICAL CHARACTERISTICS                                      |        |     |     |     |       |                                 |

|-----------------------------------------------------------------|--------|-----|-----|-----|-------|---------------------------------|

| Characteristic                                                  | Symbol | Min | Тур | Max | Units | Conditions                      |

| Input Low Voltage                                               | VIL    | -   | -   | 0.8 | Vdc   | -                               |

| Input High Voltage                                              | VIH    | 2.0 | -   | -   | Vdc   | -                               |

| Input Low Current                                               | IIL    |     |     | -66 | μΑ    |                                 |

| Input High Current                                              | IIH    |     |     | 5   | μΑ    |                                 |

| Tri-State leakage Current                                       | loz    | -   | -   | 10  | μΑ    |                                 |

| Dynamic Supply Current                                          | ldd    | -   | -   | 175 | mA    | CPU = 66.6 MHz, PCI = 33.3 MHz  |

| Static Supply Current                                           | Isdd   | -   | -   | 75  | μΑ    | -                               |

| Short Circuit Current ISC 25 mA 1 output at a time - 30 seconds |        |     |     |     |       | 1 output at a time - 30 seconds |

| VDD = VDDS =3.3V ±5%, VDDC = 2.5V ±5%, TA = 0°C to +70°C        |        |     |     |     |       |                                 |

### **Approved Product**

|                                            | SWITCHING CHARACTERISTICS                              |      |     |              |       |                                                                  |  |  |

|--------------------------------------------|--------------------------------------------------------|------|-----|--------------|-------|------------------------------------------------------------------|--|--|

| Characteristic                             | Symbol                                                 | Min  | Тур | Max          | Units | Conditions                                                       |  |  |

| Output Duty Cycle                          | -                                                      | 45   | 50  | 55           | %     | CPU measured @ 1.25V<br>SDRAM, PCI & fixed @ 1.5 V               |  |  |

| CPU to PCI Offset                          | tOFF                                                   | -1.5 | 0   | +1.5         | ns    | 20 pf Loads, PCI measured at 1.5 V,<br>CPU measured at 1.25V     |  |  |

| Output Skew any CPU to any CPU Buffer      | Ts1                                                    | -    | -   | <u>+</u> 250 | ps    | 20 pf Load Measured at 1.25V                                     |  |  |

| Output Skew any PCI to any PCI Buffer.     | Ts2                                                    | -    | -   | <u>+</u> 500 | ps    | 20 pf Load, CPU Measured @ 1.25V,<br>SDRAM measured @ 1.5V       |  |  |

| Output Skew any SDRAM to any SDRAM Buffer. | Ts3                                                    | -    | -   | <u>+</u> 250 | ps    | 30 pf Load, Measured at 1.50V                                    |  |  |

| Output Skew any CPU to any SDRAM Buffer.   | Ts4                                                    |      |     | <u>+</u> 500 | ps    | 20 pf Load, CPU Measured @ 1.25V,<br>30 pf SDRAM measured @ 1.5V |  |  |

| ΔPeriod Adjacent Cycles                    | ΔPs                                                    |      |     | <u>+</u> 250 | ps    | Short term jitter                                                |  |  |

| ΔPeriod, Absolute                          | ΔΡΙ                                                    |      |     | <u>+</u> 500 | ps    | Long term jitter                                                 |  |  |

| V                                          | VDD = VDDS =3.3V +5%, VDDC =2.5V +5% TA = 0°C to +70°C |      |     |              |       |                                                                  |  |  |

$VDD = VDDS = 3.3V \pm 5\%$ ,  $VDDC = 2.5V \pm 5\%$ ,,, TA = 0% to +70%

| TYPE TB4LB_V BUFFER CHARACTERISTICS FOR CPU5                                              |                    |     |   |            |    |              |

|-------------------------------------------------------------------------------------------|--------------------|-----|---|------------|----|--------------|

| Characteristic Symbol Min Typ Max Units Conditions                                        |                    |     |   | Conditions |    |              |

| Pull-Up Current Min                                                                       | IOH <sub>min</sub> | 22  | - | 31         | mA | Vout = VDD5V |

| Pull-Up Current Max                                                                       | IOH <sub>max</sub> | 37  | - | 56         | mA | Vout = 1.25V |

| Pull-Down Current Min                                                                     | IOL <sub>min</sub> | 30  | - | 41         | mA | Vout = 0.4V  |

| Pull-Down Current Max                                                                     | IOL <sub>max</sub> | 75  | - | 100        | mA | Vout = 1.2V  |

| Rise & Fall Time Between 0.4 V and 2.0 V                                                  | TRF                | 0.4 | - | 2.0        | nS | 20 pF Load   |

| $VDD = VDDS = 3.3V \pm 5\%$ , $VDDC = 2.5V \pm 5\%$ , $TA = 0^{\circ}C$ to $+70^{\circ}C$ |                    |     |   |            |    |              |

| TYPE TB4 BUFFER CHARACTERISTICS FOR 48M REF(1:2), CPU (1:4), SDR (1:12), AND PCI (1:8) |                                                   |    |   |    |             |              |

|----------------------------------------------------------------------------------------|---------------------------------------------------|----|---|----|-------------|--------------|

| Characteristic                                                                         | naracteristic Symbol Min Typ Max Units Conditions |    |   |    |             |              |

| Pull-Up Current Min                                                                    | IOH <sub>min</sub>                                | 18 | - | 23 | mA          | Vout = VDD5V |

| Pull-Up Current Max                                                                    | IOH <sub>max</sub>                                | 44 | - | 64 | mA          | Vout = 1.5V  |

| Pull-Down Current Min                                                                  | $IOL_{min}$                                       | 18 | - | 25 | mA          | Vout = 0.4V  |

| Pull-Down Current Max IOL <sub>max</sub> 50 - 70 mA Vout = 1.5V                        |                                                   |    |   |    | Vout = 1.5V |              |

| Rise/Fall Time Between 0.4 V and 2.4 V TRF 0.4 - 2.0 nS 20 pF Load                     |                                                   |    |   |    |             |              |

| VDD = VDDS = 3.3V + 5%, $VDDC = 2.5V + 5%$ , $TA = 0%$ to $+70%$                       |                                                   |    |   |    |             |              |

**Approved Product**

| CRYSTAI                              | L AND RE   | CRYSTAL AND REFERENCE OSCILLATOR PARAMETERS |          |         |       |                                                                       |  |  |

|--------------------------------------|------------|---------------------------------------------|----------|---------|-------|-----------------------------------------------------------------------|--|--|

| Characteristic                       | Symbol     | Min                                         | Тур      | Max     | Units | Conditions                                                            |  |  |

| Frequency                            | Fo         | 12.00                                       | 14.31818 | 16.00   | MHz   |                                                                       |  |  |

| Shunt Resistor                       | Rs         | 200                                         | 470      | 510     | Kohms | Must be connected between Xin and Xout pin to ensure correct startup. |  |  |

| Tolerance                            | TC         | -                                           | -        | +/-100  | PPM   | Calibration note 1                                                    |  |  |

|                                      | TS         | -                                           | -        | +/- 100 | PPM   | Stability (Ta -10 to +60C) note 1                                     |  |  |

|                                      | TA         | -                                           | -        | 5       | PPM   | Aging (first year @ 25C) note 1                                       |  |  |

| Mode                                 | OM         | -                                           | -        | -       |       | Parallel Resonant                                                     |  |  |

| Pin Capacitance                      | СР         |                                             | 5        |         | pF    | Capacitance of XIN and Xout pins                                      |  |  |

| DC Bias Voltage                      | $V_{BIAS}$ | 0.3Vdd                                      | Vdd/2    | 0.7Vdd  | V     |                                                                       |  |  |

| Startup time                         | Ts         | -                                           | -        | 30      | μS    |                                                                       |  |  |

| Load Capacitance                     | CL         | -                                           | 18       | -       | pF    | note 1                                                                |  |  |

| Effective Series resonant resistance | R1         | -                                           | -        | 40      | Ohms  |                                                                       |  |  |

| Power Dissipation                    | DL         | -                                           | -        | 0.10    | mW    | note 1                                                                |  |  |

| Shunt Capacitance                    | CO         | -                                           |          | 7       | pF    |                                                                       |  |  |

For maximum accuracy, the total circuit loading capacitance should be equal to CL. This loading capacitance is the effective capacitance across the crystal pins and includes the device pin capacitance (CP) in parallel with any circuit traces, the clock generator and any onboard discrete load capacitors. Typical trace capacitance, for traces less than a half inch are 4 pF. with an internal pin capacitance of 5 pF the total parasitic capacitance would be 9 pF. It this instance a 27 pF capacitor added to both legs (pins) of the crystal would bring its total load the recommended 18 pF CL pF each leg) that the crystal was calibrated to operate at.

Note 1: It is recommended but not mandatory chooses a crystal that meets these specifications.

**Approved Product**

#### PROGRAMMABLE CPU TO PCI CLOCK TIMING.

The IMISC608 features programmable CPU to PCI clock skew feature. With this feature the PCI clock can be retarded or advanced with respect to the CPU clock to permit the user the ability to adjust critical timing on a specific motherboard design. There are 4 values of skew available in this feature. They are shown in the following table. a + value indicated that the PCI clock lead or transitions before the CPU clock in time while a - value indicated that the PCI lock transitions or changes after the CPU clock has. This feature is accessible through the REF1 and REF2 clock output pins. As such they are implemented as bidirectional pins. This implementation as described below. With no programming resistors used the default table value 11 is selected causing 0 offset.

| PROGRAMMABLE CPU TO PCI CLOCK SKEW TABLE |          |                                                      |  |  |  |

|------------------------------------------|----------|------------------------------------------------------|--|--|--|

| SS0/REF1                                 | SS1/REF2 | Effect                                               |  |  |  |

| 0                                        | 0        | CPU clocks lags PCI clocks (PCI early) by 500 pSec   |  |  |  |

| 1                                        | 0        | CPU clocks leads PCI clocks (CPU early) by 1500 pSec |  |  |  |

| 0                                        | 1        | CPU clocks leads PCI clocks (CPU early) by 1000 pSec |  |  |  |

| 1                                        | 1        | CPU clocks lags PCI clocks (PCI early) by 250 pSec   |  |  |  |

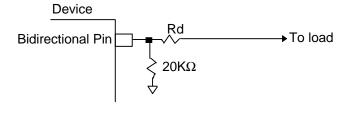

### SELECTION ON BI-DIRECTIONAL PINS

Bi-directional pins and are used for selecting different functions in this device (see Pin description, Page 2). During power-up of the device, these pins are in input mode and therefore, they are considered input select pins. Internal to the IC, these pins have a large value pull-up each ( $100K\Omega$ ), therefore, a selection "1" is the default. If a selection "0" is desired, then a direct connection to ground through a  $10K\Omega$  resistor should be implemented as shown in Fig. 3. Please note the selection resistor ( $10K\Omega$ ) is placed before the Damping resistor (Rd) and close to the devices pin.

Fig. 3

Approved Product

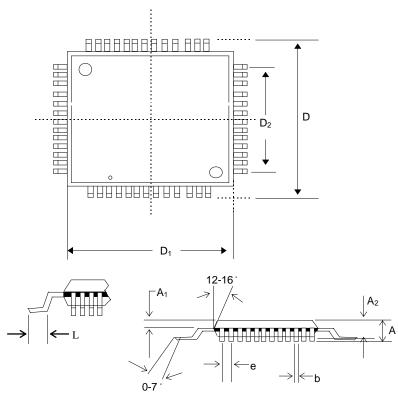

### PACKAGE DRAWING AND DIMENSIONS

| 52 PIN QFP OUTLINE DIMENSIONS |       |           |       |             |          |       |  |

|-------------------------------|-------|-----------|-------|-------------|----------|-------|--|

|                               |       | INCHES    |       | MILLIMETERS |          |       |  |

| SYMBOL                        | MIN   | NOM       | MAX   | MIN         | NOM      | MAX   |  |

| Α                             | -     | 0.084     | 0.093 | -           | 2.13     | 2.35  |  |

| A <sub>1</sub>                | 0.03  | .006      | .010  | 0.10        | 0.15     | 0.25  |  |

| A <sub>2</sub>                | 0.077 | 0.079     | 0.083 | 1.95        | 2.00     | 2.10  |  |

| D                             | 0.537 | 0.547     | 0.557 | 13.65       | 13.90    | 14.15 |  |

| D <sub>1</sub>                | 0.390 | 0.394     | 0.398 | 9.90        | 10.00    | 10.10 |  |

| $D_2$                         |       | 0.307 REI | =     |             | 7.80 REF | -     |  |

| b                             | 0.009 | -         | 0.015 | 0.22        | -        | 0.38  |  |

| е                             |       | .0256 BS0 | 2     | (           | 0.65 BSC | ;     |  |

| L                             | 0.026 | 0.031     | 0.037 | 0.65        | 0.80     | 0.95  |  |

| ORDERING INFORMATION     |  |                          |  |  |

|--------------------------|--|--------------------------|--|--|

| Part Number Package Type |  | Production Flow          |  |  |

| IMISC608AAB 52 PIN QFP   |  | Commercial, 0°C to +70°C |  |  |

The ordering part number is formed by a combination of device number, device revision, package style, and Note: screening as shown below.

Marking: Example:

SC608AAB, Date Code, Lot #

IMISC608AAB  $B = Commercial, 0^{\circ}C to + 70^{\circ}C$ <u>Package</u> A = QFPRevision **IMI Device Number**