## $\mu\text{P}$ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

#### **FEATURES**

- ♦ 2 × 4 bidirectional input/output stages at 24V

- ♦ Input/output mode programmable in 4-bit blocks

- Guaranteed high-side driving capability of 100mAdc and 500mApeak for pulse load

- ♦ Short-circuit-proof drivers with high dielectric strength

- ◆ Low saturation voltage of 0.6V/100mA and 2.0V/500mA

- Integrated flyback circuits

- PWM function with programmable duty cycle

- ♦ Flash mode for the outputs

- Power outputs can be disabled together

- Programmable current sources define logic levels and allow load monitoring

- Digital input filters with externally adjustable filtering times

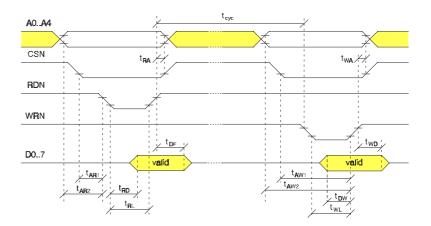

- Can be bus operated due to the high-speed μP interface

- Programmable interrupt output

- Voltage and two-stage temperature monitoring

#### **APPLICATIONS**

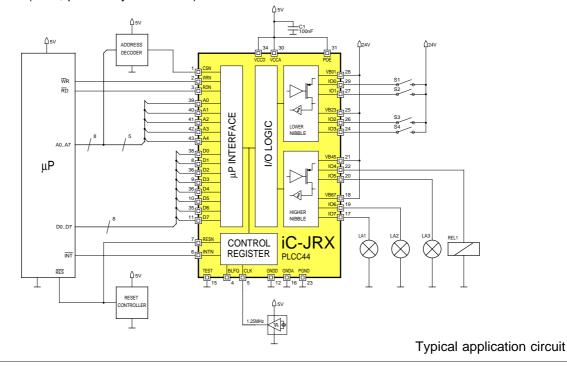

Dual quad high-side driver as a bidirectional μP interface with digital filtering in industrial 24V applications

#### **PACKAGES**

PLCC44

iC-Haus GmbH Integrated Circuits Am Kuemmerling 18, 55294 Bodenheim Tel. +49-6135-9292-0 Fax +49-6135-9292-192 http://www.ichaus.com

### μP INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 2/23

#### **DESCRIPTION**

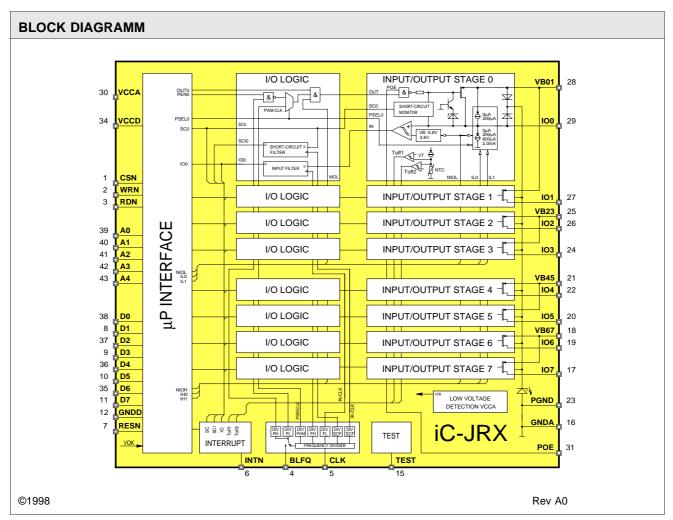

iC-JRX is an 8-fold high-side driver with integrated control logic, internally divided into two independent blocks (nibbles). Both blocks can be individually set to input or output. The  $\mu P$  interface is made up of eight data, five address and three control pins. Two further clock inputs control internal sequences (input filter, pulse operation of the outputs). Starting with reset state, various register partitionings dependent on the selected operating mode are possible.

Input mode is used to log logic levels at 24V. An interrupt message can be generated when a signal at the inputs changes. Spurious signals are rejected by the device's adjustable digital filters. When the inputs are open the programmable pull-down current sets defined levels and acts as the bias current for switching contacts.

In output mode the power output stages can drive any desired load to GND (e.g. lamps, long cables or relays) at a continuous current of 100mA or 500mA in pulse operation. Spikes and flyback currents are discharged through the integrated flyback circuits. All output stages are short-circuit-proof and two-stage temperature monitoring (with interrupt messages) protects against thermal damage caused by large power dissipation. A short circuit at one of the outputs can cause an interrupt; the current short circuit status can be scanned via the  $\mu P$  interface. Pulse mode can be selected for each output, such as for indicator lamps in plugboards, in order to offload the control software used. The actual switching level of the output can be read out via the  $\mu P$  interface and be used to check for cable fractures with the pull-up currents. A PWM signal can also be switched to any selected output. All outputs can be switched off via a mutual disable input e.g. by a processor-independent watchdog circuit.

An interrupt pipeline which prevents the loss of interrupts allows reliable processing of interrupts using the applied control software.

With low voltage the voltage monitor resets all registers and in doing so switches off the power output stages.

Diodes protect all inputs and outputs against ESD. The device is also immune to burst transients according to IEC 1000-4-4 (4 kV; previously IEC 801-4).

# $\mu\text{P}$ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 3/23

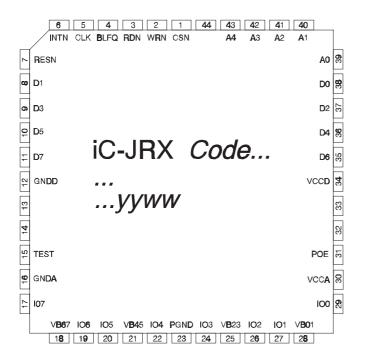

#### PACKAGES PLCC44 to JEDEC Standard

#### **PIN CONFIGURATION PLCC44**

(top view)

#### **PIN FUNCTIONS PLCC44**

| No. | Name | Fct. | Description                   | No. | Name | Fct. | Description                         |

|-----|------|------|-------------------------------|-----|------|------|-------------------------------------|

| 1   | CSN  | I    | Chip Select                   | 23  | PGND |      | Ground (ESD protection circuitry)   |

| 2   | WRN  | I    | Write Enable                  | 24  | IO3  | В    | I/O Stage 3                         |

| 3   | RDN  | 1    | Read Enable                   | 25  | VB23 |      | Power Supply Driver Stage 2+3       |

| 4   | BLFQ | 1    | Clock Flash Mode              | 26  | 102  | В    | I/O Stage 2                         |

| 5   | CLK  | I    | Clock Filter and PWM Function | 27  | IO1  | В    | I/O Stage 1                         |

| 6   | INTN | 0    | Interrupt Message             | 28  | VB01 |      | Power Supply Driver Stage 0+1       |

| 7   | RESN | I    | Reset                         | 29  | 100  | В    | I/O Stage 0                         |

| 8   | D1   | В    | Data Bus Bit 1                | 30  | VCCA |      | 5V Supply Voltage (analog section)  |

| 9   | D3   | В    | Data Bus Bit 3                | 31  | POE  | 1    | Power Output Enable                 |

| 10  | D5   | В    | Data Bus Bit 5                | 32  | n.c. |      | ·                                   |

| 11  | D7   | В    | Data Bus Bit 7                | 33  | n.c. |      |                                     |

| 12  | GNDD |      | Ground (digital section)      | 34  | VCCD |      | 5V Supply Voltage (digital section) |

| 13  | n.c. |      | ,                             | 35  | D6   | В    | Data Bus Bit 6                      |

| 14  | n.c. |      |                               | 36  | D4   | В    | Data Bus Bit 4                      |

| 15  | TEST | В    | Test Pin                      | 37  | D2   | В    | Data Bus Bit 2                      |

| 16  | GNDA |      | Ground (analog section)       | 38  | D0   | В    | Data Bus Bit 0                      |

| 17  | 107  | В    | I/O Stage 7                   | 39  | A0   | 1    | Address Bus Bit 0                   |

| 18  | VB67 |      | Power Supply Driver Stage 6+7 | 40  | A1   | 1    | Address Bus Bit 1                   |

| 19  | 106  | В    | I/O Stage 6                   | 41  | A2   | 1    | Address Bus Bit 2                   |

| 20  | IO5  | В    | I/O Stage 5                   | 42  | A3   | 1    | Address Bus Bit 3                   |

| 21  | VB45 |      | Power Supply Driver Stage 4+5 | 43  | A4   | 1    | Address Bus Bit 4                   |

| 22  | 104  | В    | I/O Stage 4                   | 44  | n.c. |      |                                     |

|     |      |      | ŭ                             |     |      |      |                                     |

Functions: I= Input, O= Output, B= bidirectional

External wiring VCCA, VCCD to +5V and GNDA, GNDD, PGND to 0V required.

# $\mu\text{P}$ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 4/23

#### **PROGRAMMING**

| Registe | r Ove | ervie | w  |    |    |                                 |                                      |  |  |  |  |  |

|---------|-------|-------|----|----|----|---------------------------------|--------------------------------------|--|--|--|--|--|

|         |       | Addre |    |    |    |                                 |                                      |  |  |  |  |  |

| A(40)d  | A4    | АЗ    | A2 | A1 | A0 | Write                           | Read                                 |  |  |  |  |  |

| 0       | 0     | 0     | 0  | 0  | 0  | -                               | Input Register 1                     |  |  |  |  |  |

| 1       | 0     | 0     | 0  | 0  | 1  | -                               | Change-of-input Message <sup>2</sup> |  |  |  |  |  |

| 2       | 0     | 0     | 0  | 1  | 0  | -                               | Interrupt Status Register            |  |  |  |  |  |

| 3       | 0     | 0     | 0  | 1  | 1  | -                               | Overcurrent Message <sup>3</sup>     |  |  |  |  |  |

| 4       | 0     | 0     | 1  | 0  | 0  | -                               | Overcurrent Status                   |  |  |  |  |  |

| 5       | 0     | 0     | 1  | 0  | 1  | -                               | Device ID                            |  |  |  |  |  |

| 6       | 0     | 0     | 1  | 1  | 0  | Output                          | Output Register                      |  |  |  |  |  |

| 7       | 0     | 0     | 1  | 1  | 1  | Flash Pu                        | lse Enable                           |  |  |  |  |  |

| 8       | 0     | 1     | 0  | 0  | 0  | Change-of-input                 | Interrupt Enable <sup>4</sup>        |  |  |  |  |  |

| 9       | 0     | 1     | 0  | 0  | 1  | Overcurrent In                  | Overcurrent Interrupt Enable         |  |  |  |  |  |

| 10      | 0     | 1     | 0  | 1  | 0  | Control Word                    | d 1 (I/O filters)                    |  |  |  |  |  |

| 11      | 0     | 1     | 0  | 1  | 1  | Control Word 2                  | (I/O pin functions)                  |  |  |  |  |  |

| 12      | 0     | 1     | 1  | 0  | 0  | Control Word 3 (fl              | lash pulse settings)                 |  |  |  |  |  |

| 13      | 0     | 1     | 1  | 0  | 1  | Control World 4 (filter setting | ngs for overcurrent message)         |  |  |  |  |  |

| 14      | 0     | 1     | 1  | 1  | 0  | Control Word 5 (PWM e           | enable and pin selection)            |  |  |  |  |  |

| 15      | 0     | 1     | 1  | 1  | 1  | PWM I                           | Register                             |  |  |  |  |  |

| 16      | 1     | 0     | 0  | 0  | 0  |                                 | -                                    |  |  |  |  |  |

|         |       |       |    |    |    |                                 | -                                    |  |  |  |  |  |

| 26      | 1     | 1     | 0  | 1  | 0  |                                 | -                                    |  |  |  |  |  |

| 27      | 1     | 1     | 0  | 1  | 1  | -                               | A/D Interface                        |  |  |  |  |  |

| 28      | 1     | 1     | 1  | 0  | 0  | Test Ro                         | Test Register 1                      |  |  |  |  |  |

| 29      | 1     | 1     | 1  | 0  | 1  | Test Ro                         | Test Register 2                      |  |  |  |  |  |

| 30      | 1     | 1     | 1  | 1  | 0  | Test Ro                         | egister 3                            |  |  |  |  |  |

| 31      | 1     | 1     | 1  | 1  | 1  | Test Cont                       | rol Register                         |  |  |  |  |  |

Reads the inputs or reads back the outputs, depending on I/O pin mode

For I/O pins in input mode (register is '0' in output mode)

For I/O pins in output mode (register is '0' in input mode)

<sup>&</sup>lt;sup>4</sup>) Only writable in input mode

# $\mu\text{P}$ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 5/23

| Control      | Control Word 1 (I/O filters) Add.: 10 |      |          |          |              |     |          |          |  |  |  |  |

|--------------|---------------------------------------|------|----------|----------|--------------|-----|----------|----------|--|--|--|--|

| reset entry: |                                       |      |          |          |              |     |          |          |  |  |  |  |

|              | higher nil                            | bble |          |          | lower nibble |     |          |          |  |  |  |  |

| Bit<br>Name  | 7<br>BYPH                             | 6 -  | 5<br>FH1 | 4<br>FH0 | 3<br>BYPL    | 2 - | 1<br>FL1 | 0<br>FL0 |  |  |  |  |

#### higher nibble

| Bit 7<br>BYPH | 0 | I/O filters a<br>Bypass for |     | the I/O signals are re   | processed in their unfiltered state. | (r) |

|---------------|---|-----------------------------|-----|--------------------------|--------------------------------------|-----|

| Bit 54        |   | FH1                         | FH0 | Filter times             |                                      |     |

| FH10          |   | 0                           | 0   | 14,5 × tc(CLK)           | ± 1 × tc(CLK)                        |     |

|               |   | 0                           | 1   | 896,5 × tc(CLK)          | $\pm$ 64 $\times$ tc(CLK)            |     |

|               |   | 1                           | 0   | $3.584,5 \times tc(CLK)$ | $\pm$ 256 $\times$ tc(CLK)           |     |

|               |   | 1                           | 1   | $7.168,5 \times tc(CLK)$ | $\pm$ 512 $\times$ tc(CLK)           |     |

#### lower nibble

| Bit 3<br>BYPL | 0 | I/O filters a<br>Bypass for |     | (r) he I/O signals are reprocessed in their unfiltered state. |                            |     |  |  |  |  |

|---------------|---|-----------------------------|-----|---------------------------------------------------------------|----------------------------|-----|--|--|--|--|

| Bit 10        |   | FL1                         | FL0 | Filter times                                                  |                            |     |  |  |  |  |

| FL10          |   | 0                           | 0   | 14,5 × tc(CLK)                                                | $\pm$ 1 $\times$ tc(CLK)   | (r) |  |  |  |  |

|               |   | 0                           | 1   | 896,5 × tc(CLK)                                               | $\pm$ 64 $\times$ tc(CLK)  |     |  |  |  |  |

|               |   | 1                           | 0   | 3.584,5 × tc(CLK)                                             | $\pm$ 256 $\times$ tc(CLK) |     |  |  |  |  |

|               |   | 1                           | 1   | $7.168,5 \times tc(CLK)$                                      | $\pm$ 512 $\times$ tc(CLK) |     |  |  |  |  |

'-' Free memory location without a function. Status after a reset is '0' 'xx'h Indicates hexadecimal data for logic states. 'x' indicates binary data

(r) Status after a reset

# μP INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 6/23

| Control      | Control Word 2 (I/O pin functions) Add.: 11 |      |          |          |           |              |          |          |  |  |  |  |

|--------------|---------------------------------------------|------|----------|----------|-----------|--------------|----------|----------|--|--|--|--|

| reset entry: |                                             |      |          |          |           |              |          |          |  |  |  |  |

|              | higher ni                                   | bble |          |          | lower nil | lower nibble |          |          |  |  |  |  |

| Bit<br>Name  | 7<br>NIOH                                   | 6 -  | 5<br>IH1 | 4<br>IH0 | 3<br>NIOL | 2 -          | 1<br>IL1 | 0<br>ILO |  |  |  |  |

### higher nibble

| Bit 7 0 Input mode Output mode |  |                  |                  |                                     |                                       |     |  |  |  |

|--------------------------------|--|------------------|------------------|-------------------------------------|---------------------------------------|-----|--|--|--|

| Bit 54                         |  | Current sou      | rces at I/O p    | pins 47                             |                                       |     |  |  |  |

| IH10                           |  | IH1              |                  | in input mode<br>(sources low-side) | in output mode<br>(sources high-side) |     |  |  |  |

|                                |  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0μΑ<br>200μΑ<br>600μΑ<br>2mA        | 0μΑ<br>200μΑ<br>0μΑ<br>200μΑ          | (r) |  |  |  |

#### lower nibble

| Bit 3<br>NIOL | 0 | Input mode<br>Output mod |                   |                                     |                                       |     |

|---------------|---|--------------------------|-------------------|-------------------------------------|---------------------------------------|-----|

| Bit 10        |   | Current so               | urces at I/O pins | s 03                                |                                       |     |

| IL10          |   | IL1 IL0                  |                   | in input mode<br>(sources low-side) | in output mode<br>(sources high-side) |     |

|               |   | 0                        | 0<br>1            | 0μΑ<br>200μΑ                        | 0μA<br>200μA                          |     |

|               |   | 1                        | 0<br>1            | 600μA<br>2mA                        | 0μA<br>200μA                          | (r) |

# μP INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 7/23

| Control     | Control Word 3 (flash pulse settings)  Add.: 12 |            |          |          |              |     |          |          |  |  |  |  |

|-------------|-------------------------------------------------|------------|----------|----------|--------------|-----|----------|----------|--|--|--|--|

| reset enti  |                                                 |            |          |          |              |     |          |          |  |  |  |  |

|             | higher nibb                                     | ole        |          |          | lower nibble |     |          |          |  |  |  |  |

| Bit<br>Name | 7<br>NOBLFQ                                     | 6<br>NOCLK | 5<br>PH1 | 4<br>PH0 | 3 -          | 2 - | 1<br>PL1 | 0<br>PL0 |  |  |  |  |

### higher nibble

| Bit 7 0 Flash pulse is generated from the external clock signal at BLFQ NOBLFQ 1 Flash Pulse is generated from clock signal CLK |  |             |                                 |              |     |                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|-------------|---------------------------------|--------------|-----|--------------------------|--|--|--|--|

| Bit 6                                                                                                                           |  |             |                                 |              |     |                          |  |  |  |  |

| Bit 54                                                                                                                          |  | Flash frequ | Flash frequency for I/O pins 47 |              |     |                          |  |  |  |  |

| PH10                                                                                                                            |  | PH1         | PH0                             | NOBLFQ= 0    |     | NOBLFQ= 1                |  |  |  |  |

|                                                                                                                                 |  | 0           | 0                               | f(BLFQ)      |     | f(CLK) / 2 <sup>19</sup> |  |  |  |  |

|                                                                                                                                 |  | 0           | 1                               | f(BLFQ) / 2  |     | f(CLK) / 2 <sup>20</sup> |  |  |  |  |

|                                                                                                                                 |  | 1           | 0                               | f(BLFQ) / 4  |     | f(CLK) / 2 <sup>21</sup> |  |  |  |  |

|                                                                                                                                 |  | 1           | 1                               | f(BLFQ) / 16 | (r) | f(CLK) / 2 <sup>23</sup> |  |  |  |  |

#### lower nibble

| Bit 10 | Flash frequency for I/O pins 03 |     |              |                              |  |  |  |  |  |

|--------|---------------------------------|-----|--------------|------------------------------|--|--|--|--|--|

| PL10   | PL1                             | PL0 | NOBLFQ= 0    | NOBLFQ= 1                    |  |  |  |  |  |

|        | 0                               | 0   | f(BLFQ)      | f(CLK) / 2 <sup>19</sup>     |  |  |  |  |  |

|        | 0                               | 1   | f(BLFQ) / 2  | f(CLK) / 2 <sup>20</sup>     |  |  |  |  |  |

|        | 1                               | 0   | f(BLFQ) / 4  | f(CLK) / 2 <sup>21</sup>     |  |  |  |  |  |

|        | 1                               | 1   | f(BLFQ) / 16 | (r) f(CLK) / 2 <sup>23</sup> |  |  |  |  |  |

| Control \ | Control Word 4 (filter settings for overcurrent message) Add.: 13 |   |   |      |        |   |   |      |  |  |  |  |

|-----------|-------------------------------------------------------------------|---|---|------|--------|---|---|------|--|--|--|--|

|           | reset entry: 00h                                                  |   |   |      |        |   |   |      |  |  |  |  |

| Bit       | 7                                                                 | 6 | 5 | 4    | 3      | 2 | 1 | 0    |  |  |  |  |

| Name      | EOI                                                               | - | - | SCFH | BYPSCF | - | - | SCFL |  |  |  |  |

| Bit 7           | 0 | No effect                                                                                                                                                                                                       | (r)  |

|-----------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| EOI             | 1 | "DELETE"s the interrupt message (change-of-input message; interrupt status register, overcurrent message), accepts successive interrupts from the pipeline, deletes the message at INTN when the pipe is empty; | line |

|                 |   | Bit automatically resets to '0'.                                                                                                                                                                                |      |

| Bit 4<br>SCFH   | 0 | Overcurrent message with 2.3ms filtering (higher nibble) Overcurrent message with 4.6ms Filtering (higher nibble)                                                                                               | (r)  |

|                 |   | Gives the filter times with the maximum clock frequency permitted at CLK, i.e. 1.25 MHz: 2.3ms from (2689,5 $\pm$ 192)× t(CLK) and 4.6ms from (5378,5 $\pm$ 384) × t(CLK) respectively                          |      |

| Bit 3<br>BYPSCF | 0 | Filters for the overcurrent message are active Bypass for the filters: overcurrent messages are reprocessed in their unfiltered state                                                                           | (r)  |

| Bit 0<br>SCFL   | 0 | Overcurrent message with 2.3ms filtering (lower nibble) Overcurrent message with 4.6ms filtering (lower nibble)                                                                                                 | (r)  |

# μΡ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 8/23

| Control V      | Nord 5 | (PWM enable and                                | d pin selectio        | n)                    |                                            |                    |                    | Add.: 14           |

|----------------|--------|------------------------------------------------|-----------------------|-----------------------|--------------------------------------------|--------------------|--------------------|--------------------|

|                |        |                                                |                       |                       |                                            |                    | res                | set entry: 00h     |

| Bit<br>Name    | 7 -    | 6 -                                            | 5 -                   | 4<br>PWMEN            | 3<br>PWMPN                                 | 2<br>PWM<br>ADR(2) | 1<br>PWM<br>ADR(1) | 0<br>PWM<br>ADR(0) |

| Bit 4<br>PWMEN | 0      | PWM "DISABLE<br>PWM "ENABLE<br>sources are swi | D": the output s      | elected with P\       | VMADR receiv                               | ves the PWM s      | ignal. The relev   | (r) ant current    |

| Bit 3<br>PWMPN | 0      | PWM signal act<br>PWM signal act               |                       |                       |                                            |                    |                    | (r)                |

| Bit 20         |        | PWMADR2                                        | PWMADR1               | PWMADRO               | Selected I                                 | /O pin             |                    |                    |

| PWMADR 2       | 20     | 1111                                           | 0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0 | IO0 (cr<br>IO1<br>IO2<br>IO3<br>IO4<br>IO5 | ontrol line PSE    | L0= 1)             |                    |

| PWM Re          | gister                |                 |                                               |                  |                |                |                 | Add.: 15          |

|-----------------|-----------------------|-----------------|-----------------------------------------------|------------------|----------------|----------------|-----------------|-------------------|

|                 |                       |                 |                                               |                  |                |                | re              | set entry: 00h    |

| Bit<br>Name     | 7<br>PWM7             | 6<br>PWM6       | 5<br>PWM5                                     | 4<br>PWM4        | 3<br>PWM3      | 2<br>PWM2      | 1<br>PWM1       | 0<br>PWM0         |

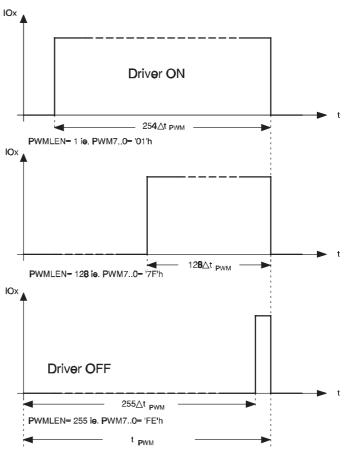

| Bit 70<br>PWM70 | '00'h<br>''h<br>'FF'h | Duration of the | OFF" (continous PWM signal in CON" (continous | n steps of 16× t | t(CLK)         |                |                 | (r)               |

|                 |                       | The PWM reg     |                                               | s the pulse leng | gth of the PWM | signal. Output | selection and e | nable are set via |

106 107

# μΡ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 9/23

|                | egister (reads) | ad only)<br>output feedba | ack                         |                    |            |          |          | Add.: 0         |

|----------------|-----------------|---------------------------|-----------------------------|--------------------|------------|----------|----------|-----------------|

|                |                 |                           |                             |                    |            |          | !        | eset entry: 00h |

| Bit<br>Name    | 7<br>IN7        | 6<br>IN6                  | 5<br>IN5                    | 4<br>IN4           | 3<br>IN3   | 2<br>IN2 | 1<br>IN1 | 0<br>INO        |

| Bit 70<br>IN70 | 0               | Input/Output              | IOx reads '0' IOx reads '1' | Ox (via I/O filter | or hypaca) |          |          | (r)             |

| es in inpu | essage (read<br>ut mode         | only)                                                                                             |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     | Add.: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|---------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                 |                                                                                                   |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                          | re                                                                                                                                                                                                                                                                                                                                                                                                  | set entry: 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7<br>DCH7  | 6<br>DCH6                       | 5<br>DCH5                                                                                         | 4<br>DCH4                                                                                                                                                                                                | 3<br>DCH3                                                                                                                                                                                                                                                                                                 | 2<br>DCH2                                                                                                                                                                                                                                                                                                                                                                                                | 1<br>DCH1                                                                                                                                                                                                                                                                                                                                                                                           | 0<br>DCH0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0          |                                 |                                                                                                   |                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                                                                         | nessages                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                     | (r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|            | successive int interrupt pipeli | errupts which c<br>ine. If this happ                                                              | occur during the ens, the messa                                                                                                                                                                          | read-out phasinge at INTN car                                                                                                                                                                                                                                                                             | e and before a<br>nnot be deleted                                                                                                                                                                                                                                                                                                                                                                        | reset with EOI a<br>by EOI, i.e. IN                                                                                                                                                                                                                                                                                                                                                                 | are trapped by ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                                 | DCH7  DCH6  No change of Input IOx has  Read access successive intinterrupt pipeli remains on low | DCH7  DCH6  DCH5  No change of state at the inp Input IOx has had a change of Read access gates off chang successive interrupts which of interrupt pipeline. If this happ remains on low. In this instan | DCH7  DCH6  DCH5  DCH4  No change of state at the input IOx or no int Input IOx has had a change of state enabled Read access gates off changes to the regist successive interrupts which occur during the interrupt pipeline. If this happens, the messa remains on low. In this instance, EOI fills the | DCH7  DCH6  DCH5  DCH4  DCH3  O No change of state at the input IOx or no interrupt enable Input IOx has had a change of state enabled for interrupt makes access gates off changes to the register; the register successive interrupts which occur during the read-out phase interrupt pipeline. If this happens, the message at INTN car remains on low. In this instance, EOI fills the change-of-inp | DCH7  DCH6  DCH5  DCH4  DCH3  DCH2   No change of state at the input IOx or no interrupt enable Input IOx has had a change of state enabled for interrupt messages  Read access gates off changes to the register; the register is reenabled or successive interrupts which occur during the read-out phase and before a interrupt pipeline. If this happens, the message at INTN cannot be deleted | 7 DCH7  6 DCH6  5 DCH5  4 DCH4  3 DCH3  2 DCH2  DCH1  0 No change of state at the input IOx or no interrupt enable Input IOx has had a change of state enabled for interrupt messages  Read access gates off changes to the register; the register is reenabled only when reset a successive interrupts which occur during the read-out phase and before a reset with EOI interrupt pipeline. If this happens, the message at INTN cannot be deleted by EOI, i.e. INT remains on low. In this instance, EOI fills the change-of-input message from the pipeline. |

# μΡ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 10/23

| Interrup    | t Status Reg  | gister (read | only)     |           |              |          |          | Add.: 2         |

|-------------|---------------|--------------|-----------|-----------|--------------|----------|----------|-----------------|

|             |               |              |           |           |              |          | r        | eset entry: 00h |

|             | higher nibble |              |           |           | lower nibble |          |          |                 |

| Bit<br>Name | 7<br>DCHI     | 6<br>IET2    | 5<br>IET1 | 4<br>ISCI | 3 -          | 2<br>ET2 | 1<br>ET1 | 0<br>SCS        |

### higher nibble

| overcurr      | ent, exces | ssive temperature, change-of-input data (interrupts stored)                                                                                                                                                                                                                                                                                                                                                           |     |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|               |            | Read access gates off changes to the register; the register is reenabled only when reset via EOI. Any successive interrupts for IET1 and IET2 which occur during the read-out phase and before a reset wit EOI are trapped (pipeline). If this happens, the message at INTN cannot be deleted by EOI, i.e. INTN constantly remains on low. In this instance, EOI fills the excessive temperatue message from the pipe | h   |

| Bit 7<br>DCHI | 0          | No message<br>Interrupt through change-of-input message                                                                                                                                                                                                                                                                                                                                                               | (r) |

| Bit 6<br>IET2 | 0          | No message<br>Interrupt through excessive temperature level 2                                                                                                                                                                                                                                                                                                                                                         | (r) |

| Bit 5<br>IET1 | 0          | No message Interrupt through excessive temperature level 1                                                                                                                                                                                                                                                                                                                                                            | (r) |

| Bit 4<br>ISCI | 0          | No message Interrupt through overcurrent message                                                                                                                                                                                                                                                                                                                                                                      | (r) |

#### lower nibble

| overcurr     | ent status | s, excessive temperature status (real time signals, at the time of readout)    |     |

|--------------|------------|--------------------------------------------------------------------------------|-----|

| Bit 2<br>ET2 | 0          | No error message<br>Excessive temperature level 2 (shutdown)                   | (r) |

| Bit 1<br>ET1 | 0          | No error message<br>Excessive temperature level 1 (warning)                    | (r) |

| Bit 0<br>SCS | 0          | No error message<br>Overcurrent status (e.g. caused by low-side short circuit) | (r) |

| Overcur         | rent Messa | age (read onl                                                   | y)                                                                                            |                                                                            |                                                    |                 |                                                        | Add.: 3         |

|-----------------|------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|-----------------|--------------------------------------------------------|-----------------|

|                 |            |                                                                 |                                                                                               |                                                                            |                                                    |                 | re                                                     | eset entry: 00h |

| Bit<br>Name     | 7<br>SCI7  | 6<br>SCI6                                                       | 5<br>SCI5                                                                                     | 4<br>SCI4                                                                  | 3<br>SCI3                                          | 2<br>SCI2       | 1<br>SCI1                                              | 0<br>SCI0       |

| Bit 70<br>SCI70 | 0 1        | Read access<br>successive ir<br>an interrupt p<br>remains on lo | gates off chan-<br>terrupts which<br>ipeline. If this how. In this insta<br>or IOx pins in ir | ges to the regis<br>occur during th<br>nappens, the m<br>nce, EOI fills th | ster; the registe<br>e read-out phasessage at INTN | se and before a | only when reset<br>reset with EOI<br>eted by EOI, i.e. | •               |

# μP INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 11/23

| Overcur        | rent Statu | s (read only) |                  |                 |                |                    |                  | Add.: 4         |

|----------------|------------|---------------|------------------|-----------------|----------------|--------------------|------------------|-----------------|

|                |            |               |                  |                 |                |                    | r                | eset entry: 00h |

| Bit<br>Name    | 7<br>SC7   | 6<br>SC6      | 5<br>SC5         | 4<br>SC4        | 3<br>SC3       | 2<br>SC2           | 1<br>SC1         | 0<br>SC0        |

| Bit 70<br>SC70 | 0          | This signal a | in output IOx, e | alysis and does | not generate a | any interrupts (re | eal time, no reç | gister).        |

| Device I        | dentificat | ion (read on | ly)                                     |           |           |           |           | Add.: 5         |

|-----------------|------------|--------------|-----------------------------------------|-----------|-----------|-----------|-----------|-----------------|

|                 |            |              |                                         |           |           |           | re        | eset entry: 00h |

| Bit<br>Name     | 7 -        | 6 -          | 5<br>DID5                               | 4<br>DID4 | 3<br>DID3 | 2<br>DID2 | 1<br>DID1 | 0<br>DID0       |

| Bit 50<br>DID50 |            |              | · iC-JRX: '00 0000<br>vith RESN= '0' an | ` ,       | tage      |           |           | (r)             |

| Output-R        |           | utput function | n                            |           |           |           |           | Add.: 6        |

|-----------------|-----------|----------------|------------------------------|-----------|-----------|-----------|-----------|----------------|

|                 |           |                |                              |           |           |           | re        | set entry: 00h |

| Bit<br>Name     | 7<br>OUT7 | 6<br>OUT6      | 5<br>OUT5                    | 4<br>OUT4 | 3<br>OUT3 | 2<br>OUT2 | 1<br>OUT1 | 0<br>OUT0      |

| Bit 70<br>OUT70 | 0         |                | er "OFF"<br>er "ON", i.e. no | -         | ,         |           |           | (r)            |

|                                                                   |           |                                                | Flash Pulse Enable for I/O stages with output function         |                                               |                                                                          |                                                                               |                |  |  |  |  |

|-------------------------------------------------------------------|-----------|------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|--|--|--|--|

|                                                                   |           |                                                |                                                                |                                               |                                                                          | re                                                                            | set entry: 00h |  |  |  |  |

| 7<br>PEN7                                                         | 6<br>PEN6 | 5<br>PEN5                                      | 4<br>PEN4                                                      | 3<br>PEN3                                     | 2<br>PEN2                                                                | 1<br>PEN1                                                                     | 0<br>PEN0      |  |  |  |  |

| Bit 70 0 Flash pulse "DISABLED" (r) PEN70 1 Flash pulse "ENABLED" |           |                                                |                                                                |                                               |                                                                          |                                                                               |                |  |  |  |  |

|                                                                   | 0 F       | PEN7 PEN6  O Flash pulse "DIS Flash pulse "EN. | PEN7 PEN6 PEN5  D Flash pulse "DISABLED" Flash pulse "ENABLED" | PEN7 PEN6 PEN5 PEN4  D Flash pulse "DISABLED" | PEN7 PEN6 PEN5 PEN4 PEN3  D Flash pulse "DISABLED" Flash pulse "ENABLED" | PEN7 PEN6 PEN5 PEN4 PEN3 PEN2  D Flash pulse "DISABLED" Flash pulse "ENABLED" | 7              |  |  |  |  |

# μP INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 12/23

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Change-of-input Interrupt Enable for I/O stages with input function  Add.: 8 |           |           |           |           |           |           |                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |           |           |           |           |           | re        | eset entry: 00h |  |

| Bit<br>Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7<br>IEN7                                                                    | 6<br>IEN6 | 5<br>IEN5 | 4<br>IEN4 | 3<br>IEN3 | 2<br>IEN2 | 1<br>IEN1 | 0<br>IEN0       |  |

| Bit 70  IEN70  IEN70  IEN70  Bit 70  IEN70  IEN70 |                                                                              |           |           |           |           |           |           | (r) terrupt.    |  |

| Overcurrent Interrupt Enable Add.: 9 |            |               |                  |                    |                   |            |            |                |

|--------------------------------------|------------|---------------|------------------|--------------------|-------------------|------------|------------|----------------|

|                                      |            |               |                  |                    |                   |            | res        | set entry: 00h |

| Bit<br>Name                          | 7<br>SCEN7 | 6<br>SCEN6    | 5<br>SCEN5       | 4<br>SCEN4         | 3<br>SCEN3        | 2<br>SCEN2 | 1<br>SCEN1 | 0<br>SCEN0     |

| Bit 70<br>SCEN70                     | 0          | "DISABLED" fo | •                | ort-circuit at IO: | x triggers an int | terrupt.   |            | (r)            |

|                                      |            | SCENx enable  | s the output IO: | x for interrupt.   |                   |            |            |                |

# $\mu\text{P}$ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 13/23

#### **ABSOLUTE MAXIMUM RATINGS**

Values beyond which damage may occur; device operation is not guaranteed.

| ltem | Symbol       | Parameter                                                                                               | Conditions                                                                        | Fig. |      |      | Unit |

|------|--------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

|      |              |                                                                                                         |                                                                                   |      | Min. | Max. |      |

| G001 | VCCD<br>VCCA | Supply Voltage VCCD, VCCA                                                                               |                                                                                   |      |      |      | V    |

| G002 | VB           | Supply Voltage VB                                                                                       |                                                                                   |      | -0.3 | 30   | V    |

| G003 | V(IO)        | Voltage at IO07                                                                                         | IOx= off                                                                          |      | -10  | 30   | V    |

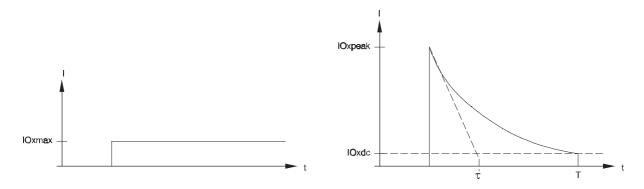

| G004 | Idc(IO)      | Current in IO07                                                                                         |                                                                                   | 1    | -500 | 100  | mA   |

| G005 | lpk(IO)      | Pulse Current in IOx                                                                                    | IOx= hi (*), τ= 2ms, T≥ 2s                                                        | 2    | -1.0 |      | Α    |

| G006 | Imax()       | Current in VCCD, VCCA                                                                                   |                                                                                   |      | -50  | 50   | mA   |

| G007 | Imax(VB)     | Current in VB01, VB23, VB45, VB67                                                                       |                                                                                   |      | -4   | 4    | Α    |

| G008 | Ic()         | Current in Clamping Diodes<br>CSN, WRN, RDN, A04, D07,<br>RESN, CLK, BLFQ, POE                          | D07 with input function                                                           |      | -20  | 20   | mA   |

| G009 | I()          | Current in D07, INTN                                                                                    | D07 with output function                                                          |      | -25  | 25   | mA   |

| G010 | llu()        | Pulse Current in CSN, WRN, RDN,<br>A04, D07, RESN, CLK, BLFQ,<br>INTN, POE, IO07 (Latch-Up<br>Strength) | pulse duration < 10μs,<br>all in-/outputs open                                    |      | -100 | 100  | mA   |

| E001 | Vd()         | ESD Susceptibility at all Pins                                                                          | MIL-STD-883.D, Method 3015.7; HBM 100pF discharged through $1.5 \mathrm{k}\Omega$ |      |      | 2    | kV   |

| E002 | Vb()         | Permissible Burst-Transients at IO07                                                                    | according to IEC 1000-4-4                                                         |      |      | 4    | kV   |

| TG1  | Tj           | Junction Temperature                                                                                    |                                                                                   |      | -40  | 150  | °C   |

| TG2  | Ts           | Storage Temperature                                                                                     |                                                                                   |      | -40  | 150  | °C   |

<sup>(\*)</sup> IOx= hi: pin set to output, active high, x=0..7

#### THERMAL DATA

Operating Conditions: VCCD= VCCA= 5V  $\pm 10\%$ , VB= 24V  $\pm 5\%$ , GNDA= GNDD= PGND= 0V, alle inputs wired (to hi respectively to lo)

| Item | Symbol | Parameter                           | Conditions                                          | Fig. |      |      |      | Unit |

|------|--------|-------------------------------------|-----------------------------------------------------|------|------|------|------|------|

|      |        |                                     |                                                     |      | Min. | Тур. | Max. |      |

| T1   | Та     | Operating Ambient Temperature Range |                                                     |      | 0    |      | 70   | °C   |

| T2   | Rthja  | Thermal Resistance Chip to Ambient  | surface mounted on PCB, no additional cooling areas |      |      | 55   |      | K/W  |

# μΡ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 14/23

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VCCD= VCCA=  $5V \pm 10\%$ , VB=  $24V \pm 5\%$ , GNDA= GNDD= PGND= 0V, all inputs wired (to hi respectively to lo), Tj= 0..125°C unless otherwise noted.

| ltem   | Symbol    | Parameter                                       | Conditions                                                                                                                             | Tj | Fig. |      |      |      | Uni        |

|--------|-----------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----|------|------|------|------|------------|

|        |           |                                                 |                                                                                                                                        | °C |      | Min. | Тур. | Max. |            |

| Total  | Device    |                                                 |                                                                                                                                        |    |      |      |      |      |            |

| 001    | VCCA      | Permissible Supply Voltage VCCA                 |                                                                                                                                        |    |      | 4.5  |      | 5.5  | V          |

| 002    | I(VCCA)   | Supply Current in VCCA                          |                                                                                                                                        |    |      |      | 7.5  | 13   | m <i>P</i> |

| 003    | I(VCCA)   | Supply Current in VCCA                          | no supply voltage VB                                                                                                                   |    |      |      |      | 25   | m/         |

| 004    | VCCD      | Permissible Supply Voltage VCCD                 |                                                                                                                                        |    |      | 4.5  |      | 5.5  | V          |

| 005    | I(VCCD)   | Supply Current in VCCD (static)                 | all logic inputs lo= 0V or hi= VCCD                                                                                                    |    |      |      | 0.3  | 3    | m/         |

| 006    | I(VCCD)   | Supply Current in VCCD (dynamic)                | continously repeated read access: tlo(RDN)= thi(RDN)= 200ns; data word changes every other cycle between "00" and "FF", CL(D07)= 200pF |    |      |      |      | 35   | mA         |

| 007    | I(VCCD)   | Supply Current in VCCD                          | all logic inputs lo= 0.8V                                                                                                              |    |      |      | 80   |      | m <i>P</i> |

| 800    | I(VCCD)   | Supply Current in VCCD                          | all logik inputs hi= 2.0V                                                                                                              |    |      |      | 100  |      | m/         |

| 009    | VB        | Permissible Supply Voltage VB (operating range) |                                                                                                                                        |    |      | 22.8 |      | 25.2 | V          |

| 010    | I(VB)     | Supply Current in VB                            | POE= hi, IOx= hi, no load                                                                                                              |    |      |      | 8.5  | 14   | m/         |

| 011    | I(VB)     | Supply Current in VB                            | IOx= off                                                                                                                               |    |      |      | 2    | 4    | m/         |

| 012    | Vc()lo    | ESD Clamp Voltage lo at VCCA, VCCD, VB          | I()= -20mA                                                                                                                             |    |      | -1.4 |      | -0.3 | V          |

| 013    | Vc()hi    | ESD Clamp Voltage hi at VCCA                    | I()= 20mA                                                                                                                              |    |      |      |      | 11   | V          |

| 014    | Vc()hi    | ESD Clamp Voltage hi at VB                      | I()= 20mA                                                                                                                              |    |      | 30   | 47   | 60   | V          |

| 015    | Vc()lo    | ESD Clamp Voltage lo at IOx                     | I()= -20mA                                                                                                                             |    |      | -30  |      | -10  | V          |

| 016    | Vc()hi    | ESD Clamp Voltage hi at IOx                     | I()= 20mA                                                                                                                              |    |      | 30   | 47   | 60   | V          |

| I/O S1 | ages: Hig | h-Side Driver IO07                              |                                                                                                                                        |    |      |      |      |      |            |

| 101    | Vs()hi    | Saturation Voltage hi                           | Vs()hi= VB -V(IOx);<br>I(IOx)= -10mA                                                                                                   | 1  |      |      |      | 0.2  | V          |

| 102    | Vs()hi    | Saturation Voltage hi                           | Vs()hi= VB -V(IOx);<br>I(IOx)= -100mA                                                                                                  | 1  |      |      |      | 0.6  | V          |

| 103    | Vs()hi    | Saturation Voltage hi for pulse load            | $Vs()hi= VB -V(IOx); \\ I(IOx)= -500mA, \ \tau= 2ms, \ T \ge 2s$                                                                       | 2  |      |      |      | 2.0  | V          |

| 104    | lsc()hi   | Overcurrent Cut-off                             | IOx= hi, V(IOx)= 0VB-3V                                                                                                                |    |      | -1.8 |      | -0.6 | Α          |

| 105    | It()scs   | Threshold Current for Overcurrent Message       |                                                                                                                                        |    |      | -1.2 |      | -0.6 | А          |

| 106    | Vc()lo    | Free-wheeling Clamp Voltage                     | I(IOx)= -100mA                                                                                                                         |    |      | -15  |      | -12  | V          |

| 107    | SRhi()    | Slew Rate hi                                    | CL= 0100pF, RL= 240Ω1kΩ                                                                                                                |    |      | 15   |      | 40   | V/µ        |

| 108    | SRIo()    | Slew Rate Io                                    | CL= 0100pF, RL= 240Ω1kΩ                                                                                                                |    |      | 15   |      | 40   | V/µ        |

| 109    | tplh()    | Propagation Delay until<br>IOx: lo→hi           | write cycle, WRN: $Io \rightarrow hi$ until $V(IOx) > V0(IOx) + 1V$                                                                    |    |      |      |      | 5    | μs         |

| 110    | tphl()    | Propagation Delay until IOx= off                | write cycle, WRN= lo→hi until<br>V(IOx) < 80% (VB-Vs(IOx)hi)                                                                           |    |      |      |      | 5    | μs         |

# μΡ INTERFACE WITH 2×4 24V HIGH-SIDE DRIVERS

Rev A0, 15/23

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VCCD= VCCA= 5V ±10%, VB= 24V ±5%, GNDA= GNDD= PGND= 0V, all inputs wired (to hi respectively to lo), Tj= 0..125°C unless otherwise noted.

| ltem  | Symbol         | Parameter                                                   | Conditions                                                                                        | Tj | Fig. |      |      |      | Unit |

|-------|----------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----|------|------|------|------|------|

|       |                |                                                             |                                                                                                   | °C |      | Min. | Тур. | Max. |      |

| I/O S | tages: Cui     | rrent Sources at IO07                                       |                                                                                                   |    |      |      |      |      |      |

| 201   | lpd()          | Pull-down Current Source<br>(200μA)                         | IOx with input function,<br>IL1= IH1= 0, IL0= IH0= 1,<br>V(IOx)= 3VVB                             |    |      | 120  | 200  | 280  | μА   |

| 202   | lpd()          | Pull-down Current Source (600μA)                            | IOx with input function,<br>IL1= IH1= 1, IL0= IH0= 0,<br>V(IOx)= 3VVB                             |    |      | 400  | 600  | 800  | μА   |

| 203   | lpd()          | Pull-down Current Source<br>(2mA)                           | IOx with input function,<br>IL1= IH1= 1, IL0= IH0= 1,<br>V(IOx)= 3VVB                             |    |      | 1.4  | 2.0  | 2.7  | mA   |

| 204   | lpu()          | Pull-up Current Source (200μA)                              | IOx with output function and IOx= off, IL0, IH0= 1; V(IOx)= -7VVB-2V                              |    |      | 120  | 200  | 280  | μА   |

| 205   | tp()lon        | Current Source Enable Time (pull-down and pull-up sources)  | write cycle, WRN: lo→hi til I(IOx) > 90% lpd(IOx) or I(IOx) > 90% lpu(IOx)                        |    |      |      |      | 5    | μs   |

| 206   | tp()loff       | Current Source Disable Time (pull-down and pull-up sources) | write cycle, WRN: lo→hi til I(IOx) < 10% lpd(IOx) or I(IOx) < 10% lpu(IOx)                        |    |      |      |      | 5    | μs   |

| 207   | llk()          | Leakage Current                                             | IOx with input function or output function with IOx= off and IL1, IH1, IL0, IH0= 0; V(IOx)= -7VVB |    |      | -20  |      | 20   | μА   |

| 208   | llk()          | Leakage Current                                             | logic see item 204;<br>V(IOx)= -10V7V                                                             |    |      | -100 |      | 20   | μА   |

| 209   | llk()          | Leakage Current                                             | logic see item 204;<br>V(IOx)= VBVB+0.4V                                                          |    |      | -20  |      | 100  | μА   |

| 210   | llk()          | Leakage Current                                             | logic see item 204;<br>V(IOx)= VB30V                                                              |    |      |      | 200  | 500  | μА   |

| 211   | llk()          | Leakage Current                                             | no supply voltage VB                                                                              |    |      |      |      | 5    | mA   |

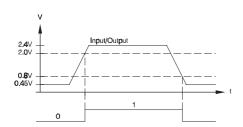

| /0 S  | tages: Coi     | mparator IO07                                               |                                                                                                   |    |      |      |      |      |      |