### 256K X 16 MULTIPORT VIDEO RAM

### **Features**

- 256K x 16 Multiport Video RAM

- · Performance:

|                  | Parameter                    | -6H  | -60  | -70   |

|------------------|------------------------------|------|------|-------|

| t <sub>RP</sub>  | RE Precharge                 | 25ns | 25ns | 30ns  |

| tSCA             | Serial Access Time           | 12ns | 15ns | 17ns  |

| tCAC             | Access Time from CE          | 15ns | 15ns | 17ns  |

| t <sub>AA</sub>  | Column Address Access Time   | 25ns | 30ns | 35ns  |

| tscc             | Serial Clock Cycle Time      | 12ns | 18ns | 20ns  |

| tRC              | Read or Write Cycle Time     | 95ns | 95ns | 110ns |

| t <sub>PC</sub>  | Fast Page Mode Cycle Time    | 30ns | 30ns | 40ns  |

| <sup>t</sup> HPC | Extended Data Out Cycle Time | 20ns | 25ns | 30ns  |

- Fully Asynchronous operation of Random port and Serial port

- Compatible to Full Depth SAM in SRS mode

- 8 Column Block Write with masking Column and WPB masking along with individual Byte Control

- 50 MHz EDO performance

- FLASH WRITE with WPBM- 512 x 16 bits

- Persistent & Non-Persistent WPBM mode

- · Split Serial Register with Width Control

- 256 Location Start Address Pointer for SAM

- · Full Read and Split Read Transfer

- Masked Write Transfer

- Masked Split Write Transfer

- Power Supply:  $5.0V \pm 0.5V$  and  $3.3V \pm 0.3V$

- High Performance, CMOS 0.55μm process

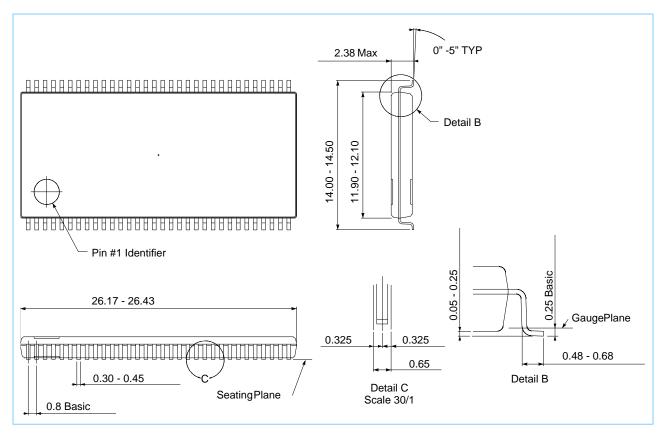

- SSOG-64 JEDEC Standard

- · TTL compatible

### **Description**

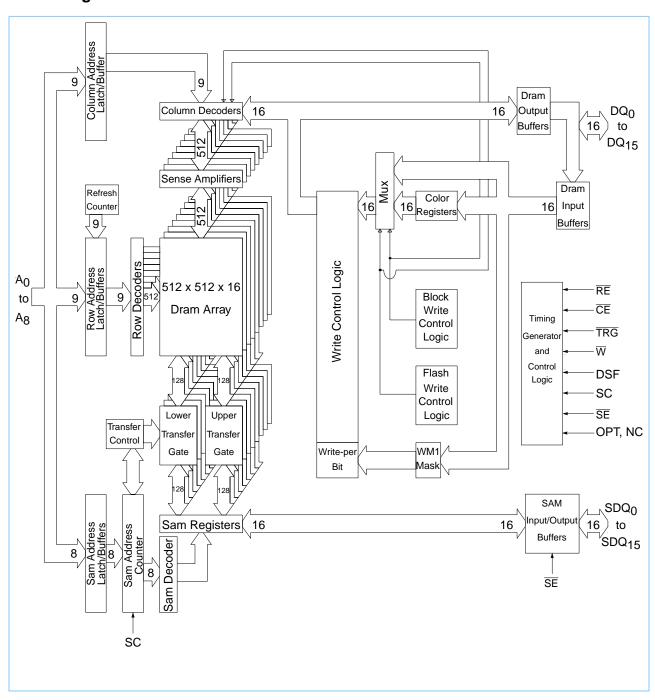

This 4Mb dual port Video RAM (VRAM) consists of a Dynamic Random Access Memory (DRAM) organized as 256K x 16 interfaced to a Serial Register / Serial Access Memory (SAM) organized as 256 x 16. The VRAM supports three basic operations: Bidirectional Random Access to the DRAM, Bidirectional Serial Access to the SAM, and Bidirectional Data Transfer between any DRAM row and the SAM. Full compatibility is provided between Half Depth SAM (256 x 16) and Full Depth SAM (512 x 16) by setting the VRAM in Serial Register Stop (SRS) mode with a stop address of 128 bit (or less).

Unique features have been added to these basic VRAM operations to improve graphics performance of the system. Higher update rates can be achieved with either Flash Write or Block Write modes. Two  $\overline{\rm W}$  or two  $\overline{\rm CE}$  inputs are provided for individual byte control for both normal Write and Block Write. For individual bit control, a Write-Per-Bit Mask (WPBM) can be supplied on the data pins at  $\overline{\rm RE}$  time to be used during Masked Write transfers or Masked Write cycles. A permanent mask to be used during Block Write cycles can be loaded using the Load Mask Register (LMR) cycle.

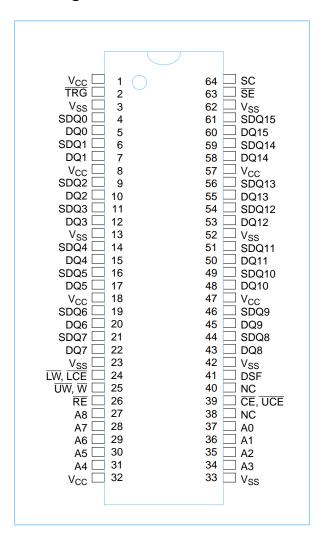

### **Pin Assignments**

### **Pin Description**

| RE                                   | Row Enable                                                                                        |

|--------------------------------------|---------------------------------------------------------------------------------------------------|

| CE                                   | Column Enable (only in dual WE parts)                                                             |

| TCE, UCE                             | Lower & Upper Column Enable (Only In Dual CE Parts)                                               |

| $\overline{W}$                       | Write (Only In Dual CE parts)                                                                     |

| LW, UW                               | Lower & Upper Byte Write (Only In Dual $\overline{W}$ Parts)                                      |

| TRG                                  | Data Transfer & Output Enable                                                                     |

| DSF                                  | Designated Special Function                                                                       |

| A <sub>8</sub> -A <sub>0</sub>       | Address Inputs                                                                                    |

| DQ <sub>15</sub> - DQ <sub>0</sub>   | Random Port Data Input/Output                                                                     |

| SDQ <sub>15</sub> - SDQ <sub>0</sub> | Serial Port Data Input/Output                                                                     |

| SC                                   | Serial Clock                                                                                      |

| SE                                   | Serial Enable                                                                                     |

| V <sub>CC</sub>                      | Voltage (5.0V $\pm$ 0.5V or 3.3V $\pm$ 0.3V). All voltages are referenced to the nearest VSS pin. |

| V <sub>SS</sub>                      | Ground. V <sub>SS</sub> =0V                                                                       |

| NC                                   | No Connect                                                                                        |

### **Detailed Pin Description**

### RE - Row Enable; also known as RAS

This pin is functionally equivalent to a chip enable signal in that whenever it is activated, 8192 storage cells of the selected row are sensed simultaneously and the sense amplifiers restore all data. The falling edge of  $\overline{\text{RE}}$  latches data on address pins A<sub>0</sub> -A<sub>8</sub>.  $\overline{\text{CE}}$ ,  $\overline{\text{TRG}}$ ,  $\overline{\text{W}}$ , and DSF are simultaneously latched to invoke the DRAM port and Serial port operations.

### CE - Column Enable (Dual WE parts only); also known as CAS.

This pin serves as a chip select signal. It activates the column decoder and the I/O buffer. The falling edge of  $\overline{CE}$  latches the column address  $A_0$  - $A_8$ . State of DSF at falling edge of  $\overline{CE}$  invokes various DRAM port and Serial port functions.

### LCE, UCE - Lower and Upper Column Enable (Dual CE parts only).

These pins enable lower and upper byte respectively of the selected column for Read/Write. The falling edge of either  $\overline{\mathsf{LCE}}$  or  $\overline{\mathsf{UCE}}$  latches the column address and state of DSF to invoke various DRAM port and Serial port functions.

### W - Write (Dual CE parts only)

This pin enables the DRAM port write circuitry. It is also used as a control input pin to define the various operations at RE fall time.

### LW, UW - Lower and Upper Write (Only in Dual W parts)

These pins enable the DRAM port write circuitry for Lower and Upper Byte Write respectively. Either  $\overline{\text{LW}}$  or  $\overline{\text{UW}}$  being low is considered low for Write cycles.

### TRG - Data Transfer and Output Enable (DT/OE)

This is a multifunctional input pin. In conjunction with  $\overline{LW}/\overline{UW}$ , DSF and  $\overline{CE}$ , it either enables the DRAM data outputs or enables transfer operations between DRAM and SAM. This is also used as a control input pin to define the various operating modes at  $\overline{RE}$  time.

### **DSF - Designated Special Function**

A control pin used in conjunction with other control pins to define the various operating modes at  $\overline{RE}$  and  $\overline{CE}$  time.

### A<sub>0</sub> - A<sub>8</sub> - Address Inputs

These pins are multiplexed as row and column address inputs. Row addresses are first used to select one of the possible 512 rows for a Read, Write, Data Transfer, or Refresh cycles. Column addresses are then supplied to select one of the possible 512 columns for a Read or a Write cycle or one of the possible 256 starting locations for the next Serial Read/Write cycle for the Serial port.

### 256K X 16 MULTIPORT VIDEO RAM

### DQ<sub>0</sub> - DQ<sub>15</sub> - Random Port Data Input/Output

In a Read cycle, these pins serve as outputs for the selected storage cells. In a Write cycle, data input on these pins is latched by the falling edge of  $\overline{\text{CE}}$  or  $\overline{\text{LW/UW}}$  whichever occurs later. Data will not appear at the outputs until after both  $\overline{\text{CE}}$  and  $\overline{\text{TRG}}$  have been brought low. During transfer operations, the DQ outputs remain in the high-Z state for the entire cycle. In a Block Write cycle, data input on these pins is used to mask the selected columns in the block. At  $\overline{\text{RE}}$  falling edge, the data input at these pins can be used for loading the Write-per-Bit Mask (WPBM).

### SDQ<sub>0</sub> - SDQ<sub>15</sub> - Serial Port Data Input/Output

16 bit data can be written or read from these pins. The output data remains valid until the next SC clock is activated.

### SC - Serial Clock

The rising edge of the SC signal is used to initiate a Read/Write from/to the SAM Register (starting from the location specified in the data transfer cycle). In the Serial Read mode, 16 of the 4096 data bits from the SAM Register are transferred to 16 Serial Data Buses and read out. In the Serial Write operation, input data is latched on the rising edge of SC clock. Whenever SC clock is low, the Serial port is in standby.

### **SE** - Serial Port Enable

This signal enables or disables the Serial Input/Output buffer. When  $\overline{SE}$  is high, the output of the Serial port is in tri-state. While  $\overline{SE}$  is held high, the serial clock is not disabled. Thus, external SC pulses will increment the internal Serial address counter regardless of the state of  $\overline{SE}$ . This ungated serial clock scheme minimizes access time of Serial output from  $\overline{SE}$  low since the Serial Clock input buffer and the Serial address counter are not disabled by  $\overline{SE}$ .

$V_{cc}$  - (5.0V  $\pm$  0.5V) or (3.3V  $\pm$  0.3V) voltage.

All voltages are referenced to the nearest Vss pin.

$V_{ss}$  - Circuit ground.  $V_{ss}$  = 0V.

### NC - No Connect.

NC implies that the pin(s) should not be grounded or connected to any other signal. These pins might be used for testing some modes at factory. Consult factory before using any one of NC pins.

### **Ordering Information**

| Part Number      | Features               | Voltage | Speed | Package    | Note |

|------------------|------------------------|---------|-------|------------|------|

| IBM025160LG5D-60 | Dual CE, Fast Page     |         | 60ns  |            |      |

| IBM025160LG5D-70 | Dual CE, Fast Fage     |         | 70ns  | ,          |      |

| IBM025170LG5D-60 | Dual W, Fast Page      |         | 60ns  | _          |      |

| IBM025170LG5D-70 | Dual W, Fast Page      |         | 70ns  | _          |      |

| IBM025161LG5D-6H |                        | 5.0V    | <60ns |            | 1    |

| IBM025161LG5D-60 | Dual CE, Extended Data |         | 60ns  | ,          |      |

| IBM025161LG5D-70 |                        |         | 70ns  |            |      |

| IBM025171LG5D-6H |                        |         | <60ns | .472" SSOG | 1    |

| IBM025171LG5D-60 | Dual W, Extended Data  |         | 60ns  |            |      |

| IBM025171LG5D-70 |                        |         | 70ns  |            |      |

| IBM025160NG5D-60 | Dual CE, Fast Page     |         | 60ns  |            |      |

| IBM025160NG5D-70 | Dual CE, Fast Page     |         | 70ns  |            |      |

| BM025170NG5D-60  | Dual W, Fast Page      |         | 60ns  |            |      |

| IBM025170NG5D-70 | Dual W, Fast Page      |         | 70ns  |            |      |

| IBM025161NG5D-6H |                        | 3.3V    | <60ns |            | 1    |

| IBM025161NG5D-60 | Dual CE, Extended Data | 3.31    | 60ns  |            |      |

| IBM025161NG5D-70 |                        |         | 70ns  |            |      |

| IBM025171NG5D-6H |                        |         | <60ns |            | 1    |

| IBM025171NG5D-60 | Dual W, Extended Data  |         | 60ns  |            |      |

| IBM025171NG5D-70 |                        |         | 70ns  |            |      |

<sup>1.</sup> The -6H means 60ns High Performance Parts.

IBM025160

### **Block Diagram**

IBM025170

### **Truth Table**

| MNE Code  |      | RE  |      |     | CE  | Ado              | Iress                                    | DQ <sub>0</sub> - | DQ <sub>15</sub>       | Function                                     |  |

|-----------|------|-----|------|-----|-----|------------------|------------------------------------------|-------------------|------------------------|----------------------------------------------|--|

| WINE Code | CE   | TRG | W    | DSF | DSF | RE               | CE                                       | RE                | CE, W                  | FullCuon                                     |  |

| CBR       | 0(5) | Х   | 1(4) | 0   | -   | Х                | -                                        | Х                 | -                      | CE before RE Refresh (RESET) (9)             |  |

| CBRS      | 0(5) | Х   | 0(3) | 1   | -   | STOP(6)<br>Point | -                                        | Х                 | -                      | CE Before RE Refresh stop point set (2)      |  |

| CBRN      | 0(5) | Х   | 1(4) | 1   | -   | Х                | -                                        | Х                 | -                      | CE Before RE Refresh without mode reset (10) |  |

| ROR       | 1    | 1   | Х    | 0   | -   | Row(1)           | -                                        | Х                 | -                      | RE Only Refresh (11)                         |  |

| KOK       | 1    | 1   | 1    | X   | -   | Row(1)           | -                                        | Χ                 | -                      | RE Only Reflesh (11)                         |  |

| LCR       | 1    | 1   | 1(4) | 1   | 1   | Row(1)           | Χ                                        | Χ                 | Color                  | Load Color Register                          |  |

| LMR       | 1    | 1   | 1(4) | 1   | 0   | Row(1)           | Х                                        | Х                 | Mask                   | Load Mask Register (13)                      |  |

| RW        | 1    | 1   | 1(4) | 0   | 0   | Row              | Column                                   | Х                 | Valid<br>Data<br>Input | Read/Write Cycle (No<br>Mask)                |  |

| RWM       | 1    | 1   | 0(3) | 0   | 0   | Row              | Column                                   | WPBM<br>(7)       | Valid<br>Data<br>Input | Read/Write Cycle<br>(Masked)                 |  |

| BW        | 1    | 1   | 1(4) | 0   | 1   | Row              | Column<br>A <sub>3</sub> -A <sub>8</sub> | Х                 | Column<br>mask         | Block Write Cycle (No<br>Mask)               |  |

| BWM       | 1    | 1   | 0(3) | 0   | 1   | Row              | Column<br>A <sub>3</sub> -A <sub>8</sub> | WPBM<br>(7)       | Column<br>mask         | Block Write Cycle<br>(Masked)                |  |

| FWM       | 1    | 1   | 0(3) | 1   | Х   | Row              | X                                        | WPBM<br>(7)       | Х                      | Flash Write Cycle<br>(Masked) (8)            |  |

| RT        | 1    | 0   | 1(4) | 0   | Х   | Row              | TAP                                      | Х                 | Х                      | Full - Register Read<br>Transfer             |  |

| MWT       | 1    | 0   | 0(3) | 0   | Х   | Row              | TAP (12)                                 | WPBM<br>(7)       | Х                      | Masked Full - Register<br>Write Transfer     |  |

| SRT       | 1    | 0   | 1(4) | 1   | Х   | Row              | TAP                                      | X                 | Х                      | Split Read Transfer                          |  |

| MSWT      | 1    | 0   | 0(3) | 1   | Х   | Row              | TAP                                      | WPBM<br>(7)       | Х                      | Masked Split Write<br>Transfer               |  |

- 1. Row address needed only for refresh operation to the selected row. Otherwise this is a don't care.

- 2. This cycle is used to put the chip into special modes. The Address at  $\overline{\text{RE}}$  fall becomes the Serial port STOP address. CBRS cycle(s) should be performed immediately after the power up initialization cycles.

- 3. Either  $\overline{W}$  is 0.

- 4. Both  $\overline{W}$  are 1.

- 5. Either  $\overline{CE}$  is 0 on Dual  $\overline{CE}$  parts.

- 6. STOP defines the Serial port address on which shift out moves to the other half of the SAM.

- 7. After LMR, WPBM is only changed by LMR. CBR resets the persistent mask.

- 8. No byte select, both bytes are written.

- 9. CBR mode will reset all the unknown modes at power up. It will also clear persistent Write-per-Bit mode.

- 10. CBRN mode will not clear persistent Write-per-Bit mode.

- 11. ROR will not clear inadvertent modes at power up time.

- 12. A<sub>0</sub>-A<sub>7</sub> define the tap point for the Serial Data input after the transfer. A<sub>8</sub> defines the particular half of the DRAM row in which the SAM data will be transferred.

- 13. LMR cycle will set the persistent Write-per-Bit mode. The persistent Write-per-Bit mode is reset by CBR cycle only.

- 14.  $DQ_0$   $DQ_{15}$  are latched on either the first  $\overline{WEX}$  falling edge or the falling edge of  $\overline{CAS}$ , whichever occurs later.

**Legend:** 'X' = Don't Care; '-' = Not Applicable

### **Absolute Maximum Ratings**

| Complete al      | ltem -                       | Rat          | ting         | Units | Notes |  |

|------------------|------------------------------|--------------|--------------|-------|-------|--|

| Symbol           |                              | 5.0 Volt     | 3.3 Volt     | Units | Notes |  |

| V <sub>CC</sub>  | Power Supply Voltage         | -1.0 to +6.0 | -0.5 to +4.6 | V     | 1     |  |

| T <sub>A</sub>   | Operating Temperature        | 0 to +70     | 0 to +70     | °C    | 1     |  |

| T <sub>STG</sub> | Storage Temperature          | -55 to +150  | -55 to +150  | °C    | 1     |  |

| P <sub>D</sub>   | Power Dissipation            | 1.3          | 1.3          | W     | 1     |  |

| l <sub>OUT</sub> | Short Circuit Output Current | 50           | 33           | mA    | 1     |  |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended DC Operating Conditions** $(T_A = 0 \text{ to } +70^{\circ}\text{C})$

| Cumbal          | Parameter          | 5.0 Volt |      |                      |      | 3.3 Volt | Units                | Notes |       |

|-----------------|--------------------|----------|------|----------------------|------|----------|----------------------|-------|-------|

| Symbol          | Farameter          | Min.     | Тур. | Max.                 | Min. | Тур.     | Max.                 | Units | Notes |

| $V_{CC}$        | Supply Voltage     | 4.5      | 5.0  | 5.5                  | 3.0  | 3.3      | 3.6                  | V     | 1     |

| $V_{IH}$        | Input High Voltage | 2.4      | _    | V <sub>CC</sub> +0.5 | 2.0  | _        | V <sub>CC</sub> +0.3 | V     | 1     |

| V <sub>IL</sub> | Input Low Voltage  | -0.5     | _    | 0.8                  | -0.3 | _        | 0.8                  | V     | 1     |

### **Capacitance** (T<sub>A</sub>= 25°C, f= 1.0 MHz)

| Symbol          | Parameter                                                | Min. | Max. | Units | Notes |

|-----------------|----------------------------------------------------------|------|------|-------|-------|

| C <sub>I1</sub> | Input Capacitance (Addresses)                            | _    | 5    | pF    |       |

| C <sub>I2</sub> | RE, CE, W, TRG, DSF, SC, SE                              | _    | 7    | pF    |       |

| C <sub>O</sub>  | Output Capacitance (DQ <sub>i</sub> , SDQ <sub>i</sub> ) | _    | 7    | pF    |       |

### **Output Drivers**

| Driver        | Impedance | Output Voltage, Low (Max)       | Output Voltage, High (Min)     |

|---------------|-----------|---------------------------------|--------------------------------|

| Serial Port   | 60±15 Ω   | I <sub>OUT</sub> =2.0 mA, V=0.4 | I <sub>OUT</sub> =-1 mA, V=2.4 |

| Parallel Port | 45±15 Ω   | I <sub>OUT</sub> =2.0 mA, V=0.4 | I <sub>OUT</sub> =-1 mA, V=2.4 |

### **AC Measurement Conditions**

| Port                              | Detect      | Load          |

|-----------------------------------|-------------|---------------|

| Parallel Port Output Detect Level | 2.0V / 0.8V | _             |

| Serial Port Output Detect Level   | 2.0V / 0.8V | _             |

| Parallel Port Output Load         | _           | 1 TTL + 50 PF |

| Serial Port Output Load           | _           | 1 TTL + 30 PF |

### **DC Electrical Characteristics** ( $T_A$ = 0 to +70°C, $V_{CC}$ = 3.3V $\pm$ 0.3V or $V_{CC}$ = 5.0V $\pm$ 0.5V)

| O seek al         | Description                                                                                                               |     | 5.0  | Volt | 3.3 Volt |      |       | Mataa            |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|-----|------|------|----------|------|-------|------------------|

| Symbol            | Parameter                                                                                                                 |     | Min. | Max. | Min.     | Max. | Units | Notes            |

|                   | Operating Current (Random)                                                                                                | -6H | _    | 135  | _        | 135  |       |                  |

| I <sub>CC1</sub>  | Average Power Supply Operating Current (RE and CE Cycling, t <sub>RC</sub> =120ns for -60 and -6H, t <sub>RC</sub> =130ns | -60 | _    | 135  | _        | 135  | mA    | 1, 2, 3, 6       |

|                   | for -70, SC = 0)                                                                                                          | -70 | _    | 130  | _        | 130  |       |                  |

|                   | Operating Current (Serial)                                                                                                | -6H | _    | 40   | _        | 40   |       |                  |

| $I_{CC2}$         | Average Power Supply Current (t <sub>SCC</sub> = 20ns for -60 and -6H, t <sub>SCC</sub> = 23ns for -70)                   | -60 | _    | 40   | _        | 40   | mA    | 1, 2, 7          |

|                   | (ISCC = 20118 101 -00 and -011, ISCC = 25118 101 -70)                                                                     | -70 | _    | 35   | _        | 35   |       |                  |

|                   | Operating Current (Both Port)                                                                                             | -6H | _    | 160  | _        | 160  |       |                  |

| $I_{CC3}$         | Average Power Supply Current (RE and CE Cycling, t <sub>RC</sub> =120ns & t <sub>SCC</sub> = 20ns for -60 and -           | -60 | _    | 160  | _        | 16 0 | mA    | 1, 2, 3,<br>6, 7 |

|                   | 6H, t <sub>RC</sub> =130ns & t <sub>SCC</sub> = 23ns for -70)                                                             | -70 | _    | 150  | _        | 150  |       |                  |

|                   | Fast Page Mode Current Average Power Supply Current, Fast Page Mode                                                       | -6H | _    | 80   | _        | 80   |       | 101              |

| I <sub>CC4</sub>  | $(\overline{RE}\ V_L Min., \overline{CE}\ Cycling, t_{PC} = 40ns for -60 and -6H,$                                        | -60 | _    | 80   | _        | 80   | mA    | 1, 2, 4,<br>6, 7 |

|                   | t <sub>PC</sub> =45ns for -70)                                                                                            | -70 | _    | 70   | _        | 70   |       |                  |

|                   | Fast Page Mode Current (Serial) Average Power Supply Current, Fast Page/Serial                                            | -6H | _    | 85   | _        | 85   |       |                  |

| I <sub>CC5</sub>  | (RE ≤ V <sub>IL</sub> Min., CE Cycling, t <sub>PC</sub> = 40ns & t <sub>SCC</sub> = 20ns for -60                          |     | _    | 85   | _        | 85   | mA    | 1, 2, 7          |

|                   | and -6H, t <sub>PC</sub> = 45ns & t <sub>SCC</sub> = 23ns for -70)                                                        | -70 | _    | 75   | _        | 75   | 5     |                  |

| I <sub>CC6</sub>  | Standby Supply Current Power Supply Standby Current (RE = CE = V <sub>CC</sub> , SC = 0V)                                 |     | _    | 5    | _        | 5    | mA    |                  |

|                   | Data Transfer Current                                                                                                     | -6H | _    | 130  | _        | 130  |       |                  |

| I <sub>CC7</sub>  | Average Power Supply Current                                                                                              | -60 | _    | 130  | _        | 130  | mA    |                  |

|                   | (t <sub>RC</sub> = 120ns for -60 and -6H, t <sub>RC</sub> = 130ns for -70, SC = 0V)                                       | -70 | _    | 120  | _        | 120  |       |                  |

|                   | Data Transfer Current                                                                                                     | -6H | _    | 140  | _        | 140  |       |                  |

| I <sub>CC8</sub>  | Average Power Supply Current (t <sub>SCC</sub> = 20ns for -60 and -6H, t <sub>SCC</sub> = 23ns for -70)                   | -60 | _    | 140  | _        | 140  | mA    |                  |

|                   | (ISCC = 20118 101 -00 atta -on, ISCC = 23118 101 -70)                                                                     | -70 | _    | 130  | _        | 130  |       |                  |

| I <sub>I(L)</sub> | Input Leakage Current, any input $(0.0 \le V_{IN} \le (V_{CC} + 1.0V))$ , All Other Pins Not Under Test = 0V              |     | -10  | +10  | -10      | 10   | μА    |                  |

| $I_{O(L)}$        | Output Leakage Current ( $D_{OUT}$ is disabled, $0.0 \le V_{OUT} \le V_{CC}(max)$ )                                       |     | -10  | +10  | -10      | 10   | μΑ    |                  |

| V <sub>OH</sub>   | Output Level (TTL) Output "H" Level Voltage (I <sub>OUT</sub> = -1mA, Random and Serial)                                  |     | 2.4  | _    | 2.4      | _    | V     | 4                |

| V <sub>OL</sub>   | Output Level (TTL) Output "L" Level Voltage (I <sub>OUT</sub> = +2.0mA, Random and Serial)                                |     | _    | 0.4  | _        | 0.4  | V     | 4                |

- 1.  $I_{CC1},\,I_{CC2},\,I_{CC3},\,I_{CC4},\,I_{CC5},\,I_{CC7}$  and  $I_{CC8}$  depend on cycle rate.

- 2.  $I_{CC1}$ ,  $I_{CC2}$ ,  $I_{CC3}$ ,  $I_{CC3}$ ,  $I_{CC5}$ ,  $I_{CC7}$  and  $I_{CC8}$  depend on output loading. Specified values are obtained with the output open.

- 3. Measured with one address change per  $\overline{\text{RE}}$  cycle.

- 4. Measured with one column address change per page cycle.

- 5. V<sub>IH</sub>(min.) and V<sub>IL</sub>(max.) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 6. Measured with  $\overline{TRG} = V_{IH}$  when  $\overline{CE} = V_{IL}$ .

- 7. Measured with  $\overline{SE} = V_{IH}$ .

### **AC Characteristics** (T<sub>A</sub>= 0 to +70°C)

### Read, Write, Read-Modify-Write and Refresh. Cycles (Part 1 of 2) (Common Parameters)

| Cymhal               | Parameter                                                                            | -6   | SH . | -60  |      | -70  |      | Units | Notes   |

|----------------------|--------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|---------|

| Symbol               | Parameter                                                                            | Min. | Max. | Min. | Max. | Min. | Max. | Units | Notes   |

| t <sub>ASC</sub>     | Column address setup time                                                            | 0    | _    | 0    | _    | 0    | _    | ns    |         |

| t <sub>ASR</sub>     | Row address setup time                                                               | 0    | _    | 0    | _    | 0    | _    | ns    |         |

| t <sub>AR</sub>      | Column address hold time after RE low                                                | 15   | _    | 20   | _    | 25   | _    | ns    |         |

| t <sub>CAH</sub>     | Column address hold time after $\overline{\text{CE}}$ low                            | 6    | _    | 6    | _    | 8    | _    | ns    | 5       |

| t <sub>CAS</sub>     | CE pulse width                                                                       | 12   | 16K  | 15   | 16K  | 17   | 16K  | ns    |         |

| tCHCL                | First $\overline{CE}$ to return high to last $\overline{CE}$ going low               | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>CLCH</sub>    | Last $\overline{\text{CE}}$ going low to first $\overline{\text{CE}}$ to return high | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>CP</sub>      | CE precharge time                                                                    | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>CRP</sub>     | CE high before RE low precharge                                                      | 5    | _    | 5    | _    | 10   | _    | ns    | 8       |

| t <sub>CSH</sub>     | CE hold time                                                                         | 60   | _    | 60   | _    | 70   | _    | ns    |         |

| t <sub>H(SFC)</sub>  | DSF hold time after $\overline{\text{CE}}$ low                                       | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>H(SFR)</sub>  | DSF hold time after RE low                                                           | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| $t_{MH}$             | Write mask hold time after RE low                                                    | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>MS</sub>      | Data-in setup before RE low                                                          | 0    | _    | 0    | _    | 0    | _    | ns    |         |

| t <sub>RAD</sub>     | RE to column address delay time                                                      | 11   | 35   | 11   | 35   | 13   | 40   | ns    | 4       |

| t <sub>RAH</sub>     | Row address hold time after RE low                                                   | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>RAS</sub>     | RE pulse width                                                                       | 60   | 100K | 60   | 100K | 70   | 100K | ns    |         |

| $t_{RC},t_{WC}$      | Random read or write cycle time                                                      | 95   | _    | 95   | _    | 110  | _    | ns    | 1, 2    |

| t <sub>RCD</sub>     | Delay from RE low to CE low                                                          | 16   | 45   | 16   | 45   | 18   | 53   | ns    | 3, 5, 9 |

| t <sub>RP</sub>      | RE precharge time                                                                    | 25   | _    | 25   | _    | 30   | _    | ns    | 1, 6, 7 |

| t <sub>RSH</sub>     | RE hold time                                                                         | 15   | _    | 15   | _    | 17   | _    | ns    |         |

| t <sub>RWH</sub>     | W hold time after RE low                                                             | 6    | _    | 6    | _    | 8    | _    | ns    |         |

| t <sub>SU(SFC)</sub> | DSF setup time before $\overline{\text{CE}}$ low                                     | 0    | _    | 0    | _    | 0    | _    | ns    |         |

- 1. An initial pause of 100µs is required after power up followed by 8  $\overline{\text{CE}}$  before  $\overline{\text{RE}}$  refresh cycles for proper device operation

- 2. AC measurements assume  $t_T = 5$ ns.

- 3. Operation within the t<sub>RCD</sub>(max) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only: If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled by t<sub>CAC</sub>.

- 4. Operation within the t<sub>RAD</sub>(max) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RAD</sub>(max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max) limit, then access time is controlled by t<sub>AA</sub>.

- 5.  $t_{RCD}$  and  $t_{CAH}$  cannot be at minimum values simultaneously.  $t_{RCD} + t_{CAH} \ge 45$ ns (60ns  $t_{RAC}$  product),  $t_{RCD} + t_{CAH} \ge 50$ ns (70ns  $t_{RAC}$  product).

- t<sub>RWL</sub> and t<sub>RP</sub> cannot be at minimum values simultaneously. t<sub>RWL</sub> + t<sub>RP</sub> ≥ 60ns (60ns t<sub>RAC</sub> product), t<sub>RWL</sub> + t<sub>RP</sub> ≥ 70ns (70ns t<sub>RAC</sub> product).

- t<sub>CWL</sub> and t<sub>RP</sub> cannot be at minimum values simultaneously. t<sub>CWL</sub> + t<sub>RP</sub> ≥ 60ns (60ns t<sub>RAC</sub> product), t<sub>CWL</sub> + t<sub>RP</sub> ≥ 70ns (70ns t<sub>RAC</sub> product).

- 8. t<sub>CRP</sub> must be 15ns (60ns t<sub>RAC</sub>) or 17ns (70ns t<sub>RAC</sub>) if a write-per-bit mask is used on the following RE cycle due to the fact that t<sub>OFF</sub> must be met.

- 9. During Serial port write transfer  $t_{RCD}$  (max) = 100ns.

### Read, Write, Read-Modify-Write and Refresh. Cycles (Part 2 of 2) (Common Parameters)

| Courselle al         | Parameter -                     | -6H  |      | -60  |      | -70  |      | Units | Notes |

|----------------------|---------------------------------|------|------|------|------|------|------|-------|-------|

| Symbol               |                                 | Min. | Max. | Min. | Max. | Min. | Max. | Units | notes |

| t <sub>SU(SFR)</sub> | DSF setup time before RE low    | 0    | _    | 0    | _    | 0    | _    | ns    |       |

| t <sub>T</sub>       | Transition time (rise and fall) | 3    | 50   | 3    | 50   | 3    | 50   | ns    |       |

| t <sub>TLH</sub>     | TRG hold time after RE low      | 6    | _    | 6    | _    | 8    | _    | ns    |       |

| t <sub>TLS</sub>     | TRG setup time before RE low    | 0    | _    | 0    | _    | 0    | _    | ns    |       |

| t <sub>WSR</sub>     | Write setup time before RE low  | 0    | _    | 0    | _    | 0    | _    | ns    |       |

| t <sub>WCR</sub>     | Write hold time after RE low    | 20   | _    | 20   | _    | 25   | _    | ns    |       |

- 1. An initial pause of 100µs is required after power up followed by 8  $\overline{\text{CE}}$  before  $\overline{\text{RE}}$  refresh cycles for proper device operation

- 2. AC measurements assume  $t_T = 5$ ns.

- Operation within the t<sub>RCD</sub>(max) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only: If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled by t<sub>CAC</sub>.

- Operation within the t<sub>RAD</sub>(max) limit ensures that t<sub>RAD</sub>(max.) can be met. t<sub>RAD</sub>(max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max) limit, then access time is controlled by t<sub>AA</sub>.

- 5.  $t_{RCD}$  and  $t_{CAH}$  cannot be at minimum values simultaneously.  $t_{RCD}$  +  $t_{CAH}$   $\geq$  45ns (60ns  $t_{RAC}$  product),  $t_{RCD}$  +  $t_{CAH}$   $\geq$  50ns (70ns  $t_{RAC}$  product).

- t<sub>RWL</sub> and t<sub>RP</sub> cannot be at minimum values simultaneously. t<sub>RWL</sub> + t<sub>RP</sub> ≥ 60ns (60ns t<sub>RAC</sub> product), t<sub>RWL</sub> + t<sub>RP</sub> ≥ 70ns (70ns t<sub>RAC</sub> product).

- t<sub>CWL</sub> and t<sub>RP</sub> cannot be at minimum values simultaneously. t<sub>CWL</sub> + t<sub>RP</sub> ≥ 60ns (60ns t<sub>RAC</sub> product), t<sub>CWL</sub> + t<sub>RP</sub> ≥ 70ns (70ns t<sub>RAC</sub> product).

- 8. t<sub>CRP</sub> must be 15ns (60ns t<sub>RAC</sub>) or 17ns (70ns t<sub>RAC</sub>) if a write-per-bit mask is used on the following RE cycle due to the fact that t<sub>OFF</sub> must be met.

- 9. During Serial port write transfer  $t_{RCD}$  (max) = 100ns.

### Write Cycle

| Cumbal           | Doromotor                                                                                       | -6H  |      | -60  |      | -70  |      | Linita | Notes |

|------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol           | Parameter                                                                                       | Min. | Max. | Min. | Max. | Min. | Max. | Units  | Notes |

| t <sub>CWL</sub> | Write Command setup before $\overline{\text{CE}}$ high                                          | 10   | _    | 15   | _    | 17   | _    | ns     | 4     |

| t <sub>DH</sub>  | Data-in hold time after $\overline{\text{CE}}$ or $\overline{\text{W}}$ low, whichever is later | 6    | _    | 8    | _    | 8    | _    | ns     | 1     |

| t <sub>DHR</sub> | Data-in hold time after RE low                                                                  | 20   | _    | 20   | _    | 25   | _    | ns     |       |

| t <sub>DSC</sub> | Data-in setup before CE low                                                                     | 0    | _    | 0    | _    | 0    | _    | ns     |       |

| t <sub>DSW</sub> | Data-in setup before W low                                                                      | 0    | _    | 0    | _    | 0    | _    | ns     |       |

| t <sub>GHD</sub> | TRG high before data-in applied on primary port data pins                                       | 10   | _    | 15   | _    | 17   | _    | ns     |       |

| t <sub>RWL</sub> | Write setup time before RE high                                                                 | 10   | _    | 15   | _    | 17   | _    | ns     | 3     |

| t <sub>WCH</sub> | Write hold time after $\overline{\text{CE}}$ low                                                | 6    | _    | 6    | _    | 8    | _    | ns     |       |

| t <sub>WCS</sub> | Early write command setup before $\overline{\text{CE}}$ Low                                     | 0    | _    | 0    | _    | 0    | _    | ns     | 1, 2  |

| t <sub>WP</sub>  | Write command pulse width                                                                       | 6    | _    | 6    | _    | 8    | _    | ns     |       |

- 1. Data-in setup and hold is measured from the later of the two timings  $\overline{\text{CE}}$  /  $\overline{\text{UCE}}$  /  $\overline{\text{LCE}}$  or  $\overline{\text{W}}$  /  $\overline{\text{UW}}$  /  $\overline{\text{W}}$ .

- 2. t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>CPW</sub> are not restrictive parameters. They are included as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min) the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle; if t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>CPW</sub> ≥ t<sub>CPW</sub> (min) (Fast Page) mode, the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

- 3.  $t_{RWL}$  and  $t_{RP}$  cannot be at minimum values simultaneously.  $t_{RWL} + t_{RP} \ge 60$ ns (60ns  $t_{RAC}$  product),  $t_{RWL} + t_{RP} \ge 70$ ns (70ns  $t_{RAC}$  product).

- 4.  $t_{CWL}$  and  $t_{RP}$  cannot be at minimum values simultaneously.  $t_{CWL} + t_{RP} \ge 60$ ns (60ns  $t_{RAC}$  product),  $t_{CWL} + t_{RP} \ge 70$ ns (70ns  $t_{RAC}$  product).

### Read-Modify-Write Cycle

| Cumbal           | Parameter                                                                               | -6H  |      | -60  |      | -70  |      | Units  | Notes |

|------------------|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol           |                                                                                         | Min. | Max. | Min. | Max. | Min. | Max. | Ullits | Notes |

| t <sub>AWD</sub> | Column address to $\overline{W}$ low                                                    | 50   | _    | 50   | _    | 60   | _    | ns     | 1     |

| t <sub>CWD</sub> | $\overline{\sf CE}$ low before $\overline{\sf W}$ low                                   | 35   | _    | 35   | _    | 40   | _    | ns     | 1     |

| t <sub>OEH</sub> | Output disable ( $\overline{\text{TRG}}$ high) hold time from $\overline{\text{W}}$ low | 15   | _    | 15   | _    | 17   | _    | ns     |       |

| t <sub>RWC</sub> | Read-modify-write cycle time                                                            | 135  | _    | 135  | _    | 155  | _    | ns     |       |

| t <sub>RWD</sub> | $\overline{RE}$ low to $\overline{W}$ low                                               | 80   | _    | 80   | _    | 95   | _    | ns     | 1     |

<sup>1.</sup> t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>CPW</sub> are not restrictive parameters. They are included as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min) the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle; if t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>CPW</sub> ≥ t<sub>CPW</sub> (min) (Fast Page) mode, the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

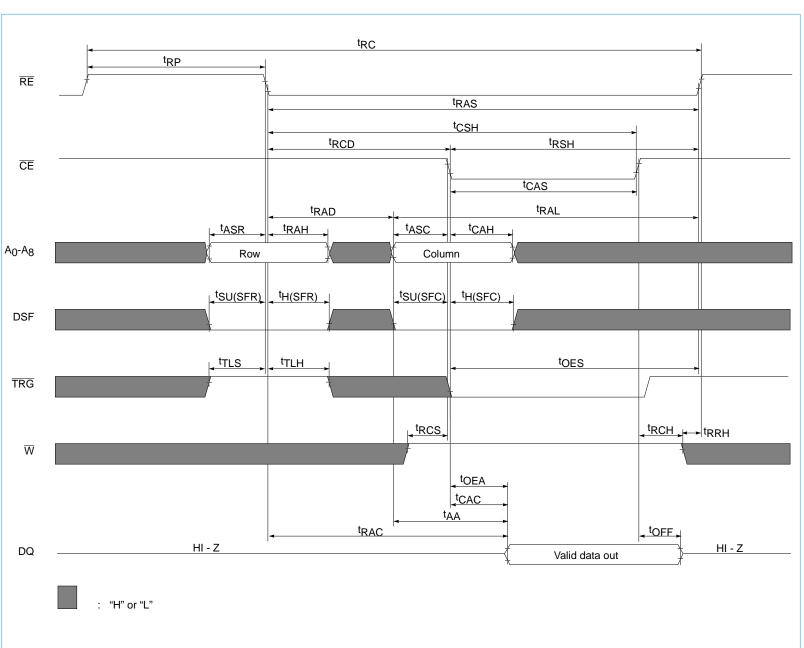

### **Read Cycle**

| Cumbal           | Parameter                                          | -6H  |      | -60  |      | -70  |      | Units | Notes   |

|------------------|----------------------------------------------------|------|------|------|------|------|------|-------|---------|

| Symbol           |                                                    | Min. | Max. | Min. | Max. | Min. | Max. | Units | notes   |

| t <sub>AA</sub>  | Access time from column address                    | _    | 25   | _    | 30   | _    | 35   | ns    | 2, 3    |

| t <sub>CAC</sub> | Access time from CE                                | _    | 15   | _    | 15   | _    | 17   | ns    | 1, 2, 3 |

| t <sub>OEA</sub> | Access time from TRG                               | _    | 15   | _    | 15   | _    | 17   | ns    |         |

| toes             | Output enable setup (TRG low) before RE high       | 10   | _    | 10   | _    | 10   | _    | ns    |         |

| toez             | Primary output disable from TRG high               | 0    | 10   | 0    | 15   | 0    | 17   | ns    |         |

| toff             | Primary output disable from $\overline{\text{CE}}$ | 0    | 10   | 0    | 15   | 0    | 17   | ns    | 5       |

| t <sub>RAC</sub> | Access time from RE                                | _    | 60   | _    | 60   | _    | 70   | ns    | 1, 2, 3 |

| t <sub>RAL</sub> | Column address to RE high                          | 25   | _    | 30   | _    | 35   | _    | ns    |         |

| t <sub>RCH</sub> | Read hold time after CE goes high                  | 0    | _    | 0    | _    | 0    | _    | ns    | 4       |

| t <sub>RCS</sub> | Read command setup time                            | 0    | _    | 0    | _    | 0    | _    | ns    |         |

| t <sub>RRH</sub> | Read command hold time to RAS high                 | 0    | _    | 0    | _    | 0    | _    | ns    | 4       |

- Operation within the t<sub>RCD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only: If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max.) limit, then access time is controlled by t<sub>CAC</sub>.

- 2. Operation within the t<sub>RAD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met t<sub>RAD</sub>(max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max.) limit, then access time is controlled by t<sub>AA</sub>.

- 3. Measured with the specified current and 50 pF load for the primary port. Output referenced levels:  $V_{OH} = 2.0V$  and  $V_{OL} = 0.8V$ .

- 4. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 5. t<sub>OFF</sub>(max.) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

### Fast Page Mode Read-Modify-Write-Cycle

| Cymhal | Down or other     | -6H                                         |      | -60  |      | -70  |      | Llaita | Notes |       |

|--------|-------------------|---------------------------------------------|------|------|------|------|------|--------|-------|-------|

|        | Symbol            | Parameter                                   | Min. | Max. | Min. | Max. | Min. | Max.   | Units | Notes |

|        | t <sub>RWCP</sub> | Fast page mode read-modify-write Cycle Time | 74   | _    | 74   | _    | 84   | _      | ns    |       |

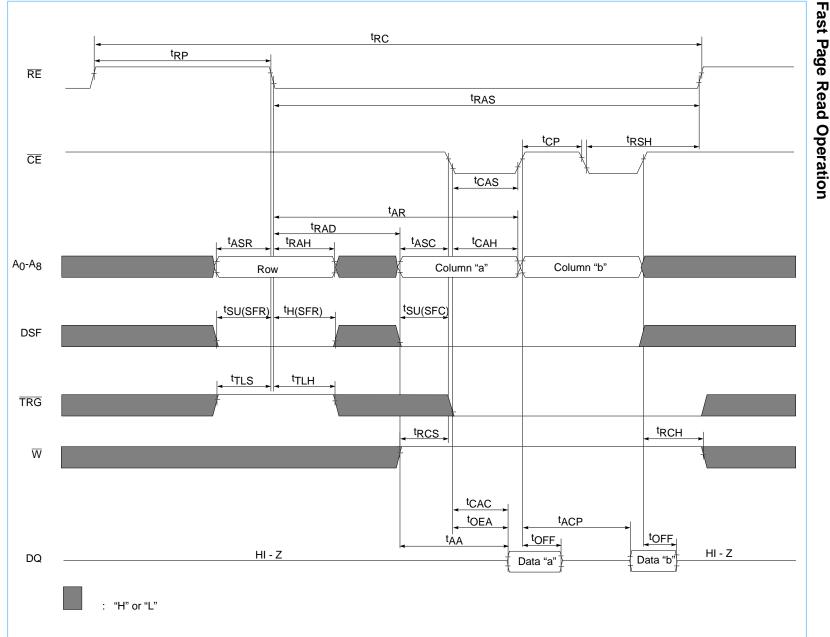

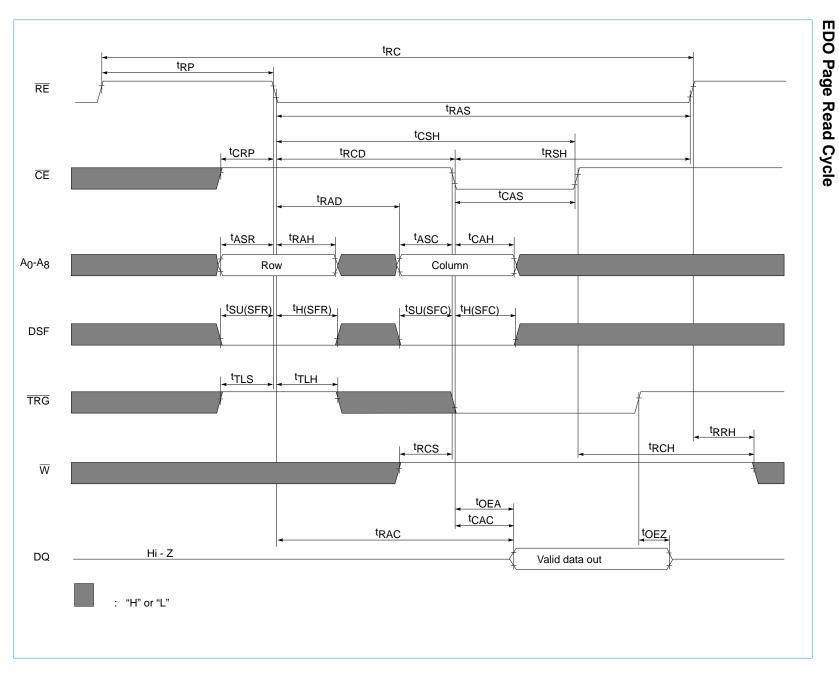

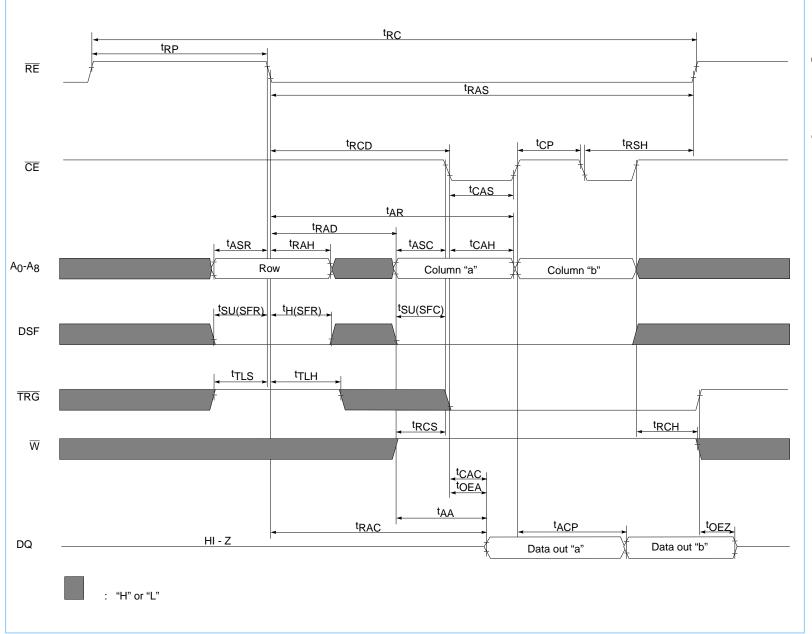

### **Page Mode Cycle**

| Symbol           | Parameter                     | -6H  |      | -60  |      | -7   | <b>'</b> 0 | Units  | Notes |

|------------------|-------------------------------|------|------|------|------|------|------------|--------|-------|

|                  |                               | Min. | Max. | Min. | Max. | Min. | Max.       | Offics | notes |

| t <sub>ACP</sub> | Access time from CE precharge | _    | 28   | _    | 35   | _    | 40         | ns     |       |

| t <sub>HPC</sub> | Extended data out cycle time  | 20   | _    | 25   | _    | 30   | _          | ns     |       |

| t <sub>PC</sub>  | Fast page mode cycle time     | 30   | _    | 35   | _    | 40   | _          | ns     |       |

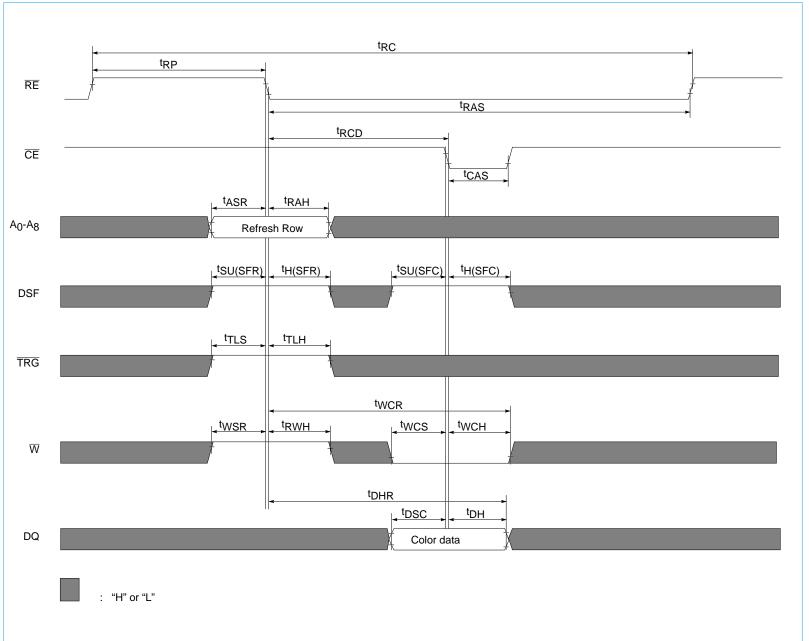

### **Refresh Cycle**

| Symbol           | Parameter                                         | -6H  |      | -60  |      | -70  |      | Units | Notes |

|------------------|---------------------------------------------------|------|------|------|------|------|------|-------|-------|

|                  |                                                   | Min. | Max. | Min. | Max. | Min. | Max. | Units | notes |

| t <sub>CHR</sub> | CE held low after RE low (CE before RE refresh)   | 6    | _    | 6    | _    | 8    | _    | ns    |       |

| t <sub>CSR</sub> | CE low setup before RE low (CE before RE refresh) | 5    | _    | 5    | _    | 5    | _    | ns    |       |

| t <sub>REF</sub> | Refresh period                                    | _    | 32   | _    | 32   | _    | 32   | ms    |       |

| t <sub>RPC</sub> | RE high to CE low precharge                       | 0    | _    | 0    | _    | 0    | _    | ns    |       |

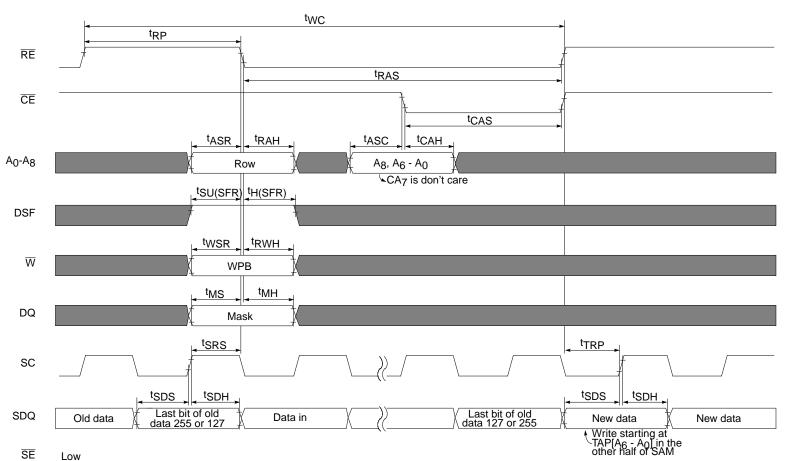

### Serial Read, Write and Transfer Cycle

| Countries al         | Doromotor                                                                                                                | -6   | SH   | -(   | 60   | -7   | 70   | Units | Notes |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|-------|

| Symbol               | Parameter                                                                                                                | Min. | Max. | Min. | Max. | Min. | Max. |       |       |

| t <sub>CSD</sub>     | CE low to first SC high after TRG goes high                                                                              | 15   | _    | 15   | _    | 17   | _    | ns    |       |

| t <sub>CTH</sub>     | Delay time from CE low to TRG high                                                                                       | 15   | _    | 15   | _    | 15   | _    | ns    |       |

| t <sub>d(RHMS)</sub> | Delay time, RE high to last (most significant rising edge of SC before boundary switch during split read transfer Cycles | 20   | _    | 20   | _    | 20   | _    | ns    |       |

| t <sub>DTH</sub>     | TRG hold after RE high                                                                                                   | 5    | _    | 5    | _    | 5    | _    | ns    |       |

| t <sub>d(TPRL)</sub> | Delay time, first (TAP) rising edge of SC after boundary switch to RE low during split read transfer cycles              | 15   | _    | 15   | _    | 17   | _    | ns    |       |

| t <sub>ESR</sub>     | SE setup before RE low                                                                                                   | 0    | _    | 0    | _    | 0    | _    | ns    |       |

| t <sub>RSD</sub>     | RE low to first SC high after TRG goes high                                                                              | 60   | _    | 60   | _    | 70   | _    | ns    |       |

| t <sub>RTH</sub>     | RE low to TRG high                                                                                                       | 45   | _    | 45   | _    | 55   | _    | ns    |       |

| t <sub>SC</sub>      | Width of SC high                                                                                                         | 4    | _    | 6    | _    | 7    | _    | ns    |       |

| t <sub>SCA</sub>     | Access time from SC going high                                                                                           | 3    | 12   | 3    | 15   | 3    | 17   | ns    | 1     |

| t <sub>SCC</sub>     | Serial clock cycle time                                                                                                  | 12   | _    | 18   | _    | 20   | _    | ns    |       |

| t <sub>SCP</sub>     | Width of SC low                                                                                                          | 4    | _    | 6    | _    | 7    | _    | ns    |       |

| t <sub>SDH</sub>     | Serial data-in hold time after SC high                                                                                   | 5    | _    | 5    | _    | 5    | _    | ns    |       |

| t <sub>SDS</sub>     | Serial data-in setup time to SC high                                                                                     | 2    | _    | 2    | _    | 2    | _    | ns    |       |

| t <sub>SEA</sub>     | Access time from SE going low                                                                                            | _    | 10   | _    | 12   | _    | 15   | ns    |       |

| t <sub>SFD</sub>     | Serial enable setup time to SC high                                                                                      | 3    | _    | 3    | _    | 3    | _    | ns    |       |

| t <sub>SEZ</sub>     | Serial output disable from SE high                                                                                       | 0    | 8    | 0    | 8    | 0    | 10   | ns    |       |

| t <sub>SOH</sub>     | Old Serial data out hold time after SC high                                                                              | 3    | _    | 3    | _    | 3    | _    | ns    |       |

| t <sub>SRS</sub>     | SC going high to RE low                                                                                                  | 8    | _    | 8    | _    | 10   | _    | ns    |       |

| t <sub>SWS</sub>     | TRG high to SC high (first serial clock after real time transfer)                                                        | 8    | _    | 8    | _    | 10   | _    | ns    |       |

| t <sub>TCH</sub>     | TRG hold time to CE high                                                                                                 | 8    | _    | 8    | _    | 10   | _    | ns    |       |

| t <sub>TRH</sub>     | TRG hold to RE high                                                                                                      | 8    | _    | 8    | _    | 10   | _    | ns    |       |

| t <sub>TRP</sub>     | RE high to SC high (Serial write transfer)                                                                               | 15   | _    | 15   | _    | 20   | _    | ns    |       |

| t <sub>TSL</sub>     | SC high delay to TRG high during a real time read transfer                                                               | 5    | _    | 5    | _    | 5    | _    | ns    |       |

<sup>1.</sup> Measured with the specified current and 30 pF load for the Serial port. Output referenced levels:  $V_{OH} = 2.0V$  and  $V_{OL} = 0.8V$ .

### Fast Page (FP) Read Cycle

### IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

$\| \mathbf{u} \mathbf{u} \|$

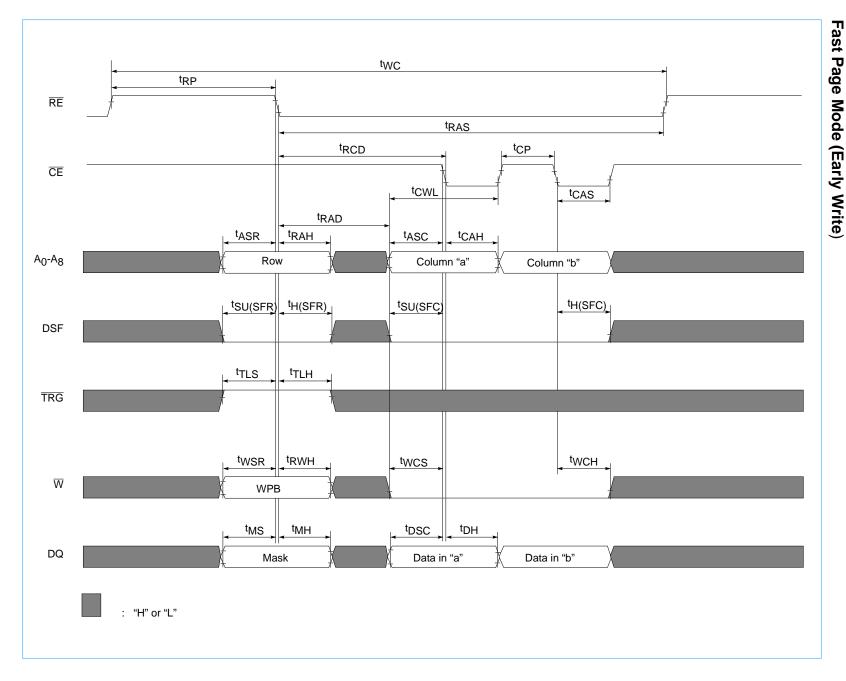

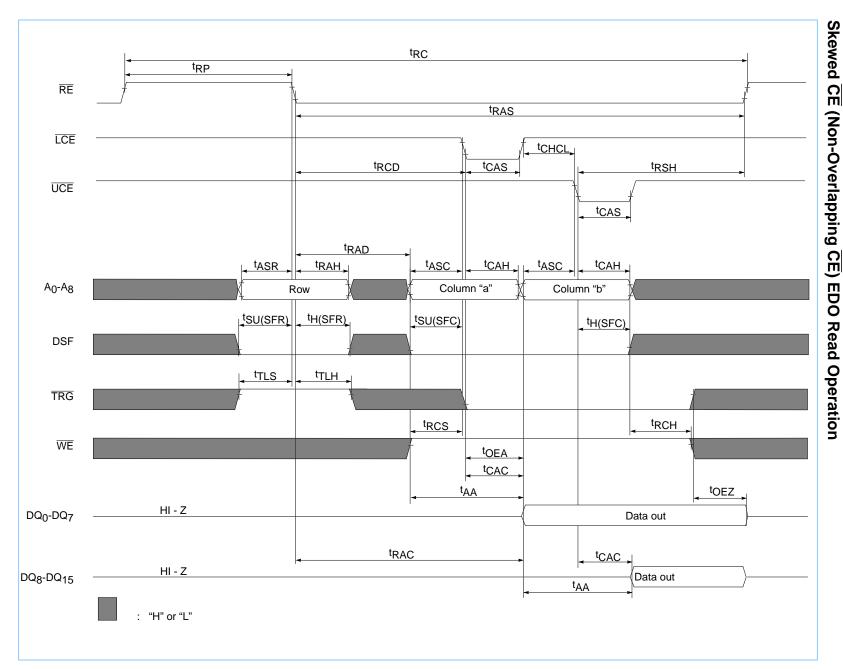

### **EDO Page Read Operation**

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

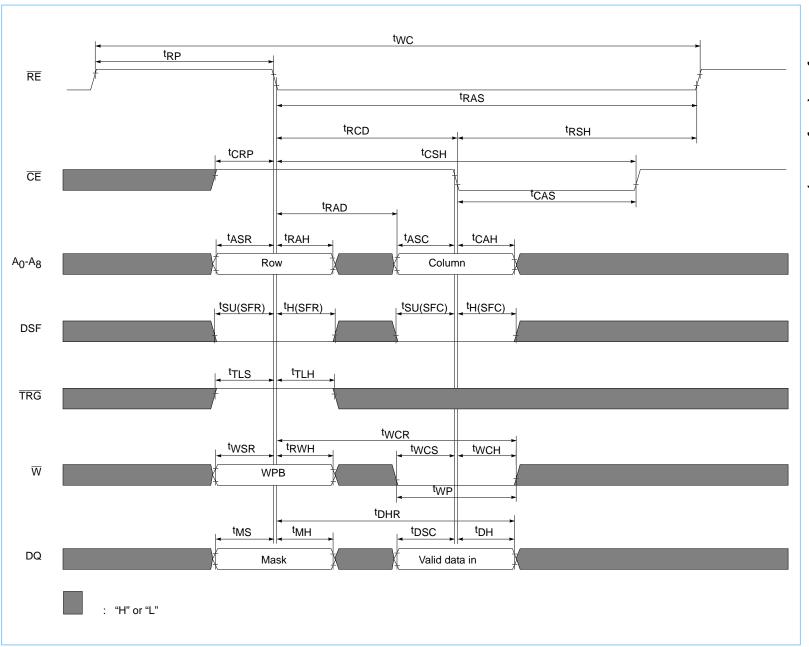

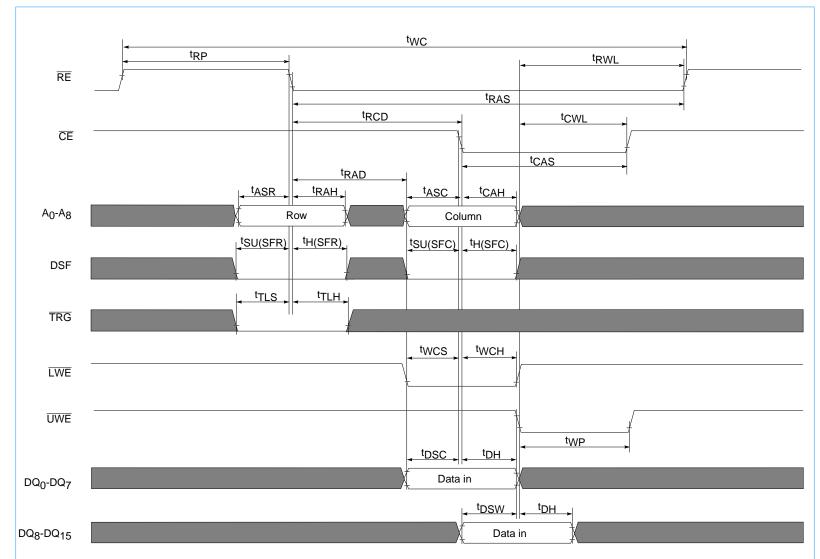

### Write Cycle (Early Write)

33G0307 SA14-4751-05 Revised 3/98

### IBM025170 IBM025160 IBM025171 IBM025161 256K X 16 MULTIPORT VIDEO RAM

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

### Write Cycle (Late Write)

### IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

$\| \mathbf{u} \mathbf{u} \|$

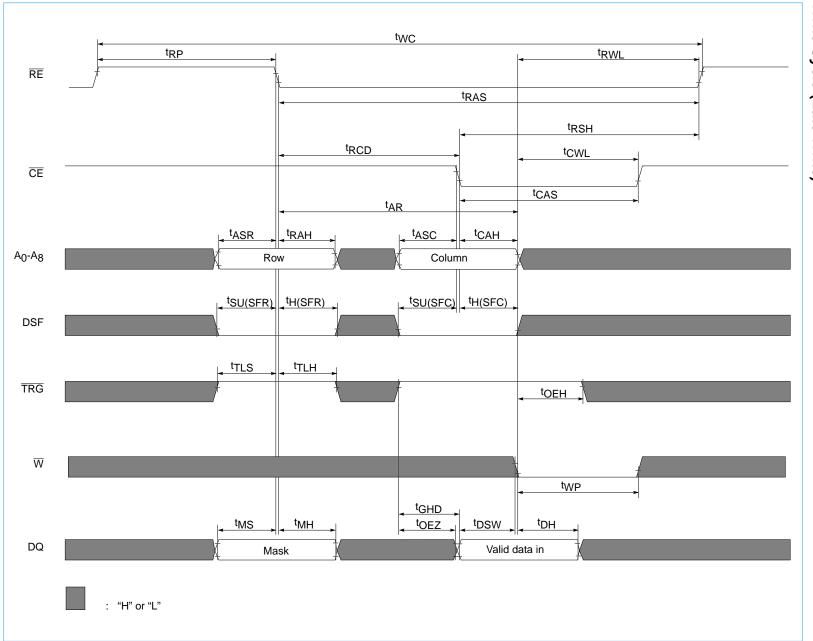

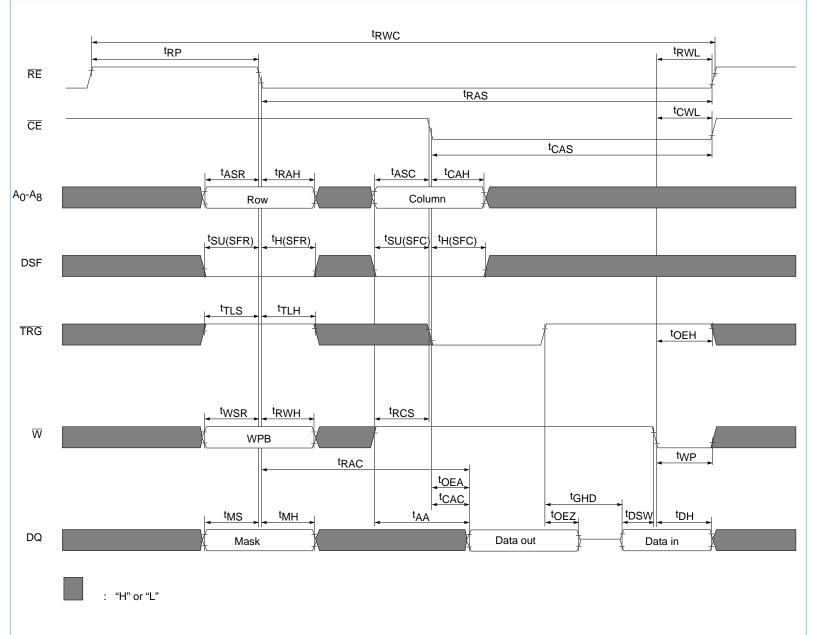

### **Read-Modify-Write Cycle**

Skewed

CE

EDO

### <sup>t</sup>RC t<sub>RP</sub> RE tRAS (Overlapping CE) **LCE** tCAS tCLCH, <sup>t</sup>RCD **UCE** tCAS tRAD <sup>t</sup>RAH tCAH tASC t<sub>ASR</sub> **Read Operation** A<sub>0</sub>-A<sub>8</sub> Row Column tSU(SFR) tH(SFR) tSU(SFC) DSF <sup>t</sup>TLS tTLH J TRG <sup>t</sup>RCH tRCS $\overline{\text{WE}}$ $t_{AA}$ <sup>t</sup>OEZ HI - Z $DQ_0-DQ_7$ Valid data out <sup>t</sup>RAC HI - Z DQ<sub>8</sub>-DQ<sub>15</sub> Valid data out tCAC : "H" or "L"

## IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

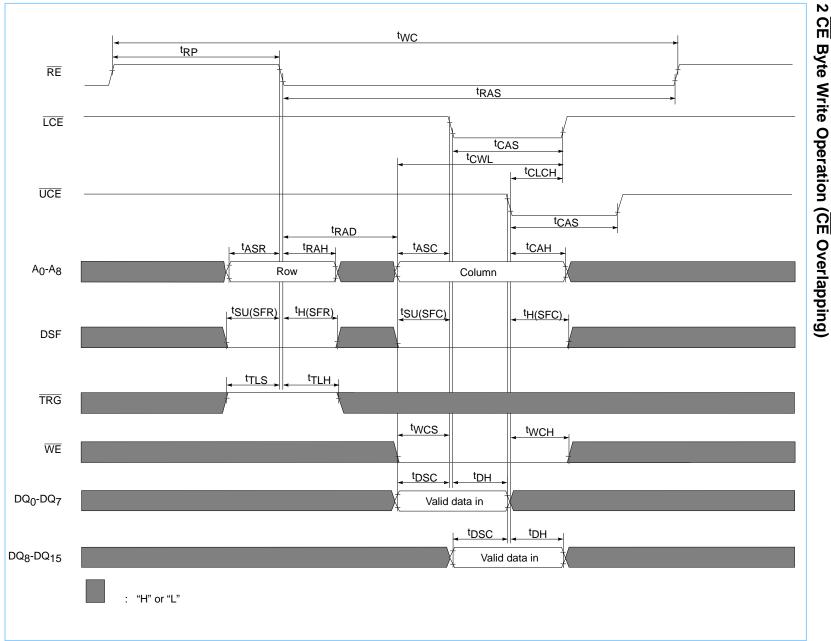

### CE Byte Write Operation (CE Overlapping)

: "H" or "L"

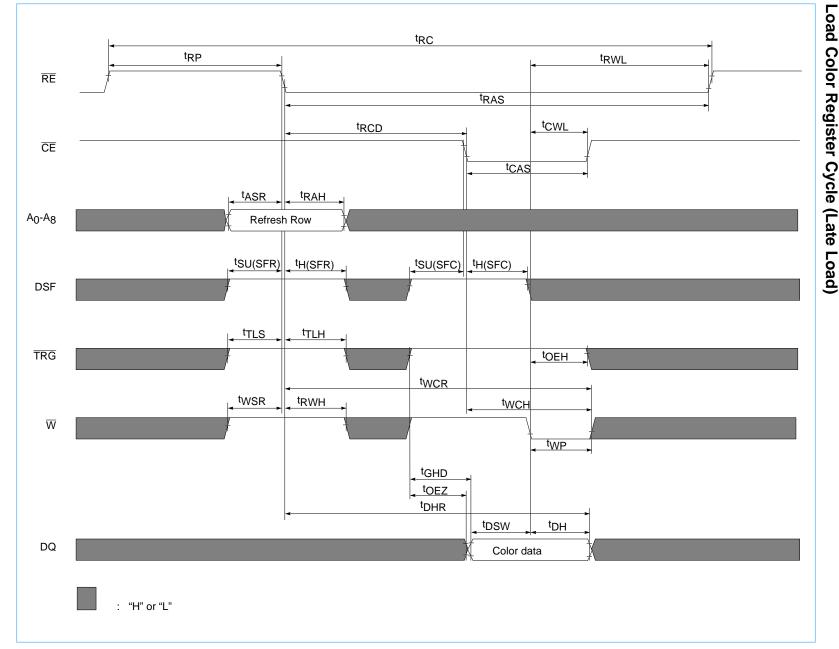

## Load Color Register Cycle (Early Load)

$\| \mathbf{u} \mathbf{u} \|$

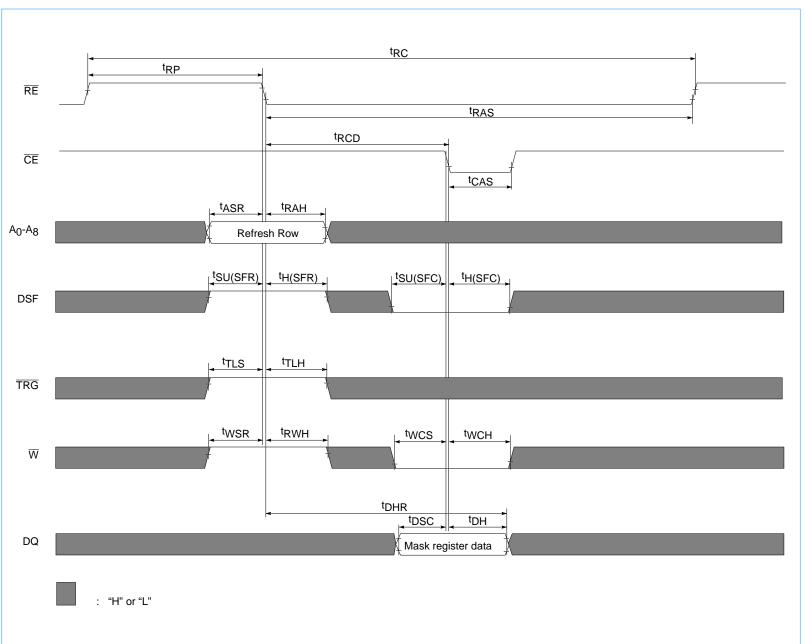

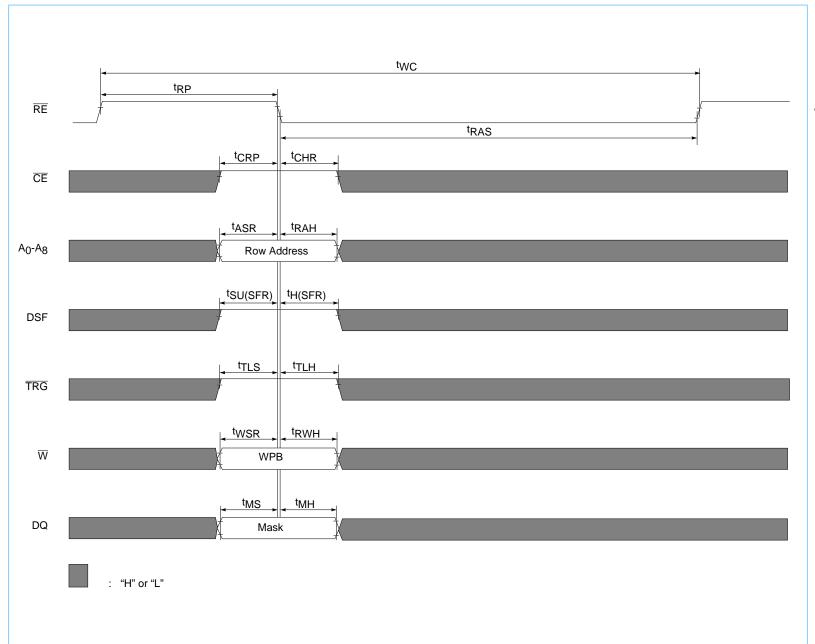

## Load Mask Register (Early Load)

IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

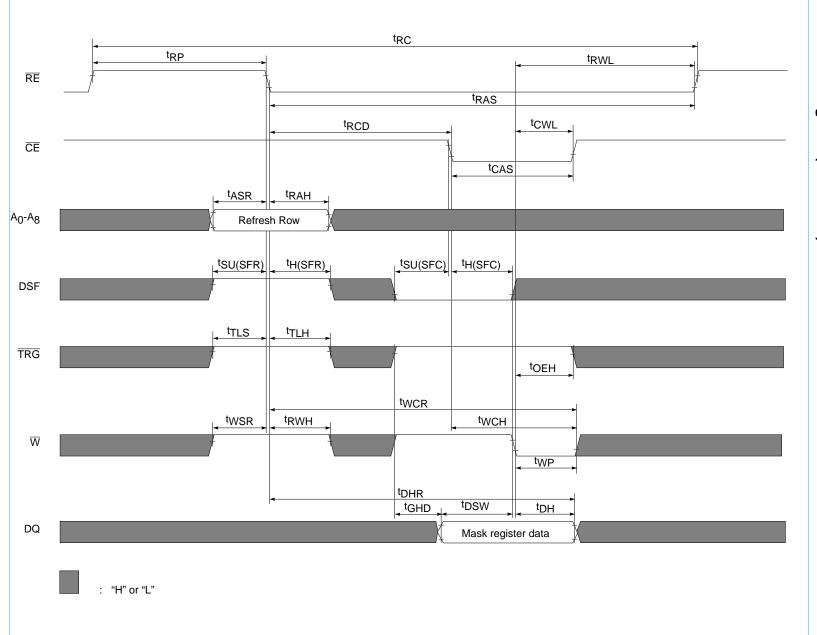

### Load Mask Register (Late Load)

###

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

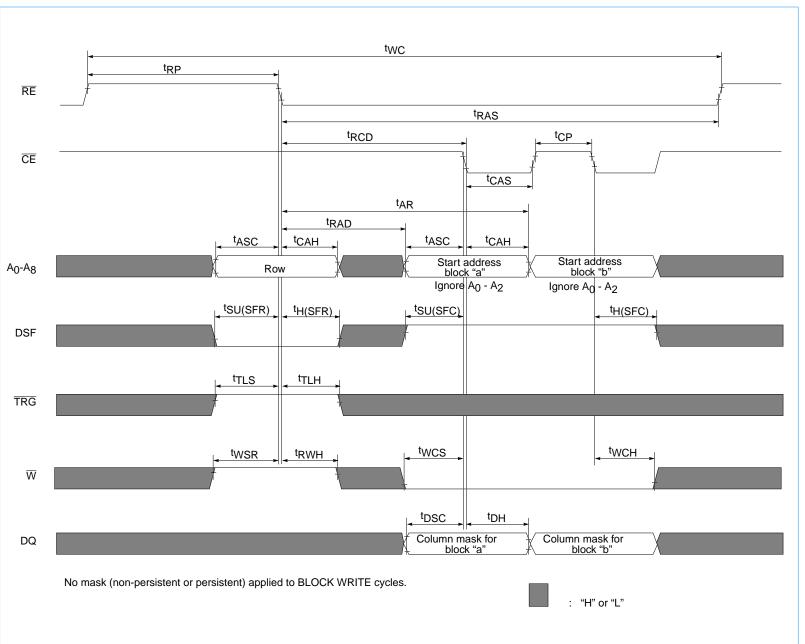

# Block Write (No Mask) Operation (Early Write)

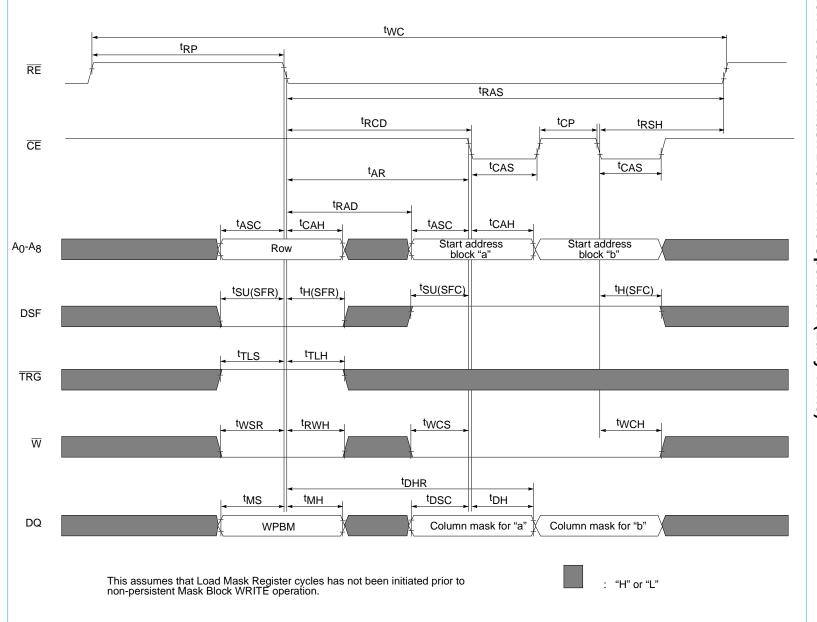

### IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM** Non-Persistent Mask Block Write Operation (Early Write)

###

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

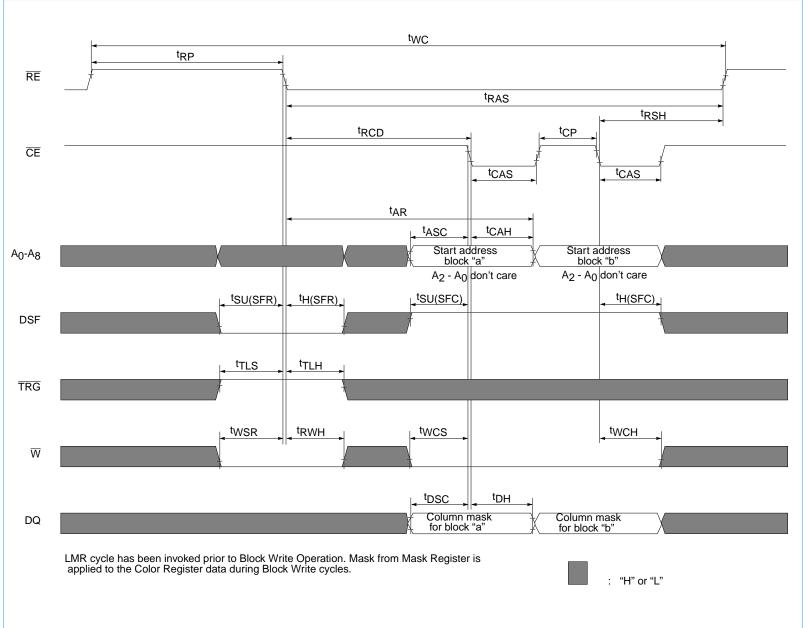

# Persistent Mask Block Write Operation (Early Write)

### IBM025170 IBM025160 IBM025171 IBM025161 256K X 16 MULTIPORT VIDEO RAM Flash Write Cycle

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

$\| \mathbf{u} \mathbf{u} \|$

Page 38 of 65

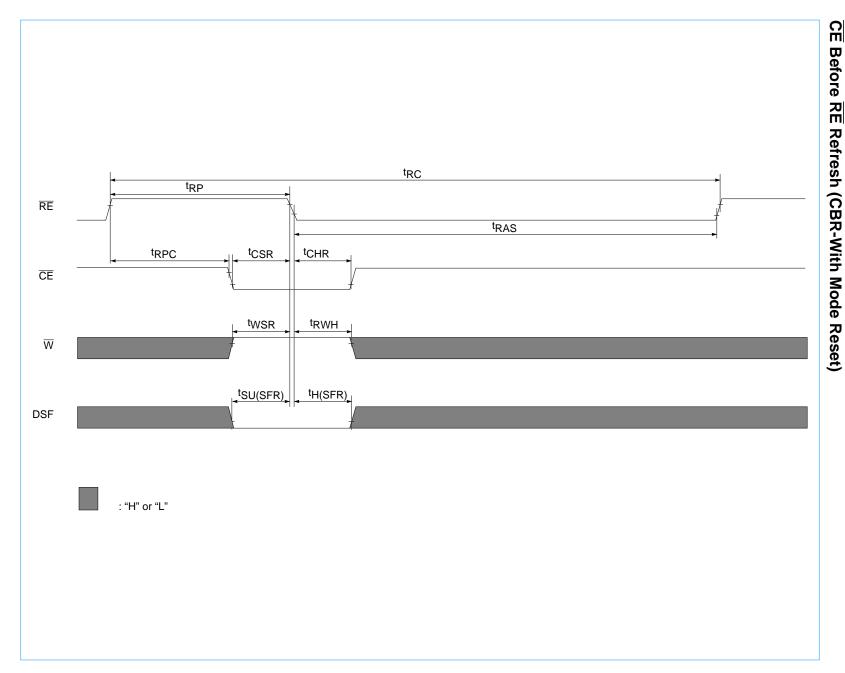

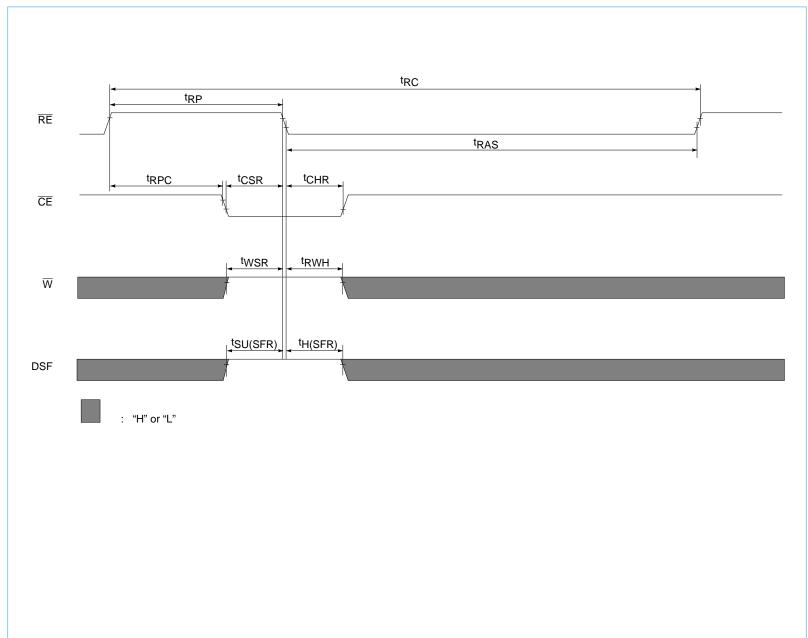

### CE Before R Refresh (CBRN-No Mode Reset)

$\| \mathbf{u} \mathbf{u} \|$

# SE

Page 40 of 65

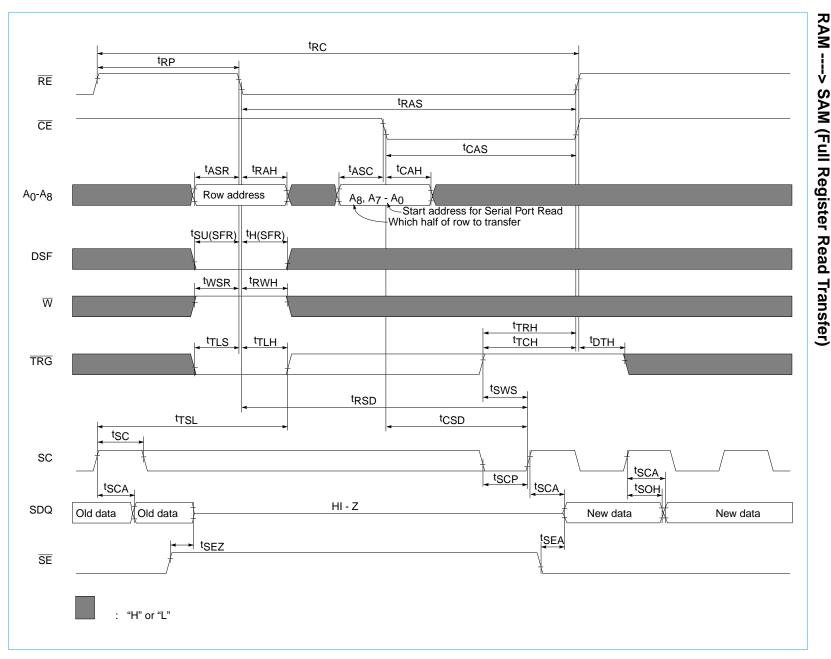

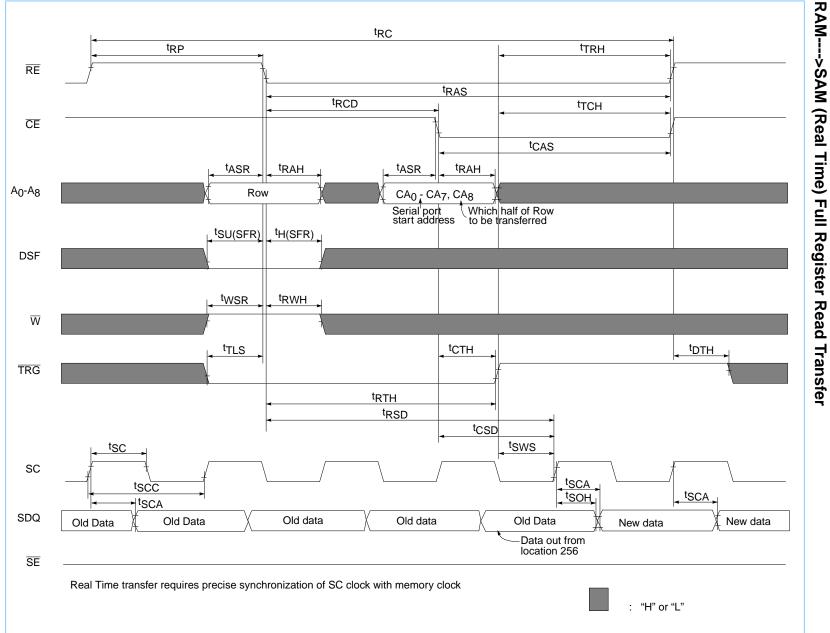

## SAM (Full Register Read Transfer)

||1111||

IBM025160 IBM025170 IBM025161 IBM025171 **256K X 16 MULTIPORT VIDEO RAM**

Never wait till the last moment to initiate a Split-Register Transfer.

## IBM025170 IBM025160 IBM025171 IBM025161 **256K X 16 MULTIPORT VIDEO RAM**

$\| \| \|$

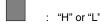

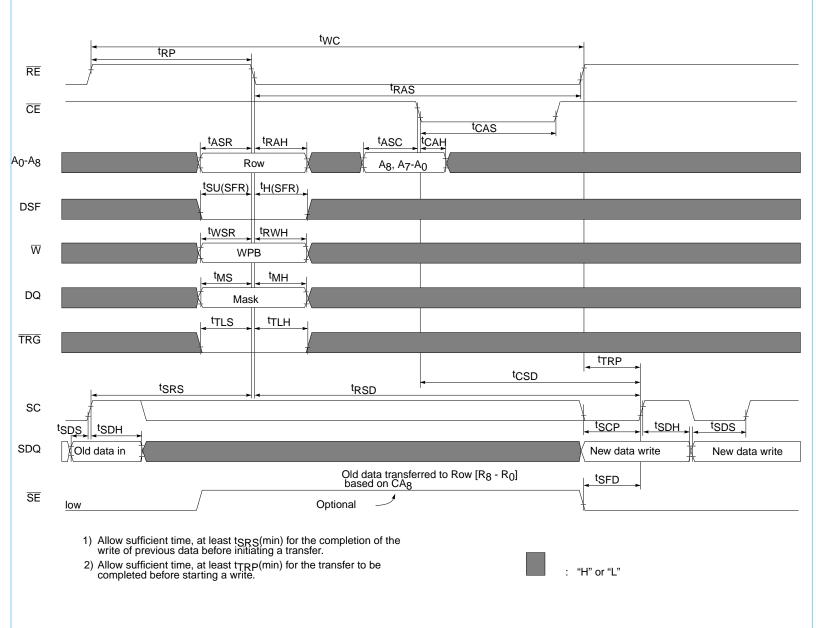

## **Full Register Write Transfer**

###

## Split Register Write Transfer

- Allow a delay of t<sub>SRS</sub>(min) to initiate a transfer from the time of writing the last bit [255 or 127] in the serial port. It is not a good idea to rush to start a Split Write Transfer especially when you have all the time on earth to initiate a Split Transfer.

- Allow at least tTRP(min) for the completion of a transfer cycle before start initiating the new data Write.

CAUTION: You can start a transfer from the particular half of SAM after few cycles of write in the other half of SAM. Don't wait till the last moment.

### **Functional Description**

The DRAM array is organized as 512 rows x 512 columns x 16 bit wide. The device is capable of performing normal Read/Write operations similar to a DRAM. Besides fast page Read/Write, the 4-Mb VRAM has the following added functions:

- Full Register Read Transfer

- Split Register Read Transfer

- Full Register Write Transfer

- Split Register Write Transfer

- 8 Column Block Write

- · Full Row Flash Write

- Extended Data Out (EDO)

- Serial Port Read

- · Serial Port Write

### **Power Up or VRAM Initialize Process**

After  $V_{CC}$  has reached its regulated value, allow at least 100 $\mu$ s for build up of N-well voltage inside the chip. Perform at least 8  $\overline{CAS}$ -Before- $\overline{RAS}$  (CBR) refresh cycles to reset unwanted mode(s) which may be set during power up. For more details refer to the Application Note, "Designing with 4-Mb VRAM". The Serial port will be initialized with the jump address of 128 bit at power up, thereby requiring no STOP address setting by the user for split Read or split Write in normal mode operations.

### **DRAM Refresh Operation**

DRAM array consists of volatile cells, therefore these cells need to be refreshed periodically. The minimum rate for VRAM is 512 refresh cycles every 32ms. Every cell therefore gets a chance to be refreshed every 32 ms. The SAM Registers memory is static in nature and therefore requires no refresh.

### The following refresh modes are available in IBM's 4-Mb VRAM:

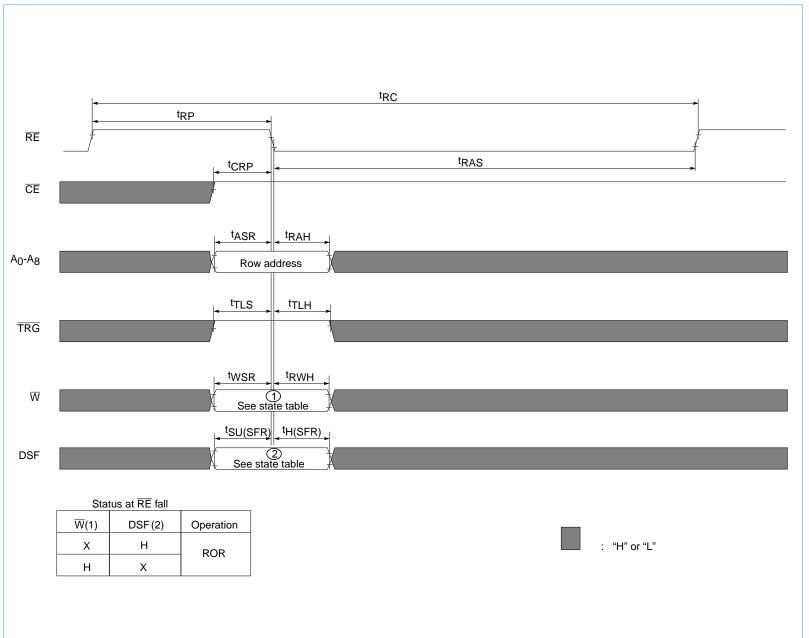

### RE Only Refresh (ROR)

A cycle having only  $\overline{RE}$  active refreshes all cells in one row of the storage array. A high  $\overline{CE}$  is maintained while  $\overline{RE}$  is active to keep DQs in high impedance.

Note that the row address for refresh is supplied by the user.  $\overline{RE}$  only Refresh mode will not clear any unknown modes at power up. Therefore, CBR cycles at power up must be performed to clear any unknown modes. The timing diagram on page 37 shows a  $\overline{RE}$  only Refresh mode.

### CE before RE Refresh (CBR)

The CBR Refresh mode is selected by bringing the  $\overline{CE}$  low before  $\overline{RE}$  is brought low and keeping DSF low as shown in the timing diagram on page 38. An internal address counter selects the row to be refreshed. *CBR cycle will reset any special modes set by CBRS or any persistent mask*. Note that DQs are in high-Z state during CBR cycle.

### CE before RE Refresh without mode Reset (CBRN)

CBRN mode is set by bringing  $\overline{CE}$  low before  $\overline{RE}$  is brought low and keeping  $\overline{W}$  and DSF high at the falling edge of  $\overline{RE}$ . The internal counter selects the row to be refreshed. *CBRN will neither clear any special modes set by the CBRS cycle nor any masks*.

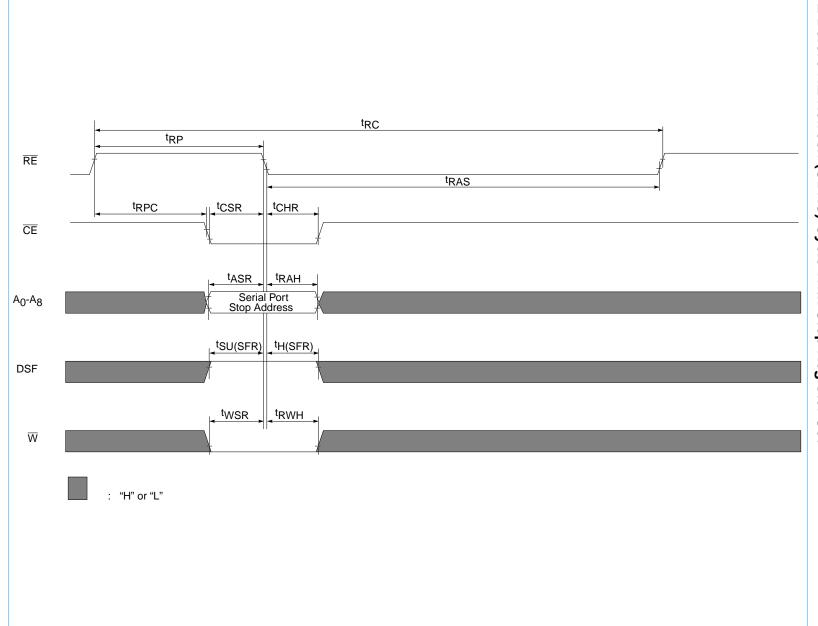

### **CE** before **RE** Refresh with Stop Register Set (CBRS)

The CBRS operation is selected by bringing  $\overline{W}$  and  $\overline{CE}$  low before  $\overline{RE}$  is brought low and keeping DSF high as shown in the timing diagram on page 40. An internal address counter selects the row to be refreshed. This cycle is also used to set the chip into Serial Register Stop mode (SRS). Full compatibility is provided between Half Depth SAM and Full Depth SAM by performing Split Transfer in SRS mode using STOP address of 127 or less. For more details, refer to Application Note, "Half SAM and Full SAM Compatibility".

### Recommended CBR, CBRS, and CBRN Cycles

To ensure that the device has not entered unwanted register modes at power up, at least *eight CBR cycles must be executed before normal operation of the device is resumed*. A CBR after each vertical retrace is recommended. This fail-safe routine is for cases where a system misoperation causes entry into an unwanted mode. If the STOP Register function is used, then a CBRS must be invoked following every CBR cycle. If the STOP register function is not required and Persistent Write masking is employed, then use a CBRN. CBRN does not clear the old mask.

### **Byte Control**

The 4-Mb VRAM is available with either Dual  $\overline{W}$  or Dual  $\overline{CE}$ . A dual  $\overline{CE}$  part has lower and upper byte control. The  $\overline{LCE}$  controls the DQ $_0$  -DQ $_7$  while  $\overline{UCE}$  controls DQ $_8$  - DQ $_{15}$ . Individual byte control can be applied during read and write operations on the primary port.

A dual  $\overline{W}$  part has a lower and upper  $\overline{W}$ . The  $\overline{LW}$  and  $\overline{UW}$  allow individual byte control of the DQs during write operations. The  $\overline{LW}$  controls DQ<sub>0</sub> -DQ<sub>7</sub> and  $\overline{UW}$  controls DQ<sub>8</sub> - DQ<sub>15</sub>. Individual byte control can be applied to the DRAM Read, Write, Block Write, Load Mask Register and Load Color Register cycles.

### **Read Cycle**

A Read cycle is executed by activating  $\overline{RE}$ ,  $\overline{CE}$ , and  $\overline{TRG}$  and by maintaining  $\overline{W}$  high while  $\overline{CE}$  is active. The DQs remain in high-Z until valid data appears at the output at access time. Device access time,  $t_{ACC}$ , will be the longest of the four calculated intervals:

- t<sub>RAC</sub> Access time from RE falling edge

- t<sub>RCD</sub> (RE to CE delay) + t<sub>CAC</sub> (Access time from CE falling edge)

- t<sub>RAD</sub> (RE to Column Address delay) + t<sub>AA</sub> (Access time from column Address)

- RE to TRG delay + t<sub>OFA</sub> (Access time from TRG)

Device dependent parameters are:  $t_{RAC}$ ,  $t_{CAC}$ ,  $t_{AA}$  and  $t_{OEA}$ . System dependent parameters are:  $t_{RCD}$ ,  $t_{RAD}$  and  $\overline{RE}$  to  $\overline{TRG}$  delay. Output becomes valid after the access time has elapsed. It remains valid while  $\overline{CE}$  and  $\overline{TRG}$  are low (Fast Page parts only). It remains valid while  $\overline{TRG}$  is low (EDO parts only). Either  $\overline{CE}$  or  $\overline{TRG}$  high returns the output pins to high-Z (Fast Page parts only).  $\overline{TRG}$  high returns the output pins to high-Z (EDO parts only).

### Write Cycle

A Write cycle is executed by bringing  $\overline{W}$  low during  $\overline{RE}/\overline{CE}$  cycle. The falling edge of  $\overline{CE}$  or  $\overline{W}$  whichever occurs later strobes the data on DQ pins into the on-chip data latch.

### **Early Write Cycle**

An early Write cycle is executed by bringing  $\overline{W}$  low before  $\overline{CE}$  falls. Data is strobed by  $\overline{CE}$  with setup and hold times referenced to this signal. This is the mode that is generally used for graphics applications.  $\overline{TRG}$  can be in any state while  $\overline{W}$  is active.

### **Late Write Cycle**

A late Write is executed by bringing  $\overline{W}$  low after  $\overline{CE}$  goes low. The input data is strobed by  $\overline{W}$  with setup and hold times referenced to  $\overline{W}$  signal. The late Write cycle is used for Read-Modify-Write operations.

### Write-per-Bit Mask (WPBM) Cycle

A Write-Per-Bit Mask cycle uses an I/O mask function to allow the system designer the flexibility of writing or not writing any combinations of DQ<sub>0</sub> through DQ<sub>15</sub>. Two types of masking are possible:

### 1. Non-persistent Mask or New mask

This mask has to be loaded at each  $\overline{RE}$  fall time as shown in the timing diagram on page 34.  $\overline{W}$  must be low as  $\overline{RE}$  falls. The DQs latched at  $\overline{RE}$  fall time are used as mask bits for Write cycle(s) for the particular  $\overline{RE}$  cycle. If mask bit is "1", the corresponding DQ input bit is written. If mask bit is "0", the corresponding DQ input is not written.

### 2. Persistent Mask or Old Mask

If a Load Mask Register cycle has been performed and has not been cleared by a CBR refresh cycle prior to a Write cycle, and  $\overline{W}$  is low at  $\overline{RE}$  fall time, data at DQ pins at  $\overline{RE}$  fall time will be ignored and the data from Mask Register is applied to the following:

- a. DQ inputs during Write cycles if  $\overline{W}$  is low at  $\overline{RE}$  fall time.

- b. Color Register data during Block Write and Flash Write cycles if  $\overline{W}$  is low at  $\overline{RE}$  fall time.

### Read-Write/Read-Modify-Write Cycle

A Read-Modify-Write is performed by first performing a normal Read, then tri-stating the DQ pins with  $\overline{TRG}$ , placing data to be written on the DQ pins, and then executing a Write operation. A WPBM can be loaded at the falling edge of  $\overline{RE}$ . The input data is strobed in reference to  $\overline{W}$ . This operation is illustrated in the timing diagram on page 24.

### **Load Mask Register Cycle**

In this cycle, data on DQ pins is written to a 16-bit write mask register, where it is retained and used by subsequent masked Write and masked Block Write cycles. This mask can be cleared by executing CBR cycle or by turning the power off. The mask data in the Mask Register can be changed by issuing another Load Mask Register cycle.

### **Load Color Register Cycle**

The load color register cycle is used to load the 16 bit color register, where it is retained to be used for data during Block Write and Flash Write operations.

### **Block Write Operation**

The Block Write Cycles are useful for clearing windows and for accelerating polygon fill operations. In all Block Write operations, the data is always supplied by the color register which is loaded by invoking a Load Color Register operation prior to the Block Write cycle(s). The color register data bits can individually be masked by either loading the mask at  $\overline{RE}$  fall time (non-persistent mask) provided that no Load Mask Register operation has been performed prior to invoking Block Write cycle(s). If a Load Mask Register operation has been performed and  $\overline{W}$  is low at  $\overline{RE}$  fall time, WPBM mask at  $\overline{RE}$  time will be ignored and the mask from the Mask Register (persistent mask) will be applied to the color data bits during Block Write cycle(s). *Iower or upper or both bytes can be written during Block Write cycle(s)*. Also a feature known as "individual Column masking" can be used to mask all or any of the 8 columns by loading the column mask at DQ pins at  $\overline{CE}$  fall time. This operation is illustrated in and the Application Note, "8 Column Block Write".

### DQ data at CE fall time during Block Write cycle(s)

DQ<sub>i</sub> = 0, Mask the selected column in the block

DQ<sub>i</sub> = 1, Write the data in the selected column in the block

| DQ0 | DQ1 | DQ2 | DQ3 | DQ4 | DQ5 | DQ6 | DQ7 | DQ8 | DQ9 | DQ10 | DQ11 | DQ12 | DQ13 | DQ14 | DQ15 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|

| 1L  | 2L  | 3L  | 4L  | 5L  | 6L  | 7L  | 8L  | 1U  | 2U  | 3U   | 4U   | 5U   | 6U   | 7U   | 8U   |

For example, if  $DQ_0$  is "0", mask the lower byte of column 1 in the block. If  $DQ_8$  is "1", write in the upper byte of column 1

1L = Lower byte of column 1.

1U = Upper byte of column 1.

### **Block Write (No Mask)**

The data from the color register is written to any or all of the eight columns starting with the column address  $A_8$ - $A_3$  ( $A_2$ ,  $A_1$ ,  $A_0$  are don't care). Any column or columns in a block of 8 columns can be masked by latching the DQ data at  $\overline{CE}$  fall time during Block Write page cycles in a way as illustrated in the timing diagram on page 33. **Both**  $\overline{W}$  **should be kept high at**  $\overline{RE}$  **fall time so that no mask is used at Block Write cycle time**.

### **Block Write (Non-persistent Mask)**

The WPBM is loaded by bringing  $\overline{W}$  low at  $\overline{RE}$  fall time and latching the data present at DQ pins. This mask is applied to the data from Color Register during Block Write page cycles. Note that the masked data is written to all or any of the non-masked columns in the selected block. The WPBM so latched at  $\overline{RE}$  fall time is applicable during that particular  $\overline{RE}$  active cycle time only.

### **Block Write (Persistent Mask or Old Mask)**

An LMR cycle is initiated to load the Mask Register prior to executing a Block Write operation with persistent mask. The 16-bit Mask Register supplies the bit mask for color register data during page mode Block Write cycles. This masked data is then written to all or any of the non-masked columns in the 8-column block.  $\overline{W}$  is low at  $\overline{RE}$  time and any data on DQ pins at  $\overline{RE}$  fall time will be ignored. To clear the persistent mask, a CBR cycle is initiated.

### 256K X 16 MULTIPORT VIDEO RAM

### Flash Write

The Flash Write operation causes an entire row (512 x 16 bits) of data to be written with the contents of the color register. The color register must be loaded on a previous Load Color Register (LCR) cycle. The Flash Write operation can be without Mask, with new mask WPBM or old mask WPBM as explained in mask write operations. The only difference is that the mask is applied for the data in the whole row. **Note that there is no provision for individual byte control, therefore both the bytes will be written or masked**.

### **Fast Page Cycle Operation**

Fast page mode cycles allow faster memory access by using the same row address while successive column addresses are strobed onto the chip. The  $\overline{RE}$  signal is kept low while successive  $\overline{CE}$  cycles are executed. The data rate is faster because row addresses are maintained internally and do not have to be reapplied. In fast page mode operation, Read, Write, Read-modify-Write cycles may be executed. During a Fast-page read cycle, the DQ pins stay in high-Z until valid data appears at the output pins at access time. The access time in this cycle will be the longest of the following intervals.

$t_{ACP}$  = Access time from start of column precharge  $t_{CP} + t_T + t_{CAC}$  = Column precharge time + transition time + Access time from  $\overline{CE}$  fall time =  $\overline{CE}$  high to column address delay +  $t_{AA}$

### **Extended Data Out (EDO)**

In extended data out mode, the primary port output drivers are not turned off by the rising edge of  $\overline{CE}$ . As rising edge of  $\overline{CE}$  does not turn off the data, the resulting longer data valid time allows speedup of the fast page cycle time. Fast page mode applications that try to run at minimum cycle times find that timing skews and propagation delays make the data valid time so narrow that reliable sampling is impossible. EDO solves this problem by providing longer data valid time. The device access time is the longest of the following intervals:

- t<sub>ACP</sub>

- t<sub>AA</sub>

- t<sub>CAC</sub>

The detailed explanation of EDO and Fast Page is given in the Application Note, "EDO for Higher Bandwidth".

### **Serial Port Operation**

The Serial port is always in either Read or Write mode. To switch the Serial port from Read to Write or vice versa, a Transfer operation of the appropriate type must be executed. A Read Transfer operation will put the Serial port into Read mode if it is not already in Read mode. A Write Transfer will switch the Serial port into Write mode if it is not already in Write mode. To prevent storing of the current contents of the SAM when first switching to Write mode, a Write transfer operation with the WPBM set to block all 16 bits should be performed. when  $\overline{SE}$  is low, each serial clock will cause a Read/Write of the SAM location addressed by the internal Serial port address counter. When  $\overline{SE}$  is high, the Serial port is disabled for Read/Write, and the SDQs are in high-Z state. Note that Each SC clock causes the internal address counter to increment independent of the state of  $\overline{SE}$ .

### **Transfer Modes**

The following Transfer Modes are available:

- 1. Full Read Transfer (Normal) Mode.

- 2. Split Read Transfer (Normal) Mode.

- 3. Full Read Transfer (SRS) Mode.

- 4. Split Read Transfer (SRS) Mode.

- 5. Full Write Transfer (Normal) Mode.

- 6. Split Write Transfer (Normal) Mode.

- 7. Full Write Transfer (SRS) Mode.

- 8. Split Write Transfer (SRS) Mode.

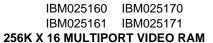

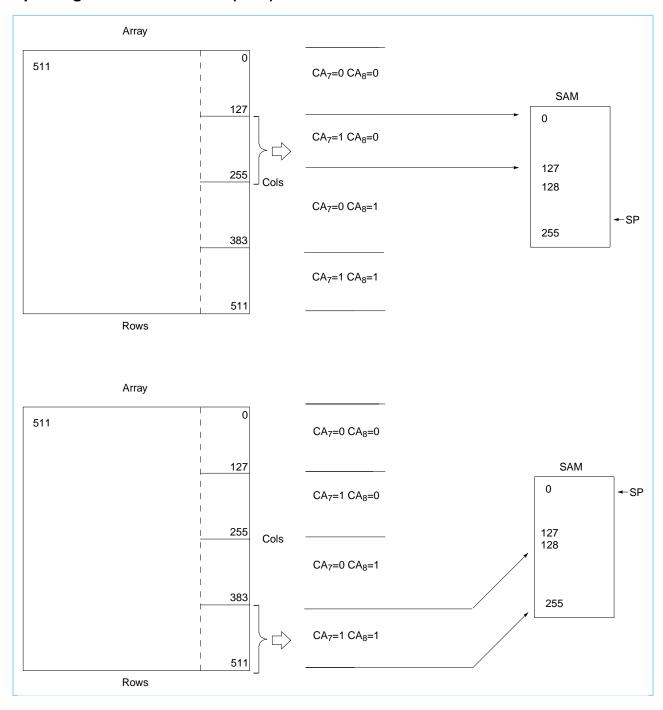

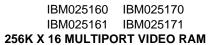

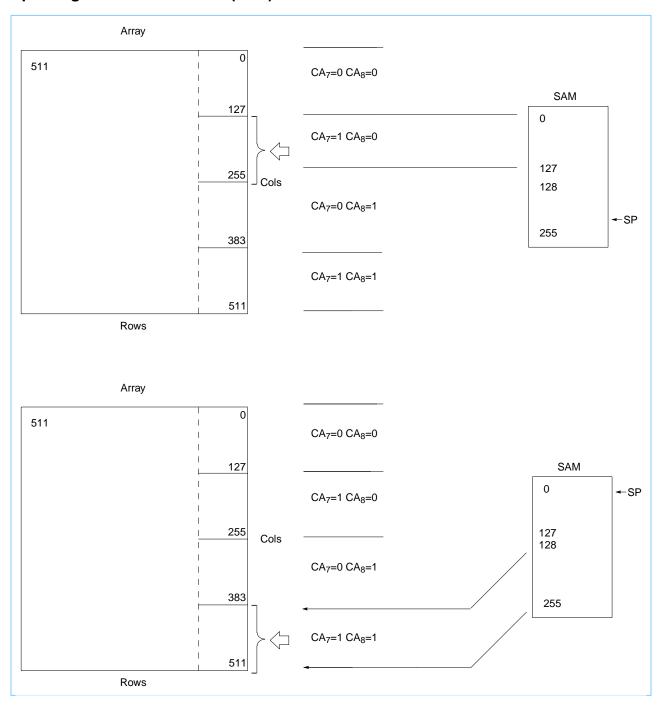

### Full Register Read Transfer (Normal) Mode

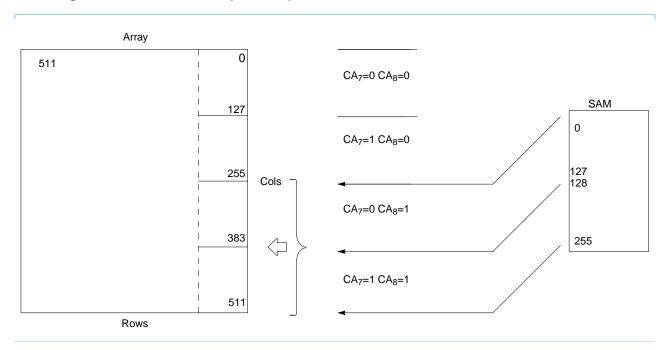

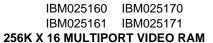

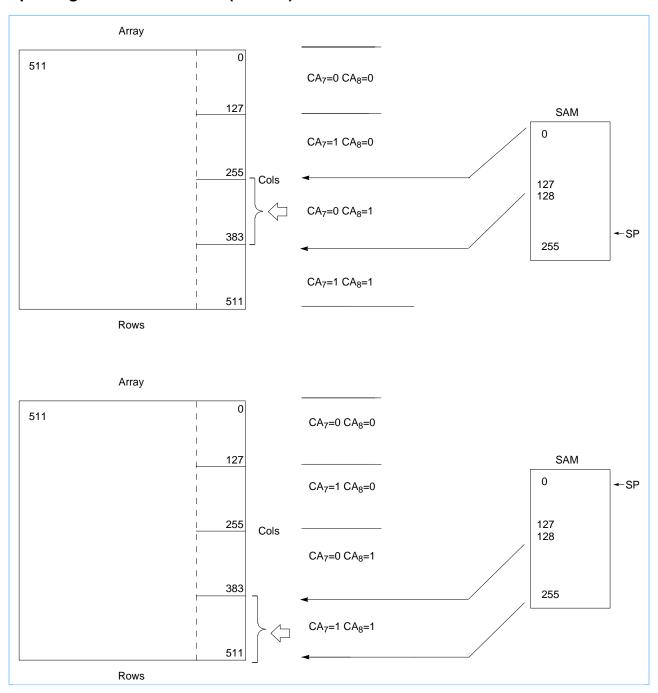

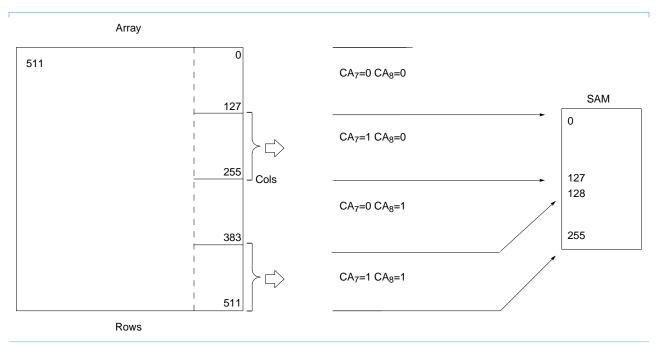

The Full Register Read Transfer operation is illustrated in the timing diagram on page 41. This operation will load the entire SAM (256 x16 bits) from the selected segment of the row.  $CA_8$  controls which half of the selected row needs to be transferred. If  $CA_8$  at  $\overline{CE}$  fall time is "0", the lower half of the selected row is transferred. If  $CA_8$  at  $\overline{CE}$  fall time is "1", the upper half of the selected row is transferred.  $CA_7$ - $CA_0$  address supplied by the user at  $\overline{CE}$  fall time is used to provide the starting address for reading of data from the Serial port. The SAM has 256 locations to be addressed starting from 0 to 255. During the Full Read Transfer cycle the Start Address Register as well as the Serial port counter will be loaded, with the user supplied address  $CA_7$ - $CA_0$ .  $CA_7$  equals "0" is associated with the lower half of the SAM and  $CA_7$  equals "1" is associated with the upper half of the SAM. A Full Register Read Transfer from the selected row to SAM is shown in the timing diagram on page 51. The example shows a transfer based on user supplied  $CA_8$  equals "1". The Serial port counter is set to the address  $CA_7$ - $CA_0$  specified by the user at  $\overline{CE}$  fall time during the Full Read Transfer cycle. The next SC cycle following the transfer will start reading data from this point in the SAM. Reading will continue until the end of the SAM location 256 and will wrap around. To keep Serial data out continuous, either a Split Read Transfer or a Full Read Transfer must be executed as the SAM runs out of new data. See the timing diagrams for the necessary timing requirements for either method of loading the SAM

### Full Register Read Transfer (Normal) Mode

### 256K X 16 MULTIPORT VIDEO RAM

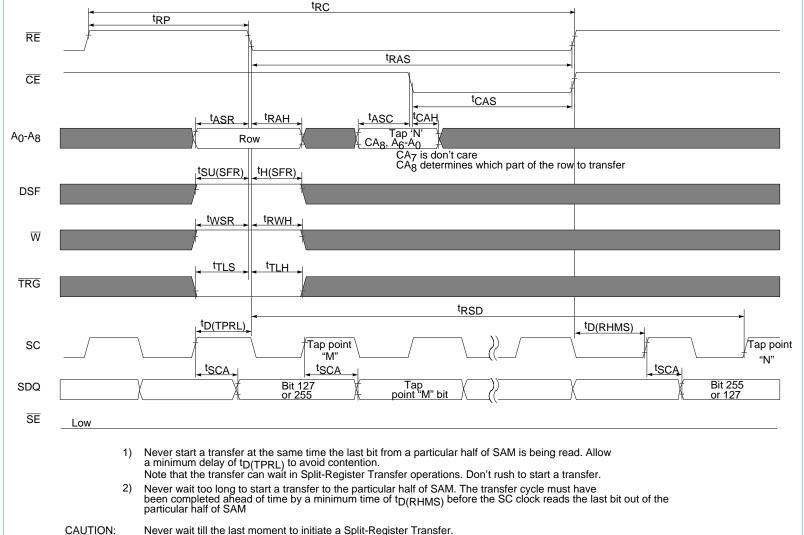

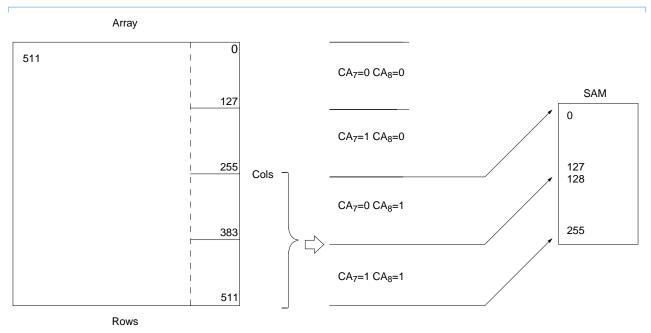

### Split Register Read Transfer (Normal) Mode

The Split Read Transfer is used to read data continuously from the Serial port without having to worry about synchronizing the SC clock with the operation of the primary port. This transfer operation loads 128 x16 bits of a wordline into half of the SAM. The user supplied column address bit " $CA_8$ " and an internally generated " $CA_7$ " determines which quarter of the word line is transferred to the SAM.

Note the user supplied " $CA_7$ " at  $\overline{CE}$  fall time during transfer cycle is a don't care and is internally generated based on which half of the SAM is active. This way, the inactive half of SAM can be loaded with the new data while data is being read out of the other active half. The start address is given by  $CA_6$  -  $CA_0$  but is held in a TAP address pointer register until the serial counter reaches the jump address (127/255). At that point, the start address register is loaded with the address from the TAP address register. The Serial port counter will also be loaded with this address at the same time. The reading of data will start from this address in the other half of SAM that was previously inactive at the next SC clock. The Split Read Transfer in normal mode is illustrated in the timing diagram on page 43.

The example in the timing diagram on page 53 illustrates a Split Read Transfer between DRAM and SAM based on user supplied  $CA_8$  during Split Read Transfer cycle and an internally generated  $CA_7$ . In the first example ( $CA_8 = 1$ ), the Serial port is active reading data from the upper half of the SAM while the lower half of SAM is idling. Therefore,  $CA_7$  is internally changed to "0" and the transfer is forced to lower half of SAM. In the second example, the Serial port is active reading data from the lower half of SAM, the transfer is therefore forced to the upper half of SAM.