#### 32K X 36 BURST SRAM

#### **Features**

- 32K x 36 Organization

- 0.5μ CMOS Technology

- Supports PowerPC™ Processor Operation

- Single +3.3V  $\pm$  5% Power Supply and Ground

- 5V Tolerant I/O

- LVTTL I/O Compatible

- Fast OE times: 4, 5, 6ns

- Common I/O

- Registered Addresses, Data Ins and Control Signals

- · Asynchronous Output Enable

- Self-Timed Write Operation and Byte Write Capability

- Low Power Dissipation

- 960 mW Active at 66MHz

- 90 mW Standby

- 100 Pin Thin Quad Flat Pack

### **Description**

IBM Microelectronics 1M SRAM is a Synchronous Burstable, high performance CMOS Static RAM that is versatile, wide I/O, and achieves 8 nsec access. A single clock is used to initiate the read/write operation and all internal operations are self-timed. At the rising edge of the Clock, all Addresses, Data Ins and Control Signals are registered internally. Burst mode operation, is accomplished by integrating input registers, internal 2-bit burst counter and high speed SRAM in a single chip. Burst reads are initiated with either ADSP or ADSC being LOW with a valid address during the rising edge of clock. Data from this address plus the three subsequent addresses will be output. The chip is operated with a single +3.3 V power supply and is compatible with LVTTL I/O interfaces.

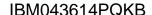

### X36 TQFP Pin Array Layout

# **Pin Description**

| A0-A14    | Address input                            | ADSP            | Address Status Processor    |

|-----------|------------------------------------------|-----------------|-----------------------------|

| DQa - DQd | Data Input/Output (0-8,9-17,18-26,27-35) | ADSC            | Address Status Controller   |

| CLK       | Clock                                    | ĀDV             | Burst Advance Control       |

| WEa       | Write Enable, Byte a (0 to 8)            | CS              | ADSP Gated Chip Select      |

| WEb       | Write Enable, Byte b (9 to 17)           | $V_{DD}$        | Power Supply (+3.3V)        |

| WEc       | Write Enable, Byte c (18 to 26)          | V <sub>SS</sub> | Ground                      |

| WEd       | Write Enable, Byte d (27 to 35)          | $V_{DDQ}$       | Output Power Supply (+3.3V) |

| ŌĒ        | Output Enable                            | NC              | No Connect                  |

| CS2, CS2  | Chip Selects                             |                 |                             |

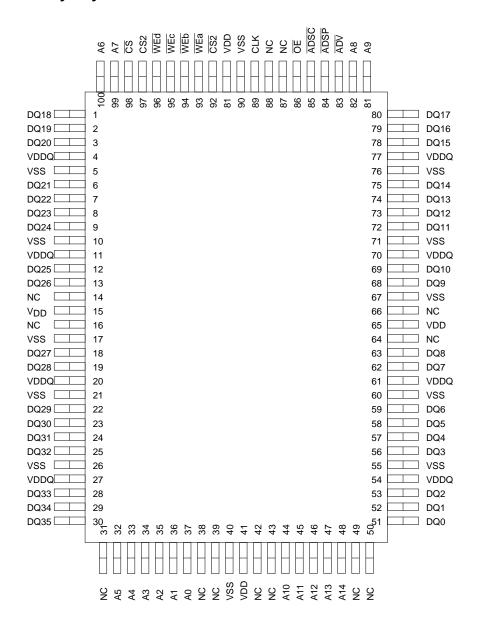

# **Block Diagram**

### **Ordering Information**

| Part Number      | Organization | Speed                      | Leads        | Notes |

|------------------|--------------|----------------------------|--------------|-------|

| IBM043614PQKB-8  | 32K x 36     | 8 ns Access / 15 ns Cycle  | 100 pin TQFP |       |

| IBM043614PQKB-9  | 32K x 36     | 9 ns Access / 15 ns Cycle  | 100 pin TQFP |       |

| IBM043614PQKB-10 | 32K x 36     | 10 ns Access / 15 ns Cycle | 100 pin TQFP |       |

| IBM043614PQKB-11 | 32K x 36     | 11 ns Access / 15 ns Cycle | 100 pin TQFP |       |

#### **Burst SRAM Clock Truth Table**

| CLK | CS2 | CS2 | <del>cs</del> | ADSP | ADSC | ADV | WE | ŌĒ | DQ     | Operation                                  |

|-----|-----|-----|---------------|------|------|-----|----|----|--------|--------------------------------------------|

| L→H | Н   | Х   | L             | L    | Х    | Х   | Х  | Х  | High-Z | Deselected Cycle                           |

| L→H | X   | L   | L             | L    | Х    | Χ   | Х  | Х  | High-Z | Deselected Cycle                           |

| L→H | Н   | Х   | X             | Х    | L    | Х   | Х  | Х  | High-Z | Deselected Cycle                           |

| L→H | X   | L   | X             | Х    | L    | X   | X  | X  | High-Z | Deselected Cycle                           |

| L→H | L   | Н   | L             | L    | Х    | Х   | Х  | L  | Q      | Read from External<br>Address, Begin Burst |

| L→H | L   | Н   | L             | L    | Х    | Х   | Х  | Н  | High-Z | Read from External<br>Address, Begin Burst |

| L→H | L   | Н   | L             | Н    | L    | Х   | Н  | L  | Q      | Read from External<br>Address, Begin Burst |

| L→H | L   | Н   | L             | Н    | L    | Х   | L  | Х  | D      | Write to External<br>Address, Begin Burst  |

| L→H | Х   | Х   | Х             | Н    | Н    | L   | Н  | L  | Q      | Read from next Add.,<br>Continue Burst     |

| L→H | Х   | Х   | Х             | Н    | Н    | L   | L  | Х  | D      | Write to next Add.,<br>Continue Burst      |

| L→H | Х   | Х   | Х             | Н    | Н    | Н   | Н  | L  | Q      | Read from Current<br>Add., Suspend Burst   |

| L→H | Х   | Х   | Х             | Н    | Н    | Н   | L  | Х  | D      | Write to Current Add.,<br>Suspend Burst    |

| L→H | X   | Х   | Н             | Х    | L    | Х   | Χ  | Х  | High-Z | Deselect Cycle                             |

| L→H | Х   | Х   | Н             | Х    | Н    | L   | Н  | L  | Q      | Read from next Add.,<br>Continue Burst     |

| L→H | Х   | Х   | Н             | Х    | Н    | L   | L  | Х  | D      | Write to next Add.,<br>Continue Burst      |

| L→H | Х   | Х   | Н             | Х    | Н    | Н   | Н  | L  | Q      | Read from current<br>Add., Suspend Burst   |

| L→H | Х   | Х   | Н             | Х    | Н    | Н   | L  | Х  | D      | Write to current Add.,<br>Suspend Burst    |

<sup>1.</sup> For a write operation preceded by a read cycle,  $\overline{\text{OE}}$  must be HIGH early enough to allow Input Data Setup, and must be kept HIGH through Input Data Hold Time.

2. WE refers to WEa, WEb, WEc, WEd.

# **Burst Sequence Truth Table**

| External Address | A14-A2 |       | Notos |       |       |       |

|------------------|--------|-------|-------|-------|-------|-------|

|                  | A14-A2 | (0,0) | (0,1) | (1,0) | (1,1) | Notes |

| 1st Access       | A14-A2 | (0,0) | (0,1) | (1,0) | (1,1) |       |

| 2nd Access       | A14-A2 | (0,1) | (1,0) | (1,1) | (0,0) |       |

| 3rd Access       | A14-A2 | (1,0) | (1,1) | (0,0) | (0,1) |       |

| 4th Access       | A14-A2 | (1,1) | (0,0) | (0,1) | (1,0) |       |

<sup>3.</sup>  $\overline{ADSP}$  is gated by  $\overline{CS}$ , and  $\overline{CS}$  is used to block  $\overline{ADSP}$  when  $\overline{CS} = V_{IH}$ , as required in applications using Processor Address Pipelin-

<sup>4.</sup> All Addresses, Data In and Control signals are registered on the rising edge of CLK.

#### Write Enable Truth Table

| WEa | WEb | WEc | WEd | Byte Written                           | Notes |

|-----|-----|-----|-----|----------------------------------------|-------|

| Н   | Н   | Н   | Н   | Read All Bytes                         |       |

| L   | L   | L   | L   | Write All Bytes                        |       |

| L   | Н   | Н   | Н   | Write Byte A (D <sub>IN</sub> 0 - 8)   |       |

| Н   | L   | Н   | Н   | Write Byte B (D <sub>IN</sub> 9 - 17)  |       |

| Н   | Н   | L   | Н   | Write Byte C (D <sub>IN</sub> 18 - 26) |       |

| Н   | Н   | Н   | L   | Write Byte D (D <sub>IN</sub> 27 - 35) |       |

### **Absolute Maximum Ratings**

| Parameter                    | Symbol           | Rating                       | Units | Notes |

|------------------------------|------------------|------------------------------|-------|-------|

| Power Supply Voltage         | $V_{DD}$         | -0.5 to 4.6                  | V     | 1     |

| Input Voltage                | V <sub>IN</sub>  | -0.5 to 6.0                  | V     | 1     |

| Output Voltage               | V <sub>OUT</sub> | -0.5 to V <sub>DD</sub> +0.5 | V     | 1     |

| Operating Temperature        | T <sub>OPR</sub> | 0 to +70                     | °C    | 1     |

| Storage Temperature          | T <sub>STG</sub> | -55 to +125                  | °C    | 1     |

| Power Dissipation            | P <sub>D</sub>   | 2.0                          | W     | 1     |

| Short Circuit Output Current | I <sub>OUT</sub> | 50                           | mA    | 1     |

<sup>1.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## Recommended DC Operating Conditions (T<sub>A</sub>=0 to 70°C)

| Parameter          | Symbol           | Min.  | Тур. | Max.  | Units | Notes   |

|--------------------|------------------|-------|------|-------|-------|---------|

| Supply Voltage     | $V_{DD}$         | 3.135 | 3.3  | 3.465 | V     | 1, 4    |

| Input High Voltage | V <sub>IH</sub>  | 2.2   | _    | 5.5   | V     | 1, 2, 4 |

| Input Low Voltage  | V <sub>IL</sub>  | -0.3  | _    | 0.8   | V     | 1, 3, 4 |

| Output Current     | I <sub>OUT</sub> | _     | 5    | 8     | mA    | 4       |

- 1. All voltages referenced to GND. All  $V_{\text{DD}(Q)}$  and  $V_{\text{SS}(Q)}$  pins must be connected.

- 2.  $V_{IH}(Max)DC = 5.5 \text{ V}$ ,  $V_{IH}(Max)AC = 6.0 \text{ V}$  (pulse width  $\leq 4.0 \text{ns}$ ).

- 3.  $V_{IL}(Min)DC$  = 0.3 V,  $V_{IL}(Min)AC$ = -1.5 V (pulse width  $\leq$  4.0ns).

- 4. Input voltage levels are tested to the following DC conditions: 1 microsecond cycle and 200 ns set-up and hold times.

#### 32K X 36 BURST SRAM

### **Capacitance** ( $T_A$ =0 to +70°C, $V_{DD}$ =3.3V $\pm$ 5%, f=1MHz)

| Parameter                       | Symbol           | Test Condition        | Max | Units | Notes |

|---------------------------------|------------------|-----------------------|-----|-------|-------|

| Input Capacitance               | C <sub>IN</sub>  | V <sub>IN</sub> = 0V  | 5   | pF    |       |

| Data I/O Capacitance (DQ0-DQ35) | C <sub>OUT</sub> | V <sub>OUT</sub> = 0V | 5   | pF    |       |

# DC Electrical Characteristics (TA= 0 to +70°C, VDD=3.3V $\pm\,5\%)$

| Parameter                                                                                                                                                                                                                   | Symbol          | Min. | Max. | Units | Notes |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|-------|-------|

| Operating Current<br>Average Power Supply Operating Current $(\overline{OE} = V_{IH}, I_{OUT} = 0)$                                                                                                                         | IDD15           | _    | 275  | mA    | 2, 3  |

| Standby Current  Power Supply Standby Current $\overline{(CS2} = V_{IH} \text{ or } \overline{CS2} = V_{IL} \text{ or } \overline{CS} = V_{IH}$ All other inputs = $V_{IH}$ or $V_{IL}$ , $I_{OUT.} = 0$ , Clock @ 66 MHz)) | I <sub>SB</sub> | _    | 25   | mA    | 1, 3  |

| Input Leakage Current Input Leakage Current, any input (V <sub>IN</sub> = 0 &V <sub>DD</sub> )                                                                                                                              | I <sub>LI</sub> | _    | +1   | μΑ    | 4     |

| Output Leakage Current $(V_{OUT} = 0 \text{ &V}_{DD}, \overline{OE} = V_{IH})$                                                                                                                                              | I <sub>LO</sub> | _    | +1   | μΑ    |       |

| Output High Level<br>Output "H" Level Voltage (I <sub>OH</sub> =-8mA @ 2.4V)                                                                                                                                                | V <sub>OH</sub> | 2.4  | _    | V     |       |

| Output Low Level<br>Output "L" Level Voltage (I <sub>OL</sub> =+8mA @ 0.4V)                                                                                                                                                 | V <sub>OL</sub> | _    | 0.4  | V     |       |

<sup>1.</sup>  $I_{SB} = Stand-by Current$ .

### AC Test Conditions ( $T_A=0$ to +70°C, $V_{DD}=3.3V \pm 5\%$ )

| Parameter                               | Symbol          | Conditions | Units | Notes    |

|-----------------------------------------|-----------------|------------|-------|----------|

| Input Pulse High Level                  | V <sub>IH</sub> | 3.0        | V     |          |

| Input Pulse Low Level                   | V <sub>IL</sub> | 0.0        | V     |          |

| Input Rise Time                         | T <sub>R</sub>  | 2.0        | ns    |          |

| Input Fall Time                         | T <sub>F</sub>  | 2.0        | ns    |          |

| Input and Output Timing Reference Level |                 | 1.5        | V     |          |

| Output Load Conditions                  |                 |            |       | 1        |

| Output Load Conditions                  |                 |            |       | <u> </u> |

<sup>1.</sup> See AC Test Loading figure 1 on page 8.

<sup>2.</sup> I<sub>DD</sub> = Selected Current.

<sup>3.</sup>  $I_{OUT} = Chip Output Current$ .

<sup>4.</sup> The input leakage current for 5.5V inputs is  $200~\mu\text{A}$  for Clk, Chip Selects, and Output Enable. Other inputs have 100  $\mu\text{A}$  of leakage current at 5.5V.

### **AC Characteristics** ( $T_A$ =0 to +70°C, $V_{DD}$ =3.3V $\pm$ 5%, Units in nsec)

| Parameter                            | Cumbal             | -    | 8    | -    | 9    | -10  |      | -11  |      | Notes   |

|--------------------------------------|--------------------|------|------|------|------|------|------|------|------|---------|

| Parameter                            | Symbol             | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Notes   |

| Cycle Time                           | t <sub>CYCLE</sub> | 15.0 | _    | 15.0 | _    | 15.0 | _    | 15.0 | _    |         |

| Clock Pulse High                     | t <sub>CH</sub>    | 3.0  | _    | 3.0  | _    | 3.0  | _    | 3.0  | _    |         |

| Clock Pulse Low                      | t <sub>CL</sub>    | 3.0  | _    | 3.0  | _    | 3.0  | _    | 3.0  | _    |         |

| Clock to Output Valid                | t <sub>CQ</sub>    | _    | 8.0  | _    | 9.0  | _    | 10.0 | _    | 11.0 | 3       |

| Address Status Controller Setup Time | t <sub>ADSCS</sub> | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Address Status Controller Hold Time  | t <sub>ADSCH</sub> | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Address Status Processor Setup Time  | t <sub>ADSPS</sub> | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Address Status Processor Hold Time   | t <sub>ADSPH</sub> | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Advance Setup Time                   | t <sub>ADVS</sub>  | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Advance Hold Time                    | t <sub>ADVH</sub>  | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Address Setup Time                   | t <sub>AS</sub>    | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Address Hold Time                    | t <sub>AH</sub>    | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Chip Selects Setup Time              | t <sub>CSS</sub>   | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Chip Selects Hold Time               | t <sub>CSH</sub>   | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Write Enables Setup Time             | t <sub>WES</sub>   | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Write Enables Hold Time              | t <sub>WEH</sub>   | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Data In Setup Time                   | t <sub>DS</sub>    | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    |         |

| Data In Hold Time                    | t <sub>DH</sub>    | 0.5  | _    | 0.5  | _    | 0.5  | _    | 0.5  | _    |         |

| Data Out Hold Time                   | t <sub>CQX</sub>   | 3.0  | _    | 3.0  | _    | 3.0  | _    | 3.0  | _    | 3       |

| Clock High to Output High-Z          | t <sub>CHZ</sub>   | _    | 5.0  | _    | 5.0  | _    | 5.5  | _    | 5.5  | 1, 2, 4 |

| Clock High to Output Active          | t <sub>CLZ</sub>   | 2.5  | _    | 2.5  | _    | 2.5  | _    | 2.5  | _    | 1, 2, 4 |

| Output Enable to High-Z              | t <sub>OHZ</sub>   | 2.0  | 5.0  | 2.0  | 5.5  | 2.0  | 6.0  | 2.0  | 6.5  | 1, 4    |

| Output Enable to Low-Z               | t <sub>OLZ</sub>   | 0.25 | _    | 0.25 | _    | 0.25 | _    | 0.25 | _    | 1, 4    |

| Output Enable to Output Valid        | t <sub>OQ</sub>    | _    | 4.0  | _    | 5.0  | _    | 5.0  | _    | 6.0  | 3       |

<sup>1.</sup> Transitions are measured  $\pm$  200 mV from steady state voltage.

<sup>2.</sup> At any given voltage and temperature, T<sub>CHZ</sub> (max) is always less than T<sub>CLZ</sub> (min) for a given device and from device to device. For any read cycle preceded by a write or deselect cycle, the data bus will transition glitch-free from High-Z to new RAM data.

<sup>3.</sup> See AC Test Loading figure 1 on page 8.

<sup>4.</sup> See AC Test Loading figure 2 on page 8.

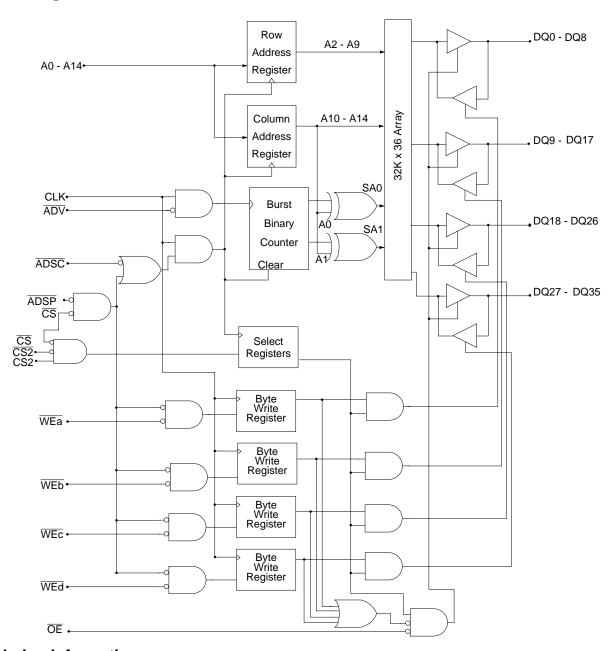

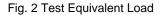

### **AC Test Loading**

Fig. 1 Test Equivalent Load

The derating curve above is for a purely capacitive load on the output driver. For example, a part specified at 8 ns access time will behave as though it has an 8.5 ns access time if a 30 pF load with no DC component was attached to the output driver. The access times guaranteed in the datasheets are based on a 50 ohm terminated test load. For unterminated loads the derating curve should be used. This curve is based on nominal process conditions with worst case parameters  $V_{DD} = 3.14 \text{ V}$ ,  $V_{A} = 70^{\circ} \text{ C}$ .

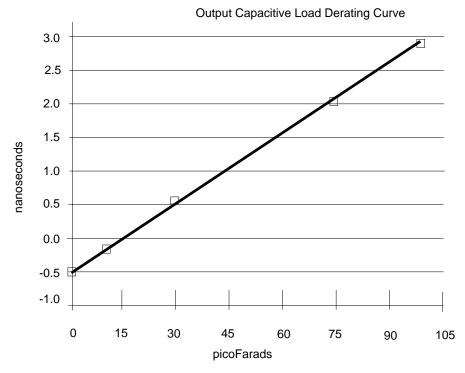

# **Timing Diagram (Burst Read)**

- 1. Q1(A) and Q2(A) refer to data read from address A1 and A2.

- 2. Q2(B), Q2(C) and Q2(D) refer to read from subsequent internal burst counter addresses.

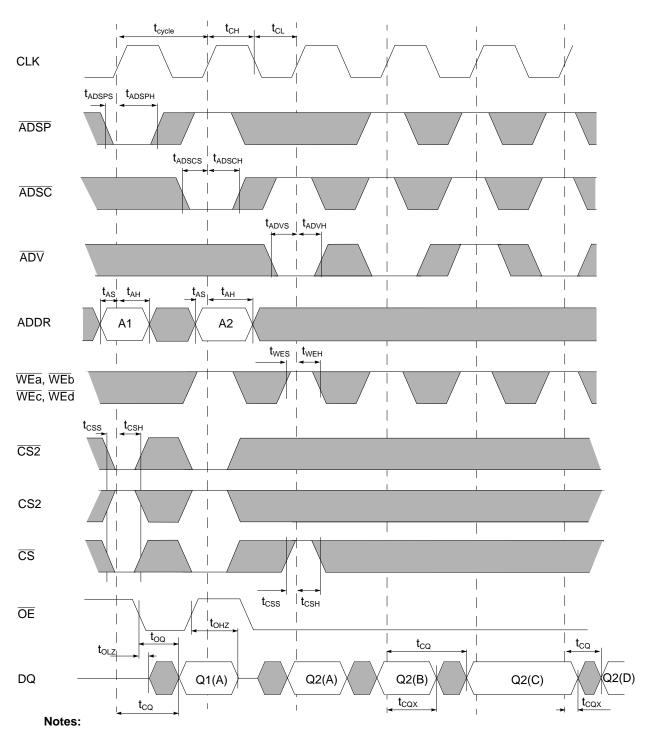

# **Timing Diagram (Burst Write)**

#### Notes:

- 1. D1(A) and D2(A) refer to data written to address A1 and A2.

- 2.  $\overline{D2(B)}$  refers to data written to a subsequent internal burst counter address. 3.  $\overline{WEa}$ ,  $\overline{WEb}$ ,  $\overline{WEc}$  and  $\overline{WEd}$  are don't cares when ADSP is sampled LOW.

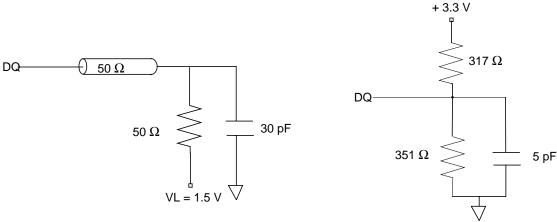

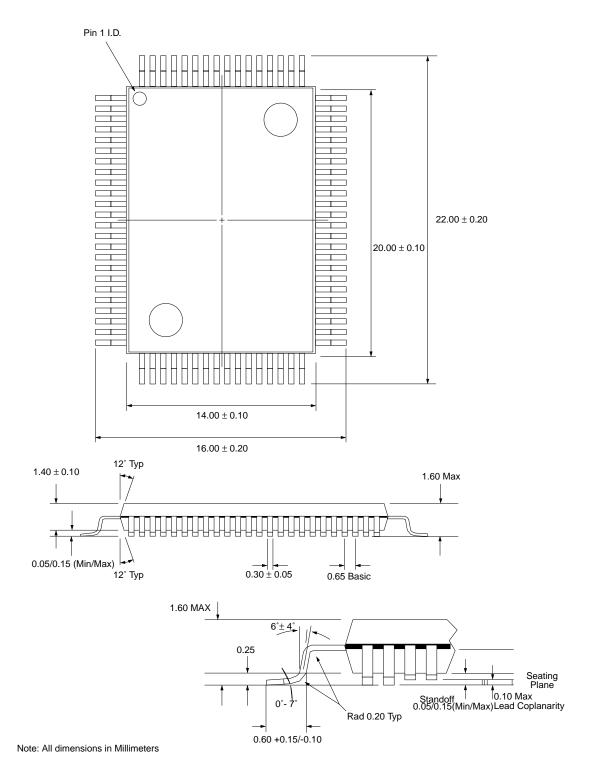

# 100 Pin TQFP Package Diagram

### 32K X 36 BURST SRAM

# **Revision Log**

| Rev  | Contents of Modification                                                                               |

|------|--------------------------------------------------------------------------------------------------------|

| 5/94 | Initial Release of the 32K x 36 (8/9/11) TQFP BURST MODE Application Spec.                             |

| 3/95 | Updated -8, -9, -11; Added -10 Specifications.                                                         |

| 7/95 | Removed Preliminary classification.                                                                    |

| 9/97 | Updated Part numbers to add die revision character. This new datasheet DOES NOT reflect a die revision |

© International Business Machines Corp.1997

Printed in the United States of America All rights reserved

IBM and the IBM logo are registered trademarks of the IBM Corporation.

This document may contain preliminary information and is subject to change by IBM without notice. IBM assumes no responsibility or liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The products described in this document are not intended for use in implantation or other direct life support applications where malfunction may result in direct physical harm or injury to persons. NO WARRANTIES OF ANY KIND, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

For more information contact your IBM Microelectronics sales representative or visit us on World Wide Web at http://www.chips.ibm.com

IBM Microelectronics manufacturing is ISO 9000 compliant.