# Intel® Gigabit Ethernet

## Over Category 5 Twisted-pair Networks

### Description

Gigabit Ethernet, initially supported on fiber links only, is now available for twisted-pair copper cable. Referred to as 1000BASE-T, Gigabit Ethernet over twisted-pair is defined by the IEEE 802.3ab standard, which is an extension of the 802.3 specification that defines 10Mbps and 100Mbps Ethernet protocols. Like its Fast Ethernet predecessor, Gigabit Ethernet relies on the technical foundations established for 10BASE-T. The new 1000BASE-T physical layer (PHY) standard provides for gigabit speed, while retaining the benefits of Ethernet over twisted-pair cabling. 1000BASE-T signaling requires four pairs of Category 5 (Cat5) unshielded twisted-pair UTP cable. Cat5 cabling is easy to reconfigure and widely installed for 100BASE-TX networks today. The success of 10/100BASE-TX dualspeed adapter cards indicates the potential for 10/100/1000Mbps triple-speed adapter cards. Triple-speed cards will be particularly advantageous in servers and other applications that must connect regardless of the network configuration.

### Function

Gigabit Ethernet expands network bandwidth to 1000Mbps, providing a fat pipe for backbone applications, high-speed workstation, and server links. The development of Fast Ethernet had been driven by market dynamics such as faster processors, more complex applications, growth of client-server architectures, and general increases in network traffic. These same forces, further fueled by e-commerce and the global Internet economy, continue to drive demand for ever-higher network bandwidth. Many network backbones already require bandwidth in excess of 100Mbps; some applications do as well.

### Key Applications

Applications and environments that will benefit from 1000BASE-T include:

- Internet Service Providers (ISPs)

- Building-level backbone, server and gateway connectivity

- Multimedia, distributed processing, imaging, medical, and CAD/CAM applications

- Aggregation of 100Mbps switches

- Upgrade for large installed base of 10/100Mbps Ethernet

- Future-proof networks—from 10/100Mbps today to 1000Mbps in the future

# Network Interface Card intel LXT1000 Media Access Controller

### **Technology Overview**

To understand 1000BASE-T, it is helpful to compare it with 10BASE-T and 100BASE-TX. There are five key differences that set 1000BASE-T apart from its predecessors.

Line code and data rate: A 100BASE-TX system uses MLT-3 coded 3-level signaling, at a symbol rate of 125MHz, over a single wire pair. This signal produces a 100Mbps data path using a 4B/5B encoding scheme. The additional bandwidth is used to provide control codes and robustness. A 1000BASE-T system uses 5-level (quinary) signals on each of the four wire pairs at a nominal clock-rate of 125MHz. This line coding is also referred to as 4D-PAM5 (4D for four pair, PAM5 for 5-level Pulse Amplitude Modulation). Each wire pair carries data in both directions at the same time. Each quinary symbol represents 2.25+ bits of data; together the four pairs carry 9 bits of information—8 bits of data (8x125M=1G) and 1 bit of forward error correction. The spectral power density of the Gigabit signal is nearly identical to that of 100BASE-TX, making the radiated emissions from Gigabit Ethernet no worse than those of Fast Ethernet.

### Media Access Controller Interface (MAC I/F):

The Media Independent Interface (MII) was originally defined for 10/100BASE-TX systems, and has been expanded to handle Gigabit Ethernet's tenfold increase in bandwidth. The extended 802.3ab specification defines the Gigabit Media Independent Interface (GMII), which is similar to the MII in 100BASE-X applications but uses eight (rather than four) data lines in each direction.

**Full/half duplex:** 1000BASE-T provides both full-duplex and half-duplex (CSMA-CD) modes of operation. Full duplex is the most efficient, and will be the predominant mode for Gigabit Ethernet applications. Most Gigabit Ethernet systems and a significant portion of Fast Ethernet

int<sub>e</sub>

Internet Exchange

Architecture

www.intel.com/

design/network

(continued)

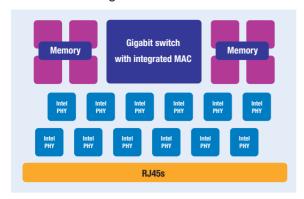

### Gigabit Switch Card

### Technology Overview (continued)

systems are full-duplex, switched configurations using point-to-point links. However, the 802.3ab standard also provides certain modifications to allow use of half-duplex operation at the higher speed:

- An increase in the minimum packet size from 64 bytes to 512 bytes

- Concatenation of packets to a maximum length of 9600 bytes

Both can be accomplished at the MAC/PHY interface using the Transmit Enable (TX\_EN) and Transmit Error (TX\_ER) signals without modifications to upper-layer drivers. This signaling causes Packet Extension: the PHY pads the end of short packets and space between concatenated packets with symbols to meet the minimum 512-byte size.

**Cabling:** The cable type (Cat5 UTP) and connectors (RJ45) have not changed, so no cable upgrades are required. Cat5

cable includes four twisted-wire pairs. Only two pairs are used in 10/100BASE-TX systems; the other two pairs are typically unused. All four pairs are required for 1000BASE-T links.

Master/slave timing: The Gigabit Ethernet clocking scheme is different from the scheme used in 10/100Mbps systems. Link partners in 100BASE-TX systems are clocked independently, whereas link partners in a 1000BASE-T system use a master-slave clocking relationship to achieve synchronous transmission and provide noise cancellation. The master-slave relationship establishes a 1000BASE-T connection as a closed-loop system across the link segment, similar to ISDN, HDSL and other applications.

The master PHY uses an external master clock, encoded into the data stream, to determine the timing of transmitter and receiver operations. The slave PHY recovers the clock from the received signal and uses it as a transmit clock; i.e., it performs loop timing. The master-slave relationship is established during auto-negotiation; typically, the PHY at the switch or repeater becomes the master and the PHY at the DTE becomes the slave.

### **Evolution of Ethernet**

|                   | 10BASE-T         | 100BASE-TX     | 1000BASE-T         |

|-------------------|------------------|----------------|--------------------|

| IEEE Standard     | 802.3            | 802.3u         | 802.3ab            |

| MAC-PHY Interface | 7-pin (de facto) | MII (IEEE)     | GMII (IEEE)        |

| Width x Speed     | 10MHz x 1 bit    | 25MHz x 4 bits | 125MHz x 8 bits    |

| Cable Used        | CAT3             | CAT5           | CAT5               |

| Number of Pairs   | 2 pair           | 2 pair         | 4 pair             |

| Baud Rate/Signal  | 10Mbps/5V        | 125Mbps/1V     | $125Mbps/\Omega V$ |

| Encoding          | Manchester       | MLT3           | 4D-PAM5            |

| Carrier           | Noncontinuous    | Continuous     | Continuous         |

| Duplex            | Half             | Full or Half   | Full Preferred     |

| Auto-negotiation  | Nonexistent      | Optional       | Required           |

| Management        | None             | MDIO/MDC       | MDIO/MDC           |

### Intel® Internet Exchange Architecture

Intel® Internet Exchange Architecture (IXA) is an end-to-end family of high-performance, flexible and scalable hardware and software development building blocks designed to meet the growing performance requirements of today's networks. Based on programmable

silicon and software building blocks, Intel® IXA solutions enable faster development, more cost-effective deployment, and future upgradability of network and communications systems. Additional information can be found at www.intel.com/IXA.

### Intel Access

| Developer's Site                               | developer.intel.com                                                                                                   |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Intel Internet Exchange Architecture Home Page | www.intel.com/IXA                                                                                                     |  |

| Networking Components Home Page                | developer.intel.com/design/network                                                                                    |  |

| Other Intel Support:                           | developer.intel.com/design/litcentr                                                                                   |  |

| Intel Literature Center                        | (800) 548-4725 7 a.m. to 7 p.m. CST (U.S. and Canada) International locations please contact your local sales office. |  |

| General Information Hotline                    | (800) 628-8686 or (916) 356-3104 5 a.m. to 5 p.m. PST                                                                 |  |

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel. \*Other brands and names are the property of their respective owners.

For more information, visit the Intel Web site at: **developer.intel.com**

UNITED STATES AND CANADA Intel Corporation Robert Noyce Bldg. 2200 Mission College Blvd. P.O. Box 58119 Santa Clara, CA 95052-8119 USA EUROPE Intel Corporation (UK) Ltd. Pipers Way Swindon Wiltshire SN3 1RJ UK ASIA-PACIFIC Intel Semiconductor Ltd. 32/F Two Pacific Place 88 Queensway, Central Hong Kong, SAR JAPAN Intel Kabushiki Kaisha P.O. Box 115 Tsukuba-gakuen 5-6 Tokodai, Tsukuba-shi Ibaraki-ken 305 SOUTH AMERICA Intel Semicondutores do Brazil Rue Florida, 1703-2 and CJ22 CEP 04565-001 Sao Paulo-SP Brazil