# IXF3461Slot Switching Dual-Channel T1/E1/J1 LIU and Framer

www.intel.com/IXA

### **Product Overview**

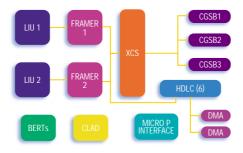

The IXF3461 is a flexible, dual-channel T1/E1/J1 Line Interface Unit (LIU) and framer. It is the only combination LIU and framer to feature a fully integrated cross connect switch (XCS) designed for use in 1.544Mbps applications (T1 or J1), or in 2.048Mbps applications (E1). The XCS can interchange both data and signaling in any time slot on any port (system or line) with any other time slot on any other port. The highly integrated IXF3461 solution is ideal for the convergence of voice and data communications. And it provides the performance, robustness, and flexibility to help speed deployment and increase the integrity and availability of the network.

The Simplified Slot Switching (SSS) features of the IXF3461 address developers' complex timing issues and faster-design requirements. The product handles critical cross connect timing internally, so that slot switching with the IXF3461 can help reduce design complexity, shorten testing time, and enable quick delivery of reliable systems to market.

# Flexibility and Control

In addition to a flexible and programmable system interface, the slot switching capability of the IXF3461 provides direct control of time slot assignment on the system bus. The IXF3461 works from a single reference clock input and generates all required T1/E1 clocks internally. It is available in a 160-pin MQFP or PBGA package with 3.3V CMOS technology, enabling you to use T1/E1/J1 equipment to efficiently build low-cost and low-power systems.

In addition, you can combine the XCS with a PCM highway system interface (CGSB) to implement a full non-blocking, 128 x 128-channel, cross connect function between two independent IXF3461 LIUs.

# Carrier Access Support

For carriers, network availability has growing importance. The IXF3461 helps meet this need by incorporating innovations such as a flexible on-chip BERT and programmable pattern generator/detection testers, diagnostic and configuration monitoring features, and elastic buffer pointer position indicators for calculating delays. In addition to standard network line, payload, and time slot loopbacks, the IXF3461 provides corresponding loopbacks to the system side. These loopbacks, when used with the embedded BERT and programmable pattern generator/ detection testers, provide both in-service and out-of-service data path fault detection and isolation capabilities. Integrated alarm signaling also helps reduce system processor loading.

### Robust, Rapid Deployment

The innovative IXF3461 is a fully switchable LIU and framer, allowing you to design a single board to support T1, E1, and J1 applications with no receive-loss compromise or external component changes. You can convert from T1 to E1 with a single IXF3461. An integrated clock adapter simplifies design and keeps component count to a minimum. In addition, each LIU port can be independently controlled, enabling you to convert from one standard interface to another on a single chip. Six HDLC controllers and its time slot switching capabilities make the IXF3461 ideal for GR303/V5.2 applications with voice and data integration.

Intel also offers an IXF3461 Evaluation Kit to help simplify otherwise complex system design. The kit includes a four-port reference design complete-protection circuitry, a comprehensive hardware API, and a GUI. Pulse Template Matching software facilitates your design efforts and ensures design conformance to stringent specifications. The Evaluation Kit also includes all design files to help speed product development and introduction to market.

| reatures                                                                                                                  | benefits                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| ■ Local switching of DS0s/DS1s                                                                                            | <ul> <li>Off-loads system resources</li> </ul>                                                               |

| ■ Counters and extensive bit error rate testing                                                                           | ■ Provides convenient performance monitoring                                                                 |

| ■ T1 or E1 switchability                                                                                                  | ■ Eliminates the need for external component changes                                                         |

| ■ Intel® technology and performance                                                                                       | ■ Facilitates robust field operation                                                                         |

| ■ Flexible backplane                                                                                                      | <ul> <li>Supports non-multiplexed and multiplexed bit and byte replication operations</li> </ul>             |

| ■ Includes GUI, Application Program Interface (API), and device drivers                                                   | ■ Accelerates system development                                                                             |

| ■ Integrated DMA controller on HDLC                                                                                       | ■ Promotes fast data transfer                                                                                |

| ■ Pulse Template Matching software                                                                                        | <ul> <li>Accelerates transceiver design and circuit deployment,<br/>shortening time-to-revenue</li> </ul>    |

| ■ Three CGSB highway system interfaces                                                                                    | <ul> <li>Offers compatibility with MVIP/ST bus, HMVIP,<br/>IOM/GCI, and CHI bus</li> </ul>                   |

| Six independently configurable HDLC controllers                                                                           | ■ Supports ISDN PRI, GR-303, V5.1, and V5.2 applications                                                     |

| ■ Extensive flexibility in interrupt operation                                                                            | <ul> <li>Optimizes software control</li> <li>Minimizes latency</li> <li>Maximizes programmability</li> </ul> |

| ■ Support for either Intel- or Motorola-compatible microprocessor bus interfaces with either an 8-bit or 16-bit data path | ■ Provides flexible design options                                                                           |

Renefits

### Acronyms

Features

BERT: Bit Error Rate Test

CGSB: Customizable Generic Serial Bus

DMA: Direct Memory Access

DSLAM: Digital Subscriber Line Access Multiplexer

FDL: Facility Data Link

FIFO: First In, First Out data buffer GUI: Graphical User Interface

HDLC: High-level Data Link Control (protocol)

JA: Jitter Attenuator

LIU: Line Interface Unit (transceiver)

PCM: Pulse Code Modulation

RAS: Remote Access Server

SSS: Simplified Slot Switching

XCS: Cross Connect Switch

### Key Applications

- Integrated access devices (IAD), LAN/WAN bridge/router

- FRAD, CSU/DSU, and base stations

- DLC, HDSL T1 extensions (and pair gain systems)

- DSLAM with local switching

- PBXs and RAS

- Microwave radio systems

## Support Products

- The IXF3461 Evaluation Kit with four-port reference design, design files, and User Guide

- GUI, programmer interface, and device drivers

- IXF3461 Datasheet

- Long-haul Frequently Asked Questions (FAQs)

- Application Notes 129, 130, and 142

# A New Approach to Development: Intel® Internet Exchange™ Architecture

Intel is addressing today's market challenges with a range of new solutions in a cohesive set of standard building blocks for network systems—the Intel® Internet Exchange $^{TM}$  (IX) architecture.

The unique silicon and software components that comprise the Intel® IX architecture facilitate your development of relevant solution platforms—with scalable performance, flexible handling of multiple protocols, and world-class development tools. Its growing suite of silicon and software building blocks were designed to offer you:

- Cost effectiveness

- Development efficiencies

- Seamless interoperability

The Intel IX architecture is helping to provide a comprehensive solution now *and* for the future of your business.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Intel and Intel logo are registered and Internet Exchange is a trademark of Intel Corporation. "All other brands and names are the property of their respective owners.

General Information Hotline +1 800.628.8686 or +1 916.356.3104 5 a.m. to 5 p.m. PST For more information, visit the Intel Web site at: www.intel.com/IXA

Copyright © 2000 Intel Corporation Order Number: PB-1005.1 Printed in USA/0600/TK/ASI/CR