# 1Mb High Performance SRAM

### **Highlights**

#### **Access Time**

2.25 ns (Pipeline), 5.7ns (Flow Thru), 6.0 ns (Register Latch)

#### **Cycle Time**

4 ns (Pipeline ),4 ns (Flow Thru), 6 ns (Register Latch)

#### **Organizations**

64K x 18, 32K x 36

#### **Power Dissipation**

HSTL x36

Active Power 23 W (250Mhz) Standby Power 8.5 mW

# HSTL/LVTTL I/O compatible HSTL/PECL clock compatible LVTTL JTAG I/O

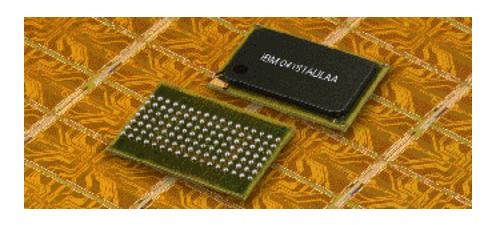

#### **Package**

Industry standard Ball Grid Array 7 x 17, MO-163.

# 2.5VI/O capability

3.3V power supply

Registered addresses, write enables, synch select, data ins

#### Registered outputs

Pipeline operations Register latch operations

# Programmable HSTL output impedance

Asynchronous output enable Flow thru output hold time

#### Self-timed late write

control

Byte write capability and global write enable

Asynchronous sleep mode

Boundary scan using limited set of JTAG 1149.1 functions

## **Description**

IBM introduces a High Performance 1 Mb Synchronous SRAM for workstations, workstation servers, and telecommunication applications operating at frequencies up to 250 MHz. These versatile CMOS SRAMs offer wide I/O configurations and various I/O voltage interface levels operating with a single 33 volt power supply. They support fully pipelined, flow thru, and register latch operations. The self-timed late write is featured in all SRAM devices.

Pipelined operation is accomplished by placing registers at the inputs and outputs of the devices. During a read or write operation, a latency of one cycle between the addresses and the data is expected. Pipelining is supported with a single clock operation.

Flow thru operation is accomplished by gating the output registers with the output clock. This dual clock operation provides control of the data out window. An output clock can be used to control data output hold time. This mode is available with dual clock operation.

Register latch operation uses the falling edge of the output clock to control the output register.

Self-timed late write simplifies the write operation significantly. The SRAM timings do not require an extra cycle when switching from a read to a write operation.

| Org. |

|------|

|      |

| x18  |

| x36  |

|      |

© International Business Machines Corp. 1997

IBM Microelectronics Division 1580 Route 52 Hopewell Junction, NY 12533-6531

Printed in the United States of America, January 1997

All rights reserved

The IBM logo is a registered trademarks of the IBM Corporation.

This document may contain preliminary information and is subject to change by IBM without notice. IBM assumes no responsibility or liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The products described in this document are not intended for use in implantation or other direct life support applications where malfunction may result in direct physical harm or injury to persons. NO WARRANTIES OF ANY KIND, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRAN-TIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

For datasheets and more information contact your IBM Microelectronics Sales Representative.

Or visit us on the World Wide Web: http://www.chips.ibm.com/products/memory