# Integrated Silicon Solution, Inc.

# TARGET SPECIFICATION

# **TRAILBLAZER**

# IS82C600 — Virtual Dual-Port SRAM

## **GENERAL DESCRIPTION**

The TrailBlazer Virtual Dual Port (VDP) SRAM simplifies DSP-based system design and layout, providing no-wait-state performance up to 120 MHz, along with the convenience of a dual-ported interface. And in many cases, TrailBlazer allows existing system designs to be easily upgraded, enabling the reuse of available ASICs and logic designs.

A key benefit of the TrailBlazer device is its ability to interface easily to high-performance DSPs taking advantage of minimum impedance, point-to-point interconnect between the DSP and SRAM. Together with access times as fast as 7 ns, this allows the DSP to operate at maximum frequency with no-wait-states up to 120 MHz. Also, it eases PCB timing and layout related considerations and simplifies layout, often allowing a reduction in the number of PC board layers.

#### **FEATURES**

- Virtual dual-port (VDP) SRAM

- Seamless interface to Texas Instruments' '5x and '54x high-speed DSPs

- Zero wait-state performance up to 120 MHz on the primary DSP port

- Point-to-point interface between the SRAM and the high-speed DSP

- Integrates the single ported SRAM with a dual ported interface

- -7 ns access time to the SRAM

- TrailBlazer can be used as a stand alone highspeed SRAM

- Integrates the DSP port to DSP port bridge function

- Broadcasts all DSP cycles from primary DSP port to the secondary DSP port

- Programmability to only broadcast non-SRAM cycles to the secondary DSP port

- Programmability to "divide" the memory into six segments, corresponding to the six regions of TI DSPs

- The upper/lower halves of Data Space (DS), the upper/lower halves of Program Space (PS) and the upper/lower halves of I/O Space (IS).

- Programmability to insert wait states to the memory space (TI DSPs can only program wait states for all of I/O Space)

- Supports existing, slower DSP peripheral control devices on the secondary DSP port

- "No glue logic" interface for local peripherals on the secondary DSP poprt

- 12 chip selects, six on the primary DSP port and six on the secondary DSP port

- Allows the DSP to access the devices on the secondary port

- Supports bootable ROM on the secondary or primary port

- Allows the Shadowing of the ROM on the secondary port into the on-board SRAM

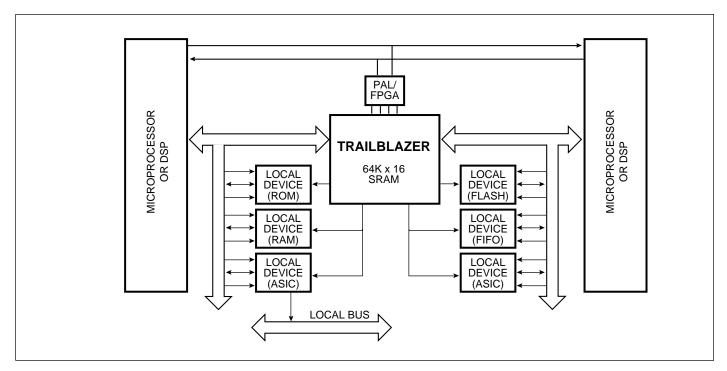

- Supports dual DSP designs

- Provides high-speed SRAM access on both DSP ports

- Programmable to be local or global memory of the DSPs

- Programmable "software locked" operations

- Programmable Master/Slave configuration for the dual-ported SRAM access

- Allows local port concurrency for each DSP

- XCVR pin allows device to be a transceiver for the DMA transfers between two DSPs

- Allows dynamic reallocation of memory space for transparent block moves

- Large blocks of data can be "transparently" moved from data space to program space and back by reprogramming mode bits

This document is a TARGET SPECIFICATION only. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1997, Integrated Silicon Solution, Inc.

2231 Lawson Lane • Santa Clara, CA 95054-3311 • 1-800-379-4774 • Fax: (408) 588-0806 e-mail: sales@issiusa.com • www.issiusa.com

#### **Product Overview**

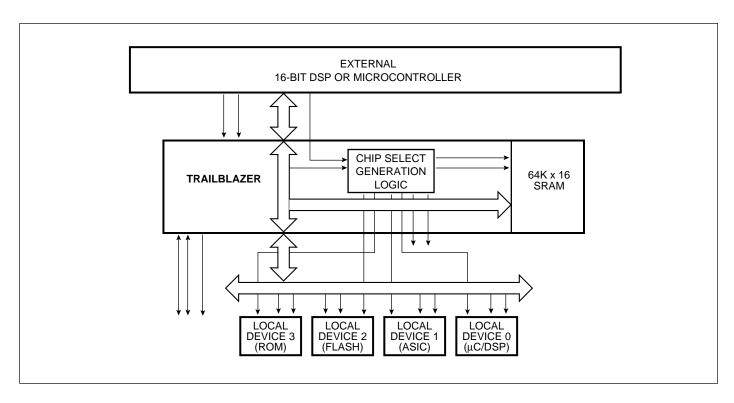

TrailBlazer, Virtual Dual-Ported SRAM, integrates the high-speed dual ported SRAM with a DSP port to DSP port bridge function to the high-speed DSP designs. This provides 7 ns access times to the DSP on the primary port that enables low cost implementation of the 120 MHz DSP system.

TrailBlazer combines a high-performance, single ported memory array with two-ported interface logic to enable maximum performance and flexibility while keeping costs at a minimum. In order to simplify system development, TrailBlazer duplicates the DSP bus signals on its second port to permit the use of existing system solutions and ASICs with a new generation of higher frequency DSPs. On its primary port, TrailBlazer provides a high-speed SRAM interface to the DSP and then broadcasts DSP cycles to its secondary port allowing the DSP to access peripherals. Since the peripherals are accessed using the same signals, in may cases existing ASICs can be reused.

TrailBlazer provides an optimized, seamless interface to TI '5x and '54x high speed DSPs along with a "no glue logic" interface for local peripherals on the second port; up to 12 chip select outputs are provided. If desired, TrailBlazer can turn off broadcast of DSP cycles to its second port which can save considerable system power at high frequency.

TrailBlazer can also be used as local or global memory for a two DSP or microcontroller system; chip select logic on each port allows the same data to be accessed at different locations in memory if desired.

TrailBlazer System Block Diagram with High-Speed DSP on the Primary Port and the Slower Existing DSP System Components on the Secondary Port

TrailBlazer ISSI\*

TrailBlazer System Block Diagram showing a Dual DSP System

## **PIN CONFIGURATION: 119-pin PBGA**

|   | 1       | 2       | 3      | 4    | 5                  | 6      | 7                  |

|---|---------|---------|--------|------|--------------------|--------|--------------------|

| Α | CSMEMp3 | CSMEMp5 | Ap4    | Ap5  | Ap11               | XCVR   | ĪSp                |

| В | CSMEMp2 | CSMEMp4 | Ap3    | Ap6  | Ap12               | PSp    | DSp                |

| С | CSMEMp0 | CSMEMp1 | Ap2    | Ap7  | Ap13               | Dp0    | Dp1                |

| D | Ds1     | Ds0     | Ap1    | Ap8  | Ap14               | Dp2    | Dp3                |

| Е | Ds3     | Ds2     | Ap0    | Ap9  | Ap15               | Dp4    | Dp5                |

| F | Ds4     | GND     | GNDQ   | Ap10 | GNDQ               | Vcc    | Dp6                |

| G | Ds7     | Ds6     | Ds5    | Dp7  | HOLDAp             | CSINTp | RWp                |

| Н | ОЕМЕМр  | GNDQ    | WEMEMp | Vccq | RDp                | GNDa   | <del>IOSTRBp</del> |

| J | Ds8     | OEMEMs  | Vccq   | Vccq | WEs                | WEp    | MSTRBp             |

| K | Ds9     | GNDQ    | WEMEMs | Vccq | <del>IOSTRBs</del> | GNDQ   | MSTRBs             |

| L | Ds10    | Ds11    | As1    | As7  | CSINTs             | RWs    | RDs                |

| М | Ds12    | GND     | GNDQ   | As8  | GNDQ               | GND    | HOLDAs             |

| N | Ds13    | Ds14    | As2    | As9  | Dp10               | Dp9    | Dp8                |

| Р | Ds15    | CSMEMs0 | As3    | As10 | Dp13               | Dp12   | Dp11               |

| R | CSMEMs1 | CSMEMs2 | As4    | As11 | PRGM               | DSs    | Dp14               |

| T | CSMEMs3 | CSMEMs5 | As5    | As12 | As15               | ĪSs    | Dp15               |

| U | CSMEMs4 | As0     | As6    | As13 | As14               | PSs    | NC                 |

**TrailBlazer**

### **DETAILED PIN DESCRIPTION**

## **Table 1. Primary Side Pins**

| Pin Name        | Pin Count | Pin Type | Pin Description                                                                 |

|-----------------|-----------|----------|---------------------------------------------------------------------------------|

| Ap[15:0]        | 16        | I/O      | ADDRESS: Address pins that connect to the primary side DSP or microcontroller.  |

| Dp[15:0]        | 16        | I/O      | <b>DATA:</b> Data pins that connect to the primary side DSP or microcontroller. |

| RDp             | 1         | I/O      | READ STROBE: Enables a read on the primary side.                                |

| WEp             | 1         | I/O      | WRITE STROBE: Enables a write on the primary side.                              |

| <b>IOSTRB</b> p | 1         | I/O      | I/O STROBE: Enables I/O access on the primary side.                             |

| MSTRBp          | 1         | I/O      | MEMORY (DATA) STROBE: Memory access on the primary side.                        |

| PSp             | 1         | I/O      | PROGRAM SPACE SELECT: Selects Program Space on the primary side.                |

| DSp             | 1         | I/O      | DATA SPACE SELECT: Selects Data Space on the primary side.                      |

| <del>ĪSp</del>  | 1         | I/O      | I/O SPACE SELECT: Selects I/O Space on the primary side.                        |

| RWp             | 1         | I/O      | READ/WRITE: Indicates a Read or Write Cycle on the primary side.                |

| HOLDAp          | 1         | I        | HOLD ACKNOWLEDGE: Indicates primary side is relinguishing control of            |

|                 |           |          | TrailBlazer.                                                                    |

| CSINTp          | 1         | I        | INTERNAL SRAM CHIP SELECT: When asserted, it overrides any                      |

|                 |           |          | MODE configuration.                                                             |

| CSMEMp[5:0      | 0] 6      | 0        | EXTERNAL MEMORY CHIP SELECTS: Based on the 6-32K memory regions.                |

| WEMEMp          | 1         | 0        | EXTERNAL MEMORY WRITE ENABLE: Based on the 6-32K memory regions.                |

| <u>OEMEMp</u>   | 1         | 0        | <b>EXTERNAL MEMORY OUTPUT ENABLE:</b> Based on the 6-32K memory regions.        |

### **Table 2. Secondary Side Pins**

| Pin Name   | Pin Count Pin Type |     | Pin Description                                                                         |  |

|------------|--------------------|-----|-----------------------------------------------------------------------------------------|--|

| As[15:0]   | 16                 | I/O | <b>ADDRESS:</b> Address pins that connect to the secondary side DSP or microcontroller. |  |

| Ds[15:0]   | 16                 | I/O | <b>DATA:</b> Data pins that connect to the secondary side DSP or microcontroller.       |  |

| RDs        | 1                  | I/O | READ STROBE: Enables a read on the secondary side.                                      |  |

| WEs        | 1                  | I/O | WRITE STROBE: Enables a write on the secondary side.                                    |  |

| IOSTRBs    | 1                  | I/O | I/O STROBE: Enables I/O access on the secondary side.                                   |  |

| MSTRBs     | 1                  | I/O | MEMORY (DATA) STROBE: Memory access on the secondary side.                              |  |

| PSs        | 1                  | I/O | PROGRAM SPACE SELECT: Selects Program Space on the secondary side.                      |  |

| DSs        | 1                  | I/O | DATA SPACE SELECT: Selects Data Space on the secondary side.                            |  |

| ĪSs        | 1                  | I/O | I/O SPACE SELECT: Selects I/O Space on the secondary side.                              |  |

| RWs        | 1                  | I/O | <b>READ/WRITE:</b> Indicates a Read or Write Cycle on the secondary side.               |  |

| HOLDAs     | 1                  | I   | HOLD ACKNOWLEDGE: Indicates secondary side is relinguishing control of                  |  |

|            |                    |     | TrailBlazer.                                                                            |  |

| CSINTs     | 1                  | 1   | INTERNAL SRAM CHIP SELECT: When asserted, it overrides any                              |  |

|            |                    |     | MODE configuration.                                                                     |  |

| CSMEMs[5:0 | 0] 6               | 0   | <b>EXTERNAL MEMORY CHIP SELECTS:</b> Based on the 6-32K memory regions.                 |  |

| WEMEMs     | 1                  | 0   | <b>EXTERNAL MEMORY WRITE ENABLE:</b> Based on the 6-32K memory regions.                 |  |

| OEMEMs     | 1                  | 0   | <b>EXTERNAL MEMORY OUTPUT ENABLE:</b> Based on the 6-32K memory regions.                |  |

#### **Table 3. Miscellaneous Pins**

| Pin Name | Pin Count Pin Type |   | Pin Description                                                                                                                            |

|----------|--------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------|

| PRGM     | 1                  | I | PROGRAM ENABLE: This pin latches the As[15:0] bus to determine the MODEp[7:0] and MODEs[7:0] registers.                                    |

| XCVR     | 1                  | I | <b>TRANSCEIVER MODE:</b> This pin puts TrailBlazer device into a transceiver-like mode, supports internal DSP DMA through the TrailBlazer. |

2231 Lawson Lane • Santa Clara, CA 95054-3311 • 1-800-379-4774 • Fax: (408) 588-0806 • e-mail: sales@issiusa.com • www.issiusa.com