## Low Cost DDR Phase Lock Loop Clock Driver

#### **Recommended Application:**

DDR Clock Driver

#### **Product Description/Features:**

- · Low skew, low jitter PLL clock driver

- I<sup>2</sup>C for functional and output control

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

### Switching Characteristics:

- PEAK PEAK jitter (66MHz): <120ps

- PEAK PEAK jitter (>100MHz): <75ps

- CYCLE-CYCLE jitter (>100MHz):<50ps

- OUTPUT OUTPUT skew: <100ps

- Output Rise and Fall Time: 650ps 950ps

- DUTY CYCLE: 49.5% 50.5%

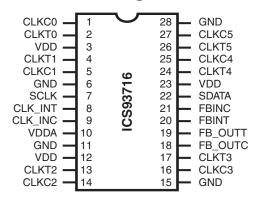

### **Pin Configuration**

28-Pin SSOP

### **Functionality**

|               | INPUTS  |                     |      |      | PLL State |         |           |

|---------------|---------|---------------------|------|------|-----------|---------|-----------|

| AVDD          | CLK_INT | CLK_INC             | CLKT | CLKC | FB_OUTT   | FB_OUTC | FLL State |

| 2.5V<br>(nom) | L       | Н                   | L    | Н    | L         | Н       | on        |

| 2.5V<br>(nom) | Н       | L                   | Н    | L    | Н         | L       | on        |

| 2.5V<br>(nom) | <20M    | IHz) <sup>(1)</sup> | Z    | Z    | Z         | Z       | off       |

### **Block Diagram**

# ICS93716

# **Preliminary Product Preview**

# **Pin Descriptions**

| PIN NUMBER           | PIN NAME  | TYPE | DESCRIPTION                                                                                                                                          |

|----------------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6, 11, 15, 28        | GND       | PWR  | Ground                                                                                                                                               |

| 27, 25, 16, 14, 5, 1 | CLKC(5:0) | OUT  | "Complementory" clocks of differential pair outputs.                                                                                                 |

| 26, 24, 17, 13, 4, 2 | CLKT(5:0) | OUT  | "True" Clock of differential pair outputs.                                                                                                           |

| 3, 12, 23            | VDD       | PWR  | Power supply 2.5V                                                                                                                                    |

| 7                    | SCLK      | IN   | Clock input of I <sup>2</sup> C input, 5V tolerant input                                                                                             |

| 8                    | CLK_INT   | IN   | "True" reference clock input                                                                                                                         |

| 9                    | CLK_INC   | IN   | "Complementory" reference clock input                                                                                                                |

| 10                   | VDDA      | PWR  | Analog power supply, 2.5V                                                                                                                            |

| 18                   | FB_OUTC   | OUT  | "Complementory" Feedback output, dedicated for external feedback. It switches at the same frequency as the CLK. This output must be wired to FB_INC. |

| 19                   | FB_OUTT   | OUT  | "True" "Feedback output, dedicated for external feedback. It switches at the same frequency as the CLK. This output must be wired to FB_INT.         |

| 20                   | FB_INT    | IN   | "True" Feedback input, provides feedback signal to the internal PLL for synchronization with CLK_INT to eliminate phase error.                       |

| 21                   | FB_INC    | IN   | "Complementory" Feedback input, provides signal to the internal PLL for synchronization with CLK_INC to eliminate phase error.                       |

| 22                   | SDATA     | IN   | Data input for I <sup>2</sup> C serial input, 5V tolerant input                                                                                      |

Byte 0: Output Control (1 = enable, 0 = disable)

| BIT   | PIN#   | PWD | DESCRIPTION  |

|-------|--------|-----|--------------|

| Bit 7 | 2, 1   | 1   | CLKT0, CLKC0 |

| Bit 6 | 4, 5   | 1   | CLKT1, CLKC1 |

| Bit 5 | -      | 1   | Reserved     |

| Bit 4 | -      | 1   | Reserved     |

| Bit 3 | 13, 14 | 1   | CLKT2, CLKC2 |

| Bit 2 | 26, 27 | 1   | CLKT5, CLKC5 |

| Bit 1 | -      | 1   | Reserved     |

| Bit 0 | 24, 25 | 1   | CLKT4, CLKC4 |

Byte 1: Output Control

(1 = enable, 0 = disable)

| BIT   | PIN#   | PWD | DESCRIPTION  |

|-------|--------|-----|--------------|

| Bit 7 | -      | 1   | Reserved     |

| Bit 6 | 17, 16 | 1   | CLKT3, CLKC3 |

| Bit 5 | -      | 1   | Reserved     |

| Bit 4 | -      | 1   | Reserved     |

| Bit 3 | -      | 1   | Reserved     |

| Bit 2 | -      | 1   | Reserved     |

| Bit 1 | -      | 1   | Reserved     |

| Bit 0 | -      | 1   | Reserved     |

Byte 2: Reserved (1=enable, 0=disable)

| BIT   | PIN# | PWD | DESCRIPTION |

|-------|------|-----|-------------|

| Bit 7 | -    | 1   | Reserved    |

| Bit 6 | -    | 1   | Reserved    |

| Bit 5 | -    | 1   | Reserved    |

| Bit 4 | -    | 1   | Reserved    |

| Bit 3 | -    | 1   | Reserved    |

| Bit 2 | -    | 1   | Reserved    |

| Bit 1 | -    | 1   | Reserved    |

| Bit 0 | -    | 1   | Reserved    |

Byte 3: Reserved (1=enable, 0=disable)

| BIT   | PIN# | PWD | DESCRIPTION |

|-------|------|-----|-------------|

| Bit 7 | -    | 1   | Reserved    |

| Bit 6 | -    | 1   | Reserved    |

| Bit 5 | -    | 1   | Reserved    |

| Bit 4 | -    | 1   | Reserved    |

| Bit 3 | -    | 1   | Reserved    |

| Bit 2 | -    | 1   | Reserved    |

| Bit 1 | -    | 1   | Reserved    |

| Bit 0 | -    | 1   | Reserved    |

Byte 4: Reserved (1 = enable, 0 = disable)

| BIT   | PIN# | PWD | DESCRIPTION |

|-------|------|-----|-------------|

| Bit 7 | -    | 1   | Reserved    |

| Bit 6 | -    | 1   | Reserved    |

| Bit 5 | -    | 1   | Reserved    |

| Bit 4 | -    | 1   | Reserved    |

| Bit 3 | -    | 1   | Reserved    |

| Bit 2 | -    | 1   | Reserved    |

| Bit 1 | -    | 1   | Reserved    |

| Bit 0 | -    | 1   | Reserved    |

Byte 5: Reserved (1 = enable, 0 = disable)

| BIT  | PIN# | PWD | DESCRIPTION     |

|------|------|-----|-----------------|

| Bit7 | -    | 0   | Reserved (Note) |

| Bit6 | -    | 0   | Reserved (Note) |

| Bit5 | -    | 0   | Reserved (Note) |

| Bit4 | -    | 0   | Reserved (Note) |

| Bit3 | -    | 0   | Reserved (Note) |

| Bit2 | -    | 1   | Reserved (Note) |

| Bit1 | -    | 1   | Reserved (Note) |

| Bit0 | -    | 0   | Reserved (Note) |

Note: Don't write into this register, writing into this register can cause malfunction

### ICS93716

### **Preliminary Product Preview**

### **Absolute Maximum Ratings**

Supply Voltage (VDD & AVDD) ..... -0.5V to 3.6V

Logic Inputs . . . . . . . . . GND  $-0.5\,V$  to  $V_{DD}+0.5\,V$

Ambient Operating Temperature ...... 0°C to +85°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

# Electrical Characteristics - Input/Supply/Common Output Parameters $T_A = 0$ - 85C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

| PARAMETER                        | SYMBOL               | CONDITIONS                                                  | MIN  | TYP             | MAX   | UNITS     |

|----------------------------------|----------------------|-------------------------------------------------------------|------|-----------------|-------|-----------|

| Input High Current               | $I_{IH}$             | VI = VDD or GND                                             |      |                 | //_   | μA        |

| Input Low Current                | $I_{IL}$             | VI = VDD or GND                                             |      |                 |       | μΑ        |

| Operating Supply Current         | $I_{\mathrm{DD2.5}}$ | CL = 0pf                                                    |      |                 | 7/\\/ | mA        |

| operating suppry current         | $I_{DDPD}$           | CL = 0pf                                                    |      |                 | 100   | $\mu^{A}$ |

| Output High Current              | $I_{OH}$             | $VDD = 2.3  \text{V},  \text{V}_{\text{OUT}} = 1  \text{V}$ | V-18 |                 |       | mA        |

| Output Low Current               | $I_{OL}$             | $VDD = 2.3 V, V_{OUT} = 1.2 V$                              | 26   |                 |       | mA        |

| High Impedance<br>Output Current | I <sub>OZ</sub>      | VDD=2.7V, Vout=VDD or GND                                   |      | <b>&gt;&gt;</b> | ±10   | μA        |

| Input Clamp Voltage              | V <sub>IK</sub>      | Iin = -18mA                                                 |      |                 |       | V         |

| High-level output                | V <sub>OH</sub>      | VDD = min to max,<br>IOH = -1 mA                            |      |                 |       | V         |

| voltage                          |                      | VDD = 2.3 V,<br>IOH = -12 mA                                |      |                 |       | V         |

| Low-level output voltage         | V <sub>OL</sub>      | VDD = min to max<br>I <sub>OL</sub> =1 mA                   |      |                 | 0.1   |           |

| ,                                | >(C)                 | VDD = 2.3V $IOH=12  mA$                                     |      |                 | 0.6   | V         |

| Input Capacitance <sup>1</sup>   | $C_{IN}$             | VI = GND or VDD                                             |      |                 |       | pF        |

| Output Capacitance <sup>1</sup>  | $C_{OUT}$            | VOUT = GND or VDD                                           |      | 3               |       | pF        |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Recommended Operating Condition**

$T_A = 0 - 85C$ ; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2 V (unless otherwise stated)

| PARAMETER                | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------|---------------------|------------|-----|-----|-----|-------|

| Analog/core supply       | $\bigcirc_{\Delta}$ |            | 2.3 | 2.5 | 2.7 | V     |

| voltage                  | $A_{ m VDD}$        |            | 2.3 | 2.3 | 2.7 | '     |

| Input voltage level      | V <sub>IN</sub>     |            |     |     |     | V     |

| Input differential-pair  | V <sub>IC</sub>     |            |     |     |     | V     |

| crossing voltage         | v IC                |            |     |     |     | , i   |

| Output differential-pair | V <sub>oc</sub>     |            |     |     |     | V     |

| crossing voltage         | V OC                |            |     |     |     | V     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

**Timing Requirements**T<sub>A</sub> = 0 - 85C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

| PARAMETER                 | SYMBOL             | CONDITIONS                         | MIN | MAX | UNITS |

|---------------------------|--------------------|------------------------------------|-----|-----|-------|

| Operating clock frequency | freq <sub>op</sub> |                                    | 66  | 233 | MHz   |

| Input clock duty cycle    | $d_{tin}$          |                                    | 40  | 60  | %     |

| CLK stabilization         | $T_{STAB}$         | from VDD = 3.3V to 1% target freq. |     | 100 | μs    |

**Switching Characteristics**

| PARAMETER               | SYMBOL                        | CONDITION               | MIN  | TYP | MAX  | UNITS |

|-------------------------|-------------------------------|-------------------------|------|-----|------|-------|

| Jitter; Absoulte Jitter | $T_{ m jabs}$                 | 66MHz                   |      |     | 120  | ps    |

| Jitter, Absourte Jitter | i jabs                        | 100/125/133/167/233MHz  |      |     | 75   | ps    |

| Cycle to Cycle Jitter1  | $T_{\rm cyc}$ - $T_{\rm cyc}$ | 66MHz                   |      |     | 110  | ps    |

| Cycle to Cycle state i  | cyc cyc                       | 100/125/133/167/233MHz  |      | 50  | 65   | ps    |

| Phase error             | t <sub>(phase error)</sub>    |                         | -150 |     | 150  | ps    |

| Output to Output Skew   | $T_{\rm skew}$                |                         |      |     | 100  | ps    |

| Pulse skew              | $T_{\rm skewp}$               |                         |      |     | 100  | ps    |

| Duty cycle              | $D_{\rm C}^{\ 2}$             | 66MHz to 100MHz         | 49.5 |     | 50.5 | %     |

| Duty Cycle              | $D_{\rm C}$                   | 101MHz to 167/233MHz    | 49   |     | 51   | %     |

| Rise Time, Fall Time    | tr, tf                        | Load = $120\Omega/16pF$ | 650  | 800 | 950  | ps    |

#### **Notes:**

- Refers to transition on noninverting output.

- While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies. This is due to the formula: duty cycle= $t_{WH}/t_c$ , were the cycle  $(t_c)$ decreases as the frequency goes up.

# General I<sup>2</sup>C serial interface information

The information in this section assumes familiarity with I<sup>2</sup>C programming. For more information, contact ICS for an I<sup>2</sup>C programming application note.

### **How to Write:**

- Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends a dummy command code

- ICS clock will acknowledge

- Controller (host) sends a dummy byte count

- ICS clock will acknowledge

- Controller (host) starts sending first byte (Byte 0) through byte 5

- ICS clock will *acknowledge* each byte *one at a time*.

- Controller (host) sends a Stop bit

| How to Write:      |                      |  |  |  |

|--------------------|----------------------|--|--|--|

| Controller (Host)  | ICS (Slave/Receiver) |  |  |  |

| Start Bit          |                      |  |  |  |

| Address            |                      |  |  |  |

| D2 <sub>(H)</sub>  |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Dummy Command Code |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Dummy Byte Count   |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Byte 0             |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Byte 1             |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Byte 2             |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Byte 3             |                      |  |  |  |

| -                  | ACK                  |  |  |  |

| Byte 4             |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Byte 5             |                      |  |  |  |

|                    | ACK                  |  |  |  |

| Stop Bit           |                      |  |  |  |

### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the byte count

- Controller (host) acknowledges

- ICS clock sends first byte (Byte 0) through byte 5

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a stop bit

| How to Read:      |                      |  |  |  |

|-------------------|----------------------|--|--|--|

| Controller (Host) | ICS (Slave/Receiver) |  |  |  |

| Start Bit         |                      |  |  |  |

| Address           |                      |  |  |  |

| D3 <sub>(H)</sub> |                      |  |  |  |

|                   | ACK                  |  |  |  |

|                   | Byte Count           |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 0               |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 1               |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 2               |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 3               |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 4               |  |  |  |

| ACK               |                      |  |  |  |

|                   | Byte 5               |  |  |  |

| ACK               |                      |  |  |  |

| Stop Bit          |                      |  |  |  |

#### **Notes:**

- 1. The ICS clock generator is a slave/receiver, I<sup>2</sup>C component. It can read back the data stored in the latches for verification. **Read-Back will support Intel PIIX4 "Block-Read" protocol**.

- 2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

- 3. The input is operating at 3.3V logic levels.

- 4. The data byte format is 8 bit bytes.

- 5. To simplify the clock generator I<sup>2</sup>C interface, the protocol is set to use only "**Block-Writes**" from the controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those two bytes. The data is loaded until a Stop sequence is issued.

- 6. At power-on, all registers are set to a default condition, as shown.

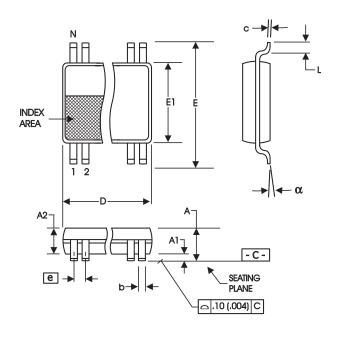

|        | In Millimeters    |      | In Inches         |      |

|--------|-------------------|------|-------------------|------|

| SYMBOL | COMMON DIMENSIONS |      | COMMON DIMENSIONS |      |

|        | MIN               | MAX  | MIN               | MAX  |

| Α      |                   | 2.00 |                   | .079 |

| A1     | 0.05              |      | .002              |      |

| A2     | 1.65              | 1.85 | .065              | .073 |

| b      | 0.22              | 0.38 | .009              | .015 |

| С      | 0.09              | 0.25 | .0035             | .010 |

| D      | SEE VARIATIONS    |      | SEE VARIATIONS    |      |

| E      | 7.40              | 8.20 | .291              | .323 |

| E1     | 5.00              | 5.60 | .197              | .220 |

| е      | 0.65 BASIC        |      | 0.0256 BASIC      |      |

| L      | 0.55              | 0.95 | .022              | .037 |

| N      | SEE VARIATIONS    |      | SEE VARIATIONS    |      |

| α      | 0°                | 8°   | 0°                | 8°   |

#### **VARIATIONS**

|  | N  | D mm. |       | D (inch) |      |

|--|----|-------|-------|----------|------|

|  |    | MIN   | MAX   | MIN      | MAX  |

|  | 28 | 9.90  | 10.50 | .390     | .413 |

Reference Doc.: JEDEC Publication 95, MO-150

10-0033

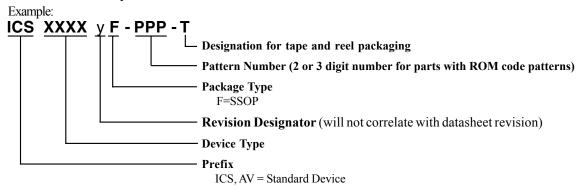

## **Ordering Information**

ICS93716<sub>¥</sub>F-T