**Approved Product**

### PRODUCT FEATURES

- Supports Pentium<sup>TM</sup> asynchronous PCI system board designs using mobile Triton core logic

- Integrates system clocks and distribution buffers

- Operates from 5V or 3.3V supply

- Separate B1 buffer VDD supports mixed 5V/3.3V outputs

- Doze and power down low power operating modes

- 60 mA buffer switching current

- 28 Pin SSOP package for minimum board space

| FREQUENCY SELECTION |    |           |         |  |  |  |

|---------------------|----|-----------|---------|--|--|--|

| S1                  | S0 | MCLK      |         |  |  |  |

|                     |    | DOZE# = 1 | P LE# 7 |  |  |  |

| 0                   | 0  | 66.66     | 33.3    |  |  |  |

| 0                   | 1  | 50        | 33.3    |  |  |  |

| 1                   | 0  | 60        | 33.3    |  |  |  |

| 1                   | 1  | 1         | 23.3    |  |  |  |

### **APPLICATIONS**

Two 3.3V operating odes support new low voltage components on the CPU bus. Operating the B1OUT\* buffers at 3.3V (1VDF) and routing the CPU clock through Book districtions as 3.7 signal to the CPU bus. 60mA on hing current provided at the B1out\* buffers operated at 3 volts.

Br buffers can distribute the CPU signal at 3.3V if the bre logic VDD and B1VDD=3.3V. With this contration, the CPU signal can be distributed to 8 traces with up to 2 planar loads per trace.

**Approved Product**

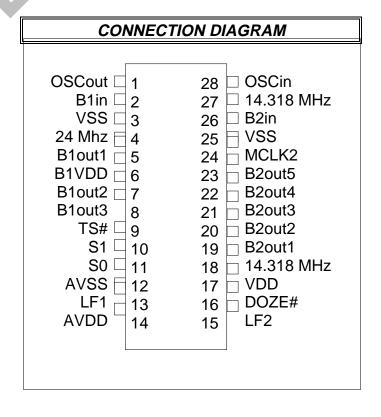

### PIN DESCRIPTION

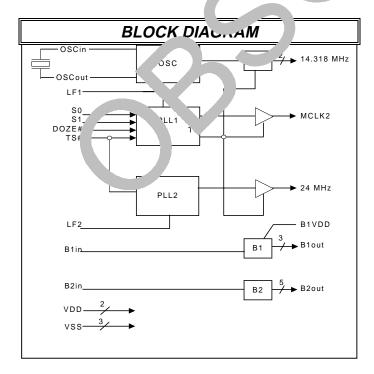

**OSCin OSCout-** These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal (nominally 14.318 MHz). OSCin may also serve as input for an externally generated reference signal.

**S0 and S1-** Standard frequency select inputs. These inputs control the high speed MCLK2, frequency selection. All these inputs have internal pull-ups. MCLK2 switches smoothly to changes in these inputs.

The output frequency selection is shown on page 1.

**MCLK2** - Master clock output. Programmable output frequencies can be selected using S0-S1 inputs.

DOZE# - DOZE control pin. When DOZE# is nigh, the clock chip operates in the standard mode. We en this pin goes low, output frequencies are switch to the preprogrammed DOZE frequencies. Switching DOZE frequencies occurs smoothly to all we tracking internal PLL. This pin has an internal pull-

**B1in and B2in** - On-chip by inputs. These and have internal pull-up.

**B1out** - Buffered outputs in. Sw ching current and output high level con. "led B1VDD.

**B2out** - Buffered outputs of B2 buffer. Switching current and output high level or arolled by VDD.

24 MHz - SIO clock utput

**TS#** - Logic w on this put \* states all PLL outputs if S1=S0 = .gic igh. PLL's stopped to reduce power and all circuitry reset. Other states of S1 and S0 put circ in a test moo. This pin has an internal pull-up.

1.318 Az- 14.318 MHz output. Buffered output from on the reference oscillator or externally provided reference.

**LF1 and LF2 -** These are the phase detector outputs for the lock generators. They are single-ended, tristate put for use as loop error signal. A 0.1uF capacitor to ground should be connected from this pin to form the loop filter. Grounding LF puts PLL in low power mode.

VSS- Circuit ground

**VDD-** Positive power supply

**AVDD-** Analog positive power supply

AVSS- Analog circuit ground

**B1VDD** - 3.3V/5V logic level control for B1out buffers. B1VDD  $\leq$  VDD.

Approved Product

#### **MAXIMUM RATINGS**

Voltage Relative to VSS -0.3VVoltage Relative to VDD 0.3VAmbient Temperature:  $-0^{\circ}C$  to  $+70^{\circ}C$ Storage Temperature:  $-65^{\circ}C$  to  $+150^{\circ}C$ Maximum Power Supply: 7V This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precaution should be taken to avoid application of any voltage higher than the maximum rated voltages to this freuit. Or proper operation, Vin and Vout should for a contained to the range:

√SS<(Vin \ Vou+ \ VDD

Unused in St. st always Led to an appropriate logic voltage level ("ther VSS or VDD).

#### ELECTRICAL CHAR/ TERV TICS Characteristic Symbol Min Typ Max nits **Conditions** Input Low Voltage VIL 8.0 Vuc VIH Input High Voltage 2.0 Vdc All Inputs Input Low Current with Pull IIL TS#, S0-S1 Inputs uA 5 up or Pull-down ±50 IIH 5 TS#, S0-S1 Inputs uΑ Input High Current with Pull-up or Pull-down ±50 Output Low Voltage 8.0 All Outputs IOL = 12 mAOutput High Voltage Vdc All Outputs JΗ 2.4 IOH=12mA Tri-State Leakage June. 107 LF1 and LF2 10 uΑ Dynamic Suppl Current NC. 30 MCLK2 = 50 MHzmΑ TS# = low, S1=S0= HighStatic Supply current ICC(PD) 300 иΑ Short Circuit Curi ' 25 **ISC** mΑ

AVDD = VDD =  $5V \pm 10\%$ , B1VDD =  $3.3v \pm 10\%$  TA =  $0^{\circ}$ C to  $+70^{\circ}$ C

Approved Product

| SWITCHING CHARACTERISTICS                                       |               |     |                           |      |       |                          |

|-----------------------------------------------------------------|---------------|-----|---------------------------|------|-------|--------------------------|

| Characteristic                                                  | Symbol        | Min | Тур                       | Max  | Units | Conditions               |

| Output Rise (0.4V - 2.0V) and Fall (2.0V-0.4V) time All Outputs | tTLH,<br>tTHL | -   | -                         | 1.5  | ns    | 15 pf Load               |

| Output Duty Cycle                                               |               | 45  | 50                        | 55   | %     | Measured at 1.5V         |

| Buffer Propagation Delay tPLH, - 5                              |               | ns  | ∫ pf Lo₂ Measured at 1.5V |      |       |                          |

| Bin to Bout                                                     | tPHL          |     |                           |      |       |                          |

| Buffer out Skew                                                 | tSKEW         | -   | -                         | 250  | ps    | 15 p oad Masured at 1.5V |

| All B1 and B2 Buffer Outputs                                    |               |     |                           |      |       |                          |

| ΔPeriod Adjacent Cycles MCLK2                                   | ΔΡ            | -   | -                         | ±200 | ps    | -                        |

| Jitter Absolute MCLK2                                           | <b>t</b> jab  | -   | ±200                      | -    | DS    | -                        |

| Input Rise/Fall Time S0-S1                                      |               | -   | -                         | 3    | us    | -                        |

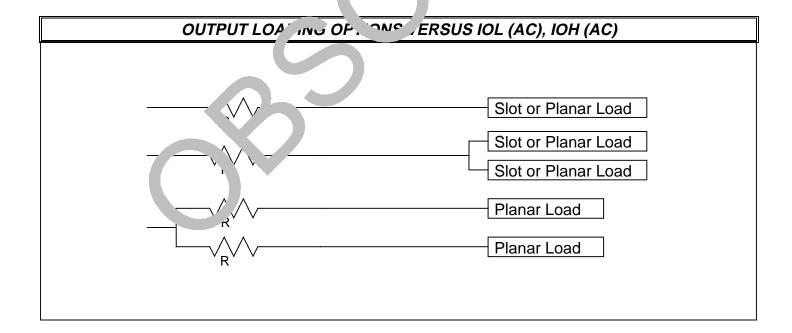

| Switching Current Low:                                          | IOL (AC)      | -   | 60                        | -    | mA    | VOL = 1.5V               |

| Switching Current High:                                         | IOH (AC)      | -   | 50                        | -    | r     | VOL = 1.5V               |

| $V = 5V \pm 10\%$ , B1VDD = 3.3V $\pm 10\%$ , TA = 0°C to 70°C  |               |     |                           |      |       |                          |

**Approved Product**

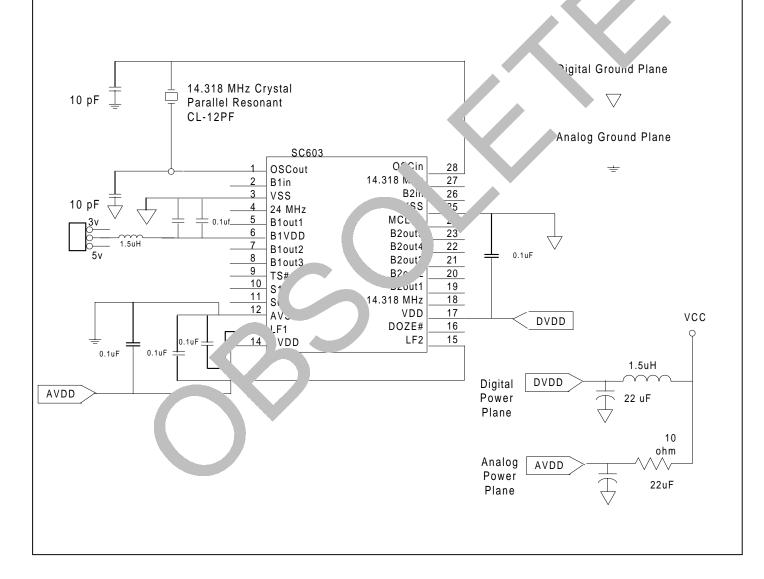

### APPLICATION SUGGESTION

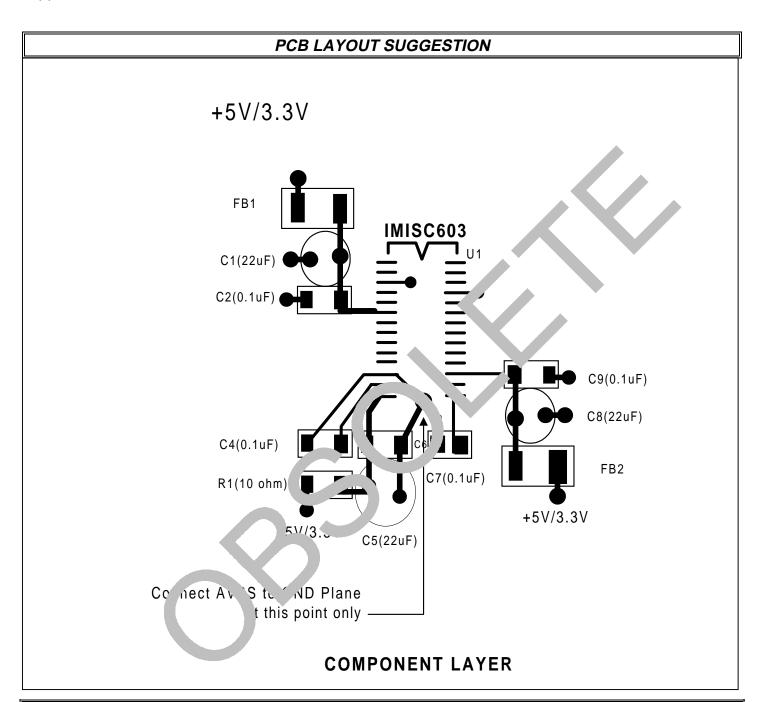

- NOTE 1: Connect analog ground (AVSS) to PC Board ground through one point only.

- NOTE 2: Caps connected to pins 6, 14, and 17 should be as close as possible to their VDD pins.

- NOTE 3: If VDD at clock generator ramps up more than 100 MV DC within a 5 us time period from turning disk drive off, etc.). The values of the DVDD and AVDD filter components should be increased.

Approved Product

### **NOTES**

- 1) Power supply bypass cap  $(0.1\mu\text{F})$  must be positioned close to VDD pins to be effective.

- 2) LF caps must be low leakage, such as multilayer ceramic Z5U or X7r material.

Approved Product

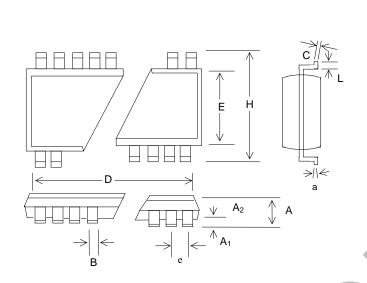

### PACKAGE DRAWING AND DIMENSIONS

| 28 PIN SSOP OUTLINE DIMENSIONS |            |        |       |          |             |       |  |

|--------------------------------|------------|--------|-------|----------|-------------|-------|--|

|                                |            | INCHES |       |          | MILLIMETERS |       |  |

| SYMBOL                         | MIN        | NOM    | , X   | MIN      | NOM         | MAX   |  |

| Α                              | 0.068      | 0.073  | 0.078 | 1.73     | 1.86        | 1.99  |  |

| A <sub>1</sub>                 | 0.002      | 0.0    | 0.00  | 0.05     | 0.13        | 0.21  |  |

| A2                             | 0.066      | .068   | 10    | 1.65     | 1.73        | 1.78  |  |

| В                              | 0.010      | 0.012  | 15    | <u>5</u> | 0.30        | 0.38  |  |

| С                              | 0 5        | ો.006  | 0.00  | 0.13     | 0.15        | 0.22  |  |

| D                              | 0.397      | 0. 3   | 0.407 | 10.07    | 10.20       | 10.33 |  |

| E                              | 0.205      | 0.20ა  | 0.212 | 5.20     | 5.30        | 5.38  |  |

|                                | 0.0256 BSC |        |       | 0.65 BSC |             |       |  |

|                                | ر301`.     | 0.307  | 0.311 | 7.65     | 7.80        | 7.90  |  |

| а                              | 0°         | 4°     | 8°    | 0°       | 4°          | 8°    |  |

| L                              | 0          | 0.030  | 0.037 | 0.55     | 0.75        | 0.95  |  |

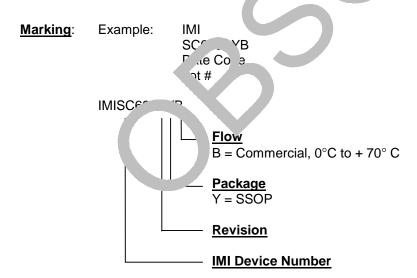

| ORD' KING II TOK. 1 ATION |              |  |                         |  |

|---------------------------|--------------|--|-------------------------|--|

| Part Number               | Package Type |  | Production Flow         |  |

| IMISC603AYB               | 28 Pin SSOP  |  | mmercial, C 2 to + 70°C |  |