**Approved Product**

### PRODUCT FEATURES

- Supports clocking requirements for Multi-Function Products supporting Printers, Copiers, Scanners, Fax/modem integration.

- Programmable CPU clock output.

- Operates from 3.3V or 5V supply

- 60 mA buffer switching current

- 16 Pin SOIC for minimum board space

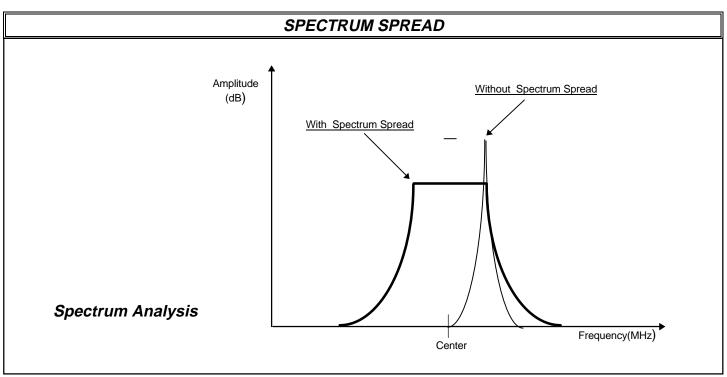

- Integrates a Spectrum Spread technology for EMI attenuation of up to 15dB at harmonic frequencies.

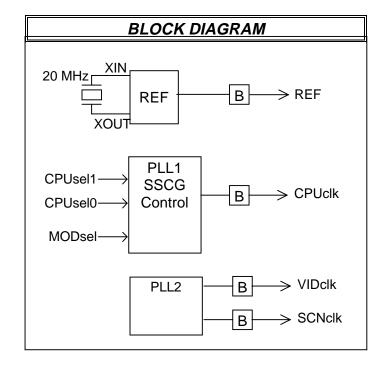

The IMISG536 is a clock generator that integrates clocking requirements for Multi-Function Products or stand alone products such as Printers, Copiers, and Scanners. In addition, it integrates a Spectrum Spread technology, a modulation technique designed specifically for reducing EMI at the fundamental frequency and at its harmonics. The EMI attenuation is proportional to the frequency, therefore achieving greater reduction at the harmonics where it is more difficult to pass federal regulations for radiated emissions (such as FCC, CSPIR, etc.).

The IMISG536 operates from a 20 MHz crystal oscillator across pins 2 and 3, or from an external clock source. The REF output is a buffered output of the input signal at XIN. CPUclk is the modulated output for EMI attenuation. This clock has optional frequency outputs which can be selected with CPUsel(0:1).

VIDclk (60 MHz) and SCNclk(40 MHz) are highly accurate fixed frequencies and therefore are not modulated.

This device is packaged in a 16 pin SOIC package for minimum occupation of board space.

| CONNECTION DIAGRAM |   |            |  |  |  |  |

|--------------------|---|------------|--|--|--|--|

|                    |   |            |  |  |  |  |

| VDD□               | 1 | 16 □REF    |  |  |  |  |

| XIN□               | 2 | 15 □CPUclk |  |  |  |  |

| XOUT□              | 3 | 14 □VSS    |  |  |  |  |

| vss⊏               | 4 | 13 □VDD    |  |  |  |  |

| CPUsel1 <u></u>    | 5 | 12 □SCNclk |  |  |  |  |

| CPUsel0□           | 6 | 11 □VIDclk |  |  |  |  |

| VSS□               | 7 | 10 □VSS    |  |  |  |  |

| VDD□               | 8 | 9          |  |  |  |  |

|                    |   |            |  |  |  |  |

|                    |   |            |  |  |  |  |

| CPUcik SELECTION TABLE |         |              |  |  |  |  |

|------------------------|---------|--------------|--|--|--|--|

| CPUsel1                | CPUsel0 | CPUclk (MHz) |  |  |  |  |

| 0                      | 0       | 16           |  |  |  |  |

| 0                      | 1       | 33           |  |  |  |  |

| 1                      | 0       | 25           |  |  |  |  |

| 1                      | 1       | 50           |  |  |  |  |

**Approved Product**

### PIN DESCRIPTION

**OSCin, OSCout** - These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal. OSCin may also serve as an input for an externally generated CMOS level or AC coupled reference signal.

**CPUsel(0:1)** - Input controls pins used to select the clock frequency of the CPUclk output. See table page 1. These pins have internal pull-ups.

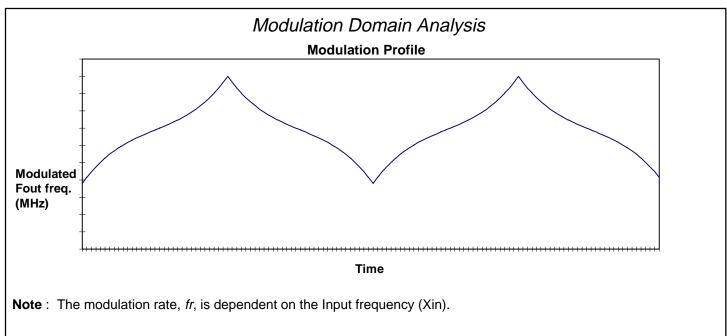

**MODsel -** This pin is used to control the Spectrum Spread enable/disable. When Low, Spectrum Spread is not applied to the CPUclk output. When High (default), this pin enables the CPUclk to be modulated at +/-1.25 % of its center frequency as described in figure 2, Page 4 and reduces EMI as described in figure 1. It has an internal pull-up.

CPUclk - SSCG modulated clock output for system CPU. Frequency may be selected based on the table on page 1.

SCNclk - Non-modulated clock output for system scanner processing. It is centered exactly at 40.00000 MHz.

VIDcIk - Non-modulated clock output for system engine logic. It is centered exactly at 60.00000 MHz.

**VDD** - Circuit positive power supply.

VSS - Circuit ground.

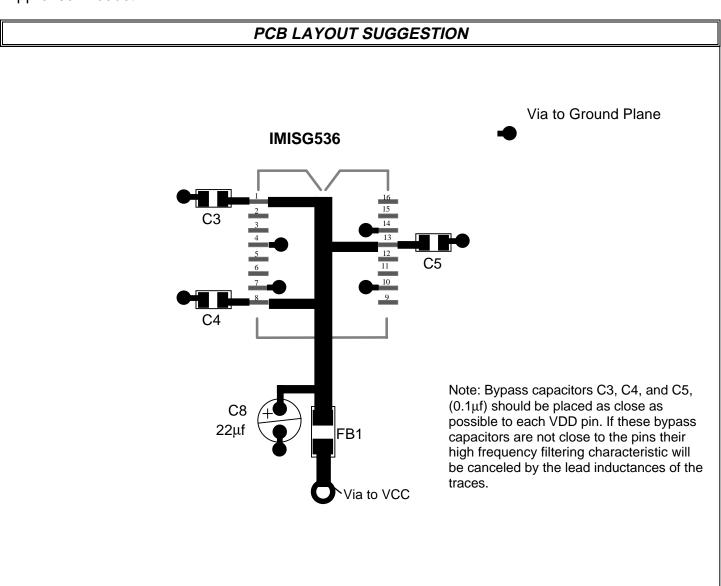

A bypass capacitor (0.1 $\mu$ F) should be placed as close as possible to each VDD pin. If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be canceled by the lead inductances of the traces.

#### **MAXIMUM RATINGS**

Voltage Relative to VSS:

Voltage Relative to VDD:

Storage Temperature:

Ambient Temperature:

Maximum Power Supply:

-0.3V

0.3V

-65°C to + 150°C

-55°C to +125°C

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

**Approved Product**

| ELECTRICAL CHARACTERISTICS                            |          |     |     |     |       |                                 |  |

|-------------------------------------------------------|----------|-----|-----|-----|-------|---------------------------------|--|

| Characteristic                                        | Symbol   | Min | Тур | Max | Units | Conditions                      |  |

| Input Low Voltage                                     | VIL      | -   | -   | 0.8 | Vdc   | CPUsel (0:1), MODsel            |  |

| Input High Voltage                                    | VIH      | 2.0 | -   | -   | Vdc   | CPUsel (0:1), MODsel            |  |

| Input Low, or High Current with Pull- up or Pull-down | IIL, IIH | -   | -   | 66  | μA    | CPUsel (0:1), MODsel            |  |

| Output Low Voltage<br>IOL = 12mA                      | VOL      | -   | -   | 0.4 | Vdc   | All Outputs                     |  |

| Output High Voltage<br>IOH = 12mA                     | VOH      | 2.4 | -   | -   | Vdc   | All Outputs                     |  |

| Dynamic Supply Current                                | Icc      | -   | -   | 40  | mA    | CPUclk = 50 MHz                 |  |

| Static Supply Current                                 | Icc (PD) | -   | 200 | -   | μA    | -                               |  |

| Short Circuit Current                                 | ISC      | 25  | -   | -   | mA    | 1 output at a time - 30 seconds |  |

|                                                       |          | -   | ·   |     |       | VDD = 5 V, TA = 0°C to +70°C    |  |

| SWITCHING CHARACTERISTICS                              |               |                             |    |              |    |                              |  |

|--------------------------------------------------------|---------------|-----------------------------|----|--------------|----|------------------------------|--|

| Characteristic                                         | Symbol        | Symbol Min Typ Max Units Co |    | Conditions   |    |                              |  |

| Output Rise (0.4V - 2.0V)<br>and Fall (2.0V-0.4V) time | tTLH,<br>tTHL | -                           | -  | 2            | ns | 15 pf Load                   |  |

| Output Duty Cycle                                      | -             | 45                          | 50 | 55           | %  | Measured at 1.5V             |  |

| ΔPeriod Adjacent Cycles<br>CPU                         | ΔΡ            | -                           | -  | <u>+</u> 250 | ps | -                            |  |

| Jitter Absolute<br>CPU                                 | tjab          | -                           |    | 500          | ps | MODsel = 0                   |  |

| Switching Current Low*                                 | IOL(AC)       | -                           | 60 | -            | mA | VOL = 1.5V                   |  |

| Switching Current High*                                | IOH(AC)       | -                           | 60 | -            | mA | VOL = 1.5V                   |  |

|                                                        |               |                             |    |              |    | VDD = 5 V, TA = 0°C to +70°C |  |

**Approved Product**

**Approved Product**

### **NOTES**

- 1. POWER SUPPLY BYPASS CAPS (O.1UF) MUST BE POSITIONED CLOSE TO VDD PINS TO BE EFFECTIVE.

- 2. C3, C4, C5, C and C8 CAPS MUST BE LOW LEAKAGE SUCH AS MULTILAYER CERAMIC Z5U OR X7R MATERIAL.

**Approved Product**

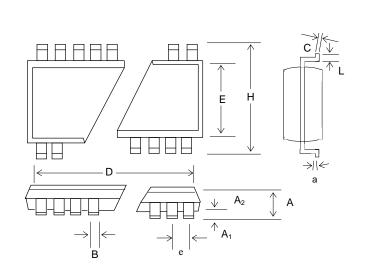

### PACKAGE DRAWING AND DIMENSIONS

| 16 PIN SOIC OUTLINE DIMENSIONS |        |           |        |             |       |       |  |

|--------------------------------|--------|-----------|--------|-------------|-------|-------|--|

|                                |        | INCHES    |        | MILLIMETERS |       |       |  |

| SYMBOL                         | MIN    | NOM       | MAX    | MIN         | NOM   | MAX   |  |

| Α                              | 0.097  | 0.101     | 0.104  | 2.46        | 2.56  | 2.64  |  |

| A <sub>1</sub>                 | 0.0020 | 0.009     | 0.0015 | 0.060       | 0.22  | 0.38  |  |

| A2                             | 0.090  | 0.092     | 0.111  | 2.29        | 2.34  | 2.39  |  |

| В                              | 0.014  | 0.016     | 0.019  | 0.35        | 0.41  | 0.48  |  |

| С                              | 0.0091 | 0.010     | 0.0125 | 0.23        | 0.25  | 0.32  |  |

| D                              | .399   | .407      | .412   | 10.13       | 10.34 | 10.46 |  |

| Е                              | 0.285  | 0.296     | 0.299  | 7.24        | 7.52  | 7.59  |  |

| е                              |        | 0.050 BSC | )      | 1.27 BSC    |       |       |  |

| Н                              | 0.400  | 0.406     | 0.40   | 10.16       | 10.31 | 10.41 |  |

| а                              | 0°     | 5°        | 10°    | 0°          | 5°    | 10°   |  |

| L                              | 0.24   | 0.032     | 0.040  | 0.61        | 0.81  | 1.02  |  |

| ORDERING INFORMATION                     |             |                           |  |  |

|------------------------------------------|-------------|---------------------------|--|--|

| Part Number Package Type Production Flow |             |                           |  |  |

| IMISG536AXB                              | 16 PIN SOIC | Commercial, 0°C to + 70°C |  |  |

Marking: Example: IMI

SM536AXB Date Code, Lot#

### **IMISM536AXB**