#### **Product Features**

- Supplies:

- 2 Ref clocks

2 Host (CPU) clocks

- 1 free running and 5 PCI Clocks

- 1 48MHz fixed clock

- 1 48 or 24 MHz fixed clock

- Separate supply pins for mixed (3.3/2.5V) voltage application.

- 100 or 66 MHz CPU clock operation

- Spread Spectrum modulation for reducing EMI

- · Rich Power Management Functions.

- 28-pin SSOP & TSSOP packages for minimum board space.

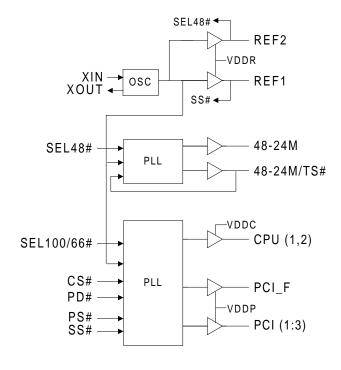

## **Block Diagram**

#### Frequency Table

| SEL 100/66# | CPU Clock | PCI Clock |

|-------------|-----------|-----------|

| 0           | 66 MHz    | 33 MHz    |

| 1           | 100 MHz   | 33 MHz    |

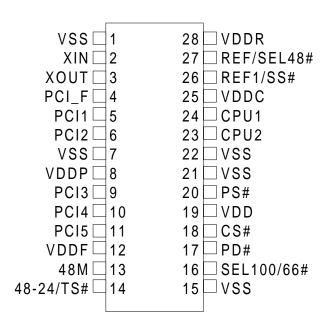

# **Pin Configuration**

**Pin Description**

| Pin Desc            |            | 1                                       |     | ı      |                                                                                                                                                         |

|---------------------|------------|-----------------------------------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN No.             | Pin Name   | PWR                                     | I/O | TYPE   | Description                                                                                                                                             |

| 2                   | XIN        | VDD                                     | I   | XTAL4  | On-chip reference oscillator input pin. Requires either an                                                                                              |

|                     |            |                                         |     |        | external parallel resonant crystal (nominally 14.318 MHz) or                                                                                            |

| _                   |            |                                         |     |        | externally generated reference signal                                                                                                                   |

| 3                   | XOUT       | VDD                                     | 0   | XTAL4  | O-chip reference oscillator output pin. Drives an external                                                                                              |

|                     |            |                                         |     |        | parallel resonant crystal (14.318 MHz) when an externally                                                                                               |

|                     |            |                                         |     | 5)4/5  | generated reference signal is used.                                                                                                                     |

| 19                  | VDD        | -                                       | Р   | PWR    | 3.3 volt power supply for core logic.                                                                                                                   |

| 23, 24              | CPU (1,2)  | VDDC                                    | 0   | C100S  | Clock outputs. CPU frequency table specified on page 1.                                                                                                 |

| 17                  | PD#        | -                                       | l   | INP3U  | Powers down device when LOW                                                                                                                             |

| 18                  | CS#        | -                                       | l   | INP3U  | When signal is LOW, stops CPU clocks in low state.                                                                                                      |

| 16                  | SEL100/66# | -                                       | I   | INP3   | Frequency select input pins. See frequency select table on page 1. NO INTERNAL PULLUP RESISTOR IS PROVIDED BY DEVICE                                    |

| 25                  | VDDC       | -                                       | Р   | PWR    | 2.5V power for CPU and Host clock outputs.                                                                                                              |

| 4                   | PCI F      | VDDP                                    | 0   | P100S  | Free running PCI clock 3.3V. Does not stop when PS# is at a                                                                                             |

| •                   | . 5        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     | 1 1000 | logic LOW level                                                                                                                                         |

| 5,6,9,<br>10,11     | PCI(1:5)   | VDDP                                    | 0   | P100S  | PCI output clocks. See frequency table of page 1.                                                                                                       |

| 20                  | PS#        | -                                       | I   | INP3U  | When signal is LOW, stops all PCI clocks in low state.                                                                                                  |

| 8                   | VDDP       | -                                       | Р   | PWR    | 3.3 Volt power supply pins for free running PCI clock output buffer.                                                                                    |

| 13                  | 48M        | VDDF                                    | 0   | U48    | Fixed 48 MHz clock.                                                                                                                                     |

| 14                  | 48-24M/TS# | VDDF                                    | I/O | U48BU  | Power up selectable 48 or 24 MHz clock. If strapped LOW at powerup causes the devices outputs to be tri-stated until the next power up sequence occurs. |

| 26                  | REF1/SS#   | VDDR                                    | I/O | U48BU  | At power up this pin determines if the device's spread                                                                                                  |

|                     |            |                                         |     |        | spectrum modulation feature is enabled or disabled. After                                                                                               |

|                     |            |                                         |     |        | power up this pin becomes a reference clock output. A 0 (logic                                                                                          |

|                     |            |                                         |     |        | low) enables SSCG and a 1 (logic high) disables SSCG.                                                                                                   |

| 27                  | REF2/SEL48 | VDDR                                    | I/O | U48BU  | At power up this pin determine the frequency of the clock at pin                                                                                        |

|                     | #          |                                         |     |        | 14. If it is LOW, the clock will be 48 MHz, if HIGH the clock will                                                                                      |

|                     |            |                                         |     |        | be 24 MHz. After power up this pin will become a reference                                                                                              |

| 12                  | VDDE       |                                         | D   | PWR    | clock output.                                                                                                                                           |

|                     | VDDF       | -                                       | Р   |        | Power for fixed clock output buffer.                                                                                                                    |

| 1, 7, 15,<br>21, 22 | VSS        | -                                       | Р   | PWR    | Ground pins for device.                                                                                                                                 |

| 28                  | VDDR       | -                                       | Р   | PWR    | Power for Reference Oscillator output buffer.                                                                                                           |

|                     |            |                                         |     |        |                                                                                                                                                         |

#### Notes

1. INP3U pins have internal pullup resistors that will guarantee to a logic 1 (high) level if no connection is made to the device's pin. INP3 pins do not contain this function and must be electrically connected to VDD or VSS by external circuitry to ensure a valid logic 1 or 0 is sensed.

## **Frequency Selection Table**

|                       | Outputs                   |               |         |        |        |           |  |  |  |  |

|-----------------------|---------------------------|---------------|---------|--------|--------|-----------|--|--|--|--|

| Descriptions          | 48-24M/TS#<br>at Power UP | SEL<br>66/100 | CPU     | PCI    | 48M    | 48/24M    |  |  |  |  |

| All Outputs Tri-State | 0                         | 0             | Hi-Z    | Hi-Z   | Hi-Z   | Hi-Z      |  |  |  |  |

| 66 MHz                | 1                         | 0             | 66 MHz  | 33 MHz | 48 MHz | 24/48 MHz |  |  |  |  |

| 100 MHz               | 1                         | 1             | 100 MHz | 33 MHz | 48 MHz | 24/48 MHz |  |  |  |  |

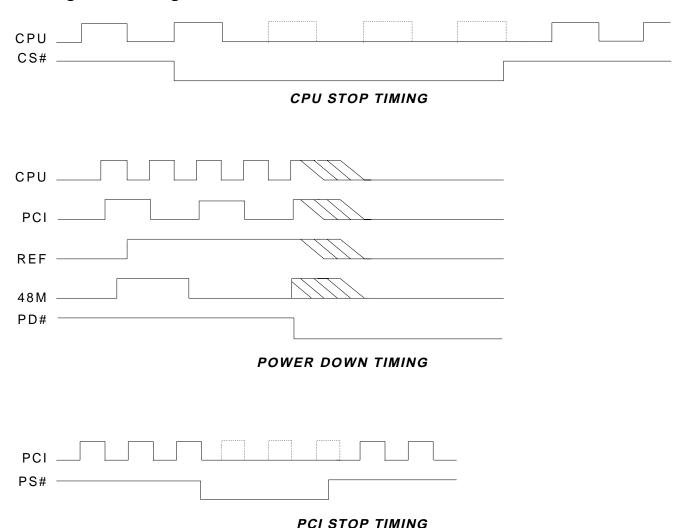

## **Power Management Functions**

| PS# | CS# | PD# | CPU | 48M | PCI | PCI_F | VCOs |

|-----|-----|-----|-----|-----|-----|-------|------|

| Х   | X   | 0   | LOW | LOW | LOW | LOW   | OFF  |

| 1   | 0   | 1   | ON  | ON  | LOW | ON    | ON   |

| 0   | 1   | 1   | LOW | ON  | ON  | ON    | ON   |

| 0   | 0   | 1   | LOW | ON  | LOW | ON    | ON   |

| 1   | 1   | 1   | ON  | ON  | ON  | ON    | ON   |

CS# is an input clock synthesizer. It is used to turn off the CPU clocks for low power operation. CS# is asserted asynchronously by the external clock control logic with the rising edge of free running PCI clock (and hence CPU Clock) and must be internally synchronized to the external PCI\_F output. All other clocks will continue to run while the CPU clocks are disabled. The CPU clocks must always be stopped in a low state and started in such a manner as to guarantee that the high pulse width is a full pulse. CPU clock on latency need to be 2 or 3 CPU clocks periods in time and CPU clock off latency needs to be 2 or 3 CPU clocks periods in time.

## **Power Management Timing**

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the clock synthesizer. PD# is an asynchronous function for powering up the system. Internal clocks are not running after the device is put in power down. When PD# is active low, all clocks need to be driven to a low value and held prior to turning off the VCO's and the Crystal. The power-up latency needs to be less than 3 mS. The power down latency should be as short as possible but conforming to the sequence requirements shown below. AS# and CS# are considered to be don't cares during the power down operations.

# **Power Management Timing**

|        |                                 | Latency                                              |

|--------|---------------------------------|------------------------------------------------------|

| Signal | Signal State                    | No. of rising edges of free running PCI CLOCK (PCIF) |

| CS#    | 0 (disabled)                    | 1                                                    |

|        | 1 (enabled)                     | 1                                                    |

| PD#    | 1 (cold start/normal operation) | 3 mS                                                 |

|        | 0 (power down)                  | 1                                                    |

## NOTES:

1. Clock on/off latency is defined in the number of rising edges of free running PCI CLOCK between the clock disable goes low/high to the first valid clock comes out of the device.

## **Spread Spectrum Clocking**

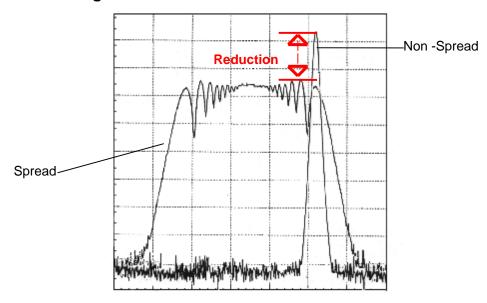

Spectrum Analysis

# **Spectrum Spreading Selection Table**

| Min<br>(MHz) | Center<br>(MHz) | Max<br>(MHz) | CPU<br>Frequency | % OF FREQUENCY<br>SPREADING | MODE        |

|--------------|-----------------|--------------|------------------|-----------------------------|-------------|

| 99.3         | 99.65           | 100          | 100              | .7% (7% + 0%)               | Down Spread |

| 66.13        | 66.37           | 66.6         | 66               | .7% (7% + 0%)               | Down Spread |

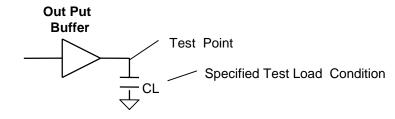

#### **Test and Measurement Condition**

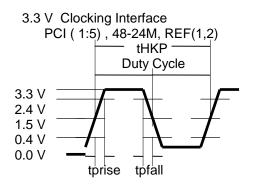

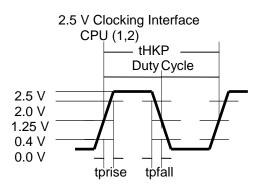

## **Clock Output Wave form**

# **Absolute Maximum Ratings**

Voltage Relative to VSS:

Voltage Relative to VDD:

Storage Temperature:

Operating Temperature:

Maximum Power Supply:

-0.3V

0°C to + 125°C

0°C to +70°C

7V

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin should be constrained to the range:

VSS<(Vin)<VDD Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

#### **DC Electrical Characteristics**

| Characteristic                   | Symbol              | Min                                                                                      | Тур | Max | Units | Conditions                                     |  |  |  |  |

|----------------------------------|---------------------|------------------------------------------------------------------------------------------|-----|-----|-------|------------------------------------------------|--|--|--|--|

| Input Low Voltage                | VIL                 | -                                                                                        | -   | 0.8 | Vdc   |                                                |  |  |  |  |

| Input High Voltage               | VIH                 | 2.0                                                                                      | -   | -   | Vdc   |                                                |  |  |  |  |

| Input Low Current                | IIL                 |                                                                                          |     | -66 | μΑ    |                                                |  |  |  |  |

| Input High Current               | IIH                 |                                                                                          |     | 5   | μΑ    |                                                |  |  |  |  |

| Output Low Voltage<br>IOL = 4mA  | VOL                 | -                                                                                        | -   | 0.4 | Vdc   | All Outputs (see buffer spec)                  |  |  |  |  |

| Output High Voltage<br>IOH = 4mA | VOH                 | 2.4                                                                                      | -   | -   | Vdc   | All Outputs Using 3.3V Power (see buffer spec) |  |  |  |  |

| Tri-State leakage Current        | loz                 | -                                                                                        | -   | 10  | μΑ    |                                                |  |  |  |  |

| Dynamic Supply Current           | Idd2 <sub>66</sub>  | -                                                                                        | -   | 35  | mA    | TS# = 1, 100/66 = 0, CS# = 1                   |  |  |  |  |

| (2.5 Volt Supply)                | Idd2 <sub>100</sub> | -                                                                                        | -   | 45  | mA    | TS# = 1, 100/66 = 0, CS# = 1                   |  |  |  |  |

| Dynamic Supply Current           | Idd3 <sub>66</sub>  | -                                                                                        | -   | 60  | mA    | TS# = 1, 100/66 = 1, CS# = 1                   |  |  |  |  |

| (3.3 Volt Supply)                | Idd3 <sub>100</sub> | -                                                                                        | -   | 60  | mA    | TS# = 1, 100/66 = 1, CS# = 1                   |  |  |  |  |

| Power Down Mode                  | 12.5 <sub>PD</sub>  | -                                                                                        | -   | 50  | μΑ    | PD# at logic low level                         |  |  |  |  |

| Power Down Mode                  | 13.3 <sub>PD</sub>  | -                                                                                        | -   | 200 | μΑ    | PD# at logic low level                         |  |  |  |  |

| VDD = VD                         | DF = VDDI           | $VDD = VDDF = VDDP = VDDR = 3.3V \pm 5\%$ , $VDDC = 2.5V \pm 5\%$ , $TA = 0$ °C to +70°C |     |     |       |                                                |  |  |  |  |

### **AC Characteristics**

| Characteristic                                 | Symbol | Min | Тур | Max          | Units | Conditions                                                              |

|------------------------------------------------|--------|-----|-----|--------------|-------|-------------------------------------------------------------------------|

| Output Duty Cycle                              | -      | 45  | 50  | 55           | %     | CPU and CPU/2 = Measured at 1.25V all others measured at 1.50V          |

| CPU to PCI Offset                              | tOFF   | 1   | -   | 4            | ns    | CPU = 20 pF load Measured at 1.25V                                      |

|                                                |        |     |     |              |       | PCI = 30 pF load Measure at 1.50V                                       |

| Buffer out Skew All CPU and PCI Buffer Outputs | tSKEW  | -   | -   | 250          | ps    | CPU = 20 pF load Measured at 1.25V<br>PCI = 30 pF Load Measured at 1.5V |

| ΔPeriod Adjacent Cycles                        | ΔΡ     | -   | -   | <u>+</u> 250 | ps    | CPU and CPU/2                                                           |

| ΔPeriod Adjacent Cycles                        | ΔΡ     | -   | -   | <u>+</u> 500 | pS    | PCI Only                                                                |

VDD = VDDF = VDDP =VDDR =3.3 $V \pm 5\%$ , VDDC = 2.5 $V \pm 5\%$ ,, TA = 0°C to +70°C

### **AC Skew Requirements**

| Characteristic | Bank Skew | Cycle to Cycle Jitters | VDD  | Skew, Jitters Measure Point |

|----------------|-----------|------------------------|------|-----------------------------|

| CPU            | 175pS     | 250pS                  | 2.5V | 1.25V                       |

| 48 MHz         | n/a       | 500pS                  | 3.3V | 1.5V                        |

| PCI, PCI_F     | 500pS     | 500pS                  | 3.3V | 1.5V                        |

| Ref            | n/a       | 500pS                  | 3.3V | 1.5V                        |

## **Offset Requirements**

| Characteristic    | Bank Offset         | Measurement Loads (lumped) | Measure Points          |

|-------------------|---------------------|----------------------------|-------------------------|

| CPU to PCI, PCI-5 | 1.5-4.0nS CPU leads | CPU @ 20pF, PCI @ 30 pF    | CPU @ 1.25V, PCI @ 1.5V |

## **Buffer Characteristics for CPU Outputs**

| Characteristic                       | Symbol                                                                                      | Min | Тур | Max | Units | Conditions     |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|----------------|--|--|--|

| Pull-Up Current Min                  | IOH <sub>min</sub>                                                                          | -82 | -   |     | mA    | Vout = 1.0 V   |  |  |  |

| Pull-Up Current Max                  | IOH <sub>max</sub>                                                                          |     |     | -67 | mA    | Vout = 2.375 V |  |  |  |

| Pull-Down Current Min                | IOL <sub>min</sub>                                                                          | 81  | -   | -   | mA    | Vout = 1.2 V   |  |  |  |

| Pull-Down Current Max                | IOL <sub>max</sub>                                                                          | -   | -   | 60  | mA    | Vout = 0.3 V   |  |  |  |

| Rise Time<br>Between 0.4 V and 2.4 V | TR                                                                                          | 0.4 | -   | 1.6 | nS    | 20 pF Load     |  |  |  |

| Fall Time<br>Between 0.4 V and 2.4 V | TF                                                                                          | 0.5 | -   | 1.6 | nS    | 20 pF Load     |  |  |  |

| VDD = VD                             | $VDD = VDDF = VDDP = VDDR = 3.3V \pm 5\%$ , $VDDC = 2.5V \pm 5\%$ , $TA = 0$ °C to $+70$ °C |     |     |     |       |                |  |  |  |

# Buffer Characteristics for 48M, 48-24M and REF Outputs

| Symbol             | Min                                                                         | Тур                                                                                                                                           | Max                                                                                             | Units                                                                                                                                                                                      | Conditions                                                                                                                                                                                                                    |

|--------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOH <sub>min</sub> | -29                                                                         | -                                                                                                                                             | -                                                                                               | mA                                                                                                                                                                                         | Vout = 1.0 V                                                                                                                                                                                                                  |

| IOH <sub>max</sub> | -                                                                           | -                                                                                                                                             | -23                                                                                             | mA                                                                                                                                                                                         | Vout = 3.135 V                                                                                                                                                                                                                |

| IOL <sub>min</sub> | 29                                                                          | -                                                                                                                                             | -                                                                                               | mA                                                                                                                                                                                         | Vout = 1.95 V                                                                                                                                                                                                                 |

| IOL <sub>max</sub> | -                                                                           | -                                                                                                                                             | 27                                                                                              | mA                                                                                                                                                                                         | Vout = 0.4 V                                                                                                                                                                                                                  |

| TR                 | 0.5                                                                         | -                                                                                                                                             | 2.0                                                                                             | nS                                                                                                                                                                                         | 20 pF Load                                                                                                                                                                                                                    |

| TF                 | 0.5                                                                         | -                                                                                                                                             | 2.0                                                                                             | nS                                                                                                                                                                                         | 20 pF Load                                                                                                                                                                                                                    |

|                    | IOH <sub>min</sub> IOH <sub>max</sub> IOL <sub>min</sub> IOL <sub>max</sub> | IOH <sub>min</sub> -29           IOH <sub>max</sub> -           IOL <sub>min</sub> 29           IOL <sub>max</sub> -           TR         0.5 | IOH <sub>min</sub> -29 - IOH <sub>max</sub> IOL <sub>min</sub> 29 - IOL <sub>max</sub> TR 0.5 - | IOH <sub>min</sub> -29     -     -       IOH <sub>max</sub> -     -     -23       IOL <sub>min</sub> 29     -     -       IOL <sub>max</sub> -     -     27       TR     0.5     -     2.0 | IOH <sub>min</sub> -29     -     -     mA       IOH <sub>max</sub> -     -     -23     mA       IOL <sub>min</sub> 29     -     -     mA       IOL <sub>max</sub> -     -     27     mA       TR     0.5     -     2.0     nS |

$VDD = VDDP = VDDR = 3.3V \pm 5\%$ ,  $VDDC = 2.5V \pm 5\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

# **Buffer Characteristics for PCI\_F, PCI (1:5)**

| Characteristic                       | Symbol             | Min | Тур | Max | Units | Conditions     |

|--------------------------------------|--------------------|-----|-----|-----|-------|----------------|

| Pull-Up Current Min                  | IOH <sub>min</sub> | -33 | -   | -   | mA    | Vout = 1.0 V   |

| Pull-Up Current Max                  | IOH <sub>max</sub> | -   | -   | -33 | mA    | Vout = 3.135 V |

| Pull-Down Current Min                | IOL <sub>min</sub> | 30  | -   | -   | mA    | Vout = 1.95 V  |

| Pull-Down Current Max                | IOL <sub>max</sub> | -   | -   | 38  | mA    | Vout = 0.4 V   |

| Rise Time<br>Between 0.4 V and 2.4 V | TR                 | 0.5 | -   | 2.0 | nS    | 30 pF Load     |

| Fall Time<br>Between 0.4 V and 2.4 V | TF                 | 0.5 | -   | 2.0 | nS    | 30 pF Load     |

*VDDP= VDDR =3.3V*  $\pm 5\%$ , *VDDC = 2.5V*  $\pm 5\%$ , *TA = 0°C to +70°C*

## **Crystal and Reference Oscillator Parameters**

| Characteristic              | Symbol     | Min    | Тур      | Max     | Units | Conditions                                                  |

|-----------------------------|------------|--------|----------|---------|-------|-------------------------------------------------------------|

| Frequency                   | Fo         | 12.00  | 14.31818 | 16.00   | MHz   |                                                             |

| Tolerance                   | TC         | -      | -        | +/-100  | PPM   | Calibration note 1                                          |

|                             | TS         | -      | ı        | +/- 100 | PPM   | Stability (Ta -10 to +60C) note 1                           |

| Mode                        | OM         | -      | ı        | -       |       | Parallel Resonant                                           |

| Pin Capacitance             | CP         |        | 5        |         | pF    | Capacitance of XIN and Xout pins                            |

| DC Bias Voltage             | $V_{BIAS}$ | 0.3Vdd | Vdd/2    | 0.7Vdd  | V     |                                                             |

| Startup time                | Ts         | -      | -        | 30      | μS    |                                                             |

| Load Capacitance            | CL         | -      | 20       | -       | pF    | note 1                                                      |

| Effective Series resistance | R1         | -      | -        | 40      | Ohms  |                                                             |

| Power Dissipation           | DL         | -      | -        | 0.10    | mW    | note 1                                                      |

| Shunt Capacitance           | СО         | -      |          | 7       | pF    |                                                             |

| X1 and X2 Load              | CL         |        | 32       |         | pF    | internal crystal loading capacitors on each pin (to ground) |

For maximum accuracy, the total circuit loading capacitance should be equal to CL. This loading capacitance is the effective capacitance across the crystal pins and includes the device pin capacitance (CP) in parallel with any circuit traces, the clock generator and any onboard discrete load capacitors.

**Budgeting Calculations**

Typical trace capacitance, (< half inch) is 4 pF, Load to the crystal is therefore 2.0 pF Clock generator internal pin capacitance of 36 pF, Load to the crystal is therefore 18.0 pF

the total parasitic capacitance would therefore be = 20.0 pF(matching CL)

Note 1: It is recommended but not mandatory that a crystal meets these specifications.

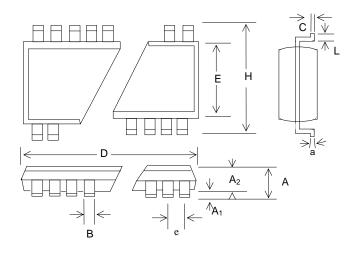

# **Package Drawing and Dimensions**

### 28 Pin SSOP Outline Dimensions

|                |       | INCHES    |       | MILLIMETERS |      |      |

|----------------|-------|-----------|-------|-------------|------|------|

| SYMBOL         | MIN   | NOM       | MAX   | MIN         | NOM  | MAX  |

| Α              | -     | -         | 0.079 | -           | -    | 2.0  |

| A <sub>1</sub> | 0.002 | -         | 0.006 | 0.05        | -    | 0.15 |

| A2             | 0.065 | 0.069     | 0.073 | 1.65        | 1.75 | 1.85 |

| В              | 0.009 | -         | 0.015 | 0.22        | -    | 0.38 |

| С              | 0.004 | -         | 0.010 | 0.09        | -    | 0.25 |

| D              | 0.390 | 0.402     | 0.413 | 6.90        | 7.20 | 7.50 |

| Е              | 0.197 | 0.209     | 0.220 | 5.00        | 5.30 | 5.60 |

| е              | (     | 0.026 BS0 |       | 0.65 BSC    |      |      |

| Н              | 0.291 | 0.307     | 0.323 | 7.40        | 7.80 | 8.20 |

| L              | 0.022 | 0.030     | 0.037 | 0.55        | 0.75 | 0.95 |

| а              | 00    | -         | 8º    | 00          | -    | 80   |

### 28 Pin TSSOP Outline Dimensions

|                |       | INCHES    |       | MILLIMETERS |      |      |

|----------------|-------|-----------|-------|-------------|------|------|

| SYMBOL         | MIN   | NOM       | MAX   | MIN         | NOM  | MAX  |

| А              | -     | -         | 0.047 | -           | -    | 1.20 |

| A <sub>1</sub> | 0.002 | -         | 0.006 | 0.05        | -    | 0.15 |

| A2             | 0.031 | 0.039     | 0.041 | 0.80        | 1.00 | 1.05 |

| В              | 0.007 | -         | 0.012 | 0.19        | 1    | 0.30 |

| С              | 0.004 | -         | 0.008 | 0.09        | 1    | 0.20 |

| D              | 0.378 | 0.382     | 0.386 | 9.60        | 9.70 | 9.80 |

| Е              | 0.169 | 0.173     | 0.177 | 4.30        | 4.40 | 4.50 |

| е              |       | 0.026 BS0 |       | 0.65 BSC    |      |      |

| Н              | 0.244 | 0.252     | 0.260 | 6.20        | 6.40 | 6.60 |

| L              | 0.018 | 0.024     | 0.030 | 0.45        | 0.60 | 0.75 |

| а              | 00    | -         | 8°    | 00          | -    | 80   |

**Ordering Information**

| Part Number | Package Type | Production Flow          |

|-------------|--------------|--------------------------|

| IMIC9714AY  | 28 PIN SSOP  | Commercial, 0°C to +70°C |

| IMIC9714AT  | 28 PIN TSSOP | Commercial, 0°C to +70°C |

Note: The ordering part number is formed by a combination of device number, device revision, package style, and

screening as shown below.

Marking: Example: IMI

C9714A

Date Code, Lot #