# IBM ®

# IBM Packet Routing Switch PRS64G

# **Datasheet**

© Copyright International Business Machines Corporation 2000.

All Rights Reserved

Printed in the United States of America August 2000

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM logo

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM's product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS.

In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

prs64\_title.fm.01 August 31, 2000

# **Contents**

| List of Figures                           | 7  |

|-------------------------------------------|----|

| List of Tables                            | 9  |

| 1. General Information                    | 11 |

| 1.1 Features                              | 11 |

| 1.2 Description                           | 11 |

| 1.3 Conventions                           | 12 |

| 1.3.1 Definition of Terms                 | 12 |

| 2. Architecture                           | 15 |

| 2.1 Basic Data Flow                       | 15 |

| 2.2 Multicast Packets                     | 15 |

| 2.3 Address Management                    | 15 |

| 2.4 Shared Memory Architecture            | 15 |

| 2.5 Flow Control                          | 16 |

| 2.5.1 Output Queuing and Priorities       | 16 |

| 2.5.2 Incoming Flow Process               |    |

| 2.5.3 Incoming Flow Control               |    |

| 2.5.4 Output Flow                         |    |

| 2.5.5 Output Flow Control                 |    |

| 2.5.6 Output Queue Manager                |    |

| 2.5.7 Shared Memory                       |    |

| 2.6 Control Packets                       |    |

| 2.7 Serial Host Interface                 |    |

| 2.8 Serial Data Interface                 |    |

| 2.9 Controllers                           |    |

| 2.10 Signaling                            |    |

| 2.10.1 Input Header (Bit Map)             |    |

| 2.10.2 Output Header (Output Queue Grant) |    |

| 2.10.3 Service Packets                    |    |

| 2.11 Link Integrity                       |    |

| 2.11 Ellik integrity                      |    |

|                                           |    |

| 2.13 Look-Up Table                        |    |

| 2.14 Side Communication Channel           |    |

| 2.15 Expansion Modes                      |    |

| 2.15.1 External Speed Expansion           |    |

| 2.15.2 Internal Speed Expansion           |    |

| 2.15.4 Physical Port Bundling             |    |

| 3. Functional Description                 | 25 |

| 3.1 Logical Interface                     |    |

| 3.2 Physical Interface                    |    |

| 3.3 Packet Type                                                   |                |

|-------------------------------------------------------------------|----------------|

| 3.3.1 Data Packets and Control Packets                            |                |

| 3.3.2 Idle Packets                                                |                |

| 3.3.3 Sync Packets                                                |                |

| 3.4 Header Format                                                 |                |

| 3.4.1 Header Byte H0 - Packet Qualifier                           |                |

| 3.4.2 Header Byte H1, H2, H3, and H4                              |                |

| 3.5 Idle Packet Trailer Format                                    |                |

| 3.6 Packet Reception                                              | 3              |

| 3.6.1 Master Input Port Operation                                 |                |

| 3.6.2 Slave Input Port Operation                                  |                |

| 3.6.3 Parity and CRC Errors                                       |                |

| 3.6.4 Address Insertion                                           | 3              |

| 3.7 Input Flow Control                                            | 3 <sup>,</sup> |

| 3.7.1 Memory Threshold Exceeded Condition                         |                |

| 3.7.2 Programming the Memory-Full Thresholds                      |                |

| 3.7.3 Output Queue Threshold Exceeded Condition                   |                |

| 3.7.4 Packet Reception Fairness                                   | 3              |

| 3.8 Output Queue Grant Signaling                                  | 30             |

| 3.8.1 Adapter Transmission Rules                                  |                |

| 3.8.2 Flow Control Error                                          |                |

| 3.9 Output Queues and Output Queue Priorities                     | 3 <sup>·</sup> |

| 3.10 Shared Memory                                                |                |

| 3.10.1 Organization                                               |                |

| 3.10.2 Shared Memory Access by Local Processor                    |                |

| 3.11 Packet Transmission                                          |                |

| 3.11.1 Output Port Servicing                                      |                |

| 3.11.2 Idle Packet Transmission                                   |                |

| 3.12 Send Grant                                                   |                |

| 3.12.1 Send Grant without Priority Indication                     |                |

| 3.12.2 Send Grant per Priority                                    |                |

| 3.13 Receive Filter                                               |                |

| 3.14 Port Disabling                                               |                |

| 3.15 Address Manager and Address Corruption (Book Keep Mechanism) |                |

| 3.16 Control Packets                                              |                |

| 3.16.1 Control Packet Reception                                   |                |

| 3.16.2 Control Packet Transmission                                |                |

| 3.16.3 Packet Reception Window for Speed Expansion                |                |

| 3.17 Speed Expansion                                              |                |

| 3.17.1 External Speed Expansion                                   |                |

| 3.17.2 Internal Speed Expansion                                   |                |

| 3.17.3 Synchronization of Slave Device with Master Device         |                |

| 3.17.4 Master Slave Address Communication                         |                |

| 3.18 Link Paralleling Bitmap Mapping                              |                |

| 3.19 Best Effort Discard                                          |                |

| 3.19.1 Subflow Best Effort Discard Filter                         |                |

| C. C. Capilon Doct Ellor Diodia i litor                           |                |

| Programming Interface                                             | 51             |

|                                                                   |                |

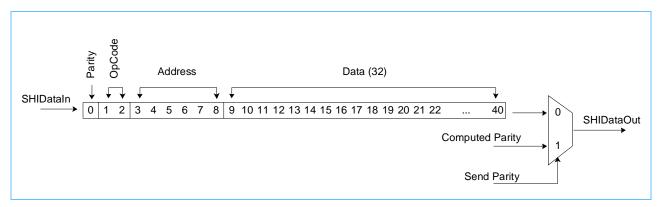

| 4.1 SHI Instruction Register                                      | 52             |

|    | 4.2 SHI Parity Error Checking                          | . 53 |

|----|--------------------------------------------------------|------|

|    | 4.3 SHI Parity Generation                              | . 53 |

|    | 4.4 SHI Operational Protocol                           | . 53 |

|    |                                                        |      |

| 5. | Application Registers                                  | 54   |

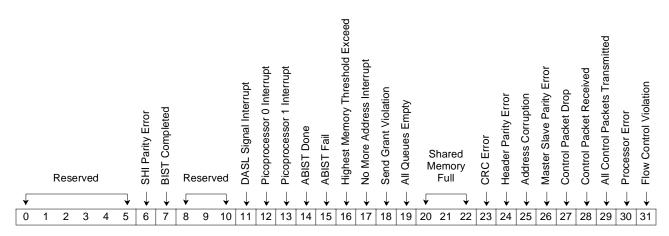

|    | 5.1 Status Register                                    | . 54 |

|    | 5.2 Register Definitions                               | . 55 |

|    | 5.3 SHI Internal Registers                             |      |

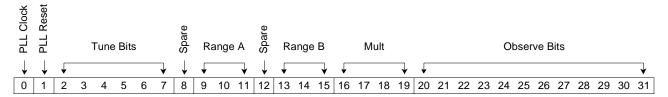

|    | 5.3.1 PLL Programming Register                         |      |

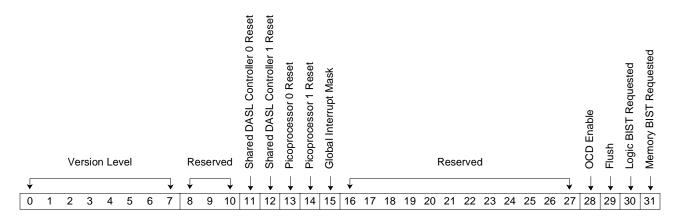

|    | 5.3.2 Reset Register                                   |      |

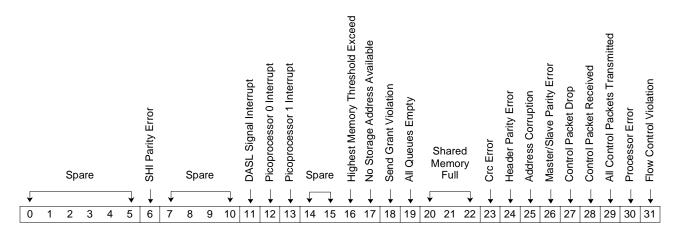

|    | 5.3.3 Interrupt Mask Register                          |      |

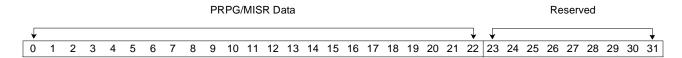

|    | 5.3.4 BIST Counter Register                            |      |

|    | 5.3.5 Bist Data Register                               |      |

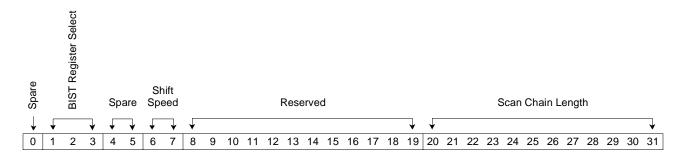

|    | 5.3.6 BIST Select Register                             |      |

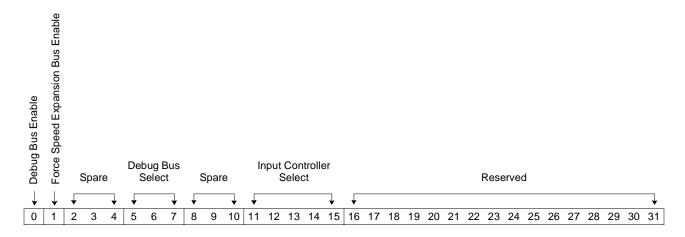

|    | 5.3.7 Debug Bus Select Register                        | . 64 |

|    | 5.4 DASL Programming Registers                         | . 68 |

|    | 5.4.1 DASL Output Drivers Enable Register              |      |

|    | 5.4.2 Output Port Enable Register                      |      |

|    | 5.4.3 Synchronization Packet Transmit Register         | . 68 |

|    | 5.4.4 Input Port Enable Register                       | . 69 |

|    | 5.4.5 DASL Signal Lost Register                        |      |

|    | 5.4.6 SDC Rlos Enable Register                         |      |

|    | 5.4.7 DASL Synchronization Hunt Register               |      |

|    | 5.4.8 DASL Synchronization Status Register             |      |

|    | 5.4.9 Picoprocessor Instruction Memory Access Register |      |

|    | 5.4.10 DASL Configuration Register                     |      |

|    | 5.4.11 DASL Port Error Register                        |      |

|    | 5.4.12 DASL Port Quality Mask Register                 |      |

|    | 5.4.13 DASL Port Quality Register                      |      |

|    | 5.4.14 SDC Resources Address Register                  |      |

|    | 5.4.15 SDC Resources Control Register                  |      |

|    | 5.4.17 SDC Resources Data Registers                    |      |

|    | · · · · · · · · · · · · · · · · · · ·                  |      |

|    | 5.5 Flow Control Pins Status and Setting Registers     |      |

|    | 5.5.2 Send Grant Status Register                       |      |

|    | 5.5.3 Receive Grant Status Register                    |      |

|    | 5.6 Functional Registers                               |      |

|    | 5.6.1 Configuration 0 Register                         |      |

|    | 5.6.2 Configuration 1 Register                         |      |

|    | 5.6.3 Output Queue Enable Register                     |      |

|    | 5.6.4 Input Controller Enable Register                 |      |

|    | 5.6.5 Color Detection Disable Register                 |      |

|    | 5.6.6 Send Grant Enable Register                       |      |

|    | 5.6.7 Force Send Grant Register                        |      |

|    | 5.6.8 Expected Color Received Register                 |      |

|    | 5.6.9 CRC Error Port ID Register                       |      |

|    | 5.6.10 Header Parity Error Port ID Register            |      |

|    | 5.6.11 Error Counters Register                         |      |

|    | 5.6.12 Flow Control Violation Port ID Register         |      |

| 5.6.13 Control Packet Counter Register                                                               |     |

|------------------------------------------------------------------------------------------------------|-----|

| 5.6.14 Output Queues Status Registers 1-4                                                            |     |

| 5.6.15 Color Packet Received Register                                                                |     |

| 5.6.16 Send Grant Violation Register                                                                 |     |

| 5.6.17 Occupancy Counters Register                                                                   |     |

| 5.6.18 Shared Memory Access Registers                                                                |     |

| 5.6.19 Shared Memory Pointer Register                                                                |     |

| 5.6.20 Shared Memory Data Register                                                                   |     |

| 5.6.21 Command Register                                                                              |     |

| 5.6.22 Control Packet Destination Register                                                           |     |

| 5.6.23 Bitmap Filter Register                                                                        |     |

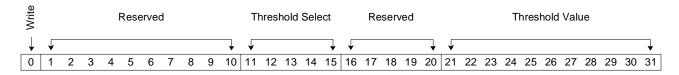

| 5.6.24 Thresholds Access Register                                                                    |     |

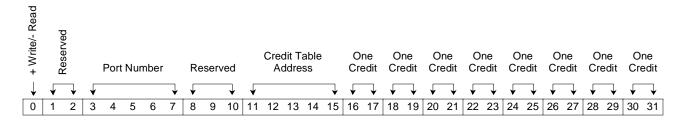

| 5.6.25 Credit Table Access Register                                                                  |     |

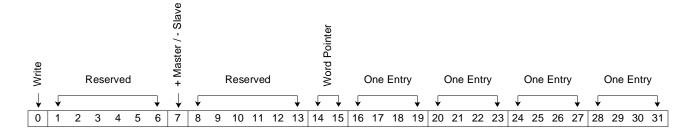

| 5.6.26 Lookup Tables Access Register                                                                 |     |

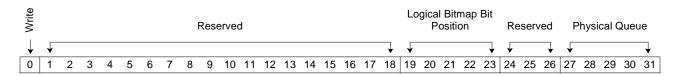

| 5.6.27 Bitmap Mapping Register                                                                       |     |

| 5.6.28 Best Effort Resources Access Register                                                         |     |

| 5.6.29 Best Effort Discard Alarm Register 5.6.30 Side Communication Channel Input Reporting Register |     |

| 6. Reset, Initialization, and Operation                                                              | 100 |

| 6.1 Clock and PLL                                                                                    | 100 |

| 6.2 Reset                                                                                            |     |

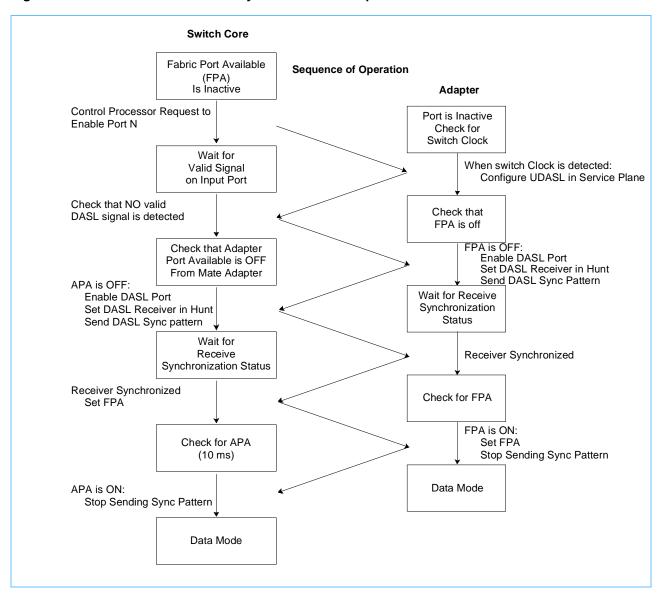

| 6.3 DASL Initialization and Operation                                                                |     |

|                                                                                                      |     |

| 7. I/O Definitions and Timing                                                                        | 103 |

| 7.1 I/O Timing                                                                                       |     |

| 7.1.1 DASL Signals                                                                                   |     |

| 7.1.2 SHI Interface Signals                                                                          |     |

| 7.1.3 Master-Slave Speed Expansion Signals                                                           |     |

| 7.1.0 Mader Glave Opeca Expansion digitals                                                           |     |

| 8. Pin Information                                                                                   | 110 |

| 0. 1 III IIII 01111ati 011                                                                           | 110 |

| 9. Electrical Characteristics                                                                        | 128 |

| 10. Line Termination                                                                                 | 131 |

| 10.1 DASL and SYS_CLK                                                                                |     |

| 10.1 DASL and STS_CER                                                                                | 131 |

| 11. Mechanical Information                                                                           | 132 |

| 12. References                                                                                       | 133 |

| Revision Log                                                                                         | 134 |

# **List of Figures**

| Figure 1: System View with IBM Packet Switch Serial Interface                | . 13 |

|------------------------------------------------------------------------------|------|

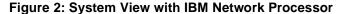

| Figure 2: System View with IBM Network Processor                             | . 13 |

| Figure 3: Packet Routing Switch Block Diagram                                | 14   |

| Figure 4: External Speed Expansion Block Diagram                             |      |

| Figure 5: Internal Speed Expansion Block Diagram                             | . 22 |

| Figure 6: Single Stage Port Expansion Block Diagram                          |      |

| Figure 7: Packet Format 2 Gb/s Port                                          | . 25 |

| Figure 8: Packet Format for 4 Gb/s Port                                      | . 25 |

| Figure 9: Packet Format for 16 Gb/s Port                                     |      |

| Figure 10: Idle Packet Format                                                | . 28 |

| Figure 11: Input-side Grant Operation                                        | . 36 |

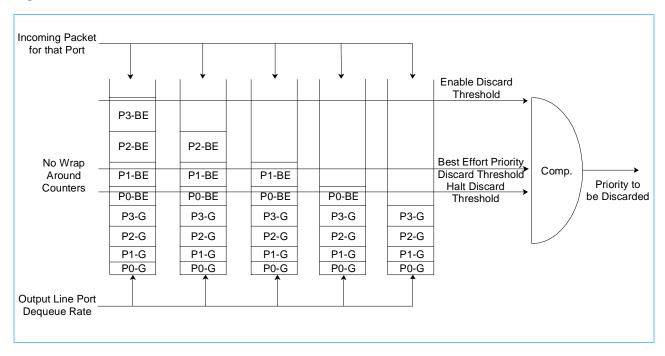

| Figure 12: Best Effort Burst Discard                                         | . 50 |

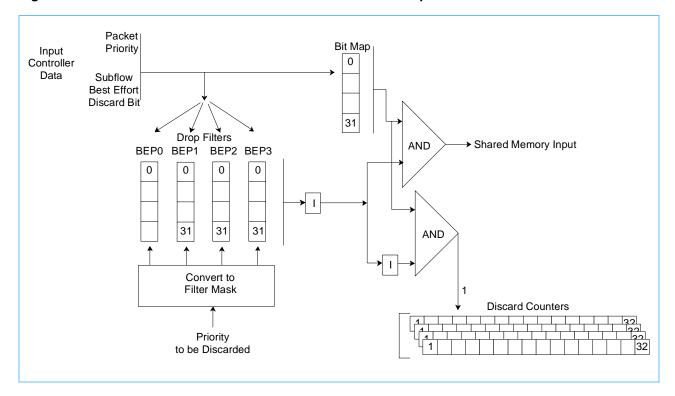

| Figure 13: Subflow Best Effort Discard Mechanism within the Input Controller | . 51 |

| Figure 14: Switch Fabric DASL Port Synchronization Sequence                  | 102  |

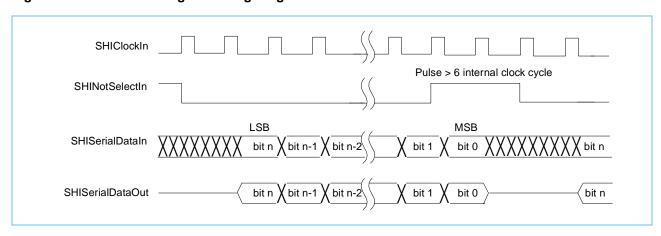

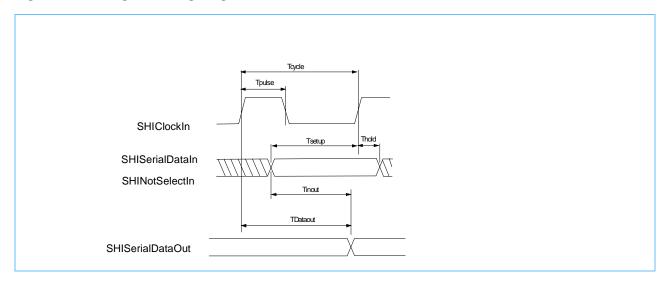

| Figure 15: SHI Interface Signal Timing Diagram                               | 107  |

| Figure 16: SHI Signal Timing Diagram                                         |      |

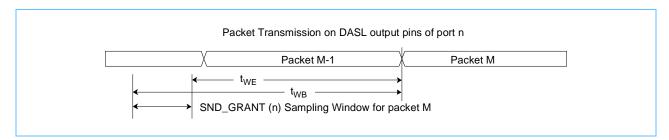

| Figure 17: SND_GRANT(n) Sampling Window                                      |      |

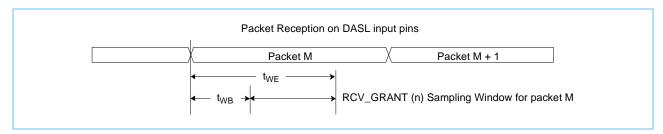

| Figure 18: RCV_GRANT(n)                                                      | 109  |

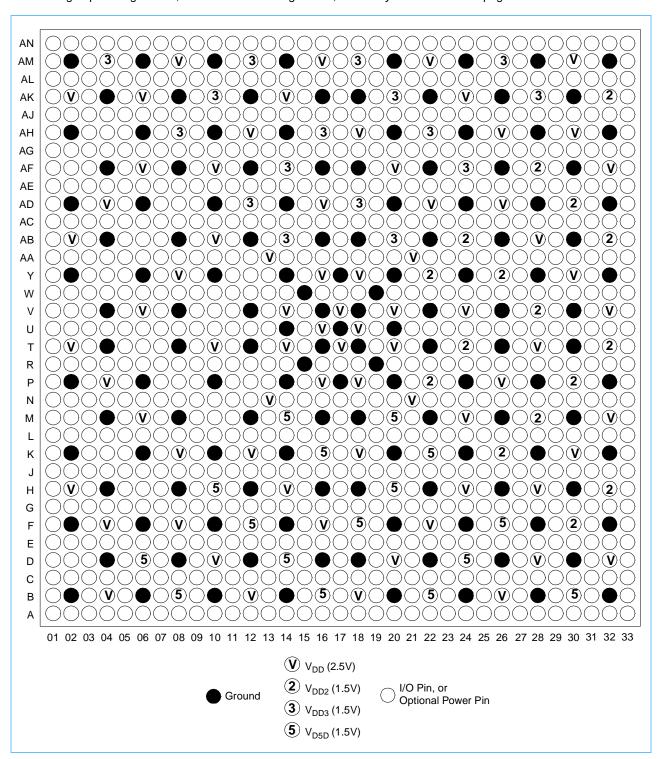

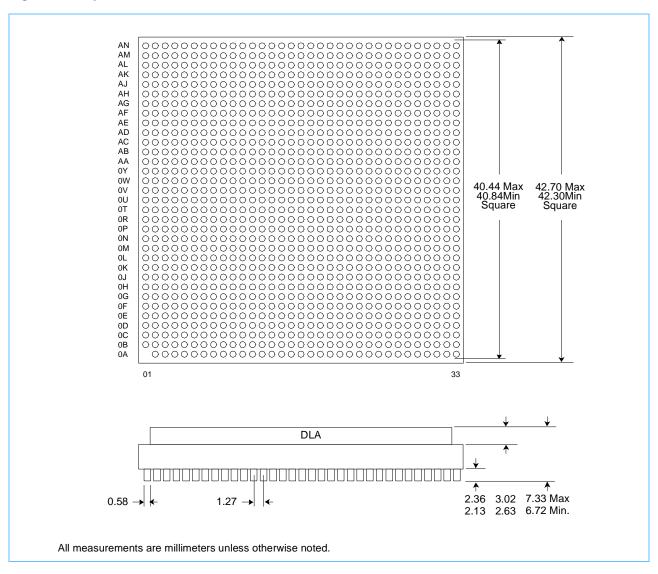

| Figure 19: Pinout                                                            |      |

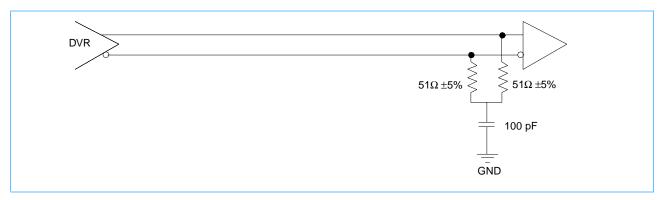

| Figure 20: DASL Termination                                                  | 131  |

|                                                                              | 132  |

# **List of Tables**

| Table 1: Ordering Information                                | 12  |

|--------------------------------------------------------------|-----|

| Table 2: Speed Expansion Shared Memory Buffering Capacities  | 22  |

| Table 3: Link Paralleling Block Diagram                      | 24  |

| Table 4: Physical Bit Organization of a Port                 | 27  |

| Table 10: Header Byte 1 through 4 and Incoming Packet Bitmap | 31  |

| Table 11: Header Byte 1 through 4 and Output Queue Grant     | 32  |

| Table 12: Example of Fly Wheel Counter Update                | 32  |

| Table 15: Shared Memory Reserved Address for Control Packets | 44  |

| Table 16: Port Combination in Internal Speed Expansion       | 45  |

| Table 17: Link Paralleling Configuration Example             | 47  |

| Table 18: SHI OpCode Commands                                | 52  |

| Table 19: DASL Initialization and Operation Registers        | 100 |

| Table 20: Signal Definitions                                 | 103 |

| Table 21: Test Signals                                       | 106 |

| Table 22: DASL Interface Skew                                | 107 |

| Table 23: SHI Signal Timing Values                           |     |

| Table 24: SND_GRANT Sampling Window Timing                   | 109 |

| Table 25: RCV_GRANT (i Sampling Window Timing)               | 109 |

| Table 26: Ground and V <sub>DD</sub> Pin Locations           |     |

| Table 27: Optional Power Pins                                | 111 |

| Table 28: I/O Signal List, Sorted by Signal Name             | 112 |

| Table 29: I/O Signal List, Sorted by Grid Position           |     |

| Table 30: Absolute Maximum Ratings                           | 128 |

| Table 31: Recommended Operating Conditions                   | 129 |

| Table 32: Power Dissipation                                  |     |

| Table 33: Electrical Characteristics for DASL I/Os           |     |

| Table 34: Clocks                                             |     |

| Table 35: Package Information                                | 132 |

# 1. General Information

## 1.1 Features

- · Non-blocking, self-routing, single-stage switch

- 32 input ports and 32 output ports

- · High Performance:

- 1.6 Gb/s to 2 Gb/s throughput per port

- Up to 64 Gb/s single device aggregate throughput

- · Speed Expansion:

- Internal: Support doubling port speed, (reducing the number of ports to 16)

- External: Up to 128 Gb/s aggregate throughput (with two devices)

- Combination of internal and external speed expansion provides 16 ports at 8 Gb/s (with two devices)

- Serial data communication from 400 to 500 Mb/s, compliant with the EIA/JEDEC JESD8-6 standard.

- Multicast support without packet duplication in shared memory

- Dynamically shared output buffer (1024 packets of 64 to 80 bytes)

- Configurable number of traffic priorities (one to four) with programmable output queue thresholds and shared memory thresholds

- Physical Port Bundling by four, with internal or external speed expansion to define logical port at 16 Gb/s

- · Packet lossless scheduled switchover facility

- Serial processor interface (Serial Host Interface)

- Configurable packet lengths of:

- 32 to 40 bytes (increment of two)

- 64 to 80 bytes (increment of four)

- 128 to 160 (increment of eight) with external speed expansion only

- Packet header of two to five bytes, containing destination bit map, packet priority, and switch redundancy support information, all protected by a parity bit

- · Shared output buffer with total capacity of:

- 1024 packets (64 bytes) for a single chip

- 2048 packets (64 bytes) with external speed expansion (with two devices)

- Reception on any input port of Control Packets destined to the local processor

- Transmission of Control Packets from the local processor to any output port

- Detection of link liveness by reception of specific packets

- Programmable byte shuffling in outgoing packets

- CMOS6SF (SA-12E) technology (Ldrawn=0.25 μm, Leff=0.18 μm): 2.5 V compliant LVCMOS compatible I/O for low speed signals

- IEEE 1149.1 standard boundary scan to facilitate circuit board testing

# 1.2 Description

The IBM Packet Routing Switch PRS64G, one of a family of second generation switching devices designed for high performance, non-blocking fixed length packet switching, enables development of scalable switch fabrics of aggregate bandwidth from 64 Gb/s to 512 Gb/s.

The switch receives packets on 32 input ports and routes them to one or more of 32 output ports based on bit map information carried in the packet header. Each port operates at two Gb/s, resulting in a single device throughput of 64 Gb/s. This data speed is

achieved by implementing, in one device, two 32 x 32 sub-switch elements, running at one Gb/s per port and organized internally in speed expansion mode. In addition, 500 Mb/s serial data communication provides, over two differential pairs, the necessary bit rate per island.

Quality of service support is provided through four levels of packet priority. The architecture supports flow control, based on a grant mechanism, and provides programmable thresholds, one per priority.

Scalability of speed is achieved via external speed expansion. Two devices operate in parallel (one as master, the other as slave) to form a 32 x 32 switch core at 4 Gb/s per port. Scalability in port speed is achieved through link paralleling by combining four physical ports together into a logical port of 16 Gb/s. Scalability of ports can be provided by single stage port expansion, which allows the number of ports on the switch fabric to be increased.

No synchronization is required between input ports. However, packets on a given port are always received or transmitted at a fixed rate according to the packet length.

**Table 1: Ordering Information**

| Part Number          | Description               | Bandwidth   | Throughput |

|----------------------|---------------------------|-------------|------------|

| IBM32SW0640DSLCDA250 | IBM Packet Routing Switch | 64-512 Gb/s | 64 Gb/s    |

#### 1.3 Conventions

Throughout this document, standard IBM notation is used: bits and bytes are numbered in ascending order from left to right. Thus the Most Significant Bit (MSB) has the lowest number and the Least Significant Bit (LSB) has the highest number:

Notation for bit encoding is as follows:

- Hexadecimal values are preceded by x and appear in single quotation marks. For example: x'0B00'.

- Binary values in text are either spelled out (zero and one) or appear in single quotation marks For example: '1010'.

- Binary values in the Default and Description columns of the register sections have no special marking, but are separated from text as in this example:

- 0 No action on read access

- 1 Auto-reset interrupt request register upon read access

The use of overbars, for example DDEL\_OUT, designates signals that are active low.

Note: By default, the bits are positive active.

#### 1.3.1 Definition of Terms

BIST: Built in self test

Local Processor: The microprocessor connected to PRS64G through the Serial Host Interface (SHI).

Logical Unit (LU): The part of the packet that is processed by one island. One packet is made of several LUs of equal length (2, 4, 8).

Packet: The user unit information element made of multiple LUs (header + payload).

IBM Utopia-3 Back-Packet Packet Protocol "like" plane Routing Optical Routing PHY Engine Port 0 Switch 0 (Ingress) Switch Serial Interface PRS64G Elements X Plane Utopia-3 "like" ATM or Layer 2 to DASL Interface Device or Layer 3 or Layer 4 ... 31 31 Switching Engine Ĉ(SHI) Local Processor Packet Protocol Routing Optical PHY Engine Port Switch 8 x DASL Serial Links at 500 Mb/s (Egress) Serial Interface Switch Core (NxN)

Figure 1: System View with IBM Packet Switch Serial Interface

The PRS64G enables the construction of non-blocking scalable switch fabrics through repeated instances of the same switch element. It is designed for a wide variety of applications including: campus, WAN edge, access, and backbone switches. The PRS64G along with the IBM Packet Routing Switch Serial Interface provides a complete redundant switch fabric for the attachment of a 32-bit wide interface to any protocol engine. This supports protocols such as Packet Over Sonet (POS), Gigabit Ethernet Multilayer switching, and ATM.

Switch Fabric

Similarly, an IBM PowerNP NP4GS3 can attach directly through the DASL links to the PRS64G, allowing a very compact and powerful switching system. For more information regarding the NP4GS3, see the IBM PowerNP NP4GS3 Product Overview.

PRS64G.fm.01 August 31, 2000

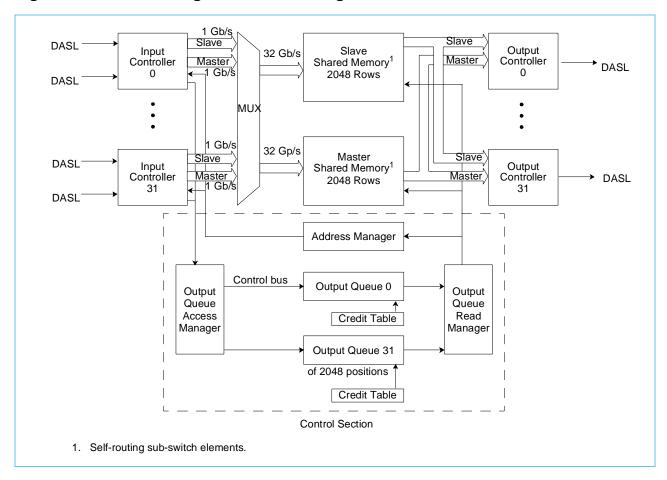

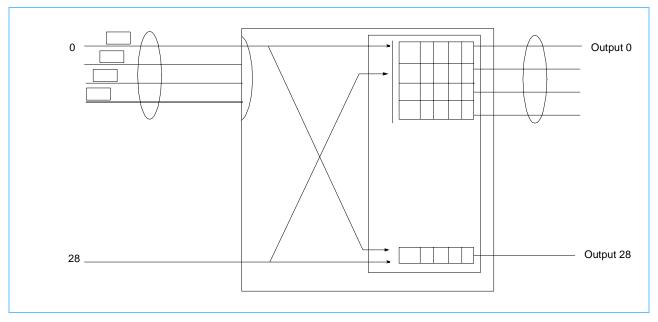

Figure 3: Packet Routing Switch Block Diagram

# 2. Architecture

#### 2.1 Basic Data Flow

The PRS64G incorporates two self-routing sub-switch elements, and a control section that is the same. The device is made of two functional islands that operate identically when the switch is in regular (not speed expansion) mode. The switch has a fixed packet length shared memory, and a buffering capacity of 2048 rows of 16 to 20 bytes.

Each 2 Gb/s port carries two data streams, one master and one slave, each at one Gb/s. The master stream carries the Data packet header bytes, followed by packet payload bytes. The slave stream carries only payload bytes.

The input controllers examine the headers of incoming data packets and check the switch header integrity, using a parity bit on the header bytes. Valid data packets are then stored in the shared memory, and their storage addresses, along with the packet priority and bit map, are further processed by a centralized Output Queue Access Manager. These addresses are enqueued into output queues, one per output port and priority, according to the packet priority and bit map field. Data Packets are then transmitted, one at a time according to their place in the output queues, with the restriction that high priority packets always (except if specified differently by the Credit Table) overtake lower priority packets. However, the priority level to be received is selectable.

#### 2.2 Multicast Packets

Multicast packets are processed the same way. A multicast packet is stored only once in Shared Memory, while its address is enqueued in all output queues indicated by its bit map field. A multicast packet is transmitted on the output ports according to the FIFO structure of each destination output queue (not necessarily at the same time on all ports). Multicast packets can only have one priority for all of their destinations.

# 2.3 Address Management

A central Address Manager maintains a pool of free Shared Memory addresses and provides new store addresses to the Input Controllers. Once a packet is transmitted, its address is returned to the Address Manager. The Address Manager also keeps track of the number of outputs still holding each address, since one address can be copied multiple times for multicast packets. Once this reaches zero, the address is returned to the free address pool.

# 2.4 Shared Memory Architecture

Shared Memory is organized as two banks, one master and one slave, each consisting of 2048 rows of 20 bytes, with one write port and one read port. Access to Shared Memory is performed one input and output port at a time. Sixteen to 20 bytes are transferred at each access, depending on the packet length. A central sequencer grants Shared Memory access to the input and output ports, cyclically. This sequencer cycle is equal, in byte cycles, to the number of data bytes stored at every access in one memory row. It is defined as an integer between 16 and 20, such that packet length is a multiple of this integer. All cycles have equal

length. Without speed expansion or with speed expansion and packet length greater than 128 bytes, an LU is received in two cycles of equal length. In speed expansion and packet length smaller than 128 bytes, it takes only one cycle to receive an LU.

#### 2.5 Flow Control

Flow control is provided for each output queue and for the entire shared memory using a grant mechanism. Grants are given to the ingress of the attached device to allow packets to enter the switch. Similarly, the egress of the attached device provides grants to each output port to enable packets to leave the switch. On the ingress, the attached device receives the output queue grants, which reflect the status of the output queues, and memory grants that reflect the status of the Shared Memory. One output queue grant is provided per output and per priority.

# 2.5.1 Output Queuing and Priorities

Queuing is provided for each output port. Packet addresses from each output are organized into four logical queues of different priority. For each logical queue, packet addresses are organized into a first in first out (FIFO) queuing structure.

Packets are sorted by priority when stored, according to a priority flag they carry. The highest priority is represented by zero and the lowest by three. Packets are transmitted on a given output with the highest available priority always overtaking the lower priorities unless the weighted cyclical function has been enabled.

## 2.5.2 Incoming Flow Process

Each incoming packet contains information about the logical port of its destinations and the logical address (priority) per output (except for Control Packets).

The island controller allows one packet, corresponding to one input, to be processed and stored at a time. Inputs are visited once per sequencer cycle. When the input on which a packet arrives is visited by the island controller, the packet data is stored once in the shared memory. The address of this location is placed in the logical queues (specified by its priority) of all of its destination outputs according to its priority. At the same time, the shared memory counter and the output queue counters of its destination are incremented.

If an incoming packet is marked as a Control Packet, it is also stored in shared memory. Its address is then placed in a Control Packet queue, and an interrupt is sent to the local processor. An incoming Control Packet can only be received if fewer than 32 Control Packets are present in the Control Packet queue. Otherwise, the packet is discarded and a flag is raised.

#### 2.5.3 Incoming Flow Control

Flow control of incoming packets is provided by grants which are authorizations for the attached adapter to transmit a packet. Grants are provided separately for each output port and for each priority of a port. An output queue grant for a priority is provided whenever the total packet count for an output (regardless of priority) is below the output priority threshold. It is removed whenever this count exceeds the threshold value (there is no hysteresis). Grants are also provided for the shared memory for each priority. The shared memory grant (memory grant) for a given priority is provided whenever the total packet count in shared memory is below the shared memory priority threshold, and it is removed whenever this count exceeds the threshold value (there is no hysteresis).

Architecture PRS64G.fm.01

Page 16 of 134

August 31, 2000

An adapter is only allowed to transmit a packet when it has the memory grant for the packet priority as well as the output queue grants for the destination logical outputs. For multicast packets, the adapter is allowed to transmit a packet if it has the memory grant for the packet priority, regardless of output queue grants.

Incoming packets also carry a "best effort" flag. This flag allows packet discard at the input of the island whenever the best effort discard threshold is reached due to persistent traffic overspeed for that output port, leading to a congestion in the attached adapter. The watermark counter used by the input controllers to decide to discard a packet is incremented once per received packet for each output port and decremented according to the line period of the attached port adapter.

Finally, an anti-streaming function is provided at the input controllers to detect badly behaving adapters. When an adapter sends a packet to an output priority for which the output queue grant or memory grant have not been given in the past N packet cycles (programmable from 8 to 36 cycles), the packet is discarded and an interrupt is raised. For multicast packets, the same mechanism is applied, but it takes only the memory grants into consideration.

#### 2.5.4 Output Flow

In each of the four logical output queues, Control Packets and Data Packets are transmitted in the following order:

- 1. Control Packets

- 2. Priority 0 packets

- 3. Priority 1 packets

- 4. Priority 2 packets

- 5. Priority 3 packets

In normal mode of operation, this order cannot be changed.

Through a weighted cyclical mechanism, it is possible to guarantee minimum bandwidth for any priority. The programmable Credit Table indicates which priority should be transmitted at each packet cycle. When a credit is generated for priority N, then a packet of priority N is sent on that output port, provided that the send grant is active for that priority and the corresponding logical queue is not empty. If a queue is empty, the normal algorithm applies.

#### 2.5.5 Output Flow Control

Output flow control is provided by send grants (one per output), regardless of priority in normal mode of operation. A packet on a given output can only be transmitted if the send grant is provided for that output.

There is also a Send Grant Per Priority Mode which allows the attached device to decide which packet priority is allowed to exit the switch. An antistreaming option prevents a defective attached device from keeping the send grant deasserted indefinitely. The send grant antistreaming option is programmable from 16 to 1024 packet cycles. When this condition occurs a send grant violation interrupt is raised to the attached Local Processor.

## 2.5.6 Output Queue Manager

The Output Queue Manager maintains a unique counter for each output queue, which indicates the total number of packets enqueued for that output, regardless of priority. The total number of packets in all four logical queues of one output is compared to the threshold value of a given priority, in order to provide flow control for

that output priority. All output counters are compared to those four thresholds once per sequencer cycle. If an output counter value is less than the threshold, the corresponding grant is set. Otherwise, it is cleared. Similarly, a counter keeps track of the total number of packets in Shared Memory.

## 2.5.7 Shared Memory

Four programmable Shared Memory thresholds are also provided, one for each priority. This counter is permanently compared to those four thresholds to generate the memory grants. An input ingress device is only allowed to transmit a packet when it has received both the output queue grants for the packet's destination and priority, and the memory grant for the packet priority. On the egress, a send grant is processed by each output port, either regardless of priority or per priority. The total number of packets in shared memory is compared to these threshold values for each priority, regardless of the output destination of the packets.

#### 2.6 Control Packets

Control packets are those packets transmitted to and received from a local processor. Packets can be received on any input port, and are passed one at a time to the local processor. A 32-position FIFO queue is provided for incoming Control packets for which priority is not assigned. Control packets can be transmitted by the local processor on any set of output ports. Control packets do not carry a priority and are always transmitted on one output before any other packet present in the shared memory. Due to the slow nature of the local processor access compared to the packet data traffic rate, control packet transmission is infrequent and does not affect the performance of high priority traffic.

Data Packets for which the bit map field (Header Bytes 1:4) is 0 are detected as Control Packets and are passed to the local processor via a dedicated queue. The first bit map byte of an incoming Control Packet is overwritten by the input port number on which the packet is received.

#### 2.7 Serial Host Interface

A Serial Host Interface (SHI) provides a serial interface to a local processor for programming application registers and accessing control packets. Refer to 7.1.2 SHI Interface Signals on page 107 for an SHI diagram.

#### 2.8 Serial Data Interface

A high speed serial interface is used to minimize the number of pins and to provide direct access over an extended distance. Two pairs of differential lines running at 500 Mb/s are provided for each master and slave LU stream. Therefore, each port is composed of four differential links. On the ingress side, the serial interface provides deserialization of one 2 ns bit stream into an 8 ns nibble stream. On the egress side, an 8 ns nibble stream is serialized into a 2 bit stream. For each stream, two nibbles are grouped to form a byte. Data is transmitted with a known clock such that only bit-phase alignment and packet alignment have to be performed. A picocode mechanism compensates for any skew between nibbles.

Link synchronization is provided by a training sequence of special Idle Packets, called Sync Packets. When sync packets are transmitted on a port, the receiving port can perform bit phase alignment of the incoming data, as well as packet alignment. The format of these Sync Packets is such that they are recognized by the receiving end as valid packets, and provide bit transitions on the physical line to allow for phase recovery. A sync packet LU is entirely composed of x'CC' bytes, except for the last byte which is x'33'.

Architecture PRS64G.fm.01

Page 18 of 134

August 31, 2000

One data byte is carried over two differential pairs. One pair carries all even numbered bits, and the other one all odd numbered bits. This converts the x'CC' sync packet bytes into alternating '0' and '1' transitions on the physical lines.

#### 2.9 Controllers

The internal controller is managed by a Sequencer, with a cycle value of 16 to 20 byte clocks (boundaries included). The island controller allows the handling of logical units (LUs) of 16 to 20 bytes (in steps of one byte), or 32 to 40 bytes (in steps of two bytes). An LU is the part of a packet that one island processes. The shared memory organization allows storage of 2048 LUs of 16 to 20 bytes, or 1024 LUs of 32 to 40 bytes.

# 2.10 Signaling

LU data is passed in and out of the island, one byte per clock cycle, for each input and output port, at a rate of 1 Gb/s. The switch header contains a packet qualifier and bit map.

The Qualifier byte is the first byte of a packet. It contains information about:

- Packet priority

- Packet identification (data, idle)

- Packet filtering support (see 2.10.4 Packet Filtering on page 20)

- · Best effort discard flag

- Parity bit over the entire header (packet qualifier plus bit map field)

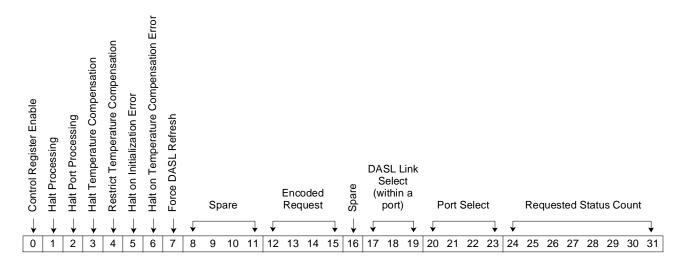

## 2.10.1 Input Header (Bit Map)

For incoming Data Packets, one to four bytes of the packet header provide the address of the packet destination, in the form of a bit map. Each bit of these bytes is associated with a logical output port, consisting of multiple (2, 4, or 8) physical ports, grouped together by either link paralleling or speed expansion into a unique logical port. In packet addressing, there is no difference between ports that are bundled together and individual ports. A bit set to '1' in the bit map indicates that the packet is to be routed to the corresponding logical port. This bit map field can point to multiple outputs.

## 2.10.2 Output Header (Output Queue Grant)

Depending on the header length, one to four bytes of outgoing packets carry the grant status of all output ports. This grant status is used by the receiver of the other adapter to make a decision on Data Packet transmission, according to the incoming flow control algorithm presented above. This grant status is referred to as an output logical queue grant (OQG).

On a given packet, the output queue grant field carries the status of all logical queues of the same priority. Ports bundled together represent a single logical queue. Consecutive packets carry the grant status for the different priorities, in a cyclic order. The synchronization of this cycle is provided by the packet numbering field (Flywheel priority field) contained in the outgoing Idle Packets.

#### 2.10.3 Service Packets

There are two sets of Service Packets - Time Fill Packets and Link Information Packets.

- Time Fill Packets are Idle Packets that contain LU CRC. They result from either a flow control situation or buffer emptiness. When no Data Packets are available on a port, Time Fill Packets are transmitted. During switchover process, Time Fill Packets can be "colored" (red or blue) to indicate that a buffer is empty of all priorities for a given switch plane. This is to maintain a continuous sequencing of the packet clock.

- Link Information Packets:

- Link Synchronization Packets are used as a training sequence for the serial links, and they contain the LU CRC.

- Yellow Idle Packets are used to test the continuity of a link (Link Liveness packets). The reception of a Yellow Idle Packet on a given input is logged into a register accessible by the local processor. Yellow Packets can only be transmitted by the local processor. There are three types of yellow packets: "Yellow1", "Yellow2", and "Yellow3".

## 2.10.4 Packet Filtering

A packet filtering function is provided on the switch island inputs in order to decide whether to receive packets for certain destinations. According to the packet filtering field in the qualifier byte, the incoming packet bit map is either logically ANDed (Red packets) with a specified mask, its complement (Red compliment packets) value, or not masked at all (Blue packets). For Data Packets, the color (red, red compliment, or blue) is used to determine how the bit map filter is applied to the bit map destination address. There is one mask for all 32 inputs.

# 2.11 Link Integrity

Link integrity is provided by a CRC field, placed in the last byte of all Idle Packet LUs. The 8-bit CRC is the checksum of all bits carried over a port since the previous Idle Packet ended. Thus, when multiple Data Packets are transmitted, followed at some time by an Idle Packet, the CRC of this Idle Packet covers all previous Data Packets. This provides a measure of the link quality for fault isolation.

#### 2.12 Receive Grants

A receive grant function is provided on device pins as a way to block packet reception for specific outputs. This function allows the implementation of packet lossless switchover for simple switch systems. It cannot be combined with the packet lossless switchover mechanism provided by filtering mechanisms. When a receive grant is asserted, reception of Data Packets in the corresponding output queue is enabled. When a receive grant is deasserted, no incoming packets are stored in the corresponding output queue, regardless of their bit map setting.

# 2.13 Look-Up Table

The Look-Up Table is a facility that allows shuffling of the bytes of outgoing packets. Only the first 16 bytes can be exchanged among each other or overwritten by one of the 16 bytes. One table is provided for all output ports. There is one table per island.

Architecture PRS64G.fm.01

Page 20 of 134

August 31, 2000

# 2.14 Side Communication Channel

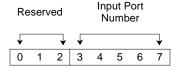

The 4-bit side communications channel (SCC) allows two-way communication between the adapters and the switch. It is assumed that the switching factor of this information is very low. On the path from the adapters to the switch, the information is transferred inband in the sixth byte of the Idle cells master logical unit. SCC information is carried in bits 0:3 and 4:7. When the switch receives the idle cell, it extracts and compares bits 0:3 and 4:7. If the value is the same, an internal register that holds the information is refreshed. The information is then made available through the read-only register. On the path from the switch to the adapters, the information is taken from four input pins (SCCIn 0:3).

The SCC information is inserted into all the outgoing idle cells; all the output ports send the same information. In order to guarantee a minimum time to propagate the information in case of information change, the switch automatically generates an idle cell to all ports on SCC input pins edge detection.

# 2.15 Expansion Modes

When multiple islands (of the same device or of two devices) are running in speed expansion, one is master and the others are slaves. The master island generates the byte stream containing the qualifier byte, bit map, and output queue grant. The master island also performs packet routing and queuing. The slave islands only receive data bytes, and do not perform any packet routing and queuing. The address of packets in shared memory is provided by the master to the slave on a special input address bus. Furthermore, the slave island's internal sequencers are synchronized on the master sequencer in order to transmit the LUs at the same time on a given port.

## 2.15.1 External Speed Expansion

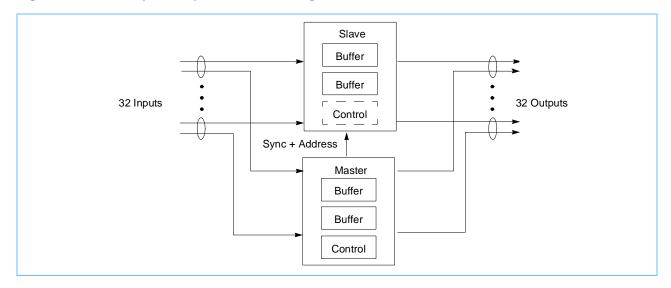

Speed expansion allows multiple devices to be connected in parallel to increase the port speed while keeping the number of ports constant, as shown in the Speed Expansion Block Diagram below.

When two devices are in external speed expansion, ports of the same number are grouped together.

Only two devices can be combined in external speed expansion.

Figure 4: External Speed Expansion Block Diagram

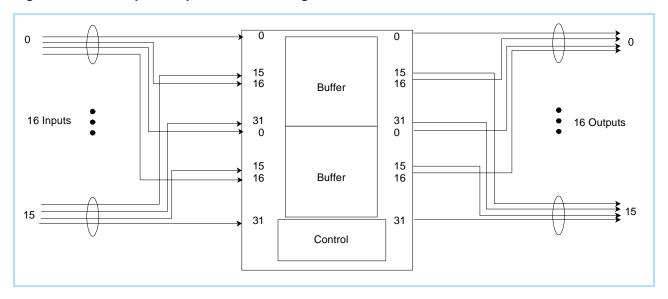

## 2.15.2 Internal Speed Expansion

Ports of one island can also be paired to double the port speed while reducing the number of input and output ports to 16. Each pair of ports consists of one master port and one slave port, which have exactly the same functions as the ports of master or slave islands in external speed expansion.

Figure 5: Internal Speed Expansion Block Diagram

**Table 2: Speed Expansion Shared Memory Buffering Capacities**

| Speed Expansion Mode                      | Switch<br>Configuration | Gb/s port | Packet Length (bytes) | LU Size<br>(bytes) | Buffering<br>(packets) | Speed<br>Expansion<br>Factor |  |

|-------------------------------------------|-------------------------|-----------|-----------------------|--------------------|------------------------|------------------------------|--|

| Single device, no internal speed expan-   | 32 x 32                 | 2         | 64 - 80               | 32 - 40            | 1 K                    | 0                            |  |

| sion                                      | 32 X 32                 | 2         | 32 - 40               | 16 - 20            | 2 K                    | 2                            |  |

| Single device, with internal speed expan- | 16 x 16                 | 4         | 64 - 80               | 16 - 20            | 1 K                    | 4                            |  |

| sion                                      | 10 X 10                 | 4         | 128 - 160             | 32 - 40            | 512                    | 4                            |  |

| Two devices speed expanded,               | 32 x 32                 | 4         | 64 - 80               | 16 - 20            | 2 K                    | 4                            |  |

| no internal speed expansion               | 32 X 32                 | 4         | 128 - 160             | 32 - 40            | 1 K                    | 4                            |  |

| Two devices speed expanded,               | 16 v 16                 |           | 128 - 160             | 16 - 20            | 1 K                    | 0                            |  |

| no internal speed expansion               | 16 x 16                 | 8         | 256 - 320             | 32 - 40            | 512                    | 8                            |  |

**Note**: In each case, the LU size seen by one island (either the master or the slave island of one device) is equal to the packet length divided by the speed expansion factor (port speed divided by the island port speed of one Gb/s).

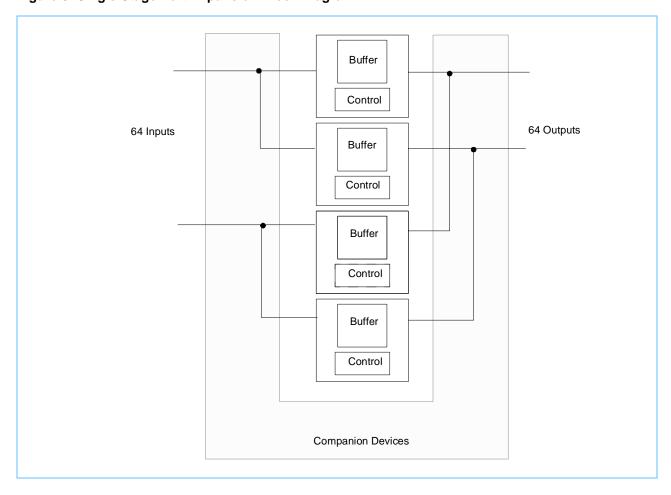

## 2.15.3 Port Expansion

Port expansion allows multiple islands to be interconnected in parallel, in a single stage, in order to increase the number of physical ports, while keeping the port speed constant.

An external function must be provided to:

• Duplicate incoming packets and insert the correct bit map used by each island

· Merge traffic from different islands

Port expansion can be combined with speed expansion (internal and/or external) to increase port speed and the number of ports at the same time.

Figure 6: Single Stage Port Expansion Block Diagram

## 2.15.4 Physical Port Bundling

Link paralleling is the grouping of physical ports to form a unique logical port. The only difference between the ports is in the packet ordering. For packets belonging to the same flow (i.e. input/output/priority combination), packet sequence must be maintained through the switch fabric, and packet ordering must be guaranteed when transmitting and receiving packets. Packet order is based on time of transmission. Packets of ports of a common link are sent one after another, with an offset of four clock cycles (32 ns). Therefore, a port 1 packet sent 32 ns after a packet on port 0 comes after the packet on port 0 in the sequence order.

Link paralleling of four ports is only possible in the following combinations: (0,1,2,3), (4,5,6,7), (8,9,10,11), (12,13,14,15), (16,17,18,19), (20,21,22,23), (24,25,26,27), and (28,29,30,31). Not all groups have to be used at the same time. This is configurable via the Input and Output Link Paralleling field in *5.6.1 Configuration 0 Register* on page 78.

The figure below shows output link paralleling of ports (0,1,2,3), with a unique link list built in OQ 0. When sending a packet to output link 0, only the output 0 bit is set in the bit map. Addresses from OQ 0 are then distributed to the output ports 0,1,2, and 3: The OQ reads from OQ 0 when the internal sequencer indicates to process output 0, 1, 2, or 3.

**Table 3: Link Paralleling Block Diagram**

Link Paralleling is a logical grouping of ports. Each port or link transports independent packets. Packet ordering is such that a packet carried on a port of lower number is processed before a packet carried at the same time on a port of a higher number (for instance, if ports 0, 1, 2, and 3 are linked, a packet on port 0 comes, and thus is processed (enqueued), before packets on port 1, 2, or 3).

# 3. Functional Description

# 3.1 Logical Interface

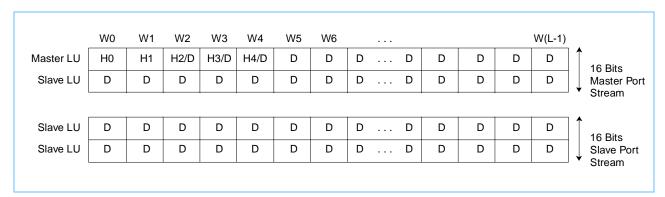

As described in 2.15 Expansion Modes on page 21, the switch consists of two switch islands running in speed expansion. Data Packets are carried over an input or output port in two byte streams of one Gb/s each, one to or from the master island, and the other to or from the slave island. Each byte stream carries Logical Units (LU). Depending on the expansion mode and packet length, an LU has a length of 16 to 20 bytes or 32 to 40 (in increments of two) bytes.

As represented in the figure below, the master LU always carries the packet routing information, or header bytes, indicated by H0, H1 through H4 (depending on the header length). Depending on the speed expansion mode and the number of ports operating in link paralleling, the number of addressable output ports can be 8, 16, 24, or 32.

Figure 7: Packet Format 2 Gb/s Port

|           | W0 | W1 | W2   | W3   | W4   | W5 | W6 |   |       |   |   |   | W(L-1) |           |

|-----------|----|----|------|------|------|----|----|---|-------|---|---|---|--------|-----------|

| Master LU | H0 | H1 | H2/D | H3/D | H4/D | D  | D  | D | <br>D | D | D | D | D      | 16 Bits   |

| Slave LU  | D  | D  | D    | D    | D    | D  | D  | D | <br>D | D | D | D | D      | ↓ TO Bits |

|           |    |    |      |      |      |    |    |   |       |   |   |   |        | •         |

When running in either internal or external speed expansion, two ports are grouped to form a 4 Gb/s port. Depending on the port and chip configuration, a 2 Gb/s port can run either as a master port or a slave port:

- The master port is composed of two streams, one master, which carries the packet header information and data bytes, and one slave, which carries data bytes only.

- The slave port is composed of two slave streams, which carry data bytes only.

Figure 8: Packet Format for 4 Gb/s Port

The LUs of a packet are always transmitted or received at the same time on both streams of a port. The LUs of successive packets are transported one after the other, with no gap between packets.

Figure 9: Packet Format for 16 Gb/s Port

| Master LU | H0 | H1 | H2/D | H3/D | H4/D | D | D | D |         | D | D | D | D | D |                    |

|-----------|----|----|------|------|------|---|---|---|---------|---|---|---|---|---|--------------------|

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | 32 Bits            |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | Physic<br>Port 0   |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | (4K)<br>↓ (K = 0:  |

| Master LU | H0 | H1 | H2/D | H3/D | H4/D | D | D | D |         | D | D | D | D | D | ] ↑                |

| Slave LU  | D  | D  | D    | D    | D    |   | D | D |         | D | D | D | D | D |                    |

|           |    |    |      |      |      |   |   |   | • • •   |   |   |   |   |   | 32 Bits            |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D | • • • • | D | D | D | D | D | Physical Port 1    |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | 4(K+1)<br><b>↓</b> |

| Master LU | H0 | H1 | H2/D | H3/D | H4/D | D | D | D |         | D | D | D | D | D | ] ↑                |

| Slave LU  | D  |    |      |      | D    |   | D | D |         |   |   |   |   |   | -                  |

| Slave LU  | U  | D  | D    | D    | U    | D | U | ט |         | D | D | D | D | D | 32 Bits            |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | Physic<br>Port 2   |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | 4(K+2)<br><b>↓</b> |

| Master LU | H0 | H1 | H2/D | H3/D | H4/D | D | D | D |         | D | D | D | D | D | ] ↑                |

|           |    |    |      |      |      |   |   |   | • • • • |   |   |   |   |   | -                  |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D | • • • • | D | D | D | D | D | 32 Bits            |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | Physical Port 3    |

| Slave LU  | D  | D  | D    | D    | D    | D | D | D |         | D | D | D | D | D | 4(K+3)             |

In the case of link paralleling the internal sequencer of device processes one physical port at a time, there is an interval of 32 (4 clock cycles x 8ns)ns between each physical port of a logical port. In order to guarantee that packets are received and processed according to their order of arrival, they must be transmitted to the input physical ports with the same pattern as the physical port processing (offset of 32 ns between ports). This is the responsibility of the attached device.

# 3.2 Physical Interface

Within the device, an LU is transported in a stream of bytes at 125 Mb/s. Externally, it is transported over two bit streams of 500 Mb/s each. At the device-pin level, each bit stream interface is differential and complies with the JEDEC JESD8-6 standard (HSTL).

Data bits are transferred across devices at a known frequency and no companion clock is required. However, bit-phase alignment is performed during the link synchronization phase.

The interface between the 8 ns and the 2 ns domains is handled by a data line interface, the Data Aligned Serial Link (DASL).

Functional Description Page 26 of 134

- On the input side, the DASL deserializes the two bit streams into one byte stream. It also performs the link synchronization through training sequence to allow bit phase alignment and packet alignment. Afterwards, it automatically compensates for any variation in temperature, voltage, etc.

- On the output side, the DASL serializes the byte stream into two bit streams.

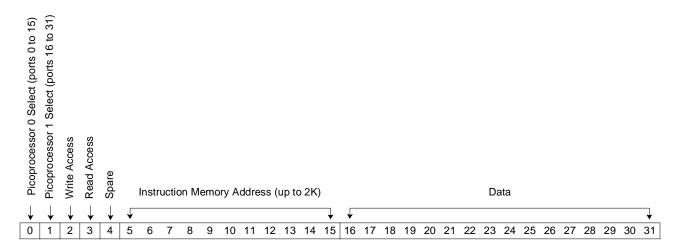

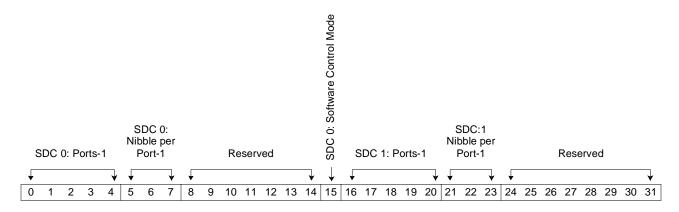

Two internal picoprocessors (shared DASL controller: SDC) perform the synchronization of all lines on all ports. One is dedicated to ports 0 to 15 and the other to ports 16 to 31. A synchronization algorithm running on the picoprocessor performs the bit-phase alignment and packet alignment of all ports during the synchronization phase (see *6.3 DASL Initialization and Operation* on page 100). The synchronization algorithm is downloaded into an internal instruction memory and is delivered along with the device.

During serialization and deserialization, a one byte stream is split into two bit streams, one carrying the even bits; the other the odd bits. A port consists of four differential pairs. The information and bit order that each pair carries is shown in the table below.

Table 4: Physical Bit Organization of a Port

| Differential Pair      | Information Carried                              | Bit Order                         |

|------------------------|--------------------------------------------------|-----------------------------------|

| Data_0_Q and Data_0_QN | even number bits of the <b>slave</b> byte stream | b0 b2 b4 b6 of <b>slave</b> byte  |

| Data_1_Q and Data_1_QN | odd number bits of the <b>slave</b> byte stream  | b1 b3 b5 b7 of <b>slave</b> byte  |

| Data_2_Q and Data_2_QN | even number bits of the master byte stream       | b0 b2 b4 b6 of <b>master</b> byte |

| Data_3_Q and Data_3_QN | odd number bits of the <b>master</b> byte stream | b1 b3 b5 b7 of <b>master</b> byte |

This bit grouping guarantees bit transitions to perform the phase alignment during synchronization on SYNC packets.

# 3.3 Packet Type

A packet can be one of the following types:

- · A Data Packet that contains user data to be switched from input to output.

- A Control Packet that is used to communicate with the local processor.

- An Idle Packet that does not contain user data. Idle Packets are sent on a link when no Data Packets are available, or to perform link synchronization.

- Link Information Packet: Yellow Idle used to test the continuity of the link.

#### 3.3.1 Data Packets and Control Packets

Data packets carry user data and Control packets carry information for local processor communication. *Figure 7: Packet Format 2 Gb/s Port* on page 25 shows the format of a Data and Control packet without speed expansion. A packet consists of 16-bit words, divided into a master stream and a slave stream.

Figure 8: Packet Format for 4 Gb/s Port on page 25 shows the format of a data or a control packet with speed expansion, either internal or external. In those configurations, the packet is transported over two different ports, either in the same device or in separate devices, in four LUs. The master port receives the master LU and a slave LU, and the slave port receives two slave LUs.

Data packets have a priority that ranges from '0' (highest) to '3' (lowest). In addition, they also carry filtering (color) information used for switchover support, and a "best effort discard" flag.

Control Packets do not have priority.

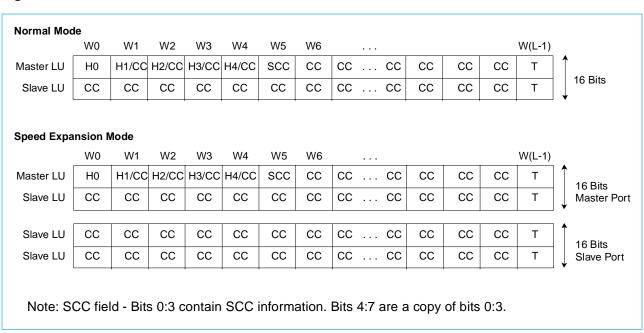

#### 3.3.2 Idle Packets

The figure below shows the format of an egress Idle Packet with and without speed expansion. In normal mode, the format is identical to the Data Packet format for 2 Gb/s ports, except that an Idle packet contains two trailer bytes in the last word of the packet. The ingress Idle packet has the same content as the egress Idle Packet except byte H1 through H4 contain 'CC'.

Speed expansion mode is similar to the Data packet format for 4 Gb/s ports, except for the trailer bytes at the end of the packet. The ingress Idle packet has the same content as the egress packet except bytes H1 through H4 contain 'CC'.

Figure 10: Idle Packet Format

Like Data Packets, Idle Packets also carry color information. However, in this case the color (filtering) information is for signaling (such as liveness messages, or to identify link synchronization packets, called Sync packets), in addition to switchover support.

# 3.3.3 Sync Packets

Sync packets are special types of Idle Packets, which allow link synchronization by providing bit transition and packet delineation.

The bit organization by the physical interface provides on a given differential pair, a sequence of 'A', followed by a '5'. This bit sequence provides the necessary bit transition while the 'A to 5' transition allows for packet delineation.

# 3.4 Header Format

# 3.4.1 Header Byte H0 - Packet Qualifier

Table 5: H0 for "TimeFill" packets (Idle Packets)

| Packet Type      | Bit Position         |        |   |   |         |                     |  |  |  |  |

|------------------|----------------------|--------|---|---|---------|---------------------|--|--|--|--|

|                  | 0                    | 1      | 2 | 3 | 4 and 5 | 6 and 7             |  |  |  |  |

|                  | FlyWheel<br>Extender | Parity | 0 | 0 | Color   | Grant Priority bits |  |  |  |  |

| Blue Idle Packet | FWE                  | r      | 0 | 0 | 00      | gg                  |  |  |  |  |

| Red Idle Packet  | FWE                  | r      | 0 | 0 | 01      | gg                  |  |  |  |  |

r Even parity bit on entire header.

Table 6: H0 for "Synchronization" Packets

| Packet Type            | Bit Position |   |   |   |   |   |   |   |  |  |

|------------------------|--------------|---|---|---|---|---|---|---|--|--|

| racket type            | 0            | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |  |

| Synchronization Packet | 1            | 1 | 0 | 0 | 1 | 1 | 0 | 0 |  |  |

Table 7: H0 for "Yellow" Packets

| Packet Type         | Bit Position |   |   |   |   |   |   |   |  |  |

|---------------------|--------------|---|---|---|---|---|---|---|--|--|

| r acker type        | 0            | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |  |

| YellowPacket Type 1 | 0            | r | 0 | 0 | 1 | 0 | х | х |  |  |

| YellowPacket Type 2 | 0            | r | 0 | 0 | 1 | 1 | х | х |  |  |

| YellowPacket Type 3 | 1            | r | 0 | 0 | 1 | 0 | х | Х |  |  |

r Even parity bit on entire header.

**Table 8: H0 for Data Packet and Control Packet** (Bits 2 and/or 3 ≠ 0)

|                                    | Bit Position |               |                   |                   |                        |                 |                 |  |  |

|------------------------------------|--------------|---------------|-------------------|-------------------|------------------------|-----------------|-----------------|--|--|

| Packet Type                        | 0            | 1             | 2                 | 3                 | 4                      | 5               | 6 and 7         |  |  |

|                                    | EBM<br>(1)   | Parity<br>(1) | Active Bit<br>(1) | Backup Bit<br>(1) | Best Effort<br>Bit (1) | Reserved<br>(1) | Priority<br>(2) |  |  |

| Red compliment Data/Control Packet | х            | r             | 0                 | 1                 | be                     | х               | pp              |  |  |

Key:

EBM extended bit map x value = '0' or '1'

r even parity bit on entire header

be best effort pp packet priority

gg Value of grant sync bits (ignored for received packets - value = '00'. Grant synchronization is a flywheel mechanism that allows the device to indicate to the attached chip the priority level of the output queue grant information contained in header bytes H1 through H4.

x x value = 0 or 1.

**Table 8: H0 for Data Packet and Control Packet** (Bits 2 and/or 3 ≠ 0)

| Packet Type                       | Bit Position |               |                   |                   |                        |                 |                 |  |  |  |

|-----------------------------------|--------------|---------------|-------------------|-------------------|------------------------|-----------------|-----------------|--|--|--|

|                                   | 0            | 1             | 2                 | 3                 | 4                      | 5               | 6 and 7         |  |  |  |

|                                   | EBM<br>(1)   | Parity<br>(1) | Active Bit<br>(1) | Backup Bit<br>(1) | Best Effort<br>Bit (1) | Reserved<br>(1) | Priority<br>(2) |  |  |  |

| Red direct<br>Data/Control Packet | х            | r             | 1                 | 0                 | be                     | х               | pp              |  |  |  |

| Blue<br>Data/Control Packet       | х            | r             | 1                 | 1                 | be                     | х               | pp              |  |  |  |

<u>Key</u>:

EBM extended bit map x value = '0' or '1'

r even parity bit on entire header

be best effort pp packet priority

# Table 9: H0 Fields

| Field Name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Settings                                                                                                                                                                                                                                           |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parity Bit                   | The parity bit is even parity calculated on the entire packet header including the reserved fields. Even parity is such that the resulting number of '1' in the packet header is even. This ensures that the SYNC cell has a valid header.                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                    |

| Reserved Bits                | Reserved bits pass through the device unmodified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                    |

| Data Packet<br>Priority bits | The priority of a Data packet distinguishes between four levels of priority. When the packet is a Control packet, it is always transmitted before any other Data packets, and the priority field is ignored.  Data Packets with higher priority will always be transmitted before those with lower priorities. There is a weighted cyclical mechanism based on a credit table which makes it possible to give precedence to a lower priority packet on a per port basis.                                                                                                                                 | '00' Highest priority '01' Medium - High '10' Medium - Low '11' Lowest priority                                                                                                                                                                    |

| Active and<br>Backup Bits    | The Active and Backup bits are used to determine how the Bit Map Filter Mask is applied to the Bit Map Destination Address (header bytes H1 through H4) and to determine the traffic type (Red or Blue) of Data Packets or Idle Packets.  The Bit Map Filter is a programmable register. The resulting masked destination bit map is used by the device to route the packets to the appropriate destination(s), or to ignore the packet if the resulting bit map is all zeros. Control packet detection is performed before the Bit Map Filter is applied to the bit map contained in the packet header. | Active/ Backup Bit Map FilterColor '00' Idle Packetn/a '01' Packet bit map is bit wiseRed ANDed with bit wise complement of bit map filter '10' Packet bit map is bit wiseRed ANDed with bit map filter '11' Packet bit map is usedBlue unfiltered |

| Best Effort<br>Discard Bit   | Incoming packets with the "best effort discard" bit set will be dropped by the device when a threshold of four up/down counters (one per priority) representing the inverse of the switch speedup compared to the attached line is reached. By monitoring the packets destined to an output queue it is possible to determine up to which best effort priority is to be discarded to ease the congestion at the convergence of the output port.                                                                                                                                                          | '01' Packet bit map is bit wise ANDed with bit wise complement of bit map filter                                                                                                                                                                   |

Table 9: H0 Fields (Continued)

| Field Name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                         | Settings                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| gg Bits                   | The grant priority bits (gg) are defined only for Idle Packets transmitted by the switch. They are used to synchronize the grant priority fly wheel of the attached device. For received packets, this field is not examined (its value is 'xx'). These bits encode the priority of the inband output queue grant information stored in header bytes H1 through H4. The coding of bits gg is identical to the Data packet priority. | '00' Highest priority '01' Medium - High '10' Medium - Low '11' Low priority                                                                                                                                                                                                                                                                                                                                |  |  |  |

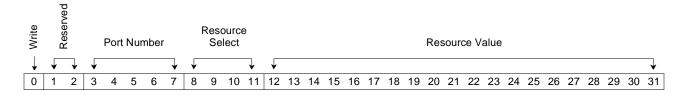

| EBM: Extended<br>BitMap   | The purpose of this bit is to address in one cell header, half of the ports, in order to reduce the bitmap field length.  When the "Extended bitmap function" is enabled, PRS64G will address 16 or 32 ports with a bitmap field of respectively 1 or 2 bytes.                                                                                                                                                                      | <ul> <li>'0' The bitmap field addresses the ports 0 to 7 for a 1 byte bitmap and the ports 0 to 15 for a 2 byte bitmap.</li> <li>'1' The bitmap field addresses the ports 8 to 15 for a 1 byte bitmap and the ports 16 to 31 for a 2 byte bitmap.</li> </ul>                                                                                                                                                |  |  |  |