#### 16Mx64 One Bank Unbuffered DDR SDRAM Module

#### **Features**

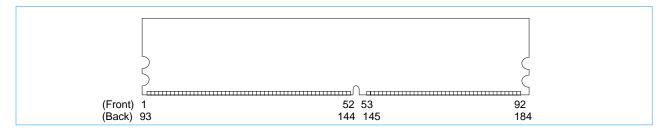

- 184-Pin Unbuffered 8-Byte Dual In-Line Memory Module

- 16Mx64 Double Data Rate (DDR) SDRAM DIMM (16M x 8 SDRAMs)

- · Performance:

|                  |                    | PC1600 | PC2100 | Units |

|------------------|--------------------|--------|--------|-------|

| DIMM CAS Latency |                    | 2      | 2.5    |       |

| $f_{CK}$         | Clock Frequency    | 100    | 133    | MHz   |

| $t_{CK}$         | Clock Cycle        | 10     | 7.5    | ns    |

| $f_{DQ}$         | DQ Burst Frequency | 200    | 266    | MHz   |

- Intended for 100 MHz and 133 MHz applications

- Inputs and outputs are SSTL-2 compatible

- $V_{DD} = 2.5 \text{Volt} \pm 0.2$ ,  $V_{DDO} = 2.5 \text{Volt} \pm 0.2$

- Single Pulsed RAS interface

- SDRAMs have four internal banks for concurrent operation

- · Module has one physical bank

- DRAM D<sub>LL</sub> aligns DQ and DQS transitions with clock transitions. Also aligns QFC transitions with clock during Read cycles

- · Differential clock inputs

- Data is read or written on both clock edges

- Address and control signals are fully synchronous to positive clock edge

- Programmable Operation:

- DIMM CAS Latency: 2, 2.5

- Burst Type: Sequential or Interleave

- Burst Length: 2, 4, 8

- Operation: Burst Read and Write

- Auto Refresh (CBR) and Self Refresh Modes

- Automatic and controlled precharge commands

- 12/10/2 Addressing (row/column/bank)

- 15.6 µs Max. Average Periodic Refresh Interval

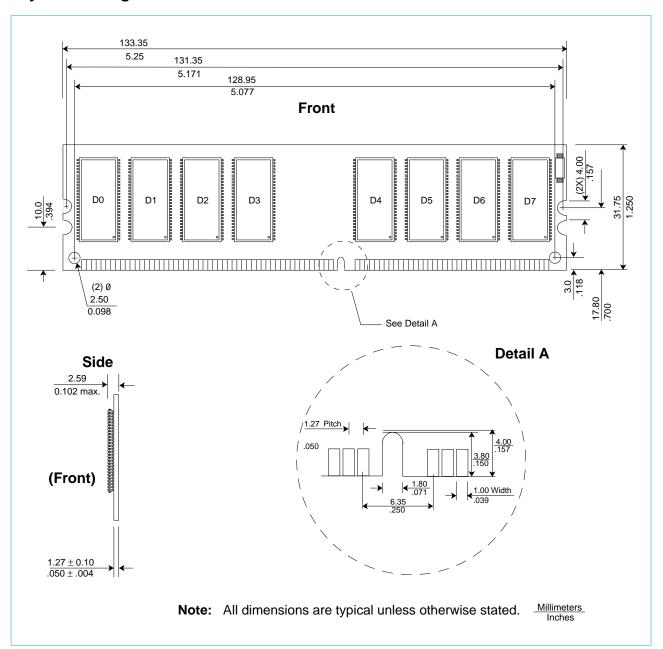

- Card size: 5.25" x 0.102" x 1.25"

- · Gold contacts

- SDRAMs in 66-pin TSOP-II Package

- Serial Presence Detect

#### **Description**

IBMB6N16644JGA is an unbuffered 184-Pin Double Data Rate (DDR) Synchronous DRAM Dual In-Line Memory Module (DIMM), organized as a one-bank high-speed memory array. The 16Mx64 module is a single-bank DIMM that uses eight 16Mx8 DDR SDRAMs in 400 mil TSOP packages. The DIMM achieves high-speed data transfer rates of up to 266 MHz.

The DIMM is intended for use in applications operating from 100 MHz to 133 MHz clock speeds with data rates of 200 to 266 MHz.

Clock enable CKE0 controls all devices on the DIMM.

Prior to any access operation, the device  $\overline{\text{CAS}}$  latency and burst type/length/operation type must

be programmed into the DIMM by address inputs A0-A11 and I/O inputs BA0 and BA1 using the mode register set cycle.

These DIMMs are manufactured using raw cards developed for broad industry use as reference designs. The use of these common design files minimizes electrical variation between suppliers.

The DIMM uses serial presence detects implemented via a serial EEPROM using the two-pin IIC protocol. The first 128 bytes of serial PD data are programmed and locked during module assembly. The last 128 bytes are available to the customer.

All IBM 184 DDR SDRAM DIMMs provide a highperformance, flexible 8-byte interface in a 5.25" long space-saving footprint.

#### **Card Outline**

# **Pin Description**

| CK0, <u>CK</u> 0<br>CK1, <u>CK</u> 1<br>CK2, CK2 | Differential Clock Inputs      | DQ0 - DQ63               | Data Input/Output                           |

|--------------------------------------------------|--------------------------------|--------------------------|---------------------------------------------|

| CKE0                                             | Clock Enable                   | DQS0-DQS7,<br>DQS9-DQS16 | Bidirectional data strobes                  |

| RAS                                              | Row Address Strobe             | $V_{DD}$                 | Power (2.5V)                                |

| CAS                                              | Column Address Strobe          | $V_{DDQ}$                | Supply voltage for DQs (2.5V)               |

| WE                                               | Write Enable                   | V <sub>SS</sub>          | Ground                                      |

| ₹0                                               | Chip Select                    | NC                       | No Connect                                  |

| A0 - A9, A11                                     | Address Inputs                 | SCL                      | Serial Presence Detect Clock Input          |

| A10/AP                                           | Address Input/Autoprecharge    | SDA                      | Serial Presence Detect Data Input/Output    |

| BA0, BA1                                         | SDRAM Bank Address Inputs      | SA0-SA2                  | Serial Presence Detect Address Inputs       |

| V <sub>REF</sub>                                 | Ref. Voltage for SSTL_2 inputs | V <sub>DDSPD</sub>       | Serial EEPROM positive power supply (2.5 V) |

# 184-Pin DDR SDRAM DIMM Pin Assignments

|       | Side (left side 1 - 52,<br>ht side 53 - 92) |       | de (left side 93-144,<br>nt side 145-184) |      | Side (left side 1 - 52,<br>ht side 53 - 92) |       | de (left side 93 -144<br>t side 145 -184) |

|-------|---------------------------------------------|-------|-------------------------------------------|------|---------------------------------------------|-------|-------------------------------------------|

| Pin # | x64 Non-Parity                              | Pin # | x64 Non-Parity                            | Pin# | x64 Non-Parity                              | Pin # | x64 Non-Parity                            |

| 1     | VREF                                        | 93    | VSS                                       | 48   | A0                                          | 140   | NC                                        |

| 2     | DQ0                                         | 94    | DQ4                                       | 49   | NC                                          | 141   | A10                                       |

| 3     | VSS                                         | 95    | DQ5                                       | 50   | VSS                                         | 142   | NC                                        |

| 4     | DQ1                                         | 96    | VDDQ                                      | 51   | NC                                          | 143   | VDDQ                                      |

| 5     | DQS0                                        | 97    | DQS9                                      | 52   | BA1                                         | 144   | NC                                        |

| 6     | DQ2                                         | 98    | DQ6                                       | '    | KEY                                         |       | KEY                                       |

| 7     | VDD                                         | 99    | DQ7                                       | 53   | DQ32                                        | 145   | VSS                                       |

| 8     | DQ3                                         | 100   | VSS                                       | 54   | VDDQ                                        | 146   | DQ36                                      |

| 9     | NC                                          | 101   | NC                                        | 55   | DQ33                                        | 147   | DQ37                                      |

| 10    | RESET                                       | 102   | NC                                        | 56   | DQS4                                        | 148   | VDD                                       |

| 11    | VSS                                         | 103   | NC                                        | 57   | DQ34                                        | 149   | DQS13                                     |

| 12    | DQ8                                         | 104   | VDDQ                                      | 58   | VSS                                         | 150   | DQ38                                      |

| 13    | DQ9                                         | 105   | DQ12                                      | 59   | BA0                                         | 151   | DQ39                                      |

| 14    | DQS1                                        | 106   | DQ13                                      | 60   | DQ35                                        | 152   | VSS                                       |

| 15    | VDDQ                                        | 107   | DQS10                                     | 61   | DQ40                                        | 153   | DQ44                                      |

| 16    | CK1                                         | 108   | VDD                                       | 62   | VDDQ                                        | 154   | RAS                                       |

| 17    | CK1                                         | 109   | DQ14                                      | 63   | WE                                          | 155   | DQ45                                      |

| 18    | VSS                                         | 110   | DQ15                                      | 64   | DQ41                                        | 156   | VDDQ                                      |

| 19    | DQ10                                        | 111   | NC                                        | 65   | CAS                                         | 157   | <u></u> \$0                               |

| 20    | DQ11                                        | 112   | VDDQ                                      | 66   | VSS                                         | 158   | NC                                        |

| 21    | CKE0                                        | 113   | NC                                        | 67   | DQS5                                        | 159   | DQS14                                     |

| 22    | VDDQ                                        | 114   | DQ20                                      | 68   | DQ42                                        | 160   | VSS                                       |

| 23    | DQ16                                        | 115   | NC                                        | 69   | DQ43                                        | 161   | DQ46                                      |

| 24    | DQ17                                        | 116   | VSS                                       | 70   | VDD                                         | 162   | DQ47                                      |

| 25    | DQS2                                        | 117   | DQ21                                      | 71   | NC                                          | 163   | NC                                        |

| 26    | VSS                                         | 118   | A11                                       | 72   | DQ48                                        | 164   | VDDQ                                      |

| 27    | A9                                          | 119   | DQS11                                     | 73   | DQ49                                        | 165   | DQ52                                      |

| 28    | DQ18                                        | 120   | VDD                                       | 74   | VSS                                         | 166   | DQ53                                      |

| 29    | A7                                          | 121   | DQ22                                      | 75   | CK2                                         | 167   | NC                                        |

| 30    | VDDQ                                        | 122   | A8                                        | 76   | CK2                                         | 168   | VDD                                       |

| 31    | DQ19                                        | 123   | DQ23                                      | 77   | VDDQ                                        | 169   | DQS15                                     |

| 32    | A5                                          | 124   | VSS                                       | 78   | DQS6                                        | 170   | DQ54                                      |

| 33    | DQ24                                        | 125   | A6                                        | 79   | DQ50                                        | 171   | DQ55                                      |

| 34    | VSS                                         | 126   | DQ28                                      | 80   | DQ51                                        | 172   | VDDQ                                      |

| 35    | DQ25                                        | 127   | DQ29                                      | 81   | VSS                                         | 173   | NC                                        |

| 36    | DQS3                                        | 128   | VDDQ                                      | 82   | VDDID                                       | 174   | DQ60                                      |

| 37    | A4                                          | 129   | DQS12                                     | 83   | DQ56                                        | 175   | DQ61                                      |

| 38    | VDD                                         | 130   | A3                                        | 84   | DQ57                                        | 176   | VSS                                       |

| 39    | DQ26                                        | 131   | DQ30                                      | 85   | VDD                                         | 177   | DQS16                                     |

| 40    | DQ27                                        | 132   | VSS                                       | 86   | DQS7                                        | 178   | DQ62                                      |

| 41    | A2                                          | 133   | DQ31                                      | 87   | DQ58                                        | 179   | DQ63                                      |

| 42    | VSS                                         | 134   | NC                                        | 88   | DQ59                                        | 180   | VDDQ                                      |

| 43    | A1                                          | 135   | NC                                        | 89   | VSS                                         | 181   | SA0                                       |

| 44    | NC                                          | 136   | VDDQ                                      | 90   | NC                                          | 182   | SA1                                       |

| 45    | NC                                          | 137   | CK0                                       | 91   | SDA                                         | 183   | SA2                                       |

| 46    | VDD                                         | 138   | CK0                                       | 92   | SCL                                         | 184   | VDDSPD                                    |

| 47    | NC                                          | 139   | VSS                                       |      |                                             | 11    |                                           |

# **Ordering Information**

| Part Number           | Organization | Speed  | SDRAM<br>CAS<br>Latency | Leads | Dimension                | Power<br>V <sub>DD</sub> /V <sub>DDQ</sub> |

|-----------------------|--------------|--------|-------------------------|-------|--------------------------|--------------------------------------------|

| IBMB6N16644JGA - 8NT  | 4004-04      | PC1600 | 2                       | Gold  | E 05" :: 4 05" :: 0 400" | 0.5.1/0.5.1/                               |

| IBMB6N16644JGA - 75NT | 16Mx64       | PC2100 | 2.5                     |       | 5.25" x 1.25" x 0.102"   | 2.5 V/2.5 V                                |

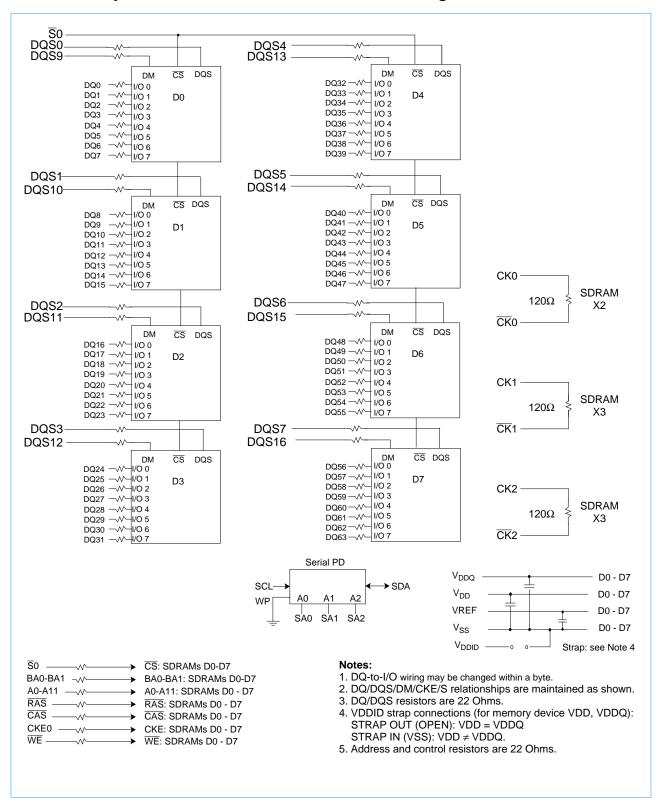

#### x64 Non-Parity DDR Unbuffered SDRAM DIMM Block Diagram (1 Bank, x8 DDR SDRAMs)

# **Input/Output Functional Description**

| Symbol                      | Туре   | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK0, CK1, CK2               | (SSTL) | Positive<br>Edge | The positive line of the differential pair of system clock inputs which drives the input to the on-<br>DIMM PLL. All the DDR SDRAM address and control inputs are sampled on the rising edge of<br>their associated clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CK0, CK1, CK2               | (SSTL) | Negative<br>Edge | The negative line of the differential pair of system clock inputs which drives the input to the on-DIMM PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CKE0                        | (SSTL) | Active<br>High   | Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <u>\$</u> 0                 | (SSTL) | Active<br>Low    | Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RAS, CAS, WE                | (SSTL) | Active<br>Low    | When sampled at the positive rising edge of the clock, $\overline{\text{CAS}}$ , $\overline{\text{RAS}}$ , and $\overline{\text{WE}}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub>            | Supply |                  | Reference voltage for SSTL-2 inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{DDQ}$                   | Supply |                  | Isolated power supply for the DDR SDRAM output buffers to provide improved noise immunity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BA0,1                       | (SSTL) | _                | Selects which SDRAM bank of four is activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0 - A9, A11,<br>A10/AP     | (SSTL) | _                | During a Bank Activate command cycle, A0-A11 defines the row address (RA0-RA11) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) when sampled at the rising clock edge. In addition to the column address, AP is used to invoke autoprecharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If AP is low, autoprecharge is disabled.  During a Precharge command cycle, AP is used in conjunction with BA0, BA1 to control which bank(s) to precharge. If AP is high, all banks will be precharged regardless of the state of BA0 or BA1. If AP is low, BA0 and BA1 are used to define which bank to precharge. |

| DQ0 - DQ63                  | (SSTL) | _                | Data Input/Output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DQS0 - DQS7<br>DQS9 - DQS16 | (SSTL) | _                | Data strobes: Output with read data, input with write data. Edge aligned with read data, centered on write data. Used to capture write data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{DD}, V_{SS}$            | Supply |                  | Power and ground for the DDR SDRAM input buffers and core logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SA0 - 2                     |        | _                | These signals are tied at the system planar to either $V_{SS}$ or $V_{DD}$ to configure the serial SPD EEPROM address range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDA                         |        | _                | This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be connected from the SDA bus line to $V_{DD}$ to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCL                         |        | _                | This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus time to $V_{DD}$ to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DDSPD</sub>          | Supply |                  | Serial EEPROM positive power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                             |        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# Serial Presence Detect (Part 1 of 2)

| Byte # | Description                                                   |         | SPD Entry Value                   | Serial PD Data Entry<br>(Hexadecimal) | Notes |

|--------|---------------------------------------------------------------|---------|-----------------------------------|---------------------------------------|-------|

| 0      | Number of Serial PD Bytes Written during Production           | 128     | 80                                |                                       |       |

| 1      | Total number of bytes in Serial PD Device                     |         | 256                               | 08                                    |       |

| 2      | Fundamental Memory Type                                       |         | SDRAM DDR                         | 07                                    |       |

| 3      | Number of Row Addresses on Assembly                           |         | 12                                | 0C                                    |       |

| 4      | Number of Column Addresses on Assembly                        |         | 10                                | 0A                                    |       |

| 5      | Number of Physical Banks on DIMM                              |         | 1                                 | 01                                    |       |

| 6-7    | Data Width of Assembly                                        |         | x64                               | 4000                                  |       |

| 8      | Voltage Interface Level of this Assembly                      |         | SSTL 2.5V                         | 04                                    |       |

| 9      | SDRAM Device Cycle Time at CLX (CL = 2.5)                     | PC1600  | 8.0ns                             | 80                                    |       |

| 9      | SDRAW Device Cycle Time at GLA (GL = 2.3)                     | PC2100  | 7.5ns                             | 75                                    |       |

| 10     | SDRAM Device Access Time from Clock at                        | PC1600  | 0.8ns                             | 80                                    |       |

| 10     | CL = 2.5                                                      | PC2100  | 0.75ns                            | 75                                    |       |

| 11     | DIMM Configuration Type                                       |         | Non-parity                        | 00                                    |       |

| 12     | Refresh Rate/Type                                             |         | 15.625 μs/SR                      | 80                                    |       |

| 13     | Primary SDRAM Device Width                                    |         | x8                                | 08                                    |       |

| 14     | Error Checking SDRAM Device Width                             |         | N/A                               | 00                                    |       |

| 15     | SDRAM Device Attributes: Minimum Clock Dela<br>Column Access  | 1 Clock | 01                                |                                       |       |

| 16     | SDRAM Device Attributes: Burst Lengths Suppo                  | orted   | 2, 4, 8                           | 0E                                    |       |

| 17     | SDRAM Device Attributes: Number of Device B                   | anks    | 4                                 | 04                                    |       |

| 18     | SDRAM Device Attributes: CAS Latencies supp                   | orted   | 2, 2.5                            | 0C                                    |       |

| 19     | SDRAM Device Attributes: CS Latency                           |         | 0                                 | 01                                    |       |

| 20     | SDRAM Device Attributes: WE Latency                           |         | 1                                 | 02                                    |       |

| 21     | SDRAM Module Attributes                                       |         | Unbuffered, Differential<br>Clock | 20                                    |       |

| 22     | SDRAM Device Attributes: General                              |         | AP, $V_{DD} \pm 0.2V$             | 80                                    |       |

|        |                                                               | PC1600  | 10.0ns                            | A0                                    |       |

| 23     | Minimum Clock Cycle at CLX-0.5 (CL = 2)                       | PC2100  | 8.0ns                             | 80                                    |       |

|        | Maximum Data Access Time (t <sub>AC</sub> ) from Clock        | PC1600  | ± 0.8ns                           | 80                                    |       |

| 24     | at CLX-0.5 (CL = 2)                                           | PC2100  | ± 0.75ns                          | 75                                    |       |

| 25     | Minimum Clock Cycle Time at CLX-1 (CL = 1.5)                  |         | N/A                               | 00                                    |       |

| 26     | Maximum Data Access Time ( $t_{AC}$ ) from Clock a (CL = 1.5) | t CLX-1 | N/A                               | 00                                    |       |

| 27     | Minimum Row Precharge Time (t <sub>RP</sub> )                 |         | 20.0ns                            | 50                                    |       |

| 28     | Minimum Row Active to Row Active Delay (t <sub>RRD</sub>      | 5)      | 15.0ns                            | 3C                                    |       |

| 29     | Minimum RAS to CAS Delay (t <sub>RCD</sub> )                  |         | 20.0ns                            | 50                                    |       |

| 20     | Minimum Active to Procharge Time (t                           | PC1600  | 50.0ns                            | 32                                    |       |

| 30     | Minimum Active to Precharge Time (t <sub>RAS</sub> )          | PC2100  | 45.0ns                            | 2D                                    |       |

| 31     | Module Bank Density - 16Mx64                                  |         | 128MB                             | 20                                    |       |

- 1. Setup and hold values assume a 1 Volt/ns slew rate.

- 2. cc = Checksum Data byte, 00-FF (Hex).

- 3. "MM" = Alphanumeric revision code, A-Z, 0-9.

- 4. mm = ASCII coded revision code byte "MM".

- 5. ww = Binary coded decimal week code, 01-52 (Decimal) 01-34 (Hex).

- 6. yy = Binary coded decimal year code, 00-99 (Decimal) 00-63 (Hex).

- 7. ss = Serial number data byte, 00-FF (Hex).

#### Serial Presence Detect (Part 2 of 2)

| Byte #  | Description                                         |        | SPD Entry Value              | Serial PD Data Entry<br>(Hexadecimal)    | Notes |

|---------|-----------------------------------------------------|--------|------------------------------|------------------------------------------|-------|

| 32      | Address and Command Setup Time before               | PC1600 | 1.1ns                        | B0                                       |       |

| 32      | Clock                                               | PC2100 | 0.9ns                        | 90                                       |       |

| 33      | Address and Command Hold Time after Clock           | PC1600 | 1.1ns                        | B0                                       |       |

| 33      | Address and Command Hold Time after Clock           | PC2100 | 0.9ns                        | 90                                       | 1     |

| 34      | Data/Data Mask Input Setup Time before              | PC1600 | 0.6ns                        | 60                                       | '     |

| 34      | Clock                                               | PC2100 | 0.5ns                        | 50                                       |       |

| 35      | Data/Data Mask Input Hold Time ofter Clock          | PC1600 | 0.6ns                        | 60                                       |       |

| 33      | Data/Data Mask Input Hold Time after Clock          | PC2100 | 0.5ns                        | 50                                       |       |

| 36-40   | Reserved for VCSDRAM                                |        | Undefined                    | 00                                       |       |

| 41      | A4 Minimum Active/Auto Defreeb Time (t.)            | PC1600 | 70                           | 46                                       |       |

| 41 10   | Minimum Active/Auto Refresh Time (t <sub>RC</sub> ) | PC2100 | 65                           | 41                                       |       |

| 42-61   | Reserved                                            |        | Undefined                    | 00                                       |       |

| 62      | SPD Revision                                        |        | 0                            | 00                                       |       |

| 63      | Checksum for Bytes 0 - 62                           |        | Checksum Data                | cc                                       | 2     |

| 64-71   | Manufacturers' JEDEC ID Code                        |        | IBM                          | A400000000000000                         |       |

| 72      | Module Manufacturing Location                       |        | MM                           | mm                                       | 3, 4  |

| 72.00   | Madula Part Number                                  | PC1600 | ASCII 'B6N16644JGA<br>-8NT'  | 42364E31363634344A4741<br>2D384E54202020 |       |

| 73-90   | Module Part Number PC2100                           |        | ASCII 'B6N16644JGA<br>-75NT' | 42364E31363634344A4741<br>2D37354E542020 |       |

| 91-92   | Module Revision Code                                |        | 'A' plus ASCII blank         | 4120                                     |       |

| 93-94   | Module Manufacturing Date                           |        | Year/Week Code               | yyww                                     | 5, 6  |

| 95-98   | Module Serial Number                                |        | Serial Number                | SSSSSSS                                  | 7     |

| 99-127  | Reserved                                            |        | Undefined                    | 00                                       |       |

| 128-255 | Open for Customer Use                               |        | Undefined                    | 00                                       |       |

- 1. Setup and hold values assume a 1 Volt/ns slew rate.

- 2. cc = Checksum Data byte, 00-FF (Hex).

- 3. "MM" = Alphanumeric revision code, A-Z, 0-9.

- 4. mm = ASCII coded revision code byte "MM".

- 5. ww = Binary coded decimal week code, 01-52 (Decimal) 01-34 (Hex).

- 6. yy = Binary coded decimal year code, 00-99 (Decimal) 00-63 (Hex).

- 7. ss = Serial number data byte, 00-FF (Hex).

# **Absolute Maximum Ratings**

| Symbol                             | Parameter                                                      |                     | Rating                         | Units |

|------------------------------------|----------------------------------------------------------------|---------------------|--------------------------------|-------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on I/O pins relative to V <sub>SS</sub>                |                     | -0.5 to V <sub>DDQ</sub> + 0.5 | V     |

| V                                  | S                                                              |                     | -0.5 to +3.6                   | V     |

| VIN                                | V <sub>IN</sub> Voltage on Inputs relative to V <sub>SS</sub>  | Serial PD<br>device | -0.3 to +6.5                   | V     |

| V <sub>DD</sub>                    | Voltage on $V_{DD}$ supply relative to $V_{SS}$                |                     | -0.5 to +3.6                   | V     |

| $V_{DDQ}$                          | Voltage on V <sub>DDQ</sub> supply relative to V <sub>SS</sub> |                     | -0.5 to +3.6                   | V     |

| V <sub>DDSPD</sub>                 | Voltage on $V_{DDSPD}$ supply relative to $V_{SS}$             |                     | -0.3 to +5.5                   | V     |

| T <sub>A</sub>                     | Operating Temperature (Ambient)                                |                     | 0 to +70                       | °C    |

| T <sub>STG</sub>                   | Storage Temperature (Plastic)                                  |                     | -55 to +150                    | °C    |

| $P_{D}$                            | Power Dissipation                                              |                     | TBD                            | W     |

| I <sub>OUT</sub>                   | Short Circuit Output Current                                   |                     | 50                             | mA    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Capacitance

| Parameter                                                                                                      | Symbol           | Max. | Units | Notes |

|----------------------------------------------------------------------------------------------------------------|------------------|------|-------|-------|

| Input Capacitance: CK0, $\overline{\text{CK}}$ 0, CK1, $\overline{\text{CK}}$ 1, CK2, $\overline{\text{CK}}$ 2 | C <sub>I1</sub>  | 12   | pF    | 1     |

| Input Capacitance: A0-A11, BA0, BA1, WE, RAS, CAS, CKE0, S0                                                    | C <sub>I2</sub>  | 30   | pF    | 1     |

| Input Capacitance: SA0-SA2, SCL                                                                                | C <sub>14</sub>  | 9    | pF    | 1     |

| Input/Output Capacitance DQ0-63; DQS0-7, 9-16                                                                  | C <sub>IO1</sub> | 7    | pF    | 1, 2  |

| Input/Output Capacitance: SDA                                                                                  | C <sub>IO3</sub> | 11   | pF    |       |

<sup>1.</sup>  $V_{DDQ} = V_{DD} = 2.5V$  0.2V, f = 100 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT}$  (DC) =  $V_{DDQ/2}$ ,  $V_{OUT}$  (Peak to Peak) = 0.2V. 2. DQS inputs are grouped with I/O pins reflecting the fact that they are matched in loading to DQ and DQS to facilitate trace matching at the board level.

# **Electrical Characteristics and DC Operating Conditions**

$(0^{\circ}\text{C} \le \text{T}_{\text{A}} \le 70^{\circ}\text{C}; \text{V}_{\text{DDQ}} = 2.5\text{V} \pm 0.2\text{V}, \text{V}_{\text{DD}} = +2.5\text{V} \pm 0.2\text{V}, \text{see AC Characteristics})$

| Symbol                             | Parameter                                                                                                      |                                                          | Min                     | Max                     | Units | Notes |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|-------------------------|-------|-------|

| V <sub>DD</sub>                    | Supply Voltage                                                                                                 |                                                          | 2.3                     | 2.7                     | V     | 1     |

| $V_{DDQ}$                          | I/O Supply Voltage                                                                                             |                                                          | 2.3                     | 2.7                     | V     | 1     |

| V <sub>SS</sub> , V <sub>SSQ</sub> | Supply Voltage<br>I/O Supply Voltage                                                                           |                                                          | 0                       | 0                       | V     |       |

| V <sub>REF</sub>                   | I/O Reference Voltage                                                                                          |                                                          | 1.15                    | 1.35                    | V     | 1, 2  |

| V <sub>TT</sub>                    | I/O Termination Voltage (System)                                                                               |                                                          | V <sub>REF</sub> – 0.04 | V <sub>REF</sub> + 0.04 | V     | 1, 3  |

| V <sub>DDSPD</sub>                 | Supply Voltage<br>SPD Supply Voltage                                                                           |                                                          | 2.3                     | 2.7                     | V     |       |

| V <sub>IH(DC)</sub>                | Input High (Logic1) Voltage                                                                                    |                                                          | V <sub>REF</sub> + 0.15 | V <sub>DDQ</sub> + 0.3  | V     | 1     |

| V <sub>IL(DC)</sub>                | Input Low (Logic0) Voltage                                                                                     |                                                          | - 0.3                   | V <sub>REF</sub> – 0.15 | V     | 1     |

| V <sub>IN(DC)</sub>                | Input Voltage Level, CK and CK Inputs                                                                          |                                                          | - 0.3                   | V <sub>DDQ</sub> + 0.3  | V     | 1     |

| V <sub>ID(DC)</sub>                | Input Differential Voltage, CK and CK Inputs                                                                   |                                                          | 0.30                    | V <sub>DDQ</sub> + 0.6  | V     | 1, 4  |

|                                    |                                                                                                                | Address and control inputs                               | - 40                    | 40                      |       |       |

| l <sub>l</sub>                     | Input Leakage Current Any input $0V \le V_{IN} \le V_{DD}$ (All other pins not under test = $0V$ )             | DQ0-63;<br>DQS0-7, 9-16                                  | -5                      | 5                       | μА    | 1     |

|                                    |                                                                                                                | CK0, <u>CK</u> 0<br>CK1, <u>CK</u> 1<br>CK2, <u>CK</u> 2 | <b>–</b> 15             | 15                      |       |       |

| I <sub>OZ</sub>                    | Output Leakage Current                                                                                         | DQ0-63;<br>DQS0-7, 9-16                                  | - 5                     | 5                       | μΑ    | 1     |

|                                    | (DQs are disabled; $0V \le V_{out} \le V_{DDQ}$                                                                | SDA                                                      | <b>–</b> 1              | 1                       |       |       |

| I <sub>OH</sub>                    | Output High Current (V <sub>OUT</sub> = V <sub>DDQ</sub> -0.373V, min V <sub>REF</sub> , min V <sub>TT</sub> ) |                                                          | - 16.8                  |                         | mA    | 1     |

| I <sub>OL</sub>                    | Output Low Current (V <sub>OUT</sub> = 0.373, max V <sub>REF</sub> , max V <sub>TT</sub> )                     |                                                          | 16.8                    |                         | mA    | 1     |

<sup>1.</sup> Inputs are not recognized as valid until  $\mathsf{V}_{\mathsf{REF}}$  stabilizes.

<sup>2.</sup> V<sub>REF</sub> is expected to be equal to 0.5 V<sub>DDQ</sub> of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak noise on V<sub>REF</sub> may not exceed 2% of the DC value.

<sup>3.</sup> V<sub>TT</sub> is not applied directly to the DIMM. V<sub>TT</sub> is a system supply for signal termination resistors, is expected to be set equal to V<sub>REF</sub> and must track variations in the DC level of V<sub>REF</sub>

<sup>4.</sup>  $V_{ID}$  is the magnitude of the difference between the input level on CK and the input level on  $\overline{CK}$ .

#### **AC Characteristics**

(Notes 1-5 apply to the following Tables; Electrical Characteristics and DC Operating Conditions, AC Operating Conditions, Operating, Standby, and Refresh Currents, and Electrical Characteristics and AC Timing.)

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. Tests for AC timing, I<sub>DD</sub>, and electrical, AC and DC characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 3. Outputs measured with equivalent load. Refer to the AC Output Load Circuit below.

- AC timing and I<sub>DD</sub> tests may use a V<sub>IL</sub> to V<sub>IH</sub> swing of up to 1.5V in the test environment, but input timing is still referenced to V<sub>REF</sub> (or to the crossing point for CK, CK), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1V/ns in the range between V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub> unless otherwise specified.

The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e. the receiver effectively

- 5. The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e. the receiver effectively switches as a result of the signal crossing the AC input level, and remains in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.

# **AC Output Load Circuit Diagram**

# **AC Operating Conditions** (0 °C $\leq$ T<sub>A</sub> $\leq$ 70 °C; $V_{DDQ}$ = 2.5V $\pm$ 0.2V; $V_{DD}$ = 2.5V $\pm$ 0.2V, See AC Characteristics)

| Symbol              | Parameter/Condition                                              | Min                           | Max                     | Unit | Notes   |

|---------------------|------------------------------------------------------------------|-------------------------------|-------------------------|------|---------|

| V <sub>IH(AC)</sub> | Input High (Logic 1) Voltage.                                    | V <sub>REF</sub> + 0.31       |                         | V    | 1, 2    |

| V <sub>IL(AC)</sub> | Input Low (Logic 0) Voltage.                                     |                               | V <sub>REF</sub> – 0.31 | V    | 1, 2    |

| V <sub>ID(AC)</sub> | Input Differential Voltage, CK and $\overline{\text{CK}}$ Inputs | 0.62                          | V <sub>DDQ</sub> + 0.6  | V    | 1, 2, 3 |

| V <sub>IX(AC)</sub> | Input Differential Pair Cross Point Voltage, CK and CK Inputs    | (0.5*V <sub>DDQ</sub> ) – 0.2 | $(0.5*V_{DDQ}) + 0.2$   | V    | 1, 2, 4 |

- 1. Input slew rate = 1V/ns.

- 2. Inputs are not recognized as valid until V<sub>REF</sub> stabilizes.

- 3.  $V_{ID}$  is the magnitude of the difference between the input level on CK and the input level on  $\overline{\text{CK}}$ .

- 4. The value of  $V_{IX}$  is expected to equal  $0.5^*V_{DDQ}$  of the transmitting device and must track variations in the DC level of the same.

#### Operating, Standby, and Refresh Currents (0 $^{\circ}\text{C} \le T_{A} \le 70 \,^{\circ}\text{C}$ ; $V_{DDQ} = 2.5 \text{V} \pm 0.2 \text{V}$ ; $V_{DD} = 2.5 \text{V} \pm 0.2 \text{V}$ , See AC Characteristics)

| Symbol            | Parameter/Condition                                                                                                                                                                                                                                                                | PC1600<br>t <sub>CK</sub> = 10ns | PC2100<br>t <sub>CK</sub> = 7.5ns | Unit | Notes   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|------|---------|

| I <sub>DD0</sub>  | <b>Operating Current</b> : one bank; active / precharge; $t_{RC} = t_{RC\ MIN}$ ; $t_{CK} = t_{CK\ MIN}$ ; DQ, DM, and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle                                                         | 600                              | 680                               | mA   | 1, 2    |

| I <sub>DD1</sub>  | <b>Operating Current</b> : one bank; active / read / precharge; Burst = 2; $t_{RC} = t_{RC \; MIN}$ ; CL = 2.5; $t_{CK} = t_{CK \; MIN}$ ; $t_{OUT} = t_{OMA}$ ; address and control inputs changing once per clock cycle                                                          | 720                              | 880                               | mA   | 1, 2    |

| I <sub>DD2P</sub> | Precharge Power-Down Standby Current: all banks idle; power-down mode; CKE $\leq$ V $_{IL\ MAX}$ ; $t_{CK}$ = $t_{CK\ MIN}$                                                                                                                                                        | 120                              | 120                               | mA   | 1, 2    |

| I <sub>DD2N</sub> | <b>Idle Standby Current:</b> $\overline{CS} \ge V_{IH\ MIN}$ ; all banks idle; CKE $\ge V_{IH\ MIN}$ ; $t_{CK} = t_{CK\ MIN}$ ; address and control inputs changing once per clock cycle                                                                                           | 240                              | 280                               | mA   | 1, 2    |

| I <sub>DD3P</sub> | Active Power-Down Standby Current: one bank active; power-down mode;<br>CKE $\leq$ V <sub>IL MAX</sub> ; $t_{CK} = t_{CK MIN}$                                                                                                                                                     | 120                              | 120                               | mA   | 1, 2    |

| I <sub>DD3N</sub> | Active Standby Current: one bank; active / precharge; $\overline{CS} \ge V_{IH\ MIN}$ ; CKE $\ge V_{IH\ MIN}$ ; $t_{RC} = t_{RAS\ MAX}$ ; $t_{CK} = t_{CK\ MIN}$ ; DQ, DM, and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle | 400                              | 480                               | mA   | 1, 2    |

| I <sub>DD4R</sub> | <b>Operating Current:</b> one bank; Burst = 2; reads; continuous burst; address and control inputs changing once per clock cycle; DQ and DQS outputs changing twice per clock cycle; $CL = 2.5$ ; $t_{CK} = t_{CK\ MIN}$ ; $I_{OUT} = 0$ mA                                        | 1040                             | 1320                              | mA   | 1, 2    |

| I <sub>DD4W</sub> | <b>Operating Current</b> : one bank; Burst = 2; writes; continuous burst; address and control inputs changing once per clock cycle; DQ and DQS inputs changing twice per clock cycle; $CL = 2.5$ ; $t_{CK} = t_{CK  MIN}$                                                          | 920                              | 1200                              | mA   | 1, 2    |

| loos              | Auto-Refresh Current: $t_{RC} = t_{RFC \ MIN}$                                                                                                                                                                                                                                     | 1280                             | 1360                              | mA   | 1, 2, 4 |

| I <sub>DD5</sub>  | t <sub>RC</sub> = 15.625 μs                                                                                                                                                                                                                                                        | 126                              | 126                               | IIIA | 1, 4, 4 |

| $I_{DD6}$         | Self-Refresh Current: CKE ≤ 0.2V                                                                                                                                                                                                                                                   | 16                               | 16                                | mA   | 1, 2, 3 |

<sup>1.</sup>  $I_{DD}$  specifications are tested after the device is properly initialized. 2. Input slew rate = 1V/ns.

<sup>3.</sup> Enables on-chip refresh and address counters.

<sup>4.</sup> Current at 15.625  $\mu s$  is time averaged value of  $I_{DD5}$  at  $t_{RFC\;MIN}$  and  $I_{DD2P}$  over 15.625  $\mu s.$

# AC Timing Specifications for DDR SDRAM Devices Used on Module (0 °C $\leq$ T<sub>A</sub> $\leq$ 70 °C; V<sub>DDQ</sub> = 2.5V $\pm$ 0.2V; V<sub>DD</sub> = 2.5V $\pm$ 0.2V, See AC Characteristics) (Part 1 of 2)

| Cumbal             | Dorometer                                                                      |                           | PC 2100                                  |        | PC 1600                                  |       | Linit           | Notes                         |

|--------------------|--------------------------------------------------------------------------------|---------------------------|------------------------------------------|--------|------------------------------------------|-------|-----------------|-------------------------------|

| Symbol             | Parameter                                                                      |                           | Min                                      | Max    | Min                                      | Max   | Unit            | Notes                         |

| t <sub>AC</sub>    | DQ output access time from CK/CK                                               |                           | - 0.75                                   | + 0.75 | - 0.8                                    | + 0.8 | ns              | 1, 2, 3,                      |

| t <sub>DQSCK</sub> | DQS output access time from CK/CK                                              |                           | - 0.75                                   | + 0.75 | - 0.8                                    | + 0.8 | ns              | 1, 2, 3,                      |

| t <sub>CH</sub>    | CK high-level width                                                            |                           | 0.45                                     | 0.55   | 0.45                                     | 0.55  | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>CL</sub>    | CK low-level width                                                             |                           | 0.45                                     | 0.55   | 0.45                                     | 0.55  | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>CK</sub>    | Clock avalatima                                                                | CL = 2.5                  | 7.5                                      | 12     | 8                                        | 12    | ns              | 1, 2, 3,                      |

| t <sub>CK</sub>    | Clock cycle time                                                               | CL = 2.0                  | 8                                        | 12     | 10                                       | 12    | ns              | 1, 2, 3,                      |

| t <sub>DH</sub>    | DQ and DM input hold time                                                      |                           | 0.5                                      |        | 0.6                                      |       | ns              | 1, 2, 3,<br>4, 18, 1          |

| t <sub>DS</sub>    | DQ and DM input setup time                                                     |                           | 0.5                                      |        | 0.6                                      |       | ns              | 1, 2, 3,<br>4, 18, 1          |

| t <sub>DIPW</sub>  | DQ and DM input pulse width (each input                                        | ut)                       | 1.75                                     |        | 2                                        |       | ns              | 1, 2, 3,                      |

| $t_{HZ}$           | Data-out high-impedance time from CK/                                          | CK                        | - 0.75                                   | + 0.75 | - 0.8                                    | + 0.8 | ns              | 1, 2, 3,<br>4, 5              |

| $t_{LZ}$           | Data-out low-impedance time from CK/0                                          | <del>CK</del>             | - 0.75                                   | + 0.75 | - 0.8                                    | + 0.8 | ns              | 1, 2, 3,<br>4, 5              |

| t <sub>DQSQ</sub>  | DQS-DQ skew (DQS & associated DQ s                                             | signals)                  |                                          | + 0.5  |                                          | + 0.6 | ns              | 1, 2, 3,                      |

| t <sub>DQSQA</sub> | DQS-DQ skew (DQS & all DQ signals)                                             |                           |                                          | + 0.5  |                                          | + 0.6 | ns              | 1, 2, 3,                      |

| t <sub>HP</sub>    | Minimum half clk period for any given cy $(t_{CH})$ or clk low $(t_{CL})$ time | vcle; defined by clk high | t <sub>CH</sub><br>or<br>t <sub>CL</sub> |        | t <sub>CH</sub><br>or<br>t <sub>CL</sub> |       | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>QH</sub>    | Data output hold time from DQS                                                 |                           | t <sub>HP</sub> -<br>0.75ns              |        | t <sub>HP</sub> -<br>1.0ns               |       | t <sub>CK</sub> | 1, 2, 3,                      |

| $t_{DQSS}$         | Write command to 1st DQS latching train                                        | nsition                   | 0.75                                     | 1.25   | 0.75                                     | 1.25  | t <sub>CK</sub> | 1, 2, 3,                      |

| $t_{DQSL,H}$       | DQS input low (high) pulse width (write                                        | cycle)                    | 0.35                                     |        | 0.35                                     |       | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>DSS</sub>   | DQS falling edge to CK setup time (write                                       | e cycle)                  | 0.2                                      |        | 0.2                                      |       | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>DSH</sub>   | DQS falling edge hold time from CK (wr                                         | ite cycle)                | 0.2                                      |        | 0.2                                      |       | t <sub>CK</sub> | 1, 2, 3,                      |

| $t_{MRD}$          | Mode register set command cycle time                                           |                           | 15                                       |        | 16                                       |       | ns              | 1, 2, 3,                      |

| t <sub>WPRES</sub> | Write preamble setup time                                                      |                           | 0                                        |        | 0                                        |       | ns              | 1, 2, 3,<br>4, 7              |

| t <sub>WPST</sub>  | Write postamble                                                                |                           | 0.40                                     | 0.60   | 0.40                                     | 0.60  | t <sub>CK</sub> | 1, 2, 3,<br>4, 6              |

| t <sub>WPRE</sub>  | Write preamble                                                                 |                           | 0.25                                     |        | 0.25                                     |       | t <sub>CK</sub> | 1, 2, 3,                      |

| t <sub>IH</sub>    | Address and control input hold time (fas                                       | t slew rate)              | 0.9                                      |        | 1.1                                      |       | ns              | 2, 3, 4,<br>11, 13,<br>14     |

| t <sub>IS</sub>    | Address and control input setup time (fa                                       | ast slew rate)            | 0.9                                      |        | 1.1                                      |       | ns              | 2, 3, 4,<br>11, 13,<br>14     |

| t <sub>IH</sub>    | Address and control input hold time (slo                                       | w slew rate)              | 1.0                                      |        | 1.1                                      |       | ns              | 2, 3, 4,<br>12, 13,<br>14, 17 |

# AC Timing Specifications for DDR SDRAM Devices Used on Module (0 °C $\leq$ T<sub>A</sub> $\leq$ 70 °C; V<sub>DDQ</sub> = 2.5V $\pm$ 0.2V; V<sub>DD</sub> = 2.5V $\pm$ 0.2V, See AC Characteristics) (Part 2 of 2)

| Courada a l       | Parameter                                               | PC 2                                        | 2100    | PC 1600                                  |         | Lloit           | Notes                         |

|-------------------|---------------------------------------------------------|---------------------------------------------|---------|------------------------------------------|---------|-----------------|-------------------------------|

| Symbol            | Parameter                                               | Min                                         | Max     | Min                                      | Max     | Unit            | Notes                         |

| t <sub>IS</sub>   | Address and control input setup time (slow slew rate)   | 1.0                                         |         | 1.1                                      |         | ns              | 2, 3, 4,<br>12, 13,<br>14, 17 |

| t <sub>IPW</sub>  | Input pulse width                                       | 2.2                                         |         |                                          |         | ns              | 2, 3, 4,<br>14                |

| t <sub>RPRE</sub> | Read preamble                                           | 0.9                                         | 1.1     | 0.9                                      | 1.1     | t <sub>CK</sub> | 1, 2, 3, 4                    |

| t <sub>RPST</sub> | Read postamble                                          | 0.40                                        | 0.60    | 0.40                                     | 0.60    | t <sub>CK</sub> | 1, 2, 3, 4                    |

| t <sub>RAS</sub>  | Active to Precharge command                             | 45                                          | 120,000 | 50                                       | 120,000 | ns              | 1, 2, 3, 4                    |

| t <sub>RC</sub>   | Active to Active/Auto-refresh command period            | 65                                          |         | 70                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>RFC</sub>  | Auto-refresh to Active/Auto-refresh command period      | 75                                          |         | 80                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>RCD</sub>  | Active to Read or Write delay                           | 20                                          |         | 20                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>RAP</sub>  | Active to Read Command with Autoprecharge               | 20                                          |         | 20                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>RP</sub>   | Precharge command period                                | 20                                          |         | 20                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>RRD</sub>  | Active bank A to Active bank B command                  | 15                                          |         | 15                                       |         | ns              | 1, 2, 3, 4                    |

| $t_{WR}$          | Write recovery time                                     | 15                                          |         | 15                                       |         | ns              | 1, 2, 3, 4                    |

| t <sub>DAL</sub>  | Auto precharge write recovery + precharge time          | $(t_{WR}/t_{CK})$<br>+<br>$(t_{RP}/t_{CK})$ |         | $(t_{WR}/t_{CK})$<br>+ $(t_{RP}/t_{CK})$ |         | t <sub>CK</sub> | 1, 2, 3,<br>4, 16             |

| t <sub>WTR</sub>  | Internal write to read command delay                    | 1                                           |         | 1                                        |         | t <sub>CK</sub> | 1, 2, 3, 4                    |

| t <sub>XSNR</sub> | Exit self-refresh to non-read command                   | 75                                          |         | 80                                       |         | ns              | 1, 2, 3, 4                    |

| $t_{XSRD}$        | Exit self-refresh to read command                       | 200                                         |         | 200                                      |         | t <sub>CK</sub> | 1, 2, 3, 4                    |

| t <sub>REFI</sub> | Average Periodic Refresh Interval                       |                                             | 15.6    |                                          | 15.6    | μs              | 1, 2, 3,<br>4, 8              |

| t <sub>QCS</sub>  | QFC setup time on Read                                  | 0.9                                         | 1.1     | 0.9                                      | 1.1     | t <sub>CK</sub> | 1, 2, 3,<br>4, 15             |

| t <sub>QCH</sub>  | QFC hold time on Read                                   | 0.4                                         | 0.6     | 0.4                                      | 0.6     | t <sub>CK</sub> | 1, 2, 3,<br>4, 15             |

| t <sub>QCSW</sub> | Delay from CK edge of write command to QFC low on write |                                             | 4.0     |                                          | 4.0     | ns              | 1, 2, 3,<br>4, 9, 15          |

| t <sub>QCHW</sub> | QFC hold time on write                                  | 1.25                                        | 2.0     | 1.25                                     | 2.0     | ns              | 1, 2, 3,<br>4, 10, 15         |

#### **AC Timing Specification Notes**

- 1. Input slew rate = 1V/ns.

- 2. The CK/CK input reference level (for timing reference to CK/CK) is the point at which CK and CK cross: the input reference level for signals other than CK/CK, is V<sub>REF.</sub>

- 3. Inputs are not recognized as valid until V<sub>REF</sub> stabilizes.

- 4. The Output timing reference level, as measured at the timing reference point indicated in AC Characteristics (Note 3) is V<sub>TT</sub>.

- t<sub>HZ</sub> and t<sub>LZ</sub> transitions occur in the same access time windows as valid data transitions. These parameters are not referred to a specific voltage level, but specify when the device is no longer driving (HZ), or begins driving (LZ).

- 6. The maximum limit for this parameter is not a device limit. The device operates with a greater value for this parameter, but system performance (bus turnaround) degrades accordingly.

- 7. The specific requirement is that DQS be valid (high, low, or some point on a valid transition) on or before this CK edge. A valid transition is defined as monotonic and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from Hi-Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from high to low at this time, depending on t<sub>DQSS</sub>.

- 8. A maximum of eight Auto refresh commands can be posted to any given DDR SDRAM device.

- 9. QFC is enabled as soon as possible after the rising CK edge that registers the Write command.

- 10. QFC is disabled as soon as possible after the last valid DQS edge transitions Low.