# **5 V CATV MODEM RF RECEIVER**

**ISG1000**

Integrated Solutions Group

# **FEATURES**

- DOCSIS COMPLIANT: 91-860 MHz RF BW

- INTERFACES DIRECTLY WITH QAM DEMOD ICs

- LOW PHASE NOISE: -83 dBc/Hz @ 10 KHz

- BUILT IN DIPLEXER: with >40 dB Isolation

- BUSINESS CARD SIZE: 3.4" x 2.0" x 0.5"

- RUGGED DESIGN/NO MICROPHONICS: All SMD Components "Coiless"

- LOW POWER CONSUMPTION:

Rx: 1.2 Watts

EUROPEAN AND DIRECT SAMPLING VERSIONS AVAILABLE

# **DESCRIPTION AND APPLICATIONS**

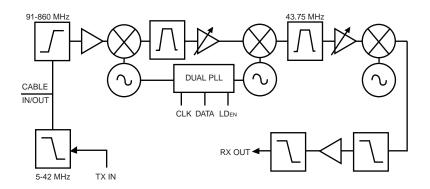

The ISG1000 is a complete RF receiver designed for use in digital cable modem and settop applications. The receiver integrates a DOCSIS compliant diplex filter, triple conversion receiver and incorporates RF path for external Tx section (see Figure 1). The diplex filter provides over 40 dB of isolation between the Tx band and the Rx band. The receiver section provides channel selectivity and converts QAM carriers to low IF sampling frequency for digital signal processing.

# ELECTRICAL CHARACTERISTICS (Vcc = 5 V, Vcc2 = 24 V, TA = 25°C)

|           | PART NUMBER                       |        | ISG1000 |      |      |

|-----------|-----------------------------------|--------|---------|------|------|

| SYMBOLS   | PARAMETERS                        | UNITS  | MIN     | TYP  | MAX  |

| RF Perfor | mance (Rx)                        |        |         |      |      |

| fop       | Operating Frequency Range         | MHz    | 91      |      | 860  |

|           | Input Signal Level                | dBmV   | -20     |      | 15   |

|           | Gain Range                        | dB     | 25      |      | 75   |

| Vagc      | Automatic Gain Control Voltage RF |        | 0       |      | 3.3  |

| Vagc      | Automatic Gain Control Voltage IF |        | 0       |      | 3.3  |

| NFMAX     | Noise Figure (Max Gain)           | dB     |         | 8    | 10   |

|           | Phase Noise at 10 kHz Offset      | dBc/Hz |         | -83  | -80  |

|           | LO Radiation at RF Input          | dBm    |         | -40  |      |

|           | Resolution                        | KHz    |         | 62.5 |      |

|           | Lock Time                         | μsec.  |         | 600  |      |

|           | Input Impedance (Nominal)         | ohms   |         | 75   |      |

| RLIN      | Input Return Loss                 | dB     | 6       |      |      |

|           | Channel Bandwidth USA             | MHz    |         | 6    |      |

|           | Output Frequency <sup>1</sup>     | MHz    | 5.70    | 5.75 | 5.80 |

|           | Passband Ripple                   | dB     |         | 1    | 2    |

|           | Image Rejection                   | dB     | 50      |      |      |

|           | Inband Group Delay                | ns     |         |      | 100  |

|           | CSO <sup>2</sup>                  | dBc    |         |      | 45   |

|           | CTB <sup>2</sup>                  | dBc    |         |      | 45   |

|           | Frequency Offset                  | KHz    | -50     |      | +50  |

### Notes

- 1. Optional Output Frequency of 43.75 MHz Available

- 2. 110 Channels at +15 dBmV/tone

- 3. Temperature performance parameters will vary slightly.

# **ELECTRICAL CHARACTERISTICS** (Vcc = 5 V, Vcc2 = 24 V, TA = 25°C)

|             | PART NUMBER                        |                                       |                  | ISG1000       |      |

|-------------|------------------------------------|---------------------------------------|------------------|---------------|------|

| SYMBOLS     | PARAMETERS                         | UNITS                                 | MIN              | TYP           | MAX  |

| RF Perfor   | mance Specs (Upstream)             | · · · · · · · · · · · · · · · · · · · | -                |               |      |

|             | Operation frequency                | MHz                                   | 5                |               | 42   |

|             | Output Return Loss at F-connector  | dB                                    | 6                |               |      |

|             | Insertion Loss                     | dB                                    |                  |               | 1.5  |

|             | Isolation from Tx to Rx            | dB                                    | 40               |               |      |

|             | Inband group delay                 | dsec                                  |                  |               | 100  |

| Power Re    | quirements                         |                                       |                  |               |      |

|             | Supply Voltage V1 Rx               | V                                     | 4.75             | 5             | 5.25 |

|             | Supply Voltage V2 Rx               | V                                     | 20               | 24            | 31.5 |

| Supply Co   | urrent                             | ·                                     |                  |               |      |

| Icc1 (Rx)   | Supply Current 1 (Rx)              | mA                                    |                  | 240           | 320  |

| Icc2 (Rx)   | Supply Current 2 (Rx)              | mA                                    |                  | 1.5           | 2    |

| Physical In | terface                            | '                                     |                  |               |      |

|             | To the CATV Network                |                                       |                  | Female        |      |

|             |                                    |                                       |                  | F-Connector   |      |

|             | To the Motherboard                 |                                       |                  | 16 Pin Header |      |

| Physical I  | Dimensions                         | 1                                     | 1                |               |      |

|             | LxWxH                              |                                       | 3.4 x 2.0 x 0.5" |               |      |

| Environm    | ental Specs                        |                                       | •                |               |      |

| Тор         | Operating Temperature <sup>3</sup> | °C                                    | -5               |               | 60   |

| Tstg        | Storage Temperature                | °C                                    | -40              |               | 75   |

# **ABSOLUTE MAXIMUM RATINGS**

(Tc = 25 °C unless otherwise noted)

| SYMBOLS                         | PARAMETERS                     | UNITS | RATINGS    |

|---------------------------------|--------------------------------|-------|------------|

| VIN                             | RF Input Voltage               | dBmV  | 60         |

| Vcc1 (Rx)                       | CC1 (Rx) Supply Voltage 1 (Rx) |       | 6          |

| Vcc2 (Rx) Supply Voltage 2 (Rx) |                                | V     | 35         |

| Top Operating Temperature       |                                | °C    | -10 to 60  |

| Тѕтс                            | Tstg Storage Temperature       |       | -55 to 150 |

| TsoL Soldering Temperature      |                                | °C    | 260        |

| tsoL Soldering Time             |                                | sec.  | 4          |

### Note

Operation in excess of any one of these parameters may result in permanent damage.

# **PIN FUNCTIONS**

| Pin No. | Pin Name  | Description                                                                                                                                                                                                      | Equivalent Circuit                      |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1       | RFAGC     | The RFAGC pin is used to adjust gain in the dual conversion tuner. This pin has a positive gain vs. AGC slope. 20 dB of gain control is available by varying the voltage from 0.5 V to 3.3 V.                    | 1 1 K 1 K 1 K 1 K 1 K 1 K 1 K 1 K 1 K 1 |

| 2       | N/C       |                                                                                                                                                                                                                  |                                         |

| 3       | N/C       |                                                                                                                                                                                                                  |                                         |

| 4       | Txin      | TXIN is the Tx input to the diplexer. The input frequency range spans 5-42 MHz.                                                                                                                                  | 4                                       |

| 5       | N/C       |                                                                                                                                                                                                                  |                                         |

| 6       | N/C       |                                                                                                                                                                                                                  |                                         |

| 7       | Vcc2 (Rx) | The Vcc2 (Rx) pin powers the loop filter for the first LO. A bias of 24 V - 30 V is required and maximum current draw is 2 mA.                                                                                   |                                         |

| 8       | Vcc1 (Rx) | The Vcc1 (Rx) pin powers the entire Rx section. A bias of 5 V is required and nominal current draw is 250 mA.                                                                                                    |                                         |

| 9       | IFAGC     | The IFAcc pin is used to adjust gain in the final downconverter stage of the Rx section. The pin has a positive gain vs. AGC slope. 30 dB of gain control is available by varying the voltage from 0.5 to 2.0 V. | (9) 1 K                                 |

| 10      | GND       | Ground.                                                                                                                                                                                                          |                                         |

# ISG1000

# **PIN FUNCTIONS**

| Pin No. | Pin Name | Description                                                                                                                                                                               | Equivalent Circuit            |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

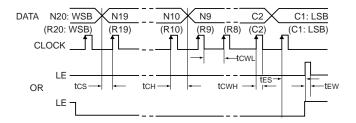

| 11      | CLK      | Clock pin for the dual PLL. High impedance CMOS input. Data for the various latches is clocked in on the rising edge into a 20-bit shift register.                                        |                               |

| 12      | DATA     | Serial data pin for the dual PLL. High impedance CMOS input. MSB entered first. The last two bits are the control bits.                                                                   |                               |

| 13      | LDEN     | Latch enable pin for the dual PLL. High impedance CMOS input. When LE goes HIGH, data stored in the shift registers is loaded into one of the 4 latches determined by the 2 control bits. |                               |

| 14      | GND      | Ground.                                                                                                                                                                                   |                               |

| 15      | IFout+   | Non-inverting final IF output.                                                                                                                                                            | - 1 240 5.6 μH<br>39 p        |

| 16      | IFout-   | Inverting final IF output.                                                                                                                                                                | 240 5.6 µH<br>39 p = 68 p = 1 |

### Note

# FIGURE 1

<sup>1.</sup> For programming information, refer to National LMX2336 data sheet (http://www.national.com)

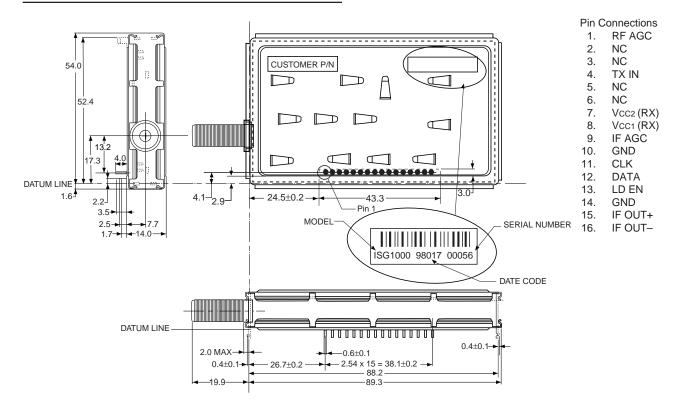

# **OUTLINE DIMENSIONS** (Units in mm)

**Table 1. Programmable Modes**

| C1 | C2 | R16       | R17      | R18       | R19    | R20    |

|----|----|-----------|----------|-----------|--------|--------|

| 0  | 0  | RF2 Phase | RF2 Icpo | RF2 Do    | RF2 LD | RF2 Fo |

|    |    | Detector  | -        | TRI-STATE |        |        |

|    |    | Polarity  |          |           |        |        |

| 0  | 1  | RF1 Phase | RF1 ICP  | RF1Do     | RF1 LD | RF1 Fo |

|    |    | Detector  |          | TRI-STATE |        |        |

|    |    | Polarity  |          |           |        |        |

| C1 C2  |   | N19           | N20      |  |

|--------|---|---------------|----------|--|

| 1      | 0 | RF2 Prescaler | Pwdn RF2 |  |

| 1 1 RF |   | RF1 Prescaler | Pwdn RF1 |  |

**Table 2. Mode Select Truth Table**

|   | Phase<br>Detector<br>Polarity <sup>3</sup> |                     | ICP <sub>O</sub> <sup>1</sup> | RF1<br>Prescaler | RF2<br>Prescaler | Pwdn <sup>2</sup> |

|---|--------------------------------------------|---------------------|-------------------------------|------------------|------------------|-------------------|

| 0 | Negative                                   | Normal<br>Operation | LOW                           | 64/65            | 64/65            | pwrd up           |

| 1 | Positive                                   |                     | HIGH                          | 128/129          | 128/129          | pwrd dn           |

# Notes:

- The ICP<sub>O</sub> LOW Current State = 1/4 x ICP<sub>O</sub> HIGH Current.

- 2. Activitation of the RF2 PLL or RF1 PLL powerdown modes result in the disabling of the respective N counter divider and debiasing of its respective fin inputs (to a high impedance state). The powerdown function is gated by the charge pump to prevent unwanted frequency jumps. Once the powerdown program mode is loaded, the part will go into powerdown mode when the charge pump reaches a TRI-STATE condition. The R counter and Oscillator functionality does not become disabled until both RF2 and RF1 powerdown bits are activated. The OSCIN is connected to Vcc through a 100 kΩ resistor and the OSCOUT goes HIGH when this condition exists. The MICROWAVE<sup>TM</sup> control register remains active and capable of loading and latching data during all the powerdown modes.

- Phase Detector Polarity

Depending upon VCO characteristics, the R16 bits should be set accordingly:

When VCO characteristics are positive like (1), R16 should be set HIGH, when VCO characteristics are negative like (2), R16 should be set LOW.

# VCO CHARACTERISTICS (1) (2) VCO Input Voltage

**Table 3. The FoLD Output Truth Table**

| RF1 R (19)<br>(RF1 LD) | RF2 R (19)<br>(RF2 LD) | RF1 R (20)<br>(RF1 Fo) | RF2 R (20)<br>(RF2 Fo) | FoLD<br>Output State                  |

|------------------------|------------------------|------------------------|------------------------|---------------------------------------|

| 0                      | 0                      | 0                      | 0                      | Disabled <sup>1</sup>                 |

| 0                      | 1                      | 0                      | 0                      | RF2 Lock<br>Detect <sup>2</sup>       |

| 1                      | 0                      | 0                      | 0                      | RF1 Lock<br>Detect <sup>2</sup>       |

| 1                      | 1                      | 0                      | 0                      | RF1/RF2<br>Lock Detect <sup>2</sup>   |

| X                      | 0                      | 0                      | 1                      | RF2 Reference<br>Divider Output       |

| X                      | 0                      | 1                      | 0                      | RF1 Reference<br>Divider Output       |

| Х                      | 1                      | 0                      | 1                      | RF2<br>Programmable<br>Divider Output |

| Х                      | 1                      | 1                      | 0                      | RF1<br>Programmable<br>Divider Output |

| 0                      | 0                      | 1                      | 1                      | Fastlock <sup>3</sup>                 |

| 0                      | 1                      | 1                      | 1                      | For internal use only                 |

| 1                      | 0                      | 1                      | 1                      | For internal use only                 |

| 1                      | 1                      | 1                      | 1                      | Counter Reset <sup>4</sup>            |

X - Don't care condition

### Notes:

- When the FoLD output is disabled, it is actively pulled to a low logic state.

- Lock detect output provided to indicate when the VCO frequency is in "lock". When the loop is locked and a lock detect mode is selected, the pin's output is HIGH, with narrow pulses LOW. In the RF1/RF2 lock detect mode a locked condition is indicated when RF2 and RF1 are both locked.

- The Fastlock mode utilized the FoLD output pin to switch a second loop filter damping resistor to ground during fastlock operation. Activation of Fastlock occurs whenever the RF loop's Icpo magnitude bit #17 is selected HIGH (while the #19 and #20 mode bits are set for Fastlock).

- 4. The Counter Reset mode bits R19 and R20 when activated reset all counters. Upon removal of the Reset bits the N counter resumes counting in "close" alignment with R counter. (The maximum error is one prescaler cycle). If the Reset bits are activated the R counter is also forced to Reset, allowing smooth acquisition upon powering up.

# **Serial Data Input Timing**

### Notes

- Parenthesis data indicates programmable reference divider data.

- 2. Data shifted into register on clock rising edge.

- 3. Data is shifted in MSB first.

### Test Conditions:

The Serial Data Input Timing is tested using a symmetrical waveform around Vcc/2. The test waveform has an edge rate of 0.6V/ns with amplitudes of 2.2 V @ Vcc = 2.7 V and 2.6 V @ Vcc = 5.5 V.

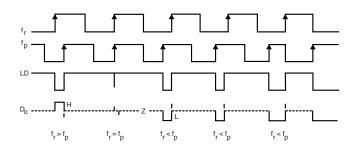

# Phase Comparator and Internal Charge Pump Characteristics.

### Notes:

- 1. Phase difference detection range:  $-2\pi$  to  $+2\pi$

- 2. The minimum width pump up and pump down current pulses occur at the Do pin when the loop is locked.