# Helium

Virata

Product Profile

Data Sheet June 2000

#### **KEY FEATURES**

- ATM switching and layer 2/3 processing device

- USB interfaces for external modem applications

- Utopia—1/2 and ADSL T1.413 interfaces

- ► Ethernet—10baseT interface

- Dual ARM RISC processor architecture

# **Product Applications**

- xDSL modem

- xDSL gateway

- Cable modem

- ATM line cards

- ATM access

- ATM SCU/DSU

- Bridging and routing

# **Description**

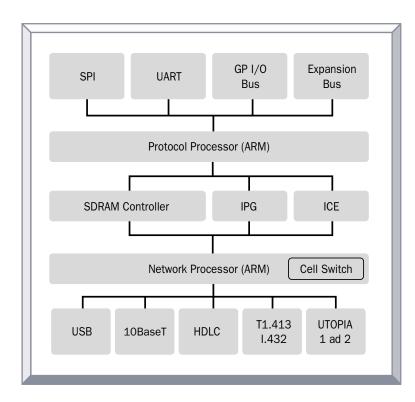

Helium is a single chip, highly integrated ATM switching and layer 2/3 processing device. A general purpose RISC Protocol Processor runs higher layer protocols while a high performance microcoded RISC Network Processor is used for cell and frame handling at up to 75Mbps switched traffic.

Integrating many common interface functions, Helium is designed for flexible, low cost, high functionality, high performance products. It may be used in gateway, ATM access device, or USB modem customer premises equipment (CPE) or central office (CO) with its wide operating range and single supply 3.3V operating voltage.

Helium contains a Network Processor that controls the direct connections to Ethernet and USB, as well as physical interfaces for Utopia 1 and 2, HDLC and ADSL T1.413.

The Network Processor has 8K of microcode RAM and a high-speed interface to external SDRAM. This supports both ATM cells and packets, OAM cell handling, policing, shaping and accounting.

**Figure 1. Helium System Interfaces**

The two processors communicate via the inter-processor gateway IPG.

Helium is the second member of Virata's ATOM architecture and runs the complete suite of ATMOS $^{\text{\tiny{M}}}$  software, including support for routing, bridging, signaling, and SNMP Management.

Software flexibility, high integration, and built-in hardware debugging (ICE) support allow rapid product development.

This combination of hardware and software, Integrated Software on Silicon, ISOS™ provides a unique time-to-market advantage.

## **Reference Platform**

The BD 3000 is the development reference platform for Helium, providing a wealth of hardware and software debug tools to assist partners in rapid development and deployment of their products. Training, documentation, and support are also available.

# **Specifications**

#### **Processors**

- Protocol Processor (PP) is a 48 MHz ARM7TDMI RISC core, which includes a 4K cache providing:

- Modem PHY Management (depending on application)

- Initialization code

- Soft real-time tasks

- Network Processor (NP) is a 48 MHz ARM7TDMI RISC core with 8K of SRAM performing:

- Data Transfer

Framing

Interleaving

CRC Generation

Switching

- · Hard real-time tasks

#### **USB**

USB slave interface—up to 12 Mbps using Control, Interrupt, Bulk, and Isochronous endpoints and transfers.

#### 10BaseT Ethernet

Helium contains a 10baseT Ethernet MAC with integrated PHY.

#### Utopia

## **Interfaces**

- USB

- 10baseT ethernet

- Utopia 1/2

- HDLC/T1.413

- GPOS

- Expansion bus

- UART

- SDRAM

- Flash PROM

- EEPROM

- Utopia 1 and 2 (master/slave) interfaces with 14 ports, configuration

- 8 ports dual-latency, or

- 2 ports dual-latency and 12 ports single latency

#### **ADSL**

ADSL full duplex data interface to external ADSL PHY. Helium implements all the framing requirements 1.432 of T1.413.

#### **HDLC**

The HDLC interface, using the same pins as ADSL, conforms to Q.921 at a frame rate of 20MHz with a 16-bit CRC generation.

#### **GPIO**

The General Purpose I/O bus contains 12 pins. Of these pins, two are used for the UART serial interface (Tx and Rx at a speed of 38,462 baud), and three for the serial boot EEPROM (data in, data out, and clock). Five pins can also be configured as Ethernet status indicators. Four of the GPIO pins can be used as chip selects when used with the Expansion bus.

#### **SDRAM**

SDRAM interface conforms to JEDEC requirements, supporting address space from 2 to 32 Mbytes with a selectable 16- or 32-bit wide data bus.

## **Expansion Bus**

Configurable as 8- or 16-bit peripheral bus, which can support 8-bit Motorola, 16-bit Intel or 16-bit multiplexed modes. Mainly used to control external devices and boot Helium from memory, ROM or Flash PROM. Up to 4 devices supported (using 4 GPIO pins as chip select) or more with additional decoder.

#### **Boot Options**

- USB interface

- Serial EEPROM

- **■** UART

- Flash PROM

- Ethernet Network Boot

## **Software**

Helium's Protocol Processor runs Virata's extensive networking software suite, including:

- ATM device driver

- IP routing

- Bridging

- PPTP, L2TP

- RFC1483 PVC/SVC

- Classical IP PVC/SVC

- PPP over ATM PVC/SVC

- Q.2931

- SSCOP

- UNI 3.0, 3.1, 4.0 signaling

- SNMP, TFTP, telnet, BOOTP

- AAL5 SAR

- ATM pacing, policing and OAM

- ATMOS lightweight real-time kernel

## **Package**

208 pin PQFP

# **Environmental**

Supply 3.3V, +/- 10% Commercial temperature range of 0 to +70 degrees Centigrade

## **Ordering Information**

VC8410-PAC, Helium IC BD3000, Helium Development Board Data book available on request D0-007133-PS

#### TRADEMARKS/COPYRIGHT

ATMOS, ISOS, Helium and Virata are trademarks of Virata. All other trademarks acknowledged. Copyright © Virata 1999, 2000.

Virata has made commercially reasonable efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by Virata for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Virata and implies no license under patents, copyrights, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form of any means, electronic, photographic, or otherwise, or used as the basis for manufacture or sale of any items without the prior written consent of Virata.