Advance Information

# FSK Receiver On A Chip 860-928 MHz Frequency Agile With SPI Bus Interface

### **Features**

- High Level of Integration Minimizes System Cost

- Data Rates from 4 to 128.8 Kbits/Sec

- Direct Connection To Microprocessor

- Adjustable detection bandwidths, data rates

- Adjustable gain, detection level/ hysterisis

- Low and high beta FSK detection modes

- Integrated Manchester decoding

- Programmable Frequency And Rx/Standby Modes

- Operates From Single 2.5V Power Supply

- Surface Mount Leadless Plastic Packaging

## **Description**

The Honeywell HRF-ROC093XR is a single chip receiver for use in digital data applications. Direct microprocessor connection for control and data transfer, eliminate the need for additional ICs, while integrated data code/decode reduces the instruction set requirements on the microprocessor. The HRF-ROC093XR is ideally suited for use in battery powered wireless applications in conjunction with microprocessors for data communication. Adjustable data rates, filter bandwidths and detection levels allow the IC to be used in a wide variety of high sensitivity / high EMI environments.

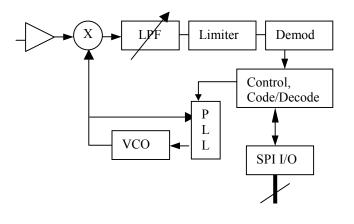

### **Functional Schematic**

#### **Product Photo**

Web Site: www.mysoiservices.com Email: mysoiservices@honeywell.com

2002 09325XR Published June 2002 Page 1

Honeywell Solid State Electronics Center 12001 State Highway 55 Plymouth, Minnesota 55441-4799 1-800-323-8295

**Advance Information**

## RF Electrical Specifications @ + 25°C

| Parameter          | Test Condition                               | Frequency     | Minimum | Typical | Maximum | Units |

|--------------------|----------------------------------------------|---------------|---------|---------|---------|-------|

| Rx Sensitivity     |                                              | 860– 928 MHz  |         | -95     |         | dBm   |

| 1db Compression    | Vdd = 2.5V                                   | 860– 928 MHz  |         | -30     |         | dBm   |

| Input IP3          | Vdd = 2.5V                                   | 860– 928 MHz  |         | -5      |         | dBm   |

| Data Rate, Tx / Rx | Continuous Packeted Data                     |               |         | 128     |         | Kbps  |

| Channel Rejection  | Adjacent Channels                            | Fc +/- 350KHz |         | 60      |         | dB    |

| Max Detection BW   | IQ Baseband Filter                           |               |         | 250     |         | KHz   |

|                    | Passband                                     |               |         |         |         |       |

| Control/Data I/O   | Serial Peripheral Interface (SPI). Direct    |               |         | 10      |         | MHz   |

|                    | Connection To Microcontroller/Microprocessor |               |         |         |         |       |

<sup>\*</sup> Adjustable bandwidth reduction using off chip elements

# DC Electrical Specifications @ + 25°C

| Parameter                                                  | Minimum | Typical | Maximum  | Units |

|------------------------------------------------------------|---------|---------|----------|-------|

| V <sub>DD</sub> Power Supply Voltage                       | 2.4     | 2.5     | 2.6      | V     |

|                                                            |         |         |          |       |

| Power Supply Current (I <sub>DD</sub> ) During Rx (915MHz) | 22      | 28      |          | mA    |

| Standby Current Consumption                                |         | <1      |          | uA    |

| CMOS Logic Level (0)                                       | 0       |         | 0.7      | V     |

| CMOS Logic Level (1)                                       | 1.7     |         | $V_{DD}$ | V     |

# **Absolute Maximum Ratings<sup>1</sup>**

| Parameter                      | Absolute Maximum | Units     |

|--------------------------------|------------------|-----------|

| Maximum Input Power            | -                | -         |

| $V_{DD}$                       | + 2.8            | V         |

| ESD Voltage (Human Body Model) | 200              | V         |

| Operating Temperature          | - 40 to + 85     | Degrees C |

| Storage Temperature            | - 40 to + 150    | Degrees C |

(Note 1) Operation Of The HRF-ROC093XR Beyond Any Of These Parameters May Cause Permanent Damage.

**ESD Protection:** The HRF-ROC093XR Contains reduced ESD Protection Circuitry for sensitive RF I/O. Precautions Should Be Taken During Handling/Assembly Until Protected By External Circuitry or Housings

Web Site: www.mysoiservices.com Email: mysoiservices@honeywell.com

2002 09325XR Published June 2002 Page 2

Honeywell Solid State Electronics Center 12001 State Highway 55 Plymouth, Minnesota 55441-4799 1-800-323-8295

**Advance Information**

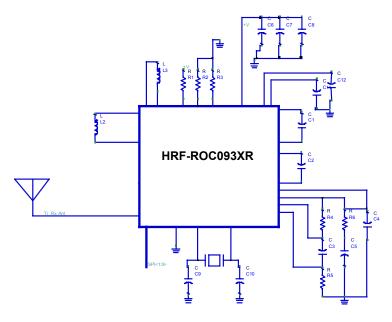

## **Typical Application**

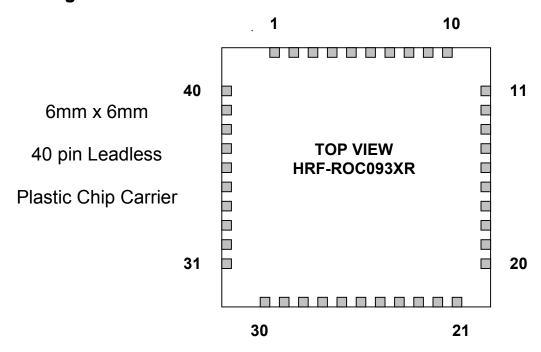

## **Package Outline**

Low inductance RF/DC ground connection required below part as bottom ground pad is used for all device grounding. Additionally, this connection prodvides a direct connection to the die for enhanced thermal dissipation. Package shown not to scale.

Web Site: Email:

www.mysoiservices.com mysoiservices@honeywell.com

2002 09325XR

Published June 2002 Page 3

Honeywell **Solid State Electronics Center** 12001 State Highway 55 Plymouth, Minnesota 55441-4799 1-800-323-8295

Advance Information

# **Pin Configuration**

# HRF-ROC093XR 40Pin LPCC<sup>™</sup> (6 mm X 6 mm) Package Pin List \* RF/Digital ground is provided through backside slug pad.

| Name             | Pin # | Function                           | Name       | Pin # | Function                                                       |

|------------------|-------|------------------------------------|------------|-------|----------------------------------------------------------------|

| LNA Bias R       | 1     | Bias resistor for LNA: ~ 16K       |            | 21    | SPI slave select                                               |

|                  |       |                                    | SPI_SSN_   |       |                                                                |

|                  |       |                                    | in         |       |                                                                |

| LNA Input        | 2     | LNA input                          |            | 22    | SPI clock                                                      |

|                  |       |                                    | SPI_CLK_   |       |                                                                |

|                  |       |                                    | in         |       |                                                                |

| Digital Gain     | 3     | Vp, high gain; gnd low gain        |            | 23    | SPI serial data output                                         |

| Control          |       |                                    | SPI_data_  |       |                                                                |

| ***              | 1     | T > T   1                          | out        | 2.4   | CDV                                                            |

| Vp               | 4     | LNA supply                         | CDI DIT    | 24    | SPI interrupt output                                           |

|                  |       |                                    | SPI_INT_   |       |                                                                |

| V.               | 5     | INIA complex                       | out        | 25    | A sum or data sustant bucComed in alarity                      |

| Vp               | 3     | LNA supply                         | Rx_out_p   | 23    | Async data output buffered, polarity selected, for board debug |

| Vp               | 6     | Mixer supply                       | Vp         | 26    | Digital positive supply                                        |

| I mixer bias     | 7     | Sensitivity/IP3 adjust, 10K res to | Hysterisis | 27    | Four level widow select, 2 bit digital                         |

| I IIIIXEI DIAS   | /     | gnd                                | A          | 27    | Four level widow select, 2 bit digital                         |

| Q mixer bias     | 8     | Sensitivity/IP3 adjust             | Hysterisis | 28    | (( ))                                                          |

| Q IIIIXCI Dias   | 0     | Schsitivity/II 3 adjust            | B          | 20    |                                                                |

| I filter bw 1    | 9     | Data bandwidth reduction           | P_test_out | 29    | Pll N-counter output                                           |

| I filter bw 2    | 10    | Con Carlot Victor Feddellon        | R_test_out | 30    | Pll R-counter out                                              |

| Q filter bw 1    | 11    | ((;)                               | Crystal 2  | 31    | reference crystal connection                                   |

| Q filter bw 2    | 12    | (())                               | Crystal 1  | 32    | reference crystal connection                                   |

| Vp               | 13    | Analog electronics supply          | Pdout      | 33    | Phase detector charge pump output                              |

| Supply filtering | 14    | Common mode voltage filtering      | Rext PLL   | 34    | PLL bias resistor                                              |

| Raw data         | 15    | Raw detected data / predetect data | Vp         | 35    | Phase detector supply                                          |

|                  |       | shaping                            | F          |       | and an array                                                   |

| Detection level  | 16    | Detection level monitor/filtering  | varactor   | 36    | VCO varactor for freq tuning                                   |

| Mixer ref        | 17    | Baseband ref voltage bypass        |            | 37    | VCO external tank connection                                   |

| _                |       |                                    | VCO_tank   |       |                                                                |

|                  |       |                                    | 1          |       |                                                                |

| Resetn           | 18    | Dig power-on reset                 |            | 38    | VCO external tank connection                                   |

|                  |       |                                    | VCO_tank   |       |                                                                |

|                  |       |                                    | 2          |       |                                                                |

| SPI_data_in      | 19    | SPI serial data input              | NC         | 39    |                                                                |

| Dig_data_in      | 20    | Dig FIFO RX data                   | NC         | 40    |                                                                |

Web Site: www.mysoiservices.com Email: mysoiservices@honeywell.com

2002 09325XR Published June 2002 Page 4

Advance Information

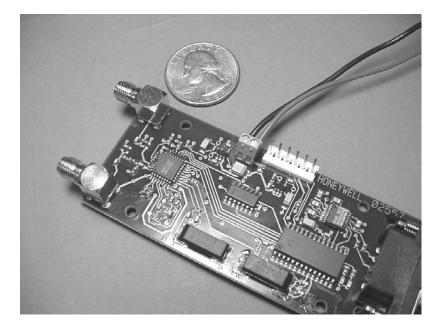

## **Engineering Evaluation Board**

The engineering evaluation board provides for a RS232 connection using a PIC microcontroller as the interface between the HRF-ROC093XR and the RS232 port. Using the software provided and a PC, control of test data, operating frequency, power levels and all internal registers is available for early product development/prototyping. The board operates from a single +6 to +9 volt supply and provides separate RF Rx/Tx ports.

### **Ordering Information**

| Ordering Number | Product                                 |  |  |

|-----------------|-----------------------------------------|--|--|

| HRF-ROC093XR -B | Delivered In Chip Tubes                 |  |  |

| HRF-ROC093XR -T | Delivered On Tape And Reel <sup>2</sup> |  |  |

| HRF-ROC093XR -E | Engineering Evaluation Board            |  |  |

Note 2: Contact Honeywell for details

Honeywell reserves the right to make changes to improve reliability, function or design. Honeywell does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Web Site: www.mysoiservices.com Email: mysoiservices@honeywell.com

2002 09325XR Published June 2002 Page 5