# RF Sigma-Delta Fractional-N / IF Integer-N / Low Power Frequency Synthesizer With Integrated RF VCOs

#### ■ Features

- Full CMOS dual-band RF synthesizer

- Full CMOS IF synthesizer

- Integrated VCOs, Loop Filters, Varactors, and Resonators

- . Minimal External Components Required

- 2.7V to 3.6V operation

- . Low current consumption

- Low Phase Noise

- . Selectable or programmable power-save mode

- Small 24 pin LGA (Leadless Grid Array) package

## Applications

- Dual-band communications

- Cordless telephone systems

- Portable wireless communications GSM, DCS1800, PCS1900 cellular systems AMPS and cellular (900MHz) CDMA PCS (Korean PCS and US PCS) CDMA

- Wireless local area networks (WLANs)

- Cable TV tuners(CATV)

- Other wireless communication systems

## ■ General Description

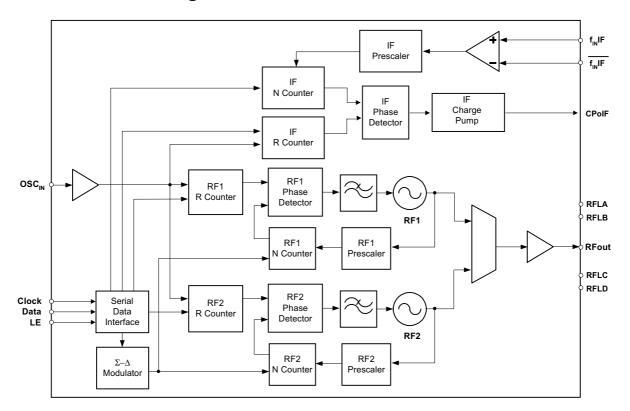

The HM6F5221 of full CMOS monolithic, both IF and dual-band RF synthesizer is to be used as a local oscillator for RF and IF of a dual conversion transceiver. It is fabricated using HYNIX semiconductor's mixed-signal/RF CMOS process.

HM6F5221 contains two VCOs, loop filters, regulators, reference and VCO dividers, charge pumps, and phase detectors. HM6F5221 performs Fractional-N frequency for RF synthesis and Integer-N frequency for IF synthesis. Serial data is transferred into the HM6F5221 via three-wire interface (Data, Enable, and Clock).

## **■** Functional Block Diagram

# Contents

| <u>Section</u>                                      | <u>Page</u> |

|-----------------------------------------------------|-------------|

| ■ Pin Assignment                                    | 4           |

| ■ Pin Descriptions ·····                            | 4           |

| ■ Absolute Maximum Ratings                          | 6           |

| ■ Electrostatic Characteristics                     | 6           |

| ■ Recommended Operating Conditions                  | 6           |

| ■ Electrical Characteristics                        | ······ 7    |

| ■ Charge Pump Current Specification Definitions     | 9           |

| ■ Functional Description                            | 10          |

| POWER ON RESET                                      | -           |

| REFERENCE OSCILLATOR INPUTS                         |             |

| REFERENCE DIVIDER                                   |             |

| PROGRAMMABLE DIVIDER ······                         |             |

| PRESCALER ·····                                     |             |

| FRACTIONAL COMPENSATION                             |             |

| SERIAL INTERFACE ······                             | -           |

| POWER CONTROL ·····                                 |             |

| PFD and CP·····                                     |             |

| ■ Programming Description                           |             |

| INPUT DATA REGISTER ·····                           |             |

| PROGRAMMABLE REFERENCE DIVIDERS                     |             |

| IF_R REGISTER·····                                  |             |

| Fout / Lock Detect Programming Bits - (FoLD) ······ | 14          |

| RF_R REGISTER······                                 |             |

| PROGRAMMABLE DIVIDER ······                         |             |

| IF_N REGISTERS ······                               |             |

| RF_N REGISTER······                                 |             |

| ■ Program Mode Control ·····                        |             |

| REFERENCE OSCILLATOR INPUT and POWER DOWN CONTROL   |             |

| ■ Application Example                               | 20          |

| ■ Serial Data Input Timing                          | 21          |

| ■ Package Outline ·····                             | 22          |

# **Table of Contents**

| <u>Table</u> | <u>Page</u>                                                                                   |

|--------------|-----------------------------------------------------------------------------------------------|

| Table.1      | Control Bit Map (CTL[1:0])12                                                                  |

| Table.2      | Data Bit Map (DATA[23:2])12                                                                   |

| Table.3      | Binary 15-Bit Programmable IF R Divider Ratio (R Counter) (IF_R[16] –IF_R[2])13               |

| Table.4      | IF Charge Pump and Phase Frequency Control - (IF_CP) (IF_R[18:17])13                          |

| Table.5      | IF Power Down and Power Down Mode - (IF_PWDN) (IF_R[20:19])13                                 |

| Table.6      | Binary 11-Bit Programmable Fractional Denominator K Divider Ratio (K Counter) (RF_R[12:2]) 14 |

| Table.7      | Binary 2-Bit Programmable RF R Divider Ratio (RF R Counter) (RF_R[14:13])14                   |

| Table.8      | RF Charge Pump and Phase Frequency Detector Control - (RF_CP) (RF_R[17:16])15                 |

| Table.9      | RF Power Down and Power Down Mode - (RF_PWDN) (RF_R[21:20])15                                 |

| Table.10     | Fout / Lock Detect Programming Truth Table - (FoLD) (IF_R[23:22] / RF_R[23:22]) ·······15     |

| Table.11     | Binary 6-Bit Programmable Swallow Counter Division Ratio (IF A Counter) (IF_N[7:2])16         |

| Table.12     | Binary 12-Bit Programmable IF Main Counter Division Ratio (IF B Counter) (IF_N[19:8])16       |

| Table.13     | IF Prescaler Select - (PRE) (IF_N[22])17                                                      |

| Table.14     | IF Frequency Divider Select - (IFSW) (IF_N[23])17                                             |

| Table.15     | Binary 11-Bit Programmable Fractional Numerator F Divider Ratio (F Counter) (RF_N[12:2]) 17   |

| Table.16     | Binary 4-Bit Programmable Swallow Counter Division Ratio (RF A Counter) (RF_N[16:13])···18    |

| Table.17     | Binary 5-Bit Programmable RF Main Counter Division Ratio (RF B Counter) (RF_N[21:17]) ··· 18  |

| Table.18     | RF Prescaler Select - (PRE) (RF_N[22]) ···········오류! 책갈피가 정의되어 있지 않습니다.                      |

| Table.19     | RF Frequency Band Select - (RFSW) (RF_N[23])18                                                |

| Table.20     | Reference Oscillator Input and Power Down Control19                                           |

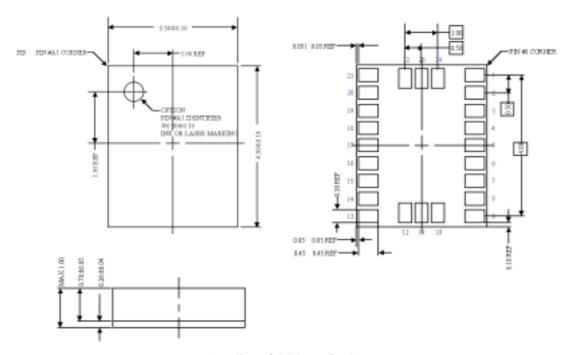

# ■ Pin Assignment

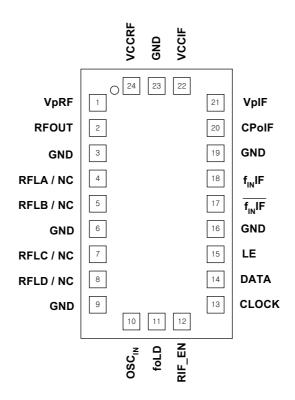

Leadless Grid Array Package

# **■** Pin Descriptions

| Pin No.<br>HM6F5221<br>24-pin LGA<br>Package | PIN NAME  | I/O | Description                                                                    |

|----------------------------------------------|-----------|-----|--------------------------------------------------------------------------------|

| 1                                            | VpRF      | -   | Power Supply for RF charge pump. Must be ≥ VCCRF.                              |

| 2                                            | RFOUT     | 0   | VCO output frequency for RF1 or RF2.                                           |

| 3                                            | GND       | -   | Ground Pin.                                                                    |

| 4                                            | RFLA / NC | I/O | RF1 center frequency control pin using external inductor connected to RF1 VCO. |

| 5                                            | RFLB / NC | I/O | RF1 center frequency control pin using external inductor connected to RF1 VCO. |

| 6                                            | GND       | -   | Ground Pin.                                                                    |

| 7                                            | RFLC / NC | I/O | RF1 center frequency control pin using external inductor connected to RF2 VCO. |

| 8                                            | RFLD / NC | I/O | RF1 center frequency control pin using external inductor connected to RF2 VCO. |

| 9                                            | GND       | -   | Ground Pin.                                                                    |

# ■ Pin Descriptions (continued)

| Pin No.<br>HM6F5221<br>24-pin LGA<br>Package | PIN NAME          | I/O | Description                                                                                                                                                                                                                                                                       |

|----------------------------------------------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                                           | OSC <sub>IN</sub> | I   | Oscillator input to drive both the IF and RF R counter inputs.                                                                                                                                                                                                                    |

| 11                                           | foLD              | 0   | Multiplexed output of the RF/IF programmable or reference dividers, and RF/IF lock detect signals.                                                                                                                                                                                |

| 12                                           | RIF_EN            | I   | RF/IF PLL Enable (Enable when HIGH, Power down when LOW). Controls both the RF and IF PLL to power down directly. Also set the charge pump output to be in TRI-STATE when LOW. Powers up when HIGH depends on the state of RF_PWDN or IF_PWDN.                                    |

| 13                                           | CLOCK             | I   | High impedance CMOS Clock input. Data for the various counters is clocked in on the rising edge, into the 24-bit shift register.                                                                                                                                                  |

| 14                                           | DATA              | I   | Binary serial data input. Data entered MSB first. The last two bits are the control bits. High impedance CMOS input.                                                                                                                                                              |

| 15                                           | LE                | I   | Load enable high impedance CMOS input. When <b>LE</b> goes HIGH.                                                                                                                                                                                                                  |

| 16                                           | GND               |     | Ground Pin.                                                                                                                                                                                                                                                                       |

| 17                                           | finIF/            | I   | IF Prescaler complementary input. For a single-ended output IF VCO, a bypass capacitor should be placed as close as possible to this pin.                                                                                                                                         |

| 18                                           | finIF             | I   | IF prescaler input. Small signal input from the VCO.                                                                                                                                                                                                                              |

| 19                                           | GND               | -   | Ground Pin.                                                                                                                                                                                                                                                                       |

| 20                                           | CPoIF             | 0   | Internal IF charge pump output. For connection to a loop filter for driving the input of an external VCO.                                                                                                                                                                         |

| 21                                           | VpIF              | -   | Power Supply for IF charge pump. Must be ≥ <b>VCCIF</b> .                                                                                                                                                                                                                         |

| 22                                           | VCCIF             | -   | Power supply voltage input for IF analog, IF digital, data interface, foLD and oscillator circuits. Input may range from 2.7V to 3.6V. VCCIF must equal VCCRF. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane. |

| 23                                           | GND               |     | Ground Pin.                                                                                                                                                                                                                                                                       |

| 24                                           | VCCRF             | -   | Power supply voltage input for RF analog and RF digital circuits. Input may range from 2.7V to 3.6V. <b>VCCRF</b> must equal <b>VCCIF</b> . Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                    |

## ■ Absolute Maximum Ratings

| Characteristics                     | Symbol | Value          | Unit |

|-------------------------------------|--------|----------------|------|

| Power Supply Voltage                | VCC    | -0.3 ~ +4.2    | V    |

| 1 ower ouppry voltage               | VPP    | -0.3 ~ +4.2    | V    |

| Voltage on any pin with GND=0 volts | Vi     | -0.3 ~ VCC+0.3 | V    |

| Storage Temperature Range           | Ts     | -55 ~ +150     | °C   |

| Lead Temperature                    | TL     | 260            | °C   |

CAUTION: Stress above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. Other conditions above those indicated in the operational sections of this specification are not implied.

## **■** Electrostatic Characteristics

| Characteristics     | Pin NO. | ESD Level | Unit |

|---------------------|---------|-----------|------|

| Human Body Model    | All     | T.B.D.    | V    |

| Machine Model       | All     | T.B.D.    | V    |

| Charge Device Model | All     | T.B.D.    | V    |

CAUTION: This Device is high performance RF integrated circuit and is ESD sensitive. Handling and assembly of this device should only be done at ESD free workstations.

## **■** Recommended Operating Conditions

| Characteristics                 | Symbol          | Min      | Тур | Max | Unit |

|---------------------------------|-----------------|----------|-----|-----|------|

| Power Supply Voltage            | VCC             | 2.7      | 3.0 | 3.6 | V    |

| Power Supply Voltage Difference | VΔ<br>(VCC-VPP) | -0.3     | -   | 0.3 | V    |

| Operating Temperature           | T <sub>A</sub>  | -40 ~ 85 |     |     | °C   |

CAUTION: All specification are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

Rev. 0.3.0

6

## **■** Electrical Characteristics

VCC = 3.0V, -40°C <  $T_A$  < 85°C, Except as Specified

| Symbol                | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Conditions                                             | Min                  | Тур | Max                 | Units    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------|-----|---------------------|----------|

| General               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                      | <b>'</b>             |     | 1                   |          |

| V <sub>CC</sub>       | Dower Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        | 2.7                  | 3.0 | 3.6                 | V        |

| V <sub>PP</sub>       | Fower Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        | 2.7                  | 3.0 | 3.6                 | V        |

|                       | Total Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RF1 and IF                                             | -                    | 18  | 24                  | mA       |

| . 1                   | RF1 Mode Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{\rm CC}$ =2.7V to 3.6V, RF1 @ , $f_{\Phi}$ = 10KHz | -                    | 13  | 17                  | mA       |

| Icc <sup>1</sup>      | Power Supply Voltage  Total Supply Current  RF1 Mode Supply Current  RF2 Mode Supply Current  IF Mode Supply Current  IF Mode Supply Current  Power down Current  Perence Oscillator Inputs  Oscillator Input Surrent  Oscillator Input Current  Oscillator Input Current  Ital Inputs²  High Level Input Voltage  Low Level Input Current  Low Level Input Current  Ital Outputs²  High-Level Output Voltage  Low-Level Output Voltage  Low-Level Output Voltage  Clock Cycle Time  Clock Rise Time  Clock Fall Time  Data Setup Time to Clock  Data Hold Time to Clock | $V_{CC}$ =2.7V to 3.6V, RF2 @ , $f_{\Phi}$ = 10KHz     | -                    | 12  | 17                  | mA       |

|                       | IF Mode Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{CC}$ =2.7V to 3.6V, IF @ , $f_{\Phi}$ = 10KHz      | -                    | 5   | 7                   | mA       |

| I <sub>CC-PWRDN</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>CC</sub> =3.0V                                  |                      | 1   | 10                  | μΑ       |

| Reference             | Oscillator Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                      |     | _                   | T        |

| fosc                  | Oscillator Frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        | 6                    | -   | 26                  | MHz      |

| Vosc                  | Oscillator Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC <sub>IN</sub>                                      | 0.5                  | -   | VCC<br>+0.3 V       | $V_{PP}$ |

| I <sub>IHR</sub>      | Oscillator Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>IH</sub> =V <sub>CC</sub> =3.6V                 | -                    | -   | 100                 | μΑ       |

| $I_{ILR}$             | Oscillator Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{IL}$ =0V, $V_{CC}$ =3.6V                           | -100                 | -   | -                   | μΑ       |

| Digital Inp           | outs <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                      |     |                     |          |

| V <sub>IH</sub>       | High Level Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | *                                                      | 0.8 V <sub>CC</sub>  | -   | -                   | V        |

| V <sub>IL</sub>       | Low Level Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | *                                                      | -                    | -   | 0.2 V <sub>CC</sub> | V        |

| I <sub>IH</sub>       | High Level Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>IH</sub> =V <sub>CC</sub> =3.6V*                | -1.0                 | -   | 1.0                 | μΑ       |

| I <sub>IL</sub>       | Low Level Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>IL</sub> =0V, V <sub>CC</sub> =3.6V*            | -1.0                 | -   | 1.0                 | μΑ       |

| Digital Ou            | tputs <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                      |     |                     |          |

| V <sub>OH</sub>       | High-Level Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>OH</sub> = -500 μA                              | V <sub>CC</sub> -0.4 | -   | -                   | V        |

| V <sub>OL</sub>       | Low-Level Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>OL</sub> = 500 μA                               | -                    | -   | 0.4                 | V        |

| Serial Dat            | a Control <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |                      |     |                     |          |

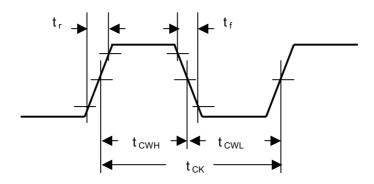

| t <sub>CK</sub>       | Clock Cycle Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | See Data Input Timing                                  | 40                   | -   | -                   | ns       |

| tr                    | Clock Rise Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See Data Input Timing                                  | -                    | -   | 50                  | ns       |

| t <sub>f</sub>        | Clock Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See Data Input Timing                                  | -                    | -   | 50                  | ns       |

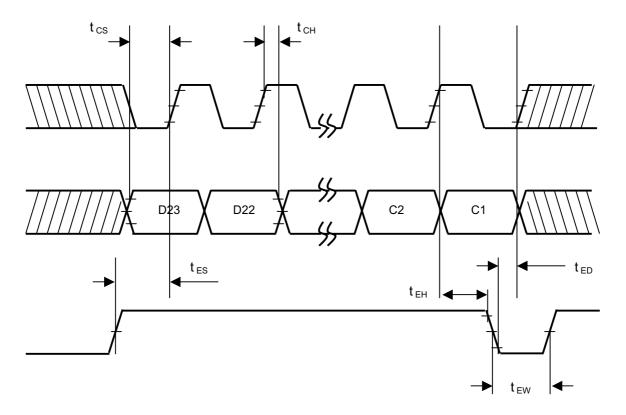

| tcs                   | Data Setup Time to Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | See Data Input Timing                                  | 5                    | -   | -                   | ns       |

| t <sub>CH</sub>       | Data Hold Time to Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | See Data Input Timing                                  | 0                    | -   | -                   | ns       |

| t <sub>CWH</sub>      | Clock Pulse Width High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | See Data Input Timing                                  | 10                   | -   | -                   | ns       |

| t <sub>CWL</sub>      | Clock Pulse Width Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | See Data Input Timing                                  | 10                   | -   | -                   | ns       |

| t <sub>ES</sub>       | Clock to Load Enable Setup Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See Data Input Timing                                  | 10                   | -   | -                   | ns       |

| t <sub>EH</sub>       | Clock to Load Enable Hold Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | See Data Input Timing                                  | 12                   | -   | -                   | ns       |

| t <sub>ED</sub>       | Load Enable to Clock Delay Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See Data Input Timing                                  | 12                   | -   | -                   | ns       |

| t <sub>EW</sub>       | Load Enable Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | See Data Input Timing                                  | 50                   | -   | -                   | ns       |

#### Notes:

- 1. RF1= 1.55GHz, RF2 = 1.2GHz, IF = 540MHz

- 2. For signal Clock, Data, LE, RIF\_EN, FoLD. Does not include  $f_{IN}RF$ ,  $f_{IN}IF$  and  $OSC_{IN}$ .

- 3. All timing is referenced to the 50% level of the waveform, unless otherwise noted.

# ■ Electrical Characteristics (Continued)

| Symbol           | Parameter <sup>1</sup>            | Conditions                     | Min  | Тур    | Max  | Units             |

|------------------|-----------------------------------|--------------------------------|------|--------|------|-------------------|

| RF Synthe        | esizer Characteristics            | L                              |      |        |      |                   |

| $f_\Phi$         | Internal Phase Detector Frequency | $f_{\Phi} = f_{OSC} / R$       | 6    | -      | 26   | MHz               |

| f <sub>CEN</sub> | RF1 VCO Center Frequency          | RF1 Active                     | 1530 | -      | 1780 | MHz               |

| f <sub>CEN</sub> | RF2 VCO Center Frequency          | RF2 Active                     | 954  | -      | 1230 | MHz               |

| f <sub>CEN</sub> | RF1 VCO Pushing                   |                                |      |        |      | MHz/V             |

|                  | RF2 VCO Pushing                   | Open Loop                      |      |        |      | MHz/V             |

|                  | RF1 VCO Pulling                   | VSWR = 2:1                     |      |        |      | MHz <sub>PP</sub> |

|                  | RF2 VCO Pulling                   | All Phases<br>Open Loop        | T    | .B.D ¯ | /    | MHz <sub>PP</sub> |

|                  | RF1 Phase Noise                   | 1.25 MHz offset<br>RFOUT =     |      | /      |      | DBc/Hz            |

|                  | DEC Phase Naise                   | 60 KHz offset<br>RFOUT =       |      |        |      | DBc/Hz            |

|                  | RF2 Phase Noise                   | 900 KHz offset<br>RFOUT =      |      |        |      | DBc/Hz            |

|                  | RF1 Harmonic Suppression          | 0                              |      | /      |      | dBc               |

|                  | RF2 Harmonic Suppression          | Second Harmonic                |      |        |      | dBc               |

|                  | DECLIE D                          | $Z_L = 50 \Omega$ , RF1 Active |      |        |      | dBm               |

|                  | RFOUT Power Level                 | $Z_L = 50 \Omega$ , RF2 Active |      |        |      | dBm               |

|                  | RF1 Output Reference Spurs        | Offset =                       |      |        |      | dBc               |

|                  | RF2 Output Reference Spurs        | Offset =                       |      |        |      | dBc               |

Note: 1. RF1 = 1.55GHz, RF2 = 1.2GHz, and IF = 540MHz for all parameters unless otherwise noted.

Rev. 0.3.0

8

## **■ Electrical Characteristics** (Continued)

| Symbol                                | Parameter                        | Conditions                                                       | Min  | Тур  | Max | Units |

|---------------------------------------|----------------------------------|------------------------------------------------------------------|------|------|-----|-------|

| IF Charge Pun                         | np                               |                                                                  | •    |      |     |       |

| I <sub>CPo-source IF</sub>            |                                  | $V_{Cpo} = V_p/2$ , IF_CP = 0                                    | -    | -100 | -   | μА    |

| I <sub>CPo-sink</sub> IF              | IF Charge Pump Output Current    | $V_{Cpo} = V_p/2$ , IF_CP = 0                                    | -    | 100  | -   | μΑ    |

| I <sub>CPo-source IF</sub>            | (See the Table.4)                | $V_{Cpo} = V_p/2$ , IF_CP = 1                                    | -    | -800 | -   | μΑ    |

| I <sub>CPo-sink</sub> IF              |                                  | V <sub>Cpo</sub> = V <sub>p</sub> /2, IF_CP = 1                  |      | 800  |     | μΑ    |

| I <sub>CPo-TRI</sub>                  | Charge Pump TRI_STATE Current    | $0.5 \le V_{CPo} \le V_{p}$ -0.5<br>-40°C \le T_A \le +85°C      | -2.5 | -    | 2.5 | nA    |

| I <sub>CPo</sub> vs. V <sub>CPo</sub> | CP Current vs. Voltage Variation | $0.5 \le T_A \le V_p$ -0.5<br>$T_A = 25$ °C, RF I <sub>CPo</sub> |      | 5    | 10  | %     |

| I <sub>CPo</sub> vs. Temp.            | CP Current vs. Temperature       | $V_{CPo} = V_p/2$ , RF $I_{CPo}$<br>-40°C $\leq T_A \leq +85$ °C |      | 8    |     | %     |

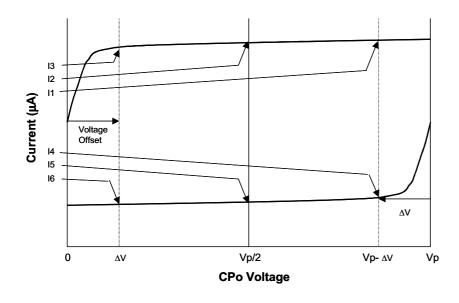

## **■** Charge Pump Current Specification Definitions

I1 = CP sink current at  $V_{\text{CPo}}$  =  $V_p$  -  $\Delta V$

$I2 = CP \text{ sink current at } V_{CPo} = V_p/2$

I3 = CP sink current at  $V_{CPo} = \Delta V$

I4 = CP source current at  $V_{CPo} = V_p - \Delta V$

I5 = CP source current at  $V_{CPo} = V_p/2$

I6 = CP source current at  $V_{CPo} = \Delta V$

$\Delta V$  = Voltage offset from positive and negative rails. Dependent on VCO tuning range relative to VCC and ground. Typical values are between 0.5V and 1.0V

#### Notes

$I_{CPo}$  vs.  $V_{CPo} = [1/2 * {||1|-||3|}] / [1/2 * {||1|+||3|}] * 100% and <math>[1/2 * {||4|-||6|}] / [1/2 * {||4|+||6|}] * 100%$

$I_{CPo-sink}$  vs.  $I_{CPo-source} = [ |I2|-|I5| ] / [ 1/2 * {|I2| + |I5|} ] * 100%$

$I_{CPo} \ vs. \ T_A = [\ |\ 12@temp\ |\ -\ |\ 12@25^{\circ}C\ |\ ]\ /\ |\ 12@25^{\circ}C\ |\ ^*\ 100\% \quad and \quad [\ |\ 15@temp\ |\ -\ |\ 15@25^{\circ}C\ |\ ]\ /\ |\ 15@25^{\circ}C\ |\ ^*\ 100\% ]$

## **■** Functional Description

#### **POWER ON RESET**

The HM6F5221 generates a power on reset operation at power up.

#### REFERENCE OSCILLATOR INPUTS

The Reference oscillator frequency for RF and IF PLL is provided by an external reference through the  $OSC_{IN}$  pin. The  $OSC_{IN}$  block can operate up to 40MHz with an input sensitivity of 0.5 Vpp. It drives both the IF and the RF R counters in common input signal path. When an external TCXO is connected to the  $OSC_{IN}$  input pin, the TCXO drives both IF R counter and RF R counter.

#### REFERENCE DIVIDER

The RF and IF R Counters are clocked through the Oscillator block either separately or in common. The maximum frequency is 40MHz. RF R counter is 2 bits CMOS counters with a divide range from 1 to 3(See the Table.7) IF R counter is 15 bits CMOS counter with a divide range from 2 to 32767(See the Table.3).

#### PROGRAMMABLE DIVIDER

The RF and IF N Counters are clocked by the small signal finRF and finIF input pins respectively. The RF N counter consists of 5-bit programmable counter(B counter) and 4-bit swallow counter(A counter)(See the Table.15 and the Table.16 and the Table.17). The IF N counter consists of 12-bit programmable counter(B counter) and 6-bit swallow counter (A counter)(See the Table.11 and the Table.12).

#### **PRESCALER**

The fully CMOS RF prescaler consists of a differential input buffer and CML frequency divider, while the fully CMOS IF prescaler consists of a differential input buffer and TSPC frequency divider. The input buffer amplifies an input signal from an internal VCO to the required level set by sensitivity requirements. The output of the

RF amplifier delivers a differential signal to the RF divider with the correct DC level, while the IF amplifier a single-ended signal to the IF divider. Buffers is single-ended driven. The single-ended operation is preferred in typical applications.

The RF prescaler provides 8/9 or 12/13 prescaler ratios to allow the multi-modulus operation, while the IF circuitry contains 32/33 or 64/65 dual-modulus prescaler. The prescaler clocks the subsequent CMOS flip-flop chain comprising the fully programmable A and B counters(See the Table.18 and the Table.13).

#### FRACTIONAL COMPENSATION

( $\Sigma$ - $\Delta$  modulator)

The RF part of HM6F5221 adopts the  $\Sigma$ - $\Delta$  modulator as core of the fractional counter that makes it possible to obtain divide ratio N to be a fractional number between two contiguous integers. The  $\Sigma$ - $\Delta$  modulator effectively randomizes the quantization noise generated from digitizing process and results in extreme suppression of in-band noise power by pushing it out to out-of-band as in conventional  $\Sigma$ - $\Delta$  data converter. This technique eliminates the need for compensation current injection into the loop filter and improves fractional spurious performance, suitable for high-tier applications.

For proper  $\Sigma$ - $\Delta$  modulator operation, the user should be kept in mind that

- 1. A fractional number should be set in the range from 0 to K-1 in step 1/K

- 2. The clock frequency (OSC<sub>IN</sub>) that is higher than 10 MHz is recommended for better performance. But power consumption can be increase.

Note that the clock frequency much lower than 10MHz can deteriorate the fractional noise performance.

(See the Table.6 and the Table.15)

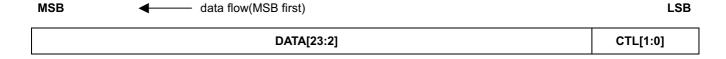

#### **SERIAL INTERFACE**

The programmable functions are accessed through the serial interface. The interface is made of 3 functions: clock, data, and latch enable(LE). Serial data for the

various counters is clocked in from data on the rising edge of clock, into the 24-bit shift register. Data is entered MSB first. The last two bits decode the internal register address. On the rising edge of LE, data stored in the shift register is loaded into one of the 4 appropriate latches (selected by address bits). A complete programming description is included in the following sections.

the IF charge pump output gain is set to either 1x or 2x using IF\_R[18] (IF\_CP\_GAIN) slope (See the Table.4 for IF and the Table.8 for RF).

#### **POWER CONTROL**

Each PLL is individually power controlled by device enable pin or serial interface power down bits. The enable pins override the power down bits. The RIF\_EN pin controls both the RF PLL and the IF PLL. When the pin is high, the power down bits determine the state of power control(See the Table.5 and Table.9 and the Table.20). Activation of any PLL power down mode results in the disabling of the respective N counter and de-biasing of its respective fin input (to a high impedance state). The R counter functionality also becomes disabled when power down bit is activated. The oscillator input block also powers down. Power down forces the respective charge pump and phase detector logic to a TRI-STATE condition. A power down counter reset function resets both N and R counters. Upon powering up the N counter resumes counting in close alignment with R counter (the maximum error is one prescaler cycle). The serial interface remains active and capable of loading and latching in data during all of power down modes.

#### PFD and CP

The RF/IF phase detector, composed of PFD and CP, outputs an average proportional to the phase difference of between outputs of N and R counter. This average is converted to the control voltage of VCO by external loop filter. The slope of the PFD is programmable using RF\_R[16](RF\_PFD\_POL) and IF\_R[17](IF\_PFD\_POL) depending on whether RF/IF VCO has positive slope or negative slope (See the Table.4 for IF and the Table.8 for RF). Also, the RF charge pump output current gain is set to either 1x or 2x using RF\_R[17] (RF\_CP\_GAIN) and

## **■** Programming Description

#### **INPUT DATA REGISTER**

The HM6F5221 can be programmed via the serial bus interface. The interface is made of 3 functional signals: **Clock**, **Data**, and load enable(**LE**). Serial data is moved into the 24-bit shift register on the rising edge of the clock. These data enters MSB first. When **LE** goes HIGH, data in the shift register is moved into one of the 4 latches(by the 2-bit control).

Table.1 Control Bit Map (CTL[1:0])

| CONT | ROL BITS | DATA LOCATION |

|------|----------|---------------|

| C[1] | C[0]     | DAIA ECCATION |

| 0    | 0        | IF_R Register |

| 0    | 1        | IF_N Register |

| 1    | 0        | RF_R Register |

| 1    | 1        | RF_N Register |

Table.2 Data Bit Map (DATA[23:2])

| Register<br>Name | MSB  | REGISTER BIT LOCATION MSB |       |                |       |                                             |    |     |                  |             |          |                   |  |  |     |        |       | L     | SB   |       |      |  |   |   |

|------------------|------|---------------------------|-------|----------------|-------|---------------------------------------------|----|-----|------------------|-------------|----------|-------------------|--|--|-----|--------|-------|-------|------|-------|------|--|---|---|

|                  | 23   | 22                        | 21    | 20             | 19    | 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 |    |     |                  |             |          |                   |  |  |     | 2      | 1     | 0     |      |       |      |  |   |   |

| IF_R             | Fo   | LD                        | х     | IF_PV          | VDN   | IF_                                         | СР |     | IF_R_DIV (15bit) |             |          |                   |  |  |     |        |       |       | 0    | 0     |      |  |   |   |

| IF_N             | IFSW | PRE                       | VA    | IT             |       | •                                           |    |     |                  | IF_B_DIV (  | 12bit)   |                   |  |  |     |        |       | IF.   | _A_D | IV(6b | oit) |  | 0 | 1 |

| RF_R             | Fo   | LD                        | RF_P\ | WDN            | X RF_ |                                             |    | _CP | x                | RF_R_D      | IV(2bit) | FRAC_K_DIV(11bit) |  |  |     |        |       |       | 1    | 0     |      |  |   |   |

| RF_N             | RFSW | PRE                       |       | RF_B_DIV(5bit) |       |                                             |    |     | RF_              | A_DIV(4bit) |          |                   |  |  | FRA | NC_F_I | DIV(1 | 1bit) |      |       |      |  | 1 | 1 |

**Note:** VNT(vendor test bits) and X (dummy bit) are reserved.

They should be set to be zero (LOW) for normal usage.

#### PROGRAMMABLE REFERENCE DIVIDERS

## IF\_R REGISTER

If the Control Bits(C[1:0]) are 00, data is moved from the 24-bit shift register into the IF\_R register which sets the IF reference counter. Serial data format is shown in the table below.

MSB IF\_R[23:0] LSB

| FoLI                    | D [1:0] | Х  | IF_PWDN [1:0] |    | IF_C | IF_CP [1:0]                        |    | IF_R_DIV [14:0] |         | C[1] | C[0] |

|-------------------------|---------|----|---------------|----|------|------------------------------------|----|-----------------|---------|------|------|

| 23                      | 22      | 21 | 20            | 19 | 18   | 17                                 | 16 |                 | 2       | 1    | 0    |

| Program Code Division F |         |    |               |    |      | Division Ratio of the IF R Counter | •  | Contro          | ol Bits |      |      |

Table.3 Binary 15-Bit Programmable IF R Divider Ratio (R Counter) (IF\_R[16] –IF\_R[2])

| Division<br>Ratio | IF_R<br>[16] | IF_R<br>[15] | IF_R<br>[14] | IF_R<br>[13] | IF_R<br>[12] | IF_R<br>[11] | IF_R<br>[10] | IF_R<br>[9] | IF_R<br>[8] | IF_R<br>[7] | IF_R<br>[6] | IF_R<br>[5] | IF_R<br>[4] | IF_R<br>[3] | IF_R<br>[2] |

|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 3                 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           |

| 4                 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           |

| •                 | •            | •            | •            | •            | •            | •            | •            | •           | •           | •           | •           | •           | •           | •           | •           |

| 32767             | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

Notes: Division ratio: 3 to 32767 (The divide ratios less than 3 are prohibited)

IF PFD POL

PWRDN\_MODE\_IF

Data shifted in MSB first.

IF\_CP\_GAIN

PWRDN\_IF

Table.4 IF Charge Pump and Phase Frequency Control - (IF\_CP) (IF\_R[18:17])

| Acronym    | Data Bits | Low(0)   | High(1)  | Comments                    |

|------------|-----------|----------|----------|-----------------------------|

| IF_CP_GAIN | IF_R[18]  | 1X       | 2X       | IF Charge Pump Current Gain |

| IF_PFD_POL | IF_R[17]  | Negative | Positive | IF Phase Detector Polarity  |

Table.5 IF Power Down and Power Down Mode - (IF\_PWDN) (IF\_R[20:19])

| Acronym       | Data Bits | Low(0)                  | High(1)                | Comments                  |

|---------------|-----------|-------------------------|------------------------|---------------------------|

| PWRDN_IF      | IF_R[20]  | Power Up                | Power Down             | IF Power Down             |

| PWRDN_MODE_IF | IF_R[19]  | Asynchronous power down | Synchronous power down | IF Power Down Mode Select |

## Fout / Lock Detect Programming Bits - (FoLD)

See the RF\_R register section for more detail.

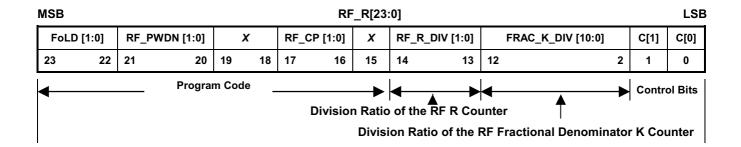

## RF\_R REGISTER

If the Control Bits(C[1:0]) are 10, data is moved from the 24-bit shift register into the RF\_R register which sets the RF reference (RF R counter; 2-bit) / fractional counter (K counter; 11-bit). Serial data format is shown below.

Table.6 Binary 11-Bit Programmable Fractional Denominator K Divider Ratio (K Counter) (RF\_R[12:2])

| Division<br>Ratio | RF_R<br>[12] | RF_R<br>[11] | RF_R<br>[10] | RF_R<br>[9] | RF_R<br>[8] | RF_R<br>[7] | RF_R<br>[6] | RF_R<br>[5] | RF_R<br>[4] | RF_R<br>[3] | RF_R<br>[2] |

|-------------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 1                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1           |

| 2                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 0           |

| 3                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           |

| •                 | •            | •            | •            | •           | •           | •           | •           | •           | •           | •           | •           |

| 2047              | 1            | 1            | 1            | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

Notes: Division ratio: 1 to 2047

Data shifted in MSB first.

Table.7 Binary 2-Bit Programmable RF R Divider Ratio (RF R Counter) (RF\_R[14:13])

| Division<br>Ratio | RF_R<br>[14] | RF_R<br>[13] |

|-------------------|--------------|--------------|

| 1                 | 0            | 1            |

| 2                 | 1            | 0            |

| 3                 | 1            | 1            |

Notice: We recommend that RF R divider ratio is 2. In this ratio, HM6F5201 have best optimized performance in power, fractional compensation and lock time.

Table.8 RF Charge Pump and Phase Frequency Detector Control - (RF\_CP) (RF\_R[17:16])

| RF CP GAIN | RF PFD POL |

|------------|------------|

| RF_CP_GAIN | KF_FFD_FOL |

| Acronym    | Data Bits | Low(0)   | High(1)  | Comments                    |

|------------|-----------|----------|----------|-----------------------------|

| RF_CP_GAIN | RF_R[17]  | 1X       | 2X       | RF Charge Pump Current Gain |

| RF_PFD_POL | RF_R[16]  | Negative | Positive | RF Phase Detector Polarity  |

Table.9 RF Power Down and Power Down Mode - (RF\_PWDN) (RF\_R[21:20])

| PWRDN_RF | PWRDN_MODE_RF |        |         |

|----------|---------------|--------|---------|

| Acronym  | Data Bits     | Low(0) | High(1) |

| Acronym       | Data Bits | Low(0)                  | High(1)                | Comments                  |  |

|---------------|-----------|-------------------------|------------------------|---------------------------|--|

| PWRDN_RF      | RF_R[21]  | Power Up                | Power Down             | RF Power Down             |  |

| PWRDN_MODE_RF | RF_R[20]  | Asynchronous power down | Synchronous power down | RF Power Down Mode Select |  |

Table.10 Fout / Lock Detect Programming Truth Table - (FoLD) (IF\_R[23:22] / RF\_R[23:22])

| RF_R[22]<br>(RF LD) | IF_R[22]<br>(IF LD) | RF_R[23]<br>(RF Fo) | IF_R[23]<br>(IF Fo) | FoLD Output State              |

|---------------------|---------------------|---------------------|---------------------|--------------------------------|

| 0                   | 0                   | 0                   | 0                   | Disabled                       |

| 0                   | 1                   | 0                   | 0                   | IF Lock Detect                 |

| 1                   | 0                   | 0                   | 0                   | RF Lock Detect                 |

| 1                   | 1                   | 0                   | 0                   | RF/IF Lock Detect              |

| х                   | 0                   | 0                   | 1                   | IF Reference Divider Output    |

| Х                   | 0                   | 1                   | 0                   | RF Reference Divider Output    |

| Х                   | 1                   | 0                   | 1                   | IF Programmable Divider Output |

| х                   | 1                   | 1                   | 0                   | RF Programmable Divider Output |

| 0                   | 0                   | 1                   | 1                   | Disabled                       |

| 0                   | 1                   | 1                   | 1                   | IF Counter Reset               |

| 1                   | 0                   | 1                   | 1                   | RF Counter Reset               |

| 1                   | 1                   | 1                   | 1                   | RF and IF Counter Reset        |

#### X = Don't care condition

Notes:

When FoLD output is disabled, it is actively pulled to low logic state.

Lock detect output provided to indicate when the VCO frequency is in "LOCK". When the loop is locked and a lock detect mode is selected, the pins output is high with narrow pulses LOW. In RF/IF detect mode a locked condition is indicated when RF and IF are both locked.

## HM6F5221

## **■ Programming Description** (Continued)

#### PROGRAMMABLE DIVIDER

#### IF\_N REGISTERS

If the Control Bits(C[1:0]) are 01, data is transferred from the 24-bit shift register into the IF\_N register which sets the IF programmable counter. IF N counter consists of swallow counter(A counter: 6-bit), main counter(B counter; 12-bit). Serial data format is shown below.

MSB

IF\_N[23:0]

LSB

IFSW

PRE

VNT [1:0]

IF\_B\_DIV [11:0]

IF\_A\_DIV [5:0]

C[1]

C[0]

| IFSW         | PRE | VNT [1:0]                  |         |       | IF_B_DIV [11:0] | IF_A_DIV [5:0] | C[1] | C[0] | ı |

|--------------|-----|----------------------------|---------|-------|-----------------|----------------|------|------|---|

| 23           | 22  | 21                         | 20      | 19    | 8               | 4 2            | 1    | 0    |   |

| Program Code |     | Division Ratio of the IF N | Counter | Conti | rol Bits        |                |      |      |   |

Table.11 Binary 6-Bit Programmable Swallow Counter Division Ratio (IF A Counter) (IF N[7:2])

| Division<br>Ratio | IF_N<br>[7] | IF_N<br>[6] | IF_N<br>[5] | IF_N<br>[4] | IF_N<br>[3] | IF_N<br>[2] |

|-------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0                 | 0           | 0           | 0           | 0           | 0           | 0           |

| 1                 | 0           | 0           | 0           | 0           | 0           | 1           |

| •                 | •           | •           | •           | •           | •           | •           |

| 63                | 1           | 1           | 1           | 1           | 1           | 1           |

Division ratio: 0 to 63 B > A

Table.12 Binary 12-Bit Programmable IF Main Counter Division Ratio (IF B Counter) (IF\_N[19:8])

| Division<br>Ratio | IF_N<br>[19] | IF_N<br>[18] | IF_N<br>[17] | IF_N<br>[16] | IF_N<br>[15] | IF_N<br>[14] | IF_N<br>[13] | IF_N<br>[12] | IF_N<br>[11] | IF_N<br>[10] | IF_N<br>[9] | IF_N<br>[8] |

|-------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|

| 3                 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 1           | 1           |

| 4                 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 1            | 0           | 0           |

| 5                 | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 1            | 0           | 1           |

| •                 | •            | •            | •            | •            | •            | •            | •            | •            | •            | •            | •           | •           |

| 4095              | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1           | 1           |

Notes: Division ratio: 3 to 4095 (The division ratio less than 3 are prohibited)

#### Vendor Test Bits - (VNT) (IF\_N[21:20])

Vendor test bits are for verification of some functions and characteristics. In normal usage, they should be set to LOW.

Rev. 0.3.0

16

Table.13 IF Prescaler Select - (PRE) (IF\_N[22])

| Acronym | Data Bits | Low(0) | High(1) | Comments                    |

|---------|-----------|--------|---------|-----------------------------|

| PRE     | IF_N[22]  | 32/33  | 64/65   | IF Prescaler Modulus Select |

Notes: PRE (prescaler select) is used to set IF prescaler. The HM6F5221 contains two dual modulus prescaler for IF mode. It uses the 16/17 or 32/33 dual modulus prescaler mode to internally operate at 680 MHz  $\sim 1.1$  GHz.

Table.14 IF Frequency Divider Select - (IFSW) (IF N[23])

| Acronym | Data Bits | Low(0)      | High(1)     | Comments                          |

|---------|-----------|-------------|-------------|-----------------------------------|

| IFSW    | IF_N[23]  | Divide by 2 | Divide by 4 | IF Frequency Divider Ratio Select |

Notes: IFSW (IF frequency divider select switch) is used to set IF output frequency divider ratio. You can select the divider ratio in order to use different communication systems.

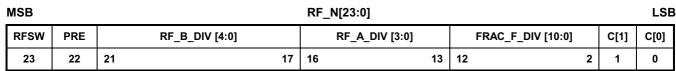

#### **RF N REGISTER**

If the Control Bits(C[1:0]) are 11, data is moved from the 24-bit shift register into the RF\_N register, which sets the RF programmable counter. RF N counter consists of swallow counter(A counter: 4-bit), main counter(B counter; 5-bit) and RF fractional counter (F counter; 11-bit). Serial data format is shown below.

Division Ratio of the RF N Counter Control Bits

Table.15 Binary 11-Bit Programmable Fractional Numerator F Divider Ratio (F Counter) (RF\_N[12:2])

| Division<br>Ratio | RF_N<br>[12] | RF_N<br>[11] | RF_N<br>[10] | RF_N<br>[9] | RF_N<br>[8] | RF_N<br>[7] | RF_N<br>[6] | RF_N<br>[5] | RF_N<br>[4] | RF_N<br>[3] | RF_N<br>[2] |

|-------------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 1                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 1           |

| 2                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 0           |

| 3                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 1           | 1           |

| 4                 | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 1           | 0           | 0           |

| •                 | •            | •            | •            | •           | •           | •           | •           | •           | •           | •           | •           |

| 2047              | 1            | 1            | 1            | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

Notes: Division ratio: 1 to 2047

It is not allowed that Fractional F divider ratio is 0. Because values of F divider ratio is used as numerator.

Rev. 0.3.0 17

Division Ratio of the RF Fractional Numerator F Counter

## HM6F5221

## **■ Programming Description** (Continued)

Table.16 Binary 4-Bit Programmable Swallow Counter Division Ratio (RF A Counter) (RF\_N[16:13])

When RF prescaler has 12/13 divide ratio

| vvnen RF prescaler has 12/13 divide ratio |              |              |              |              |  |  |  |  |

|-------------------------------------------|--------------|--------------|--------------|--------------|--|--|--|--|

| Division<br>Ratio                         | RF_N<br>[16] | RF_N<br>[15] | RF_N<br>[14] | RF_N<br>[13] |  |  |  |  |

| 0                                         | 0            | 0            | 0            | 0            |  |  |  |  |

| 1                                         | 0            | 0            | 0            | 1            |  |  |  |  |

| 2                                         | 0            | 0            | 1            | 0            |  |  |  |  |

| •                                         | •            | •            | •            | •            |  |  |  |  |

| 11                                        | 1            | 1            | 1            | 1            |  |  |  |  |

| wnen RF           | when RF prescaler has 8/9 divide ratio |              |              |              |  |  |  |  |  |

|-------------------|----------------------------------------|--------------|--------------|--------------|--|--|--|--|--|

| Division<br>Ratio | RF_N<br>[16]                           | RF_N<br>[15] | RF_N<br>[14] | RF_N<br>[13] |  |  |  |  |  |

| 0                 | X                                      | 0            | 0            | 0            |  |  |  |  |  |

| 1                 | х                                      | 0            | 0            | 1            |  |  |  |  |  |

| •                 | •                                      | •            | •            | •            |  |  |  |  |  |

| 7                 | Х                                      | 1            | 1            | 1            |  |  |  |  |  |

| х                 | Х                                      | Х            | Х            | Х            |  |  |  |  |  |

Notes: Division ratio: 0 to 11 B > A

Table.17 Binary 5-Bit Programmable RF Main Counter Division Ratio (RF B Counter) (RF\_N[21:17])

| Division<br>Ratio | RF_N<br>[21] | RF_N<br>[20] | RF_N<br>[19] | RF_N<br>[18] | RF_N<br>[17] |

|-------------------|--------------|--------------|--------------|--------------|--------------|

| 3                 | 0            | 0            | 0            | 1            | 1            |

| 4                 | 0            | 0            | 1            | 0            | 0            |

| 5                 | 0            | 0            | 1            | 0            | 1            |

| •                 | •            | •            | •            | •            | •            |

| 31                | 1            | 1            | 1            | 1            | 1            |

Notes: Division ratio: 3 to 31 (The division ratio less than 3 are prohibited)

Table.18 RF Prescaler Select - (PRE) (RF\_N[22])

| Acronym | Data Bits | Low(0) | High(1) | Comments                    |

|---------|-----------|--------|---------|-----------------------------|

| PRE     | RF_N[22]  | 8/9    | 12/13   | RF Prescaler Modulus Select |

Notes : PRE (prescaler select) is used to set RF prescaler. The HM6F5221 contains two dual modulus prescaler. It uses the 8/9 or 12/13 dual modulus prescaler mode to operate at 500 MHz  $\sim 2.5$  GHz.

In 8/9 dual modulus prescaler mode, HM6F5221 can operate up to 2.5GHz. But we recommend that you select RF prescaler mode following rule.

Table.19 RF Frequency Band Select - (RFSW) (RF\_N[23])

| Acronym | Data Bits | Low(0)  | High(1) | Comments                 |

|---------|-----------|---------|---------|--------------------------|

| RFSW    | RF_N[23]  | RF1 Out | RF2 Out | RF frequency band select |

Notes: RFSW (RF mux control bit) is used to set RF output frequency band. You can select the one of two bands order to use different communication systems.

18

# ■ Program Mode Control

## REFERENCE OSCILLATOR INPUT and POWER DOWN CONTROL

Table.20 Reference Oscillator Input and Power Down Control

| PWRDN_IF | PWRDN_RF | IF               | RF                |

|----------|----------|------------------|-------------------|

| IF_R[18] | RF_R[21] | "                | Ki                |

| 0        | 0        | OSCIN            | OSC <sub>IN</sub> |

| 0        | 1        | OSCIN            | LOW (Power down)  |

| 1        | 0        | LOW (Power down) | OSCIN             |

| 1        | 1        | LOW (Power down) | LOW (Power down)  |

# Preliminary HM6F5221

■ Application Example

# ■ Serial Data Input Timing

**CLOCK Timing Diagram**

Serial Data Timing Diagram

# ■ Package Outline

## Physical Dimensions (unit: mm)

Leadless Grid Array Package