OBSOLETE PRODUCT

No Recommended Replacement

# HFA-0003, HFA-0003L

September 1998

# Ultra High Speed Comparator

#### Features

| • | Low Propagation Delay (0003/0003L)     | 2.0/2.1ns     |

|---|----------------------------------------|---------------|

| • | Low Latch Set Up Time                  | 0.8ns         |

| • | Low Offset Voltage, Drift Coefficient  | 1.0mV, 4μV/°C |

| • | Wide Common Mode Range                 | +5.2/-2.8\    |

| • | Low Power Dissipation                  | 200mW         |

| • | Large Differential Input Resistance    | <b>1M</b> Ω   |

|   | Complementary ECL Outputs: 500 Driving | Canability    |

- Resistor Programmable Hysteresis with HFA-0003L

- Pin Compatible with MAX9690/9685 and AD96685

- Available in SOIC

# **Applications**

- Window Detector

- **High Speed Peak Detector**

- **High Speed Threshold Detector**

- **High Speed Data Acquisition Systems**

- **Fiber Optic Decision Circuits**

- **High Speed Phase Detector**

- **Frequency Counter**

#### Part Number Information

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE                       |

|----------------|----------------------|-------------------------------|

| HFA1-0003L-5   | 0°C to +75°C         | 16 Lead Ceramic Sidebraze DIP |

| HFA1-0003L-9   | -40°C to +85°C       | 16 Lead Ceramic Sidebraze DIP |

| HFA2-0003L-5   | 0°C to +75°C         | 10 Pin CAN                    |

| HFA2-0003L-9   | -40°C to +85°C       | 10 Pin CAN                    |

| HFA3-0003-5    | 0°C to +75°C         | 8 Lead Plastic DIP            |

| HFA3-0003-9    | -40°C to +85°C       | 8 Lead Plastic DIP            |

| HFA3-0003L-5   | 0°C to +75°C         | 16 Lead Plastic DIP           |

| HFA3-0003L-9   | -40°C to +85°C       | 16 Lead Plastic DIP           |

| HFA7-0003-5    | 0°C to +75°C         | 8 Lead Ceramic Sidebraze DIP  |

| HFA7-0003-9    | -40°C to +85°C       | 8 Lead Ceramic Sidebraze DIP  |

| HFA9P0003-5    | 0°C to +75°C         | 8 Lead SOIC                   |

| HFA9P0003L-5   | 0°C to +75°C         | 16 Lead Narrow Body SOIC      |

| HFA9P0003L-9   | -40°C to +85°C       | 16 Lead Narrow Body SOIC      |

# Description

The HFA-0003/0003L are monolithic, ultra high speed, voltage comparators. These comparators combine a low input offset voltage (1.0mV) with a low propagation delay (2.0ns) to achieve a large dynamic input range. The low offset voltage also makes these comparators ideally suited for high speed, precision analog-todigital processing applications. The circuits have differential analog inputs, and provide complementary. ECL compatible (10K and 100K) logic outputs. The outputs are capable of supplying the current required by terminated  $50\Omega$  transmission lines. Both outputs are open emitter structures, requiring external pulldown resistors. The recommended circuit is  $50\boldsymbol{\Omega}$ connected to -2.0V, but any equivalent ECL termination circuit may be used.

The HFA-0003L is a latched version of the HFA-0003. The latch function allows the HFA-0003L to operate in sample-hold or track-hold modes, when synchronous detection is required. The Latch Enable (LE) input can be driven by a standard ECL gate. See the Applications section for more information on this feature.

The HFA-0003L also has an additional feature, user programmable hysteresis. By connecting a resistor from the HYS pin to GND the user can select up to 20mV of input hysteresis. See the Applications section for more information on this feature.

The HFA-0003 is pin compatible with the MAX9690. and SP9680 while providing improved performance. The HFA-0003L is pin compatible with the MAX9685, AD96685, SP9685, HCMP96850, and the VC7695 while providing improved performance.

# **Pinouts**

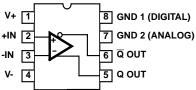

HFA-0003 (PDIP, CDIP, SOIC) TOP VIEW

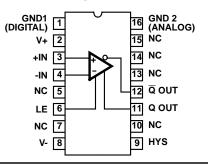

HFA-0003L (PDIP, CDIP, 150 mil SOIC) TOP VIEW

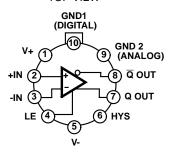

HFA-0003L (TO-100 CAN) TOP VIEW

# Specifications HFA-0003, HFA-0003L

#### Absolute Maximum Ratings (Note 1) **Operating Conditions** Supply Voltage (GND to V+)......8V Operating Temperature Range Voltage Between V+ and V- Terminals . . . . . . . . . . . . . 20V Differential Input Voltage......5.5V Thermal Package Characteristics (°C/W) Differential Ground Voltage (GND1 to GND2)..... ±1V 8 Lead Ceramic Sidebrazed DIP . . . . . . 13 Short Duration Output Current (Note 2) . . . . . . . -35mA 8 Lead Plastic DIP..... 96 34 43 157 16 Lead Ceramic Sidebrazed DIP . . . . . Junction Temperature (Plastic Package) . . . . . . . . +150°C 75 13 Lead Temperature (Soldering 10 Sec.). . . . . . . . +300°C 16 Lead Plastic DIP..... 32 92 114 35 108 32

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** V+ = 5V, V- = -5.2V, $R_L = 50\Omega$ to -2V, Unless Otherwise Specified

|                                         |             | HFA-0003-5/-9 |       |       | HFA-0003L-5/-9 |       |       |       |

|-----------------------------------------|-------------|---------------|-------|-------|----------------|-------|-------|-------|

| PARAMETER                               | TEMPERATURE | MIN           | TYP   | MAX   | MIN            | TYP   | MAX   | UNITS |

| INPUT CHARACTERISTICS                   | •           | -             | •     | •     |                | •     | •     | •     |

| Input Offset Voltage (V <sub>OS</sub> ) | +25°C       | -             | 1     | 3     | -              | 1     | 3     | mV    |

|                                         | Full        | -             | -     | 4     | -              | -     | 4     | mV    |

| Average Offset Voltage Drift (Note 8)   | Full        | -             | -     | 4     | -              | -     | 4     | μV/ºC |

| Input Bias Current                      | +25°C       | -             | 5     | 8     | -              | 5     | 8     | μΑ    |

|                                         | Full        | -             | 8     | 13    | -              | 8     | 13    | μΑ    |

| Input Offset Current                    | +25°C       | -             | 0.15  | 0.2   | -              | 0.15  | 0.2   | μΑ    |

|                                         | Full        | -             | -     | 0.3   | -              | -     | 0.3   | μΑ    |

| Common Mode Range                       | Full        | -2.8          | -     | +5.2  | -2.8           | -     | +5.2  | ٧     |

| Differential Input Resistance           | +25°C       | -             | 1     | -     | -              | 1     | -     | МΩ    |

| Common Mode Input Resistance            | +25°C       | -             | 9.5   | -     | -              | 9.5   | -     | МΩ    |

| Input Capacitance                       | +25°C       | -             | 1     | -     | -              | 1     | -     | pF    |

| TRANSFER CHARACTERISTICS                | •           | •             |       | •     |                | •     |       |       |

| Large Signal Voltage Gain               | +25°C       | -             | 3100  | -     | -              | 3100  | -     | V/V   |

|                                         | Full        | -             | 1200  | -     | -              | 1200  | -     | V/V   |

| Common Mode Rejection Ratio             | +25°C       | 70            | 75    | -     | 70             | 75    | -     | dB    |

| (Note 3)                                | Full        | 70            | -     | -     | 70             | -     | -     | dB    |

| Tracking Bandwidth (Note 4)             | +25°C       | -             | 270   | -     | -              | 270   | -     | MHz   |

| SWITCHING CHARACTERISTICS               | •           | •             |       | •     |                | •     |       |       |

| Propagation Delay Input to Output       | +25°C       | -             | 2.0   | 2.4   | -              | 2.1   | 2.6   | ns    |

| (t <sub>PD</sub> )(Notes 5, 8, 9)       | Full        | -             | -     | 2.8   | -              | -     | 3.0   | ns    |

| Maximum Dispersion (Notes 6, 8)         | Full        | -             | -     | 200   | -              | -     | 200   | ps    |

| OUTPUT CHARACTERISTICS                  |             | •             |       |       |                |       |       | •     |

| Output Voltage Level:                   |             |               |       |       |                |       |       |       |

| Logic Low (V <sub>OL</sub> )            | +25°C       | -             | -1.83 | -1.65 | -              | -1.83 | -1.65 | V     |

|                                         | Full        | -             | -1.83 | -1.57 | -              | -1.83 | -1.57 | V     |

| Logic High (V <sub>OH</sub> )           | +25°C       | -0.938        | -0.85 | -     | -0.938         | -0.85 | -     | V     |

|                                         | Full        | -1.05         | -0.96 | -     | -1.05          | -0.96 | -     | V     |

| Continuous Output Current (Note 2)      | Full        | -             | -     | -30   | -              | -     | -30   | mA    |

# Specifications HFA-0003, HFA-0003L

### **Electrical Specifications** V+ = 5V, V- = -5.2V, $R_L$ = $50\Omega$ to -2V, Unless Otherwise Specified (Continued)

|                                                    |             | HFA-0003-5/-9 |     | HFA-0003L-5/-9 |        |      |        |       |

|----------------------------------------------------|-------------|---------------|-----|----------------|--------|------|--------|-------|

| PARAMETER                                          | TEMPERATURE | MIN           | TYP | MAX            | MIN    | TYP  | MAX    | UNITS |

| LATCH CHARACTERISTICS (HFA-0003L ONLY)             |             |               |     |                |        |      |        |       |

| LE Input Voltage Level:                            |             |               |     |                |        |      |        |       |

| Logic Low (V <sub>IL</sub> )                       | Full        | -             | -   | -              | -      | -    | -1.475 | V     |

| Logic High (V <sub>IH</sub> )                      | Full        | -             | -   | -              | -1.105 | -    | -      | V     |

| LE Input Current Level:                            |             |               |     |                |        |      |        |       |

| Logic Low (V <sub>IL</sub> = -1.85V)               | Full        | -             | -   | -              | -      | 0.06 | 0.5    | μΑ    |

| Logic High (V <sub>IH</sub> = -0.81V)              | Full        | -             | -   | -              | -      | 11   | 20     | μΑ    |

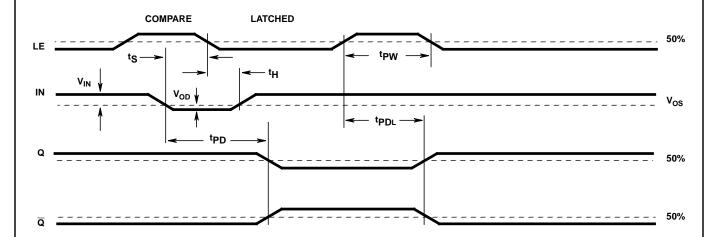

| Propagation Delay from LE to Output (tp.           | +25°C       | -             | -   | -              | -      | 2.2  | 2.7    | ns    |

| DL) (Notes 5, 8, 9)                                | Full        | -             | -   | -              | -      | 2.6  | 3.1    | ns    |

| Minimum Set-Up Time (t <sub>S</sub> ) (Notes 8, 9) | +25°C       | -             | -   | -              | -      | 0.8  | 1.2    | ns    |

|                                                    | Full        | -             | -   | -              | -      | -    | 1.5    | ns    |

| Minimum Hold Time (t <sub>H</sub> ) (Notes 8, 9)   | Full        | -             | -   | -              | -      | 0.5  | 1.0    | ns    |

| Minimum LE Pulse Width (t <sub>PW</sub> )          | +25°C       | -             | -   | -              | -      | 0.9  | 0.95   | ns    |

| (Notes 8, 9)                                       | Full        | -             | -   | -              | -      | -    | 1.1    | ns    |

| POWER SUPPLY                                       |             | •             | •   | •              | •      |      |        |       |

| PSRR (Note 7)                                      | +25°C       | 70            | 80  | -              | 70     | 80   | -      | dB    |

|                                                    | Full        | 65            | -   | -              | 65     | -    | -      | dB    |

| I <sub>CC</sub>                                    | Full        | -             | 11  | 13             | -      | 11   | 13     | mA    |

| I <sub>EE</sub>                                    | Full        | -             | 19  | 22             | -      | 19   | 22     | mA    |

| Power Dissipation                                  | Full        | -             | -   | 200            | -      | -    | 200    | mW    |

#### NOTES:

- 1. Absolute maximum ratings are limiting values, applied individually, beyond which the servicability of the circuit may be impaired. Functional operation under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions may affect device reliability.

- 2. Outputs have no sink current (+I) capability, since they are open emitter NPN transistors.

- 3.  $-2.0V \le V_{CM} \le +4.0V$ .

- 4. Tracking Bandwidth (TBW) is defined as the maximum input frequency at which the outputs still switch between  $V_{OL}$  and  $V_{OH}$ .  $V_{IN} = 15 \text{mVp-p}$  sinewave centered on 0V.

- 5.  $V_{IN} = 100$ mV.  $V_{OD}$  is the amount of input overdrive.

- 6. Dispersion is defined as the change in propagation delay for input overdrives between 0.1V and 1.0V.

- 7.  $+4.5V \le V+ \le +5.5V$  or  $-6.2V \le V- \le -4.7V$ .

- 8. This parameter is not tested. It is guaranteed by design, and by device characterization.

- 9.  $V_{OD} = 10 \text{mV}$ .

# **Applications Information**

#### **HFA-0003L Latch Functionality**

The Latch Enable (LE) pin of the HFA-0003L controls the function of the on chip latch. When the LE input is at an ECL Logic 1, the latch is open (transparent) and the comparator functions normally. When the LE input switches to a Logic 0, the outputs are latched in unambiguous states dependant on the current input state, providing the set-up and hold times are met. If the latch function is not utilized, the LE input must be connected to an ECL Logic 1 (e.g. GND).

#### **HFA-0003L Hysteresis Functionality**

To improve performance in systems with slow transition times, and/or high noise levels, the HFA-0003L allows the user to easily set the amount of input hysteresis. The hysteresis level is set by the current flowing into the HYS input; the larger the current the larger the level of hysteresis. This current is provided by connecting a resistor ( $R_{\rm H}$ ) between

the HYS pin and GND, and it is recommended that the input current not exceed 1mA. The input current can be approximated from the following formula:

$$I_{H} = \frac{GND - (V-) - 0.7V}{R_{H}}$$

The table below gives approximate levels of hysteresis for some values of  $I_H$ , at  $T_A = +25^{\circ}C$ .

| I <sub>H</sub> (mA) | 0.2 | 0.4 | 0.6 | 0.8 | 1.0 |

|---------------------|-----|-----|-----|-----|-----|

| HYS (mV)            | 1   | 4   | 8   | 13  | 22  |

If the hysteresis function isn't used, the HYS input may be left floating, or may be connected to V-. The HYS input MUST NEVER BE CONNECTED directly to GND or V+, as device damage will occur. Before inserting an HFA-0003L into a competitor socket, the user must ensure that the corresponding socket pin is a true no connect (i.e. is floating).

# Timing Diagram