## **Preliminary Specification**

# **HITACHI**

Rev. 2 March 2, 1998

### **General Description**

HD49429F is a highly integrated MCNS compliant Upstream processor optimized for applications such as Cable Modems and Set-top boxes. It forms a complete and optimal solution with its companion HD49430F Down-stream processor. The HD49429F consists of a highly programmable encoder, Nyquist Filter and RF modulator using fully digital implementation. A highly accurate on-chip 10 bit D/A provides a RF analog output which can be used after simple low pass filtering. The HD49429F also has a highly optimized interface to a external MAC.

HD49429F is implemented in an advanced CMOS process and uses a single 3.3V (+/- 10%) power supply, and is packaged in a low cost 100pin PQFP.

#### **Features**

- State of the art QPSK/16 QAM MCNS Compliant Modulator using full digital Synthesis.

- Highly programmable architecture can provide modulated carrier from 1-42Mhz using programmable NCO with very high resolution.

- Fully programmable Nyquist filter can implement a variety of standards (25% excess BW nominal).

- Highly programmable interpolators can implement a large number of related baud rates from 160Kbaud to 3.2Mbaud using a single crystal.

- Burst or Continuous Mode operation. Continuous mode operation has no restrictions.

- Programmable Bit-stream Formatting and Encoding

- Programmable preamble insertion of up to 1024 bits.

- scrambling with Pseudo- Bit Random sequence (MCNS Specification).

- Programmable RS encoder with up to 20 parity bytes (10 corrections).

- On-chip Buffer and Simplified Interface to External MAC.

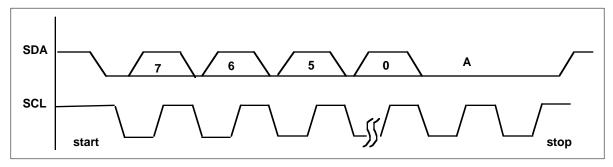

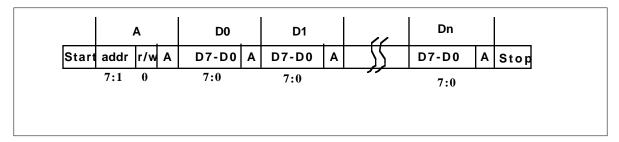

- General Purpose Parallel Port and I<sup>2</sup>C port for external control

- High Performance Analog circuits to optimize system implementation and reduce system cost.

- 102.4 MHz internal synthesis clock is derived from a on-chip 5x multiplier. This helps reduce EMI and RF interference problems.

- On-chip 10-bit DAC provides a high quality modulated carrier, and eliminates need for a expensive external DAC.

- - Low Power

- Surface -mount PQFP packaging

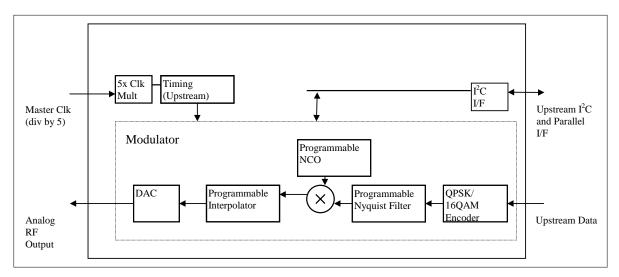

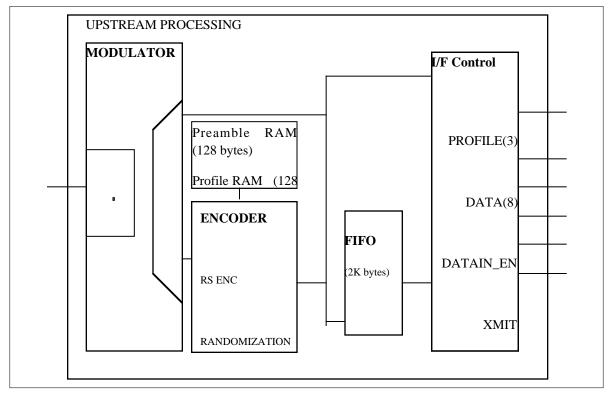

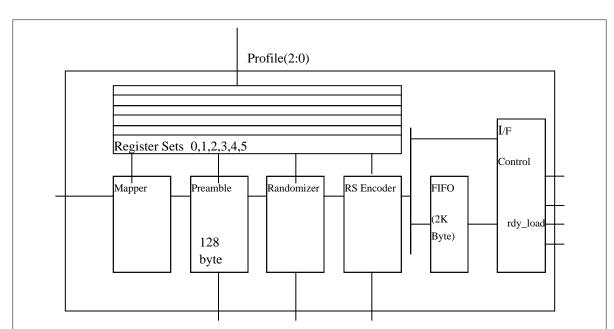

### **Simplified Chip Block Diagram**

Figure 1 Simplified Block Diagram

# **Detailed System Specifications**

### **QPSK Modulator Specifications**

**Table 1** Modulator Specifications

| Parameter                                             | Sym   | Specification                                    |

|-------------------------------------------------------|-------|--------------------------------------------------|

| Analog RF Signal to Out of band RMS noise ratio.      | SNRo  | 50 dB (Noise measured in equivalent signal B/W). |

| Programmable Carrier Frequency<br>Step Size           |       | 12 Hz                                            |

| Master Clock Frequency                                | Fmax  | 102.4 MHz                                        |

| Max Carrier Frequency                                 | Fcmax | 42 MHz                                           |

| Max Baud Rate                                         | Bmax  | F/40 (for a given master frequency F)            |

| Min Baud Rate                                         | Bmin  | F/640 (for a given master frequency F)           |

| Baud Rate Steps                                       | Bst   | F/40, F/48,F/56F/640                             |

| Programmable Nyquist Filter Roll-<br>off (excess B/W) | alpha | 25% nominal                                      |

| D/A Resolution                                        | N     | 10 bits                                          |

| D/A Slew Rate                                         | SR    | 50V/uS                                           |

| D/A Peak-Peak output                                  | Vpp   | 0.5 V                                            |

# **Detailed Register Description**

Table 2

Register Description

| Register Name     | Addr | Bits  | Value | Description                                                                                                                                                                                                                                                                            |  |

|-------------------|------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REV_NO            | 0    | [3:0] |       | Read-only register gives the revision number of the chip.                                                                                                                                                                                                                              |  |

| NYQ_MEM_ADD<br>R  | 1    | [7:0] | d0    | Register used as a address pointer for programming the Nyquist RAM. The RAM is written/read using the READ_ROW and WRITE_ROW commands described later.                                                                                                                                 |  |

| NYQ_MEM_B0        | 2    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM. This register represents the 0th byte in the 9 byte wide Nyquist RAM word.                                                                                                                                                 |  |

| NYQ_MEM_B1        | 3    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM. This register represents the 1st byte in the 9 byte wide Nyquist RAM word                                                                                                                                                  |  |

| NYQ_MEM_B2        | 4    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM. This register represents the 2nd byte in the 9 byte wide Nyquist RAM word                                                                                                                                                  |  |

| NYQ_MEM_B3        | 5    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM. This register represents the 3rd byte in the 9 byte wide Nyquist RAM word                                                                                                                                                  |  |

| NYQ_MEM_B4        | 6    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM. This register represents the 4th byte in the 9 byte wide Nyquist RAM word.                                                                                                                                                 |  |

| NYQ_MEM_B5        | 7    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM .This register represents 5th byte in the 9 byte wide Nyquist RAM word                                                                                                                                                      |  |

| NYQ_MEM_B6        | 8    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM This register represents the 6th byte in the 9 byte wide Nyquist RAM word.                                                                                                                                                  |  |

| NYQ_MEM_B7        | 9    | [7:0] | d0    | Register used for reading/writing data from/to Nyquist RAM This register represents the 7th byte in the 9 byte wide Nyquist RAM word                                                                                                                                                   |  |

| NYQ_MEM_B8        | 10   | [5:0] | d0    | Register used for reading/writing data from/to Nyquist RAM This register represents the 8th byte in the 9 byte wide Nyquist RAM word Only bits (5:0) are used, since only 70 bits are required for each half of the filter.                                                            |  |

| BUF_MEM_ADDR<br>0 | 11   | [7:0] | d0    | These 2 registers combine to form a single 9 bit register BUF_MEM_ADDR, which is used as an address pointer register for accessing the Buffer RAM.                                                                                                                                     |  |

| BUF_MEM_ADDR      | 12   | [7:0] | d0    |                                                                                                                                                                                                                                                                                        |  |

| BUF_MEM_DATA      | 13   | [7:0] | d0    | This register is used to read/write data from/to Buffer RAM. When a byte is written/to read/from this register, the byte is written/to read/from the location in Buffer RAM pointed to by the BUF_MEM_ADDR. BUF_MEM_ADDR is automatically incremented when this register is addressed. |  |

| Register Name | Addr | Bits  | Value | Description                                                                                                                                                                                                                                                                  |  |

|---------------|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PR_MEM_ADDR   | 14   | [7:0] | d0    | Address Pointer register for accessing Profile/Preamble RAM .                                                                                                                                                                                                                |  |

| PR_MEM_DATA   | 15   | [7:0] | d0    | Data Register for writing/reading Profile/Preamble RAM. When a byte is written/to read/from this register, the byte is written/to read/from the location in Preamble RAM pointed to by PR_MEM_ADDR. PR_ME.M_ADDR is automatically incremented when this register is accessed |  |

| NYQ_OVERRIDE  | 16   | [0:0] | 0     | Normal Operation                                                                                                                                                                                                                                                             |  |

|               |      |       | 1     | When accessing NYQ_RAM using microprocessor I/F, this bit must be set to 1.                                                                                                                                                                                                  |  |

| PR_OVERRIDE   | 16   | [1:1] | 0     | Normal Operation                                                                                                                                                                                                                                                             |  |

|               |      |       | 1     | When accessing PR_RAM using microprocessor I/F, this bit must be set to 1.                                                                                                                                                                                                   |  |

| BUF_OVERRIDE  | 16   | [2:2] | 0     | Normal Operation                                                                                                                                                                                                                                                             |  |

|               |      |       | 1     | When accessing BUF_RAM using microprocessor I/F, this bit must be set to 1.                                                                                                                                                                                                  |  |

| AUTO_INC_DIS  | 16   | [3:3] | 0     | Address Pointer register is auto-incremented after each read/write access.                                                                                                                                                                                                   |  |

|               |      |       | 1     | This bit turns off the auto increment feature of the micro i/f pointer register. This bit is set to 1 when bursting data into/out of PR_RAM or BUF_RAM using micro i/f.                                                                                                      |  |

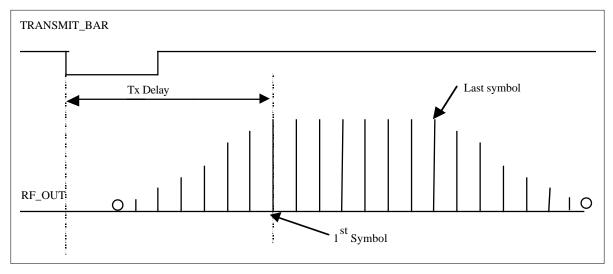

| ON_DELAY0     | 17   | [7:0] | d0    | These 2 registers form the 12 bit ON_DELAY register. This                                                                                                                                                                                                                    |  |

| ON_DELAY1     | 18   | [3:0] | d0    | register is used to delay the start of the XMIT_EN pulse. An internal clock with frequency equal to (5*REF_CLK_FREQ/4) is used to generate delay.                                                                                                                            |  |

| OFF_DELAY0    | 19   | [7:0] | d0    | These 2 registers form the 12 bit OFF_DELAY register. This                                                                                                                                                                                                                   |  |

| OFF_DELAY1    | 20   | [3:0] | d0    | register is used to delay the end of the XMIT_EN pulse. An internal clock with frequency equal to (5*REF_CLK_FREQ/4) is used to generate delay.                                                                                                                              |  |

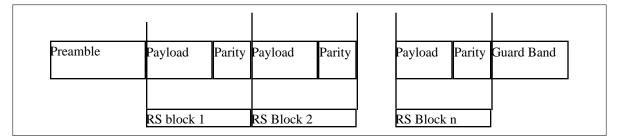

| FEC_T         | 21   | [3:0] | d3    | This register programs T, the error correction capability of the Reed-Solomon encoder. The encoder will introduce 2T parity bytes in each packet.                                                                                                                            |  |

| RAND_EN       | 21   | [4:4] | d1    | This bit enables the on-chip Randomizer.                                                                                                                                                                                                                                     |  |

| BUF_EN        | 21   | [5:5] | d1    | This bit enables the use of on-chip buffer to store the payload data. In this mode, the external controller can blast data into the on-chip 2Kbyte buffer. When this bit is 0, the external controller must present a byte of data as it is requested by the encoder         |  |

| CONT_MODE     | 21   | [6:6] | d0    | This bit enables the continuous mode when set to '1'. In continuous mode, the modulator transmits continuously (and expects continuous payload data). The payload is encoded and packetized as programmed using other registers.                                             |  |

| FEC_K         | 22   | [7:0] | d53   | This register programs the payload of the Reed-Solomon block (number of bytes). The total block length is K + 2T.                                                                                                                                                            |  |

| PAYLOAD0      | 23   | [7:0] | d59   | These 3 registers are concatenated to form the 20 bit PAYLOD register. This defines the total size of the payload in bytes.                                                                                                                                                  |  |

| Register Name            | Addr     | Bits           | Value     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------|----------|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PAYLOAD1                 | 24       | [7:0]          | d0        | PAYLOAD2[3] must be set to "0", and hence the maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PAYLOAD2                 | 25       | [3:0]          | d0        | programmable value is (2 <sup>19</sup> - 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| MASK_PAYLOAD             | 25       | [4:4]          | 0         | The register will be over-written by PAYLOAD value in profile RAM unless VALID_PR_RAM value is '0'.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                          |          |                | 1         | The register will not be over-written by PAYLOAD value in profile RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| ZERO_PAD0                | 26       | [7:0]          | d59       | These 3 registers are concatenated to form the 20 bit ZEROPAD                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| ZERO_PAD1                | 27       | [7:0]          | d0        | register. This defines the total size of the packet to be transmitted, including encoding overhead and zero-padding.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ZERO_PAD2                | 28       | [3:0]          | d0        | ZERO_PAD2[3] must be set to "0", and hence the maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                          |          |                |           | programmable value is (2 <sup>19</sup> - 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| MASK_ZERO_PA<br>D        | 28       | [4:4]          | 0         | The register will be over-written by ZEROPAD value in profile RAM unless VALID_PR_RAM value is '0'.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                          |          |                | 1         | The register will not be over-written by ZEROPAD value in profile RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PRE_START0<br>PRE_START1 | 29<br>30 | [7:0]<br>[0:0] | d0<br>d0  | These 2 registers are concatenated to form the 9 bit PRE_START register. The 1024 bit preamble stored in the PR_RAM can be accessed on 2-bit symbol boundaries. The preamble can use any contiguous portion of this 1024 bit (512 symbols in QPSK, 256 symbols in 16-QAM) sequence. This register defines the starting address of the 2-bit symbol in the sequence. For QPSK, allowed values are (0,1,2,3,511). The allowed values for 16-QAM are (0,2,4,6510).                                                     |  |

| PRE_STOP0 PRE_STOP1      | 31<br>32 | [7:0]<br>[0:0] | d15<br>d0 | These 2 registers are concatenated to form the 9 bit PRE_STOP register. The 1024 bit preamble stored in the PR_RAM can be accessed on 2-bit symbol boundaries. The preamble can use any contiguous portion of this 1024 bit (512 symbols in QPSK, 256 symbols in 16-QAM) sequence. This register defines the end address of the 2-bit symbol in the sequence. For QPSK, allowed values are (0,1,2,3,511). The allowed values for 16-QAM are (0,2,4,6510).                                                           |  |

| INCREMENT                | 33       | [7:0]          | d31       | This register defines the increment step required in the address generator for the Nyquist RAM. This value depends on the subsampling required in the filter stored in the Nyquist RAM. If Nx sub-sampling of stored filter is required, then the value programmed in this register is (2N-1). The default filter stored in the RAM is a 80-tap filter. Hence, if a interpolation ratio of 5 is requires, then a subsampling ratio of (80/5 = 16) is required, which in turn requires INCREMENT of (2*16 - 1 = 31). |  |

| START_ADDR               | 34       | [7:0]          | d0        | This register defines the starting address of the NYQ_RAM location where the filter pattern begins.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| MODTYPE                  | 35       | [0:0]          | 0         | QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                          |          |                |           | 16 QAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                          |          |                | 1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DIFF_EN                  | 35       | [1:1]          | 0         | Non-Differential Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                          |          |                |           | Differential Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Register Name | Addr | Bits  | Value | Description                                                                                                                                                                                                                                                |  |

|---------------|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               |      |       | 1     |                                                                                                                                                                                                                                                            |  |

| PI_BY_4       | 35   | [2:2] | 0     | Normal Operation                                                                                                                                                                                                                                           |  |

|               |      |       |       | MODTYPE register is overridden and pi/4 modulation is used                                                                                                                                                                                                 |  |

|               |      |       | 1     |                                                                                                                                                                                                                                                            |  |

| INTERP_RATIO  | 36   | [6:0] | d5    | This register defines the interpolation ratio to be used by the programmable interpolator. Since there is a fixed 8x interpolator, the total interpolation is 8*INTERP_RATIO.                                                                              |  |

| SEED0         | 37   | [7:0] | d255  | These 2 registers are concatenated to get a 15 bit SEED register.                                                                                                                                                                                          |  |

| SEED1         | 38   | [6:0] | d127] | This register is used to program a seed value into the data randomizer.                                                                                                                                                                                    |  |

| GBAND         | 39   | [7:0] | d5    | This register programs the number of symbols to be used a s guard band.                                                                                                                                                                                    |  |

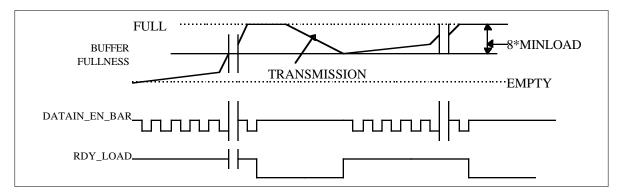

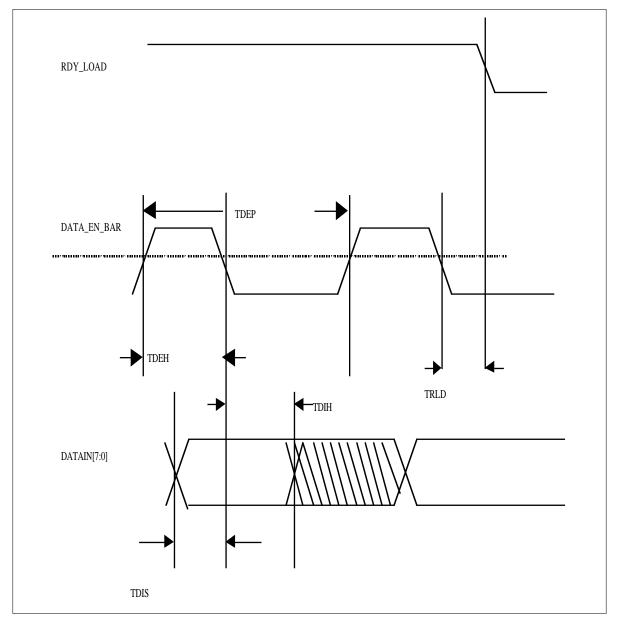

| MINLOAD       | 40   | [7:0] | d13   | This register is used to program the level of emptiness of the buffer that is required before the RDY_LOAD signal will be asserted (after the buffer has been completely filled.). The emptiness required is equal to 8*MINLOAD bytes.                     |  |

| MINXMIT       | 41   | [7:0] | d13   | ERRATA: This register is not usable.                                                                                                                                                                                                                       |  |

|               |      |       |       | Original Description is given below.                                                                                                                                                                                                                       |  |

|               |      |       |       | The Buffer controller can be programmed so that it will indicate to the external controller when certain level of fullness of buffer is reached . 8*MINXMIT is the minimum fullness (in bytes) that is required when the RDY_XMIT signal will be asserted. |  |

| DIG_EN        | 42   | [0:0] | 0     | Digital outputs are masked                                                                                                                                                                                                                                 |  |

|               |      |       |       | This bit enables the digital outputs of the modulator.                                                                                                                                                                                                     |  |

|               |      |       | 1     |                                                                                                                                                                                                                                                            |  |

| IQ_SWAP       | 42   | [1:1] | 0     | Normal Operation                                                                                                                                                                                                                                           |  |

|               |      |       |       | I,Q channels are swapped.                                                                                                                                                                                                                                  |  |

|               |      |       | 1     |                                                                                                                                                                                                                                                            |  |

| VALID_PR_RAM  | 42   | [2:2] | 0     | Selected Profile RAM data will not be transferred to program registers as soon as XMIT input is asserted.                                                                                                                                                  |  |

|               |      |       |       | Selected Profile RAM data will be transferred to program registers as soon as XMIT input is asserted                                                                                                                                                       |  |

|               |      |       | 1     |                                                                                                                                                                                                                                                            |  |

| SCALE         | 43   | [7:0] | d58   | This register is used to scale the output of the Nyquist filter. 64 is the center value.                                                                                                                                                                   |  |

| AMP_CTL       | 44   | [7:0] | d0    | This register value is output as the 1-bit output of a sigma-delta converter. This then may be used as a gain control voltage of the external amplifier.                                                                                                   |  |

| PROFILE       | 45   | [2:0] | d0    | This register is OR'd with the external PROFILE[2:0] pins to determine the profile to be used.                                                                                                                                                             |  |

| ATTENUATE     | 45   | [4:3] |       | This register controls attenuation of the modulator output into the                                                                                                                                                                                        |  |

| Register Name | Addr | Bits  | Value | Description                                                                                                                                                                                                 |

|---------------|------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |      |       |       | on-chip DAC.                                                                                                                                                                                                |

|               |      |       |       |                                                                                                                                                                                                             |

|               |      |       | 00    | No attenuation                                                                                                                                                                                              |

|               |      |       | 01    | _ attenuation                                                                                                                                                                                               |

|               |      |       | 10    | _ attenuation                                                                                                                                                                                               |

|               |      |       | 11    | unused                                                                                                                                                                                                      |

| DELAY         | 46   | [7:0] | d0    | There is a fixed delay and a programmable delay after which the encoder will respond to the XMIT pulse. This register defines the programmable delay in clock cycles whose frequency is (REF_CLK_FREQ*5/4). |

| OUT_FREQ_0    | 47   | [7:0] | d0    | These 3 registers are concatenated to give the 24 bit OUT_FREQ                                                                                                                                              |

| OUT_FREQ_1    | 48   | [7:0] | d25   | register. This controls the RF frequency.                                                                                                                                                                   |

| OUT_FREQ_2    | 49   | [7:0] | d0    |                                                                                                                                                                                                             |

|               |      |       |       |                                                                                                                                                                                                             |

| INIT_BUF      | 192  | [7:0] |       | When this value is written into the micro i/f address pointer register, the on-chip buffer is initialized. This may also be done using the INIT_BUF_BAR pin.                                                |

| READ_ROW      | 221  | [7:0] |       | When this value is loaded into the micro i/f address pointer register, the data contained in the location pointed to by NYQ_MEM_ADDR register is read into the NYQ_MEM_DATA register.                       |

| WRITE_ROW     | 238  | [7:0] |       | When this value is loaded into the micro i/f address pointer register, the data contained in NYQ_MEM_DATA register is written to the location pointed to by NYQ_MEM_ADDR register.                          |

| RESET         | 255  | [7:0] |       | When this value is written into the micro i/f address pointer register, the modulator is reset, without disturbing the programmed values.                                                                   |

# **Detailed Pin Description**

Table 3Detailed Pin List

### Modulator Pins(39)

| DATAIN[7:0]                        | I  | Upstream Data.                                                                                                                                                        | 8  |

|------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

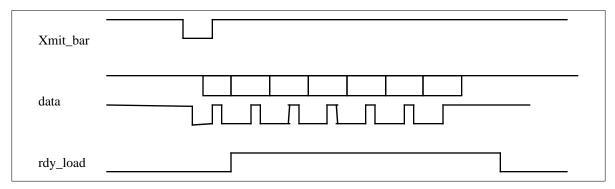

| RDY_LOAD                           | 0  | When high, Indicates that there is vacancy in the buffer. When th signal goes from low to high, it means that there is a vacancy equ to greater than 8*MINLOAD bytes. |    |

| RDY_XMIT                           | 0  | Errata:                                                                                                                                                               | 1  |

|                                    |    | Indicates that no transmission is currently in the pipeline.                                                                                                          |    |

|                                    |    | Original Description:                                                                                                                                                 |    |

|                                    |    | Indicates that one packet of data is stored in internal buffer, and a transmit operation may be done.                                                                 |    |

| INIT_BUF_BAR                       | ı  | Initializes internal Data Buffers                                                                                                                                     | 1  |

| DATAIN_EN_BAR                      | I  | Enable from data source indicating new byte to be loaded (active low)                                                                                                 | 1  |

| PROFILE[2:0]                       |    | Selects one out of 6 profiles                                                                                                                                         | 3  |

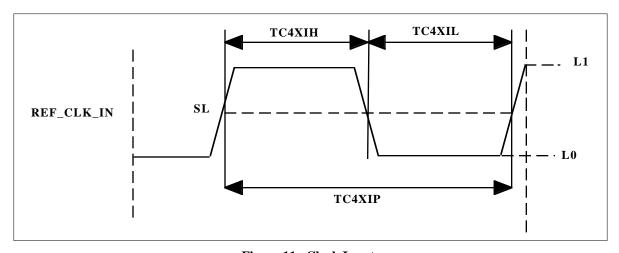

| REF_CLK_IN                         | ı  | Master Crystal Oscillator input                                                                                                                                       | 1  |

| REF_CLK_OUT                        | 0  | Master Crystal Oscillator output                                                                                                                                      | 1  |

| CPOUT                              | 0  | External Filter for on-chip Multiplier                                                                                                                                | 1  |

| CBL                                |    | Analog Pin                                                                                                                                                            | 1  |

| CBU                                |    | Analog Pin                                                                                                                                                            | 1  |

| PLL_BYPASS_BAR                     | I  | Bypasses on-chip Clock Multiplier when active(low).                                                                                                                   | 1  |

| XMIT_BAR                           |    | Transmit Enable Input (active Low)                                                                                                                                    | 1  |

| POWER_ADJ_SL                       | 0  | Sigma Delta output to control Amp power.                                                                                                                              | 1  |

| XMIT_EN                            | 0  | Transmit Enable Output (Delayed XMIT_IN)                                                                                                                              | 1  |

| DA_DIG[9:0]                        | Bi | Digital RF Output (can be disabled via programming).                                                                                                                  | 10 |

|                                    |    | DAC Test input when TEST_DAC_BAR = 0                                                                                                                                  |    |

| TEST_DAC_BAR                       |    | RF_D port becomes a input port for DAC testing.                                                                                                                       | 1  |

| CLK_DA                             | 0  | Output Sampling Clock for external D/A (High Speed)                                                                                                                   | 1  |

| DA_OUT                             | 0  | Analog RF Output                                                                                                                                                      | 1  |

| REXT                               | ı  | DAC Reference Voltage                                                                                                                                                 | 1  |

| RFREQ                              | I  | DAC Analog Pin                                                                                                                                                        | 1  |

| Upstream Control<br>Interface (13) |    |                                                                                                                                                                       |    |

| SELI2C                             | 1  | Selects I <sup>2</sup> C mode for control Interface when high. Selects GP uP when low.                                                                                | 1  |

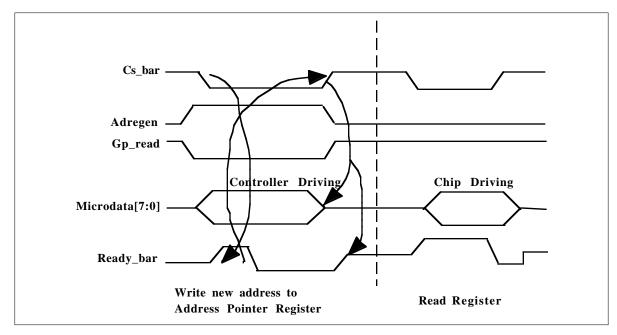

| CS_BAR[SCL]                        | I  | Chip Select Input for general purpose uP interface when SELI2C is low.                                                                                                | 1  |

| HD49429F                     |    |                                                                                                                                                                                                |     |

|------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                              |    | I <sup>2</sup> C Clock input when SELI2C is high.                                                                                                                                              |     |

| GP READ                      |    | Read/Write indicator for general purpose uP I/F                                                                                                                                                | 1   |

| RDY_BAR                      | 0  | Open Drain Output for general purpose uP I/F. De-assertion (low) of this signal after start of a transaction indicates to the master that the slave chip is ready to complete the transaction. | 1   |

| ADREGEN                      | I  | Chooses accessing of internal address pointer register or the register pointed to for general purpose uP I/F                                                                                   | 1   |

| MICRODATA[7:0]               | Bi | General Purpose uP Interface bi-directional Data bus when SELI2C is low.                                                                                                                       | 8   |

|                              |    | D[0] acts as I <sup>2</sup> C Data I/O when SELI2C is high                                                                                                                                     |     |

|                              |    | D[7:1] acts as I <sup>2</sup> C Device address input.                                                                                                                                          |     |

| Upstream Control<br>Pins(3)  |    |                                                                                                                                                                                                |     |

| RESET_BAR                    |    | Power-on Reset                                                                                                                                                                                 | 1   |

| SCAN_BAR                     | I  | For Test Purposes only                                                                                                                                                                         | 1   |

| TEST_BAR                     | ı  | For Test Purposes only                                                                                                                                                                         | 1   |

| Power and Ground<br>Pins(45) |    |                                                                                                                                                                                                |     |

| VDD                          | Р  |                                                                                                                                                                                                | 17  |

| VSS                          | Р  |                                                                                                                                                                                                | 24  |

| AVDD                         | Р  |                                                                                                                                                                                                | 2   |

| AVSS                         | Р  |                                                                                                                                                                                                | 2   |

| NC                           |    |                                                                                                                                                                                                | 0   |

| TOTAL                        |    |                                                                                                                                                                                                | 100 |

# **Package Pin Assignment**

| Name          | Package Pin No. |

|---------------|-----------------|

| vss           | 1               |

| vss           | 2               |

| vdd           | 3               |

| pwr_adj_sl    | 4               |

| xmit_en       | 5               |

| datain[0]     | 6               |

| vdd           | 7               |

| datain[1]     | 8               |

| vss           | 9               |

| datain[2]     | 10              |

| datain[3]     | 11              |

| datain[4]     | 12              |

| datain[5]     | 13              |

| datain[6]     | 14              |

| vddr          | 15              |

| datain[7]     | 16              |

| vss           | 17              |

| profile[2]    | 18              |

| profile[1]    | 19              |

| vdd           | 20              |

| profile[0]    | 21              |

| reset_bar     | 22              |

| vdd           | 23              |

| vss           | 24              |

| vss           | 25              |

| vss           | 26              |

| vss           | 27              |

| datain_en_bar | 28              |

| xmit_bar      | 29              |

| vdd           | 30              |

| init_buf_bar  | 31              |

| da_dig[0]     | 32              |

| da_dig[1]     | 33              |

| vss           | 34              |

| da_dig[2]     | 35              |

| da_dig[3]     | 36              |

| vdd         37           da_dig[4]         38           da_dig[5]         39           da_dig[7]         41           vss         42           da_dig[8]         43           vdd         44           da_dig[9]         45           clk da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         56           vdd         57           vdd         58           pl_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavd         66           ffreq         67           rext         68           da_out | Name           | Package Pin No. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|

| da_dig[5]         39           da_dig[6]         40           da_dig[7]         41           vss         42           da_dig[8]         43           vdd         44           da_dig[9]         45           clk_da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavs         64           cpout         65           pllavs         64           cpout         65           pllavd         66           dfeq         69           cbu | vdd            | 37              |

| da_dig[6]         40           da_dig[7]         41           vss         42           da_dig[8]         43           vdd         44           da_dig[9]         45           clk_da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         56           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           da_out         69           cbu         70           cbl         71           dacavss         72                                                                    | da_dig[4]      | 38              |

| da_dig[7]         41           vss         42           da_dig[8]         43           vdd         44           da_dig[9]         45           clk_da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         56           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavs         64           cpout         65           pllavdd         66           ffreq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                      | da_dig[5]      | 39              |

| vss         42           da_dig[8]         43           vdd         44           da_dig[9]         45           clk_da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           ffreq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                           | da_dig[6]      | 40              |

| da_dig[8]     43       vdd     44       da_dig[9]     45       clk_da     46       test_dac_bar     47       vdd     48       vss     49       vss     50       vss     51       vss     52       vss     53       ref_clk_in     54       ref_clk_out     55       vdd     56       vdd     58       pll_bypass_bar     59       scan_bar     60       test_bar     61       vdd     62       vss     63       pllavs     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                           | da_dig[7]      | 41              |

| vdd         44           da_dig[9]         45           clk_da         46           test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           rfreq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                            | vss            | 42              |

| da_dig[9]       45         clk_da       46         test_dac_bar       47         vdd       48         vss       49         vss       50         vss       51         vss       52         vss       53         ref_clk_in       54         ref_clk_out       55         vdd       56         vdd       57         vdd       58         pll_bypass_bar       59         scan_bar       60         test_bar       61         vdd       62         vss       63         pllavss       64         cpout       65         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                   | da_dig[8]      | 43              |

| cik_da       46         test_dac_bar       47         vdd       48         vss       49         vss       50         vss       51         vss       52         vss       53         ref_clk_in       54         ref_clk_out       55         vdd       56         vdd       57         vdd       58         pll_bypass_bar       59         scan_bar       60         test_bar       61         vdd       62         vss       63         pllavss       64         cpout       65         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                                              | vdd            | 44              |

| test_dac_bar         47           vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           freq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                 | da_dig[9]      | 45              |

| vdd         48           vss         49           vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           freq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                   | clk_da         | 46              |

| vss     49       vss     50       vss     51       vss     52       vss     53       ref_clk_in     54       ref_clk_out     55       vdd     56       vdd     57       vdd     58       pll_bypass_bar     59       scan_bar     60       test_bar     61       vdd     62       vss     63       pllavss     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                                                                                                                                       | test_dac_bar   | 47              |

| vss         50           vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                                                                                               | vdd            | 48              |

| vss         51           vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                                                                                                                        | vss            | 49              |

| vss         52           vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           freq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                                                                                                                       | vss            | 50              |

| vss         53           ref_clk_in         54           ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           rfreq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                                                                                                                                               | vss            | 51              |

| ref_clk_in       54         ref_clk_out       55         vdd       56         vdd       57         vdd       58         pll_bypass_bar       59         scan_bar       60         test_bar       61         vdd       62         vss       63         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vss            | 52              |

| ref_clk_out         55           vdd         56           vdd         57           vdd         58           pll_bypass_bar         59           scan_bar         60           test_bar         61           vdd         62           vss         63           pllavss         64           cpout         65           pllavdd         66           rfreq         67           rext         68           da_out         69           cbu         70           cbl         71           dacavss         72                                                                                                                                                                                                                                                                                                                                                                                                                        | vss            | 53              |

| vdd     56       vdd     57       vdd     58       pll_bypass_bar     59       scan_bar     60       test_bar     61       vdd     62       vss     63       pllavss     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ref_clk_in     | 54              |

| vdd     57       vdd     58       pll_bypass_bar     59       scan_bar     60       test_bar     61       vdd     62       vss     63       pllavss     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ref_clk_out    | 55              |

| vdd     58       pll_bypass_bar     59       scan_bar     60       test_bar     61       vdd     62       vss     63       pllavss     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vdd            | 56              |

| pll_bypass_bar       59         scan_bar       60         test_bar       61         vdd       62         vss       63         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vdd            | 57              |

| scan_bar       60         test_bar       61         vdd       62         vss       63         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vdd            | 58              |

| test_bar 61  vdd 62  vss 63  pllavss 64  cpout 65  pllavdd 66  rfreq 67  rext 68  da_out 69  cbu 70  cbl 71  dacavss 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | pll_bypass_bar | 59              |

| vdd     62       vss     63       pllavss     64       cpout     65       pllavdd     66       rfreq     67       rext     68       da_out     69       cbu     70       cbl     71       dacavss     72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | scan_bar       | 60              |

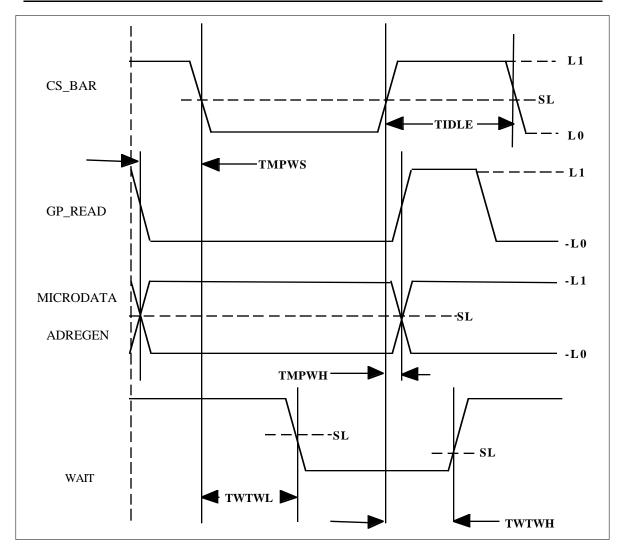

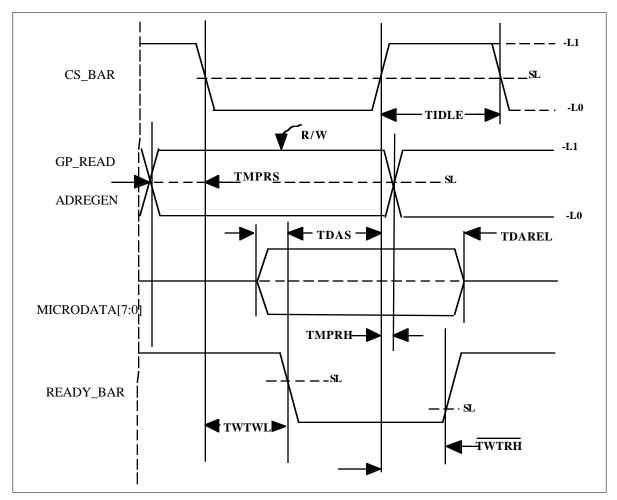

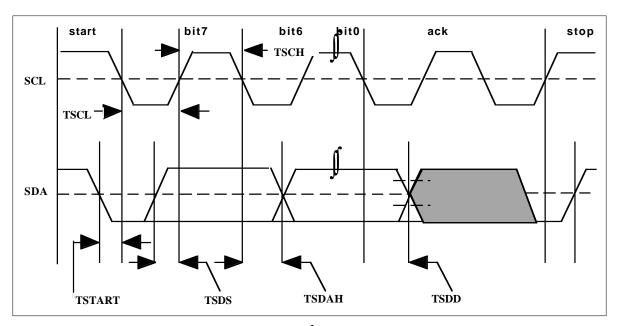

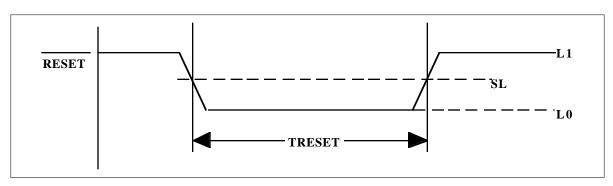

| vss       63         pllavss       64         cpout       65         pllavdd       66         rfreq       67         rext       68         da_out       69         cbu       70         cbl       71         dacavss       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | test_bar       | 61              |