# H8S/2245 Series Overview

Hitachi Single-Chip Microprocessor

# **HITACHI**

ADE-802-194 Rev. 1

3/96

Hitachi

# **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Preface

Hitachi's H8S Series of single-chip microcomputers comprises new series which offer the high performance and low power consumption of the existing H8 Series, which is widely used for machine control, etc., together with significantly greater ease of use,

The H8S/2245 Series offers CPU object-level compatibility with the H8/300H Series, H8/300 Series, and H8/300L Series within the H8 Series.

| Series   | Features                                                                                                                                                       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H8S/2245 | Upward-compatible with the H8/300H Series and H8/300 Series; twice the performance at the same frequency                                                       |

| H8/300H  | 16-Mbyte linear address space; upward-compatible with the H8/300 Series; concise instruction set; powerful word-size and longword-size arithmetic instructions |

| H8/300   | 64-kbyte address space; general register system; concise instruction set; powerful bit manipulation instructions                                               |

| H8/300L  | Same CPU as the H8/300 Series; consumer application oriented peripheral functions; low voltage, low power consumption                                          |

# **Intended Readership**

This Overview is intended for readers who require a basic understanding of microcomputers, or are looking for information on the features and functions of the H8S/2245 Series. Readers undertaking system design using these products, or requiring more detailed information on their use, should refer to the H8S/2245 Series Hardware Manual and H8S/2600 Series, H8S/2000 Series Programming Manual.

#### **Related Documents**

| Contents                                  | Document Title and No.                                             |

|-------------------------------------------|--------------------------------------------------------------------|

| On H8S/2245 hardware                      | H8S/2245 Series Hardware Manual<br>ADE-602-100                     |

| On H8S/2245 Series execution instructions | H8S/2600 Series, H8S/2000 Series Programming<br>Manual ADE-602-083 |

# Contents

| -  | C     |   |

|----|-------|---|

| Dr | eface | 1 |

|    | STACE |   |

| Section 1 H8S/2245 Series Features       | 1  |

|------------------------------------------|----|

| 1.1 H8S/2245 Series Functions            | 1  |

| 1.2 Pin Description                      | 5  |

| 1.3 Block Diagram                        | 9  |

|                                          |    |

| Section 2 CPU                            | 11 |

| 2.1 Features                             | 11 |

| 2.2 Register Configuration               | 14 |

| 2.2.1 General Registers                  | 15 |

| 2.2.2 Control Registers                  | 15 |

| 2.3 Data Formats                         | 18 |

| 2.4 Addressing Modes                     | 21 |

| 2.4.1 Effective Address (EA) Calculation | 21 |

| 2.5 Instruction Set                      | 23 |

| 2.5.1 Features                           | 23 |

| 2.5.2 Assembler Format                   | 23 |

| 2.5.3 Instruction Set Tables             | 24 |

| 2.6 Basic Bus Timing                     | 47 |

| 2.7 Basic Clock Timing                   | 47 |

| 2.8 CPU Read/Write Cycles                | 47 |

| 2.9 Processing States                    | 51 |

| 2.10 Exception Handling                  | 53 |

| 2.11 Interrupts                          | 55 |

| 2.11.1 Interrupt Control                 | 55 |

| 2.12 Operating Modes                     | 60 |

| 2.12.1 Normal Modes (Modes 1 to 3)       | 60 |

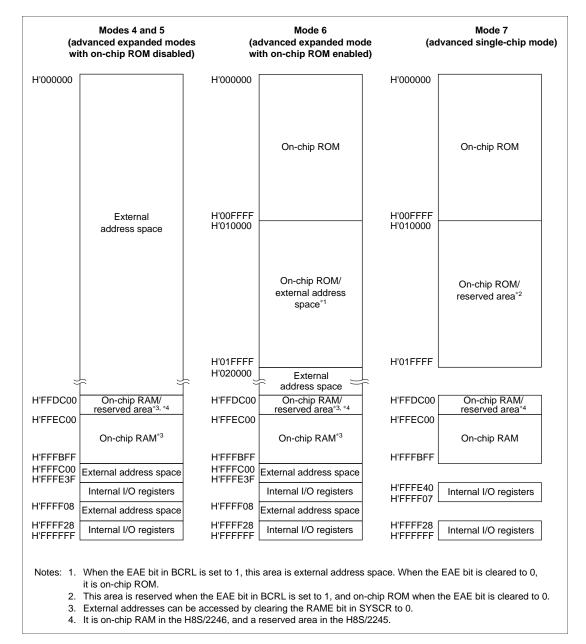

| 2.12.2 Advanced Modes (Modes 4 to 7)     | 60 |

| 2.13 Address Map                         | 63 |

| Section 2 Designations                   |    |

| Section 3 Peripheral Functions           | 66 |

| 3.1 Bus Controller (BSC)                 | 66 |

| Features                                 | 66 |

| Bus Controller Block Diagram             | 67 |

| 3.1.1 Area Partitioning                  | 67 |

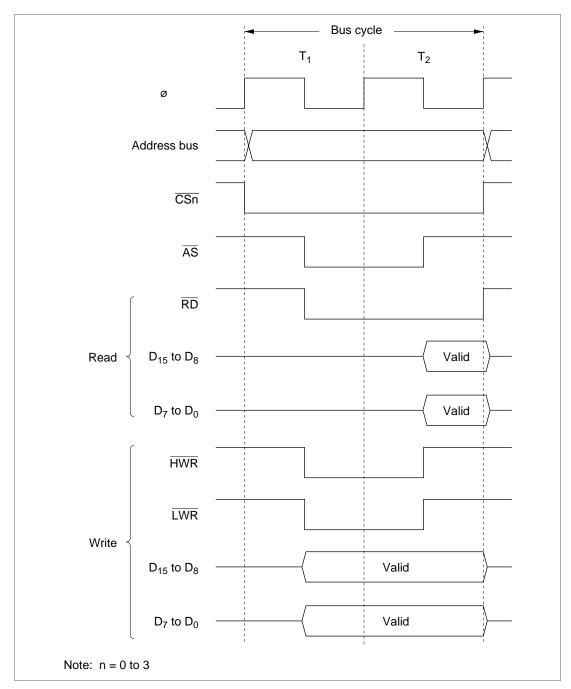

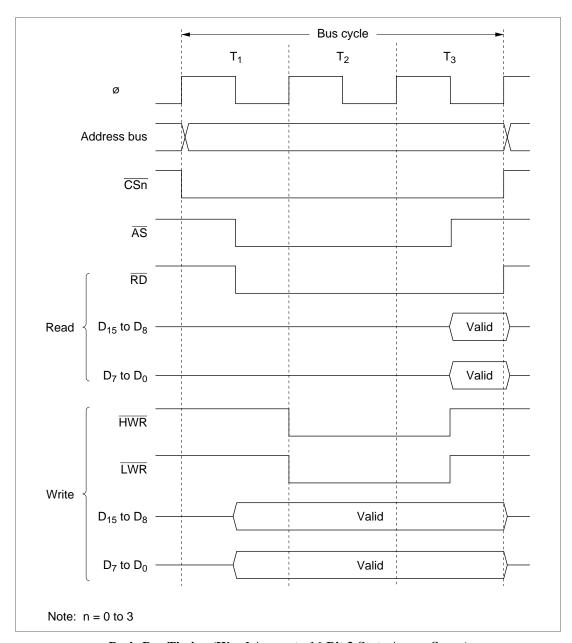

| 3.1.2 Basic Bus Interface                | 69 |

| Basic Bus Timing                         | 70 |

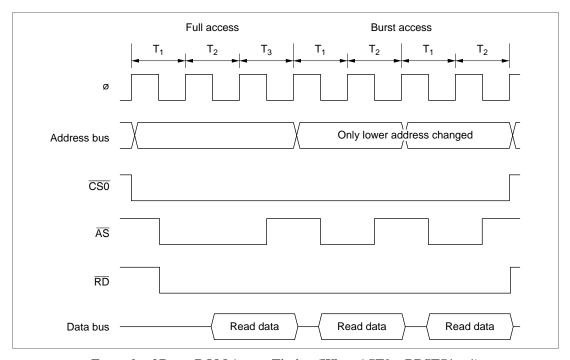

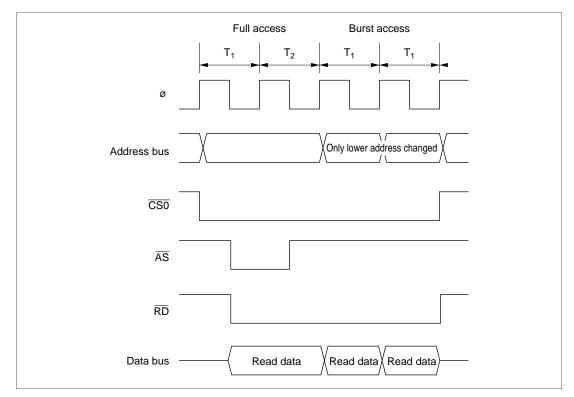

| 3.1.3 Burst ROM Interface                | 72 |

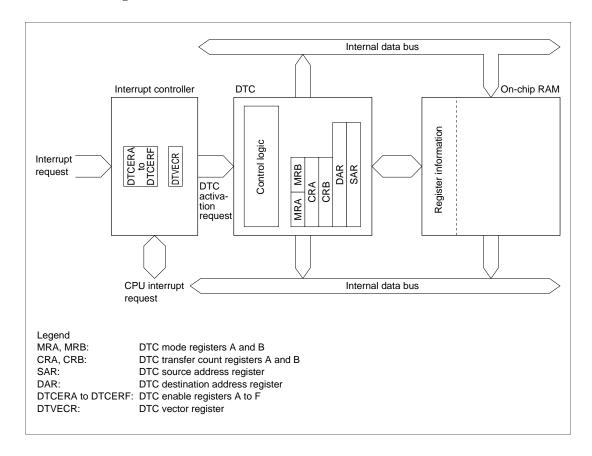

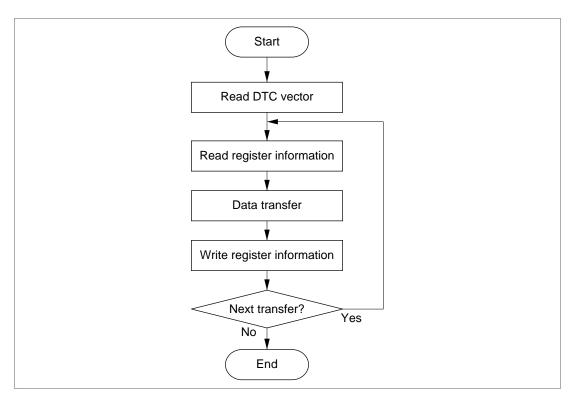

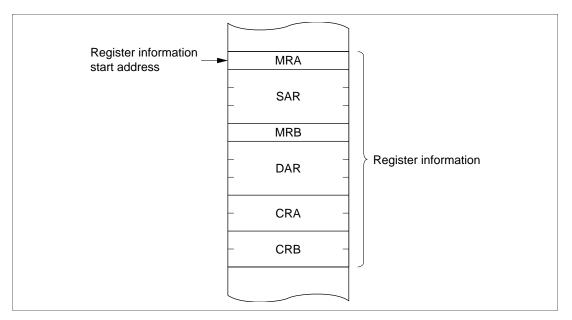

| 3.2 Data Transfer Controller (DTC)                              | 74  |

|-----------------------------------------------------------------|-----|

| Features                                                        | 74  |

| DTC Block Diagram                                               | 75  |

| 3.2.1 Data Transfer Operation                                   | 75  |

| 3.2.2 Transfer Modes                                            | 80  |

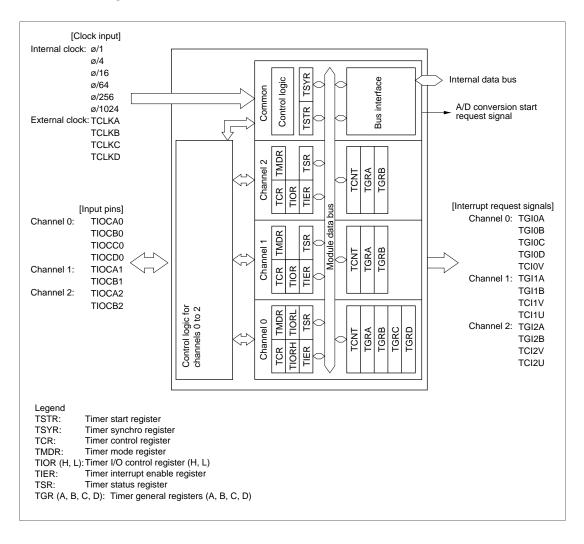

| 3.3 16-Bit Timer Pulse Unit (TPU)                               | 85  |

| Features                                                        | 85  |

| TPU Block Diagram                                               | 86  |

| Interrupt Sources and Data Transfer Controller (DTC) Activation | 87  |

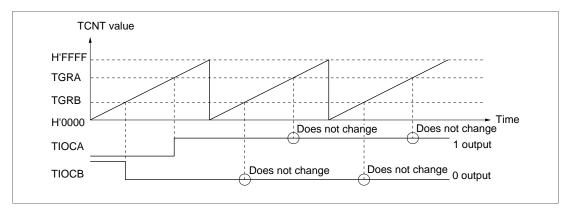

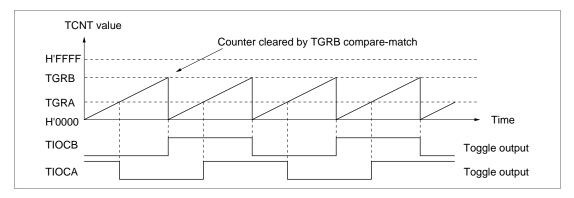

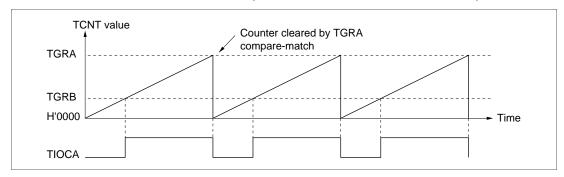

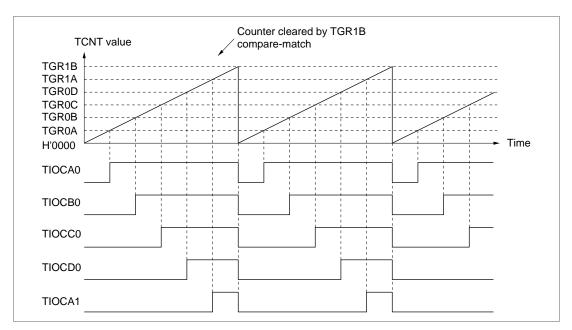

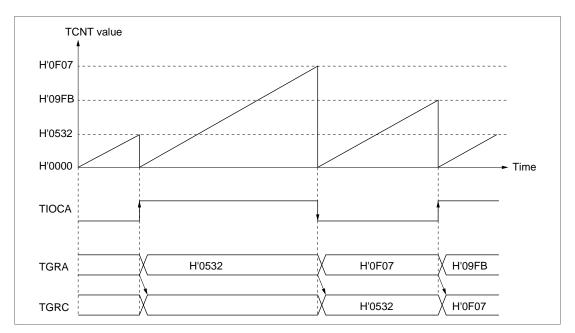

| Operation                                                       | 87  |

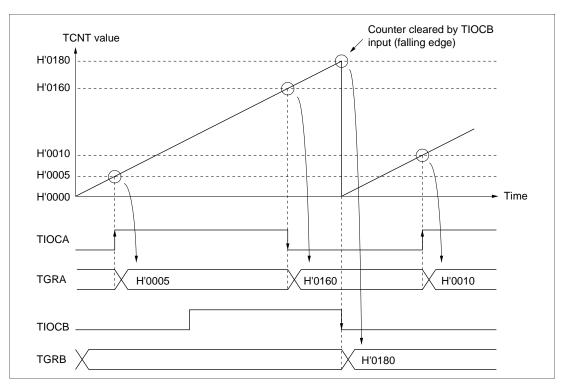

| Input Capture Operation                                         | 90  |

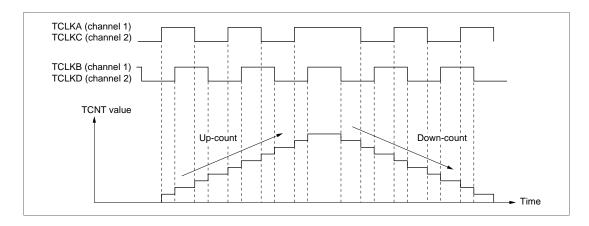

| Phase Counting Mode                                             | 91  |

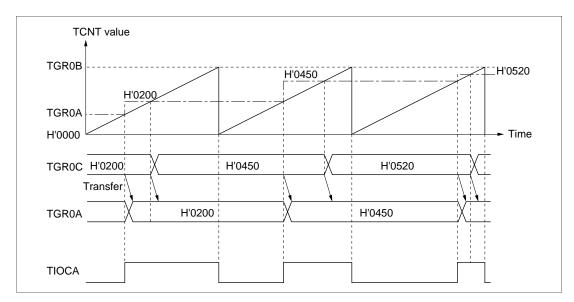

| Buffer Operation                                                | 92  |

| Synchronous Operation                                           | 94  |

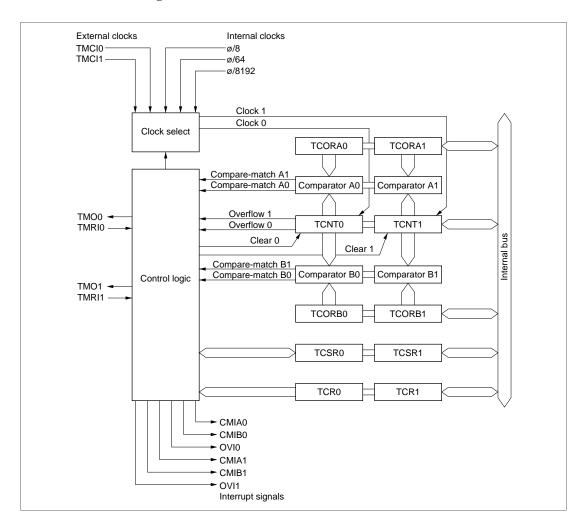

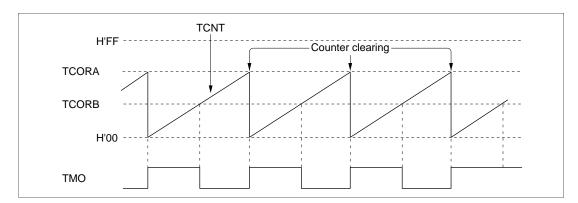

| 3.4 8-Bit Timer                                                 | 95  |

| Features                                                        | 95  |

| 8-Bit Timer Block Diagram                                       | 96  |

| Interrupt Source and Data Transfer Controller (DTC) Activation  | 97  |

| Example of Pulse Output                                         | 97  |

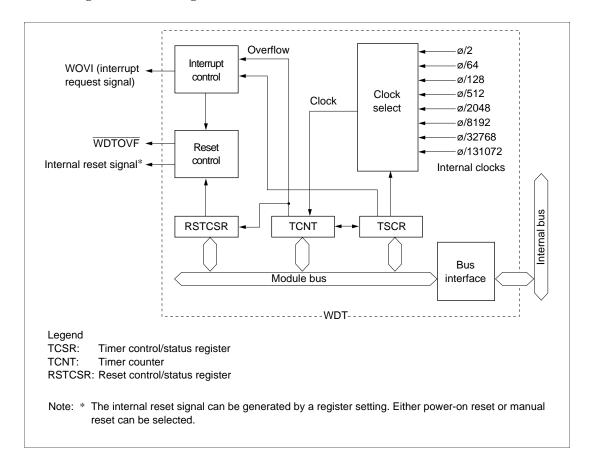

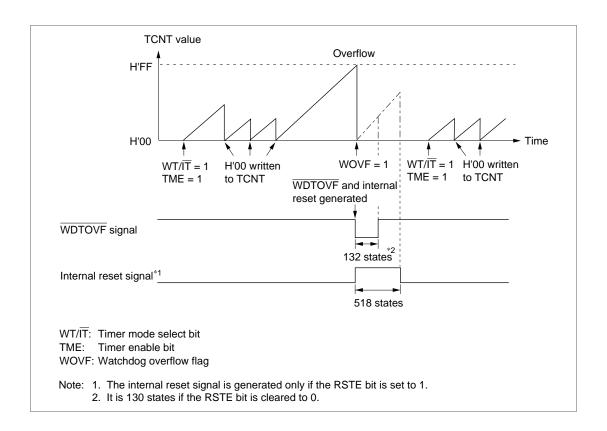

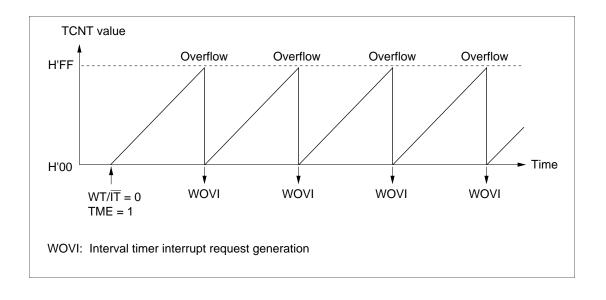

| 3.5 Watchdog Timer                                              | 98  |

| Features                                                        | 98  |

| Watchdog Timer Block Diagram                                    | 99  |

| Watchdog Timer Operation                                        | 99  |

| Interval Timer Operation                                        | 100 |

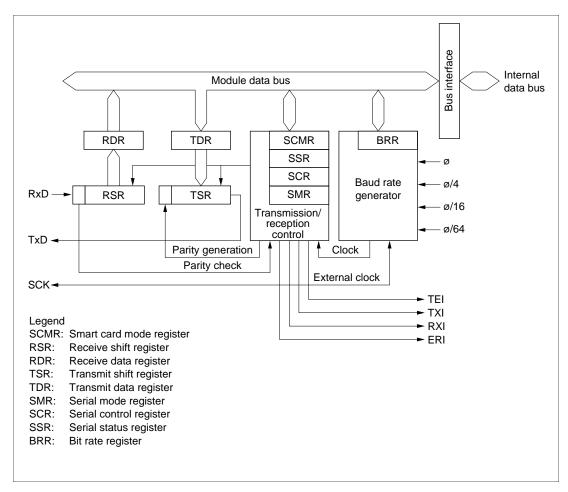

| 3.6 Serial Communication Interface (SCI)                        | 102 |

| Features                                                        | 102 |

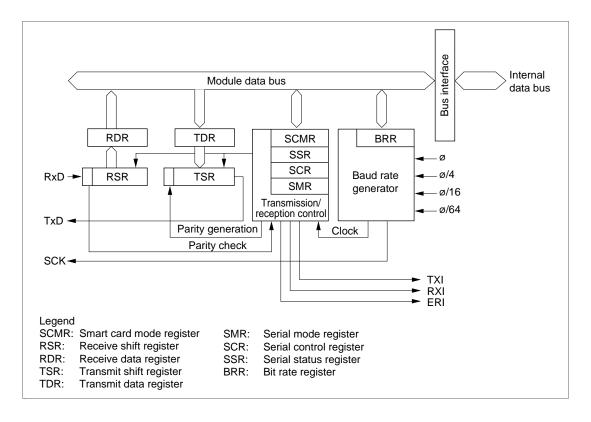

| SCI Block Diagram                                               | 103 |

| 3.6.1 SCI Asynchronous Communication                            | 104 |

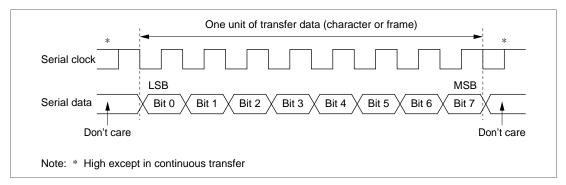

| 3.6.2 SCI Synchronous Communication                             | 106 |

| 3.7 Smart Card Interface                                        | 111 |

| Features                                                        | 111 |

| Smart Card Interface Block Diagram                              | 112 |

| Outline of Operation                                            | 112 |

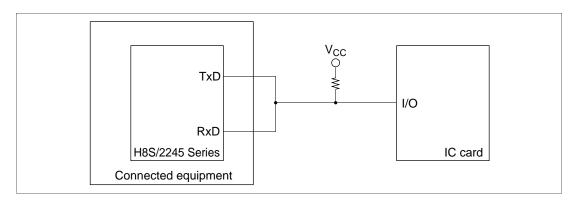

| Schematic Connection Diagram                                    | 113 |

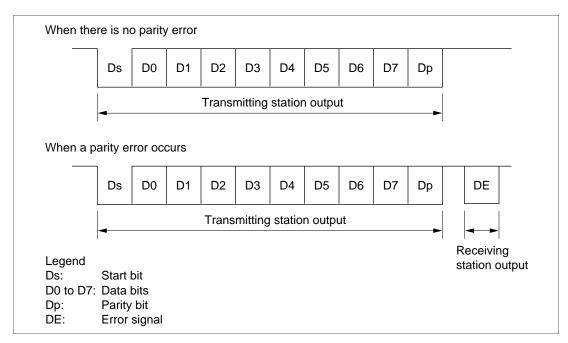

| Data Format                                                     | 113 |

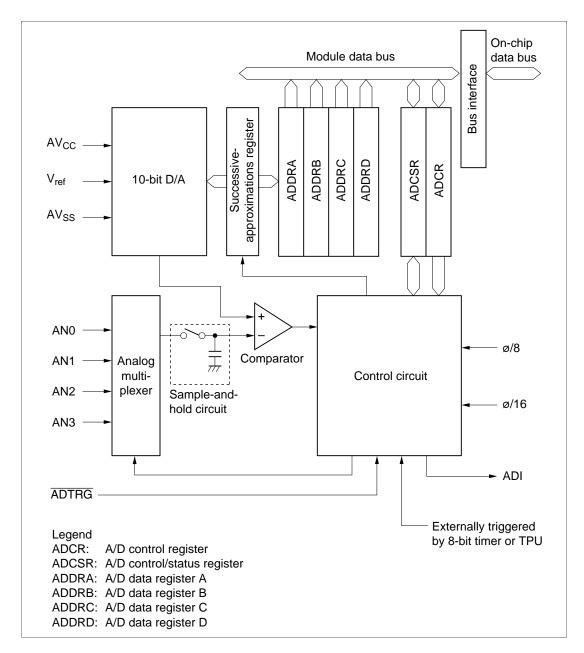

| 3.8 A/D Converter                                               | 114 |

| Features                                                        | 114 |

| A/D Converter Block Diagram                                     | 115 |

| Input Channel Setting                                           | 116 |

| Operation                                                       | 116 |

| 3.9 I/O Ports                                                   | 117 |

| Port Functions in Each Operating Mode                           | 117 |

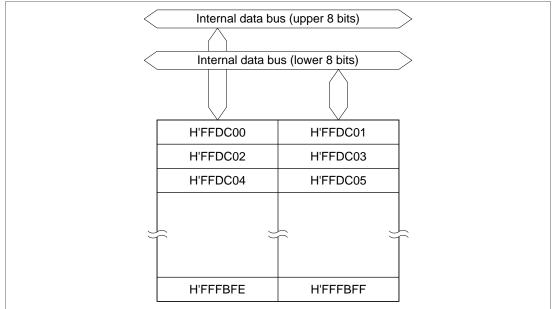

| 3.10 RAM                                                        | 123 |

| Block        | Diagram of RAM (Example with H8S/2246 in Advanced Mode)           | 123 |

|--------------|-------------------------------------------------------------------|-----|

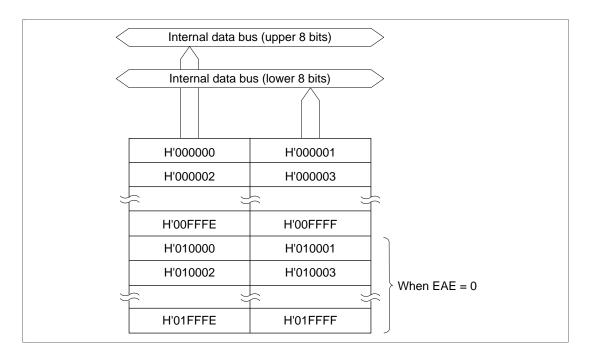

| 3.11 ROM (   | PROM)                                                             | 124 |

| Block        | Diagram of ROM (Example with H8S/2246 and H8S/2245 in Modes 6, 7) | 124 |

| PRO          | M Programming                                                     | 124 |

| G .: 4       |                                                                   |     |

|              | Power-Down State                                                  |     |

| 4.1 Power-L  | Oown State                                                        | 125 |

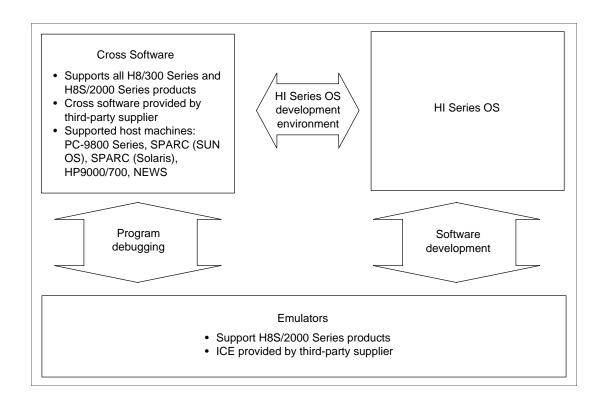

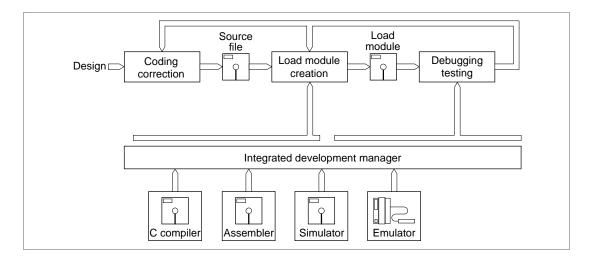

| Section 5    | Development Environment                                           | 128 |

| 5.1 Develop  | ment Environment                                                  | 128 |

| Lineu        | p                                                                 | 128 |

| 5.2 Cross Sc | ftware                                                            | 130 |

|              | mpiler                                                            |     |

| Asser        | nbler                                                             | 130 |

| Simul        | lator/Debugger                                                    | 130 |

| 5.3 Graphica | al User Interface                                                 | 132 |

| -            | rated Development Manager (EWS)*                                  |     |

| _            | eptual Diagram of Integrated Development Manager                  |     |

|              | 0 PC GUI (PC)                                                     |     |

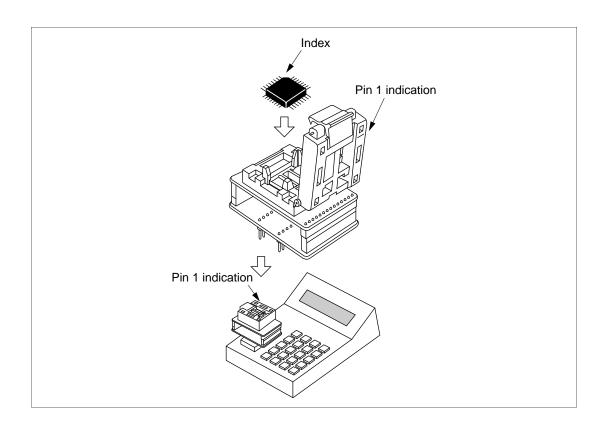

|              | Adapters                                                          |     |

|              | cable EPROM Writer Table                                          |     |

|              | od of Use (In Case of HS2245ESNS1H)                               |     |

|              | rs                                                                |     |

|              | 0/E7000PC                                                         |     |

|              |                                                                   |     |

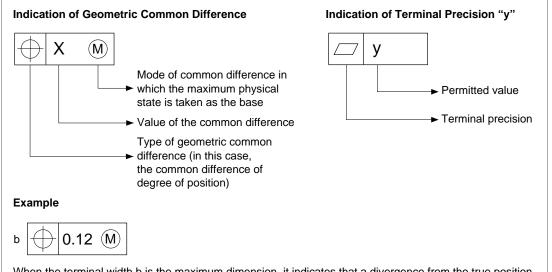

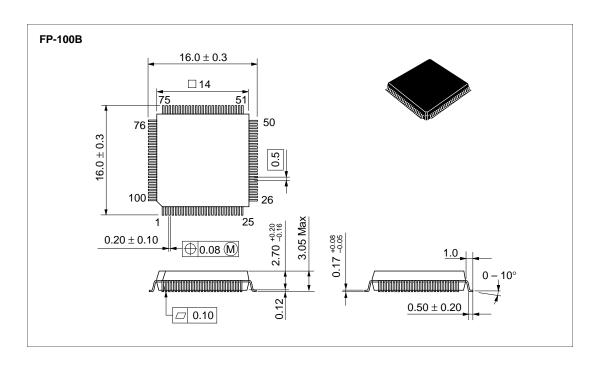

| Appendix     |                                                                   | 138 |

| Package      |                                                                   | 138 |

| Packa        | ge Outline Dimensions (Unit: mm)                                  | 138 |

|              |                                                                   |     |

| Figures      |                                                                   |     |

| Figure 1.1   | 100-Pin Plastic TQFP (FP-100B, TFP-100B)                          |     |

| Figure 1.2   | Block Diagram                                                     | 10  |

| Figure 2.1   | CPU Internal Register Configuration                               |     |

| Figure 2.2   | Use of General Registers                                          |     |

| Figure 2.3   | General Register Data Formats                                     | 19  |

| Figure 2.4   | Memory Data Formats                                               | 20  |

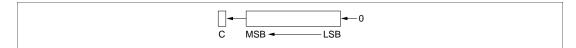

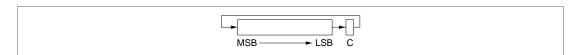

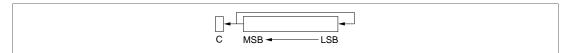

| Figure 2.5   | SHAL Operation                                                    | 33  |

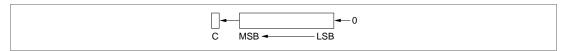

| Figure 2.6   | SHAR Operation                                                    | 34  |

| Figure 2.7   | SHLL Operation                                                    | 34  |

| Figure 2.8   | SHLR Operation                                                    | 34  |

| Figure 2.9   | ROTXL Operation                                                   | 34  |

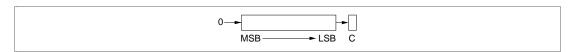

| Figure 2.10  | ROTXR Operation                                                   | 34  |

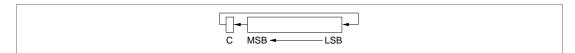

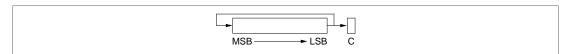

| Figure 2.11  | ROTL Operation                                                    | 34  |

| Figure 2.12 | ROTR Operation                                                | 34 |

|-------------|---------------------------------------------------------------|----|

| Figure 2.13 | Basic Clock Timing                                            | 47 |

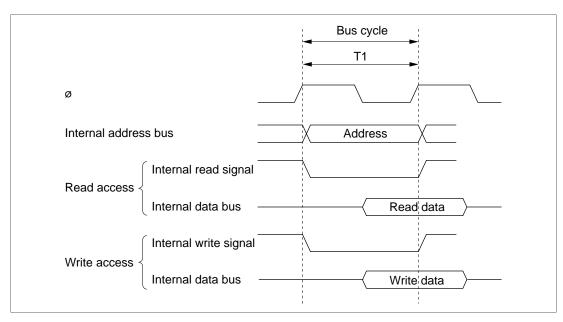

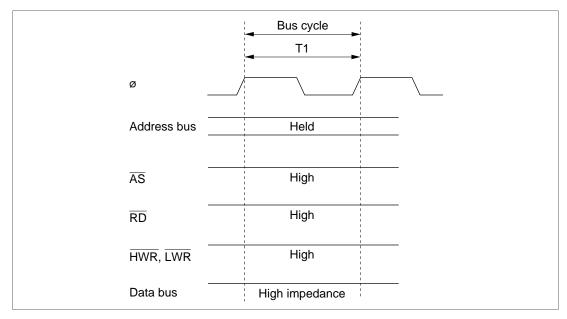

| Figure 2.14 | On-Chip Memory Access Cycle (One-State Access)                | 48 |

| Figure 2.15 | Pin States during On-Chip Memory Access                       | 48 |

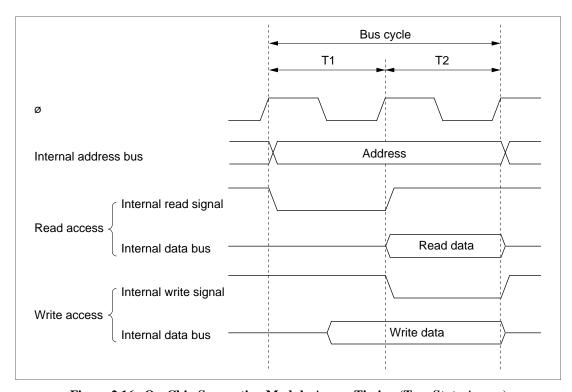

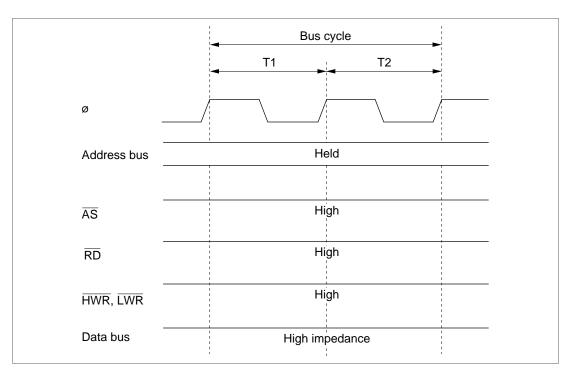

| Figure 2.16 | On-Chip Supporting Module Access Timing (Two-State Access)    | 49 |

| Figure 2.17 | Pin States during On-Chip Supporting Module Access            | 50 |

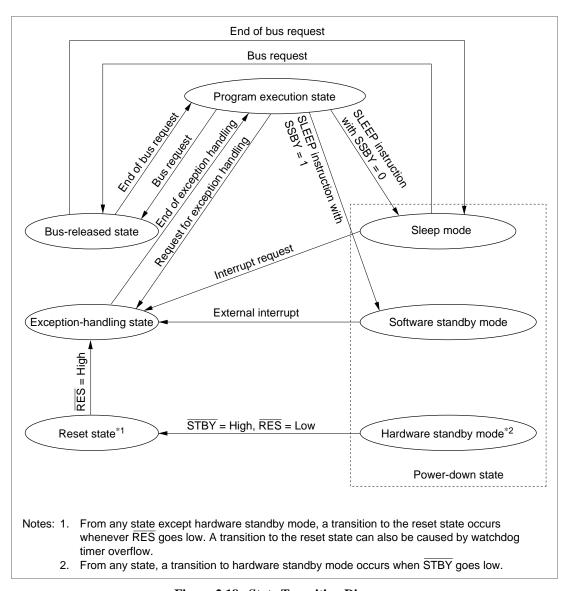

| Figure 2.18 | State Transition Diagram                                      | 52 |

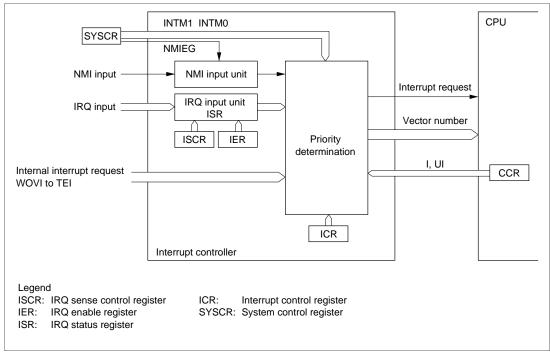

| Figure 2.19 | Block Diagram of Interrupt Controller                         | 55 |

| Figure 2.20 | Block Diagram of Interrupt Control Operation                  | 56 |

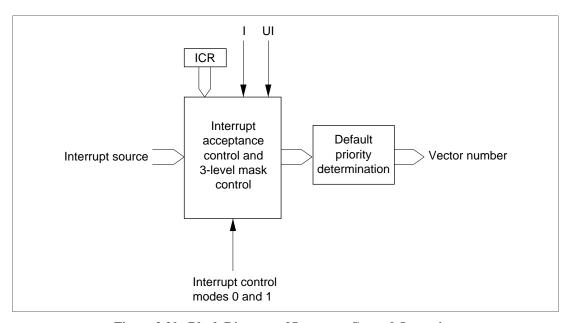

| Figure 2.21 | Normal Mode Address Map                                       | 64 |

| Figure 2.22 | Advanced Mode Address Map                                     | 65 |

| Tables      |                                                               |    |

| Table 1.1   | MCU Operating Modes                                           | 3  |

| Table 1.2   | Product Lineup                                                | 4  |

| Table 1.3   | Pin Functions                                                 | 6  |

| Table 2.1   | Addressing Modes                                              | 21 |

| Table 2.2   | Data Transfer Instructions                                    | 24 |

| Table 2.3   | Arithmetic Instructions                                       | 27 |

| Table 2.4   | Logical Instructions                                          | 31 |

| Table 2.5   | Shift Instructions                                            | 32 |

| Table 2.6   | Bit Manipulation Instructions                                 | 35 |

| Table 2.7   | Branch Instructions                                           | 40 |

| Table 2.8   | System Control Instructions                                   | 42 |

| Table 2.9   | Program Transfer Instructions                                 | 44 |

| Table 2.10  | Number of States Required for Execution                       | 45 |

| Table 2.11  | Condition Code Notation                                       | 45 |

| Table 2.12  | Operation Notation                                            | 46 |

| Table 2.13  | Processing States                                             | 51 |

| Table 2.14  | Exception Handling Types and Priorities                       | 53 |

| Table 2.15  | Exception Vector Table                                        | 54 |

| Table 2.16  | Interrupt Control Modes                                       | 56 |

| Table 2.17  | Interrupt Sources, Vector Addresses, and Interrupt Priorities | 58 |

| Table 2.18  | Operating Modes                                               | 62 |

# Section 1 H8S/2245 Series Features

#### 1.1 H8S/2245 Series Functions

H8S/2245 Series microcomputers are designed for faster instruction execution, using a realtime control oriented CPU with an internal 32bit architecture, and can run programs based on the C high-level language efficiently. As well as large-capacity ROM and RAM, these microcomputers include on-chip the peripheral functions needed for control systems. These features simplify the implementation of sophisticated, high-performance systems.

# High-Performance H8S/2000 CPU

- General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- High-speed operation suitable for realtime control

- 20 MHz maximum operating frequency (20 MHz oscillation frequency)

- High-speed arithmetic operations

8/16/32-bit register-register add/subtract: 50 ns

16 × 16-bit register-register multiply: 1000 ns

32/16-bit register-register divide: 1000 ns

- Instruction set suitable for high-speed operation

- Sixty-five basic instructions

- 8/16/32-bit move/arithmetic and logic instructions

- Unsigned/signed multiply and divide instructions

- Powerful bit-manipulation instructions

- Two CPU operating modes

- Normal mode: H8/300 Series compatible, maximum 64-kbyte address space

- Advanced mode: Maximum 16-Mbyte address space

#### **On-Chip Byte PROM (Mask ROM)**

128 Kbytes

#### **On-Chip High-Speed Static RAM**

4 Kbytes or 8 Kbytes

#### **On-Chip Bus Controller**

- Address space divided into 8 areas, with bus specifications settable independently for each area

- Chip select output possible for each area ( $\overline{CS0}$  to  $\overline{CS3}$ )

- Selection of 8-bit or 16-bit access space for each area

- 2-state or 3-state access space can be designated for each area

- Number of program wait states can be set for each area

- Burst ROM directly connectable

- External bus release function

#### **Data Transfer Controller (DTC)**

- · Activated by internal interrupt or software

- Multiple transfers or multiple types of transfer possible for one activation source

- Transfer possible in repeat mode, block transfer mode, etc.

- Request can be sent to CPU for interrupt that activated DTC

#### 16-Bit Timer-Pulse Unit (TPU)

- Three-channel 16-bit timer on-chip

- Pulse I/O processing capability for up to 8 pins'

- Automatic 2-phase encoder count capability

#### **Two On-Chip 8-Bit Timer Channels**

- 8-bit up-counter (external event count capability)

- Two time constant registers

- Two-channel connection possible

#### On-Chip Watchdog Timer (WDT)

• Watchdog timer or interval timer selectable

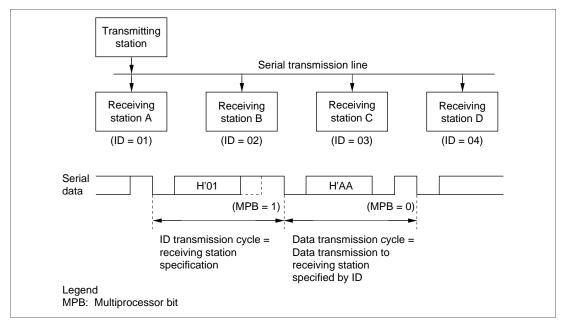

#### Three On-Chip Serial Communication Interface (SCI) Channels

- Asynchronous mode or synchronous mode selectable

- Multiprocessor communication function

- Smart card interface function

#### On-Chip A/D Converter

Resolution: 10 bitsInput: 4 channels

- Single or scan mode selectable

- Sample and hold circuit

- A/D conversion can be activated by external trigger or timer trigger

#### Twelve I/O Ports

• 75 I/O pins, 4 input-only pins

# **On-Chip Interrupt Controller**

- Nine external interrupt pins (NMI,  $\overline{IRQ0}$  to  $\overline{IRQ7}$ )

- 34 internal interrupt sources

- Selection of two interrupt control modes

#### **Power-Down State**

- Medium-speed mode

- Sleep mode

- Module stop mode

- Software standby mode

- Hardware standby mode

Table 1.1 lists the MCU operating modes.

**Table 1.1** MCU Operating Modes

|      |                       |                                     |             | External Data Bus |                  |  |

|------|-----------------------|-------------------------------------|-------------|-------------------|------------------|--|

| Mode | CPU Operating<br>Mode | Description                         | On-Chip ROM | Initial Value     | Maximum<br>Value |  |

| 1    | Normal                | On-chip ROM disabled expansion mode | Disabled    | 8 bits            | 16 bits          |  |

| 2    | _                     | On-chip ROM enabled expansion mode  | Enabled     | 8 bits            | 16 bits          |  |

| 3    | _                     | Single-chip mode                    | Enabled     | _                 |                  |  |

| 4    | Advanced              | On-chip ROM disabled expansion mode | Disabled    | 16 bits           | 16 bits          |  |

| 5    | _                     | On-chip ROM disabled expansion mode | Disabled    | 8 bits            | 16 bits          |  |

| 6    | _                     | On-chip ROM enabled expansion mode  | Enabled     | 8 bits            | 16 bits          |  |

| 7    | _                     | Single-chip mode                    | Enabled     | _                 |                  |  |

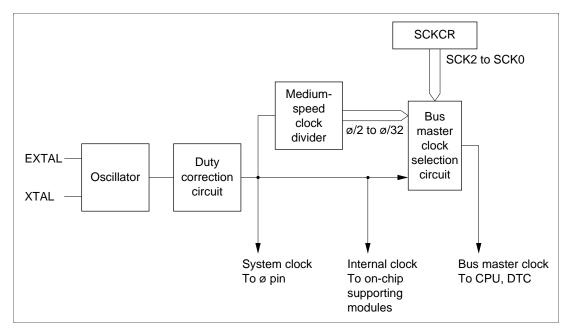

# **On-Chip Clock Pulse Generator**

• Built-in duty correction circuit

# **Packages**

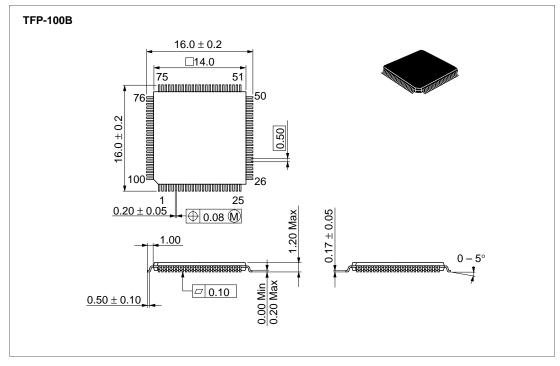

- 100-pin plastic QFP (FP-100B)

- 100-pin plastic TQFP (TFP-100B)

Table 1.2 lists the product lineup.

**Table 1.2** Product Lineup

# Model

| Mask ROM Version | ZTAT™ Version | ROM/RAM (Bytes) | Packages            |

|------------------|---------------|-----------------|---------------------|

| HD6432246        | HD6472246     | 128 k/8 k       | FP-100B<br>TFP-100B |

| HD6432245*       | _             | 128 k/4 k       | FP-100B<br>TFP-100B |

Note: Under development

# 1.2 Pin Description

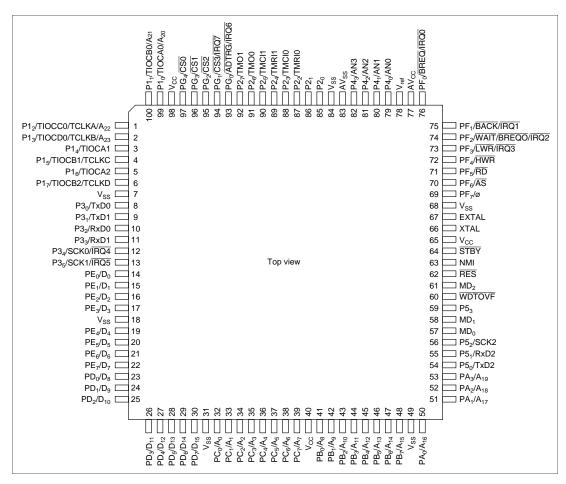

Figure 1.1 100-Pin Plastic TQFP (FP-100B, TFP-100B)

Table 1.3 lists the pin functions.

**Table 1.3** Pin Functions

| Туре                                                                                                                                                                                                                                                                                                                 | Symbol          | I/O    | Name and Function                                                                                                                                       |                                                                                  |                           |                                                 |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|-------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Power                                                                                                                                                                                                                                                                                                                | V <sub>CC</sub> | Input  |                                                                                                                                                         | r supply:<br>n power:                                                            |                           | ins should be connected to the                  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | V <sub>SS</sub> | Input  | <b>Ground:</b> All $V_{SS}$ pins should be connected to the spower supply (0 V).                                                                        |                                                                                  |                           |                                                 |  |  |  |  |  |  |  |  |  |

| Clock                                                                                                                                                                                                                                                                                                                | XTAL            | Input  | Conne                                                                                                                                                   | Connects to a crystal oscillator.                                                |                           |                                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | EXTAL           | Input  |                                                                                                                                                         | Connects to a crystal oscillator. The EXTAL pin can all input an external clock. |                           |                                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | Ø               | Output | Syste device                                                                                                                                            |                                                                                  | Supplies                  | the system clock to an external                 |  |  |  |  |  |  |  |  |  |

| Operating $\mathrm{MD}_2$ to $\mathrm{MD}_0$ Input mode control $\mathrm{MD}_2$ to $\mathrm{MD}_0$ Input mode control $\mathrm{MD}_2$ to $\mathrm{MD}_0$ Input in $\mathrm{MD}_2$ to $\mathrm{MD}_0$ and the operating mode is shown below. These pins should not be changed while the H8S/2245 Series is operating. |                 |        |                                                                                                                                                         |                                                                                  |                           |                                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        | $MD_2$                                                                                                                                                  | $MD_1$                                                                           | $MD_0$                    | Operating Mode                                  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        | 0                                                                                                                                                       | 0                                                                                | 0                         | _                                               |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         |                                                                                  | 1                         | Mode 1                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         | 1                                                                                | 0                         | Mode 2                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         |                                                                                  | 1                         | Mode 3                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        | 1                                                                                                                                                       | 0                                                                                | 0                         | Mode 4                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         |                                                                                  | 1                         | Mode 5                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         | 1                                                                                | 0                         | Mode 6                                          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      |                 |        |                                                                                                                                                         |                                                                                  | 1                         | Mode 7                                          |  |  |  |  |  |  |  |  |  |

| System control                                                                                                                                                                                                                                                                                                       | RES             | Input  | Reset                                                                                                                                                   | input: V                                                                         | Vhen this p               | oin is driven low, the chip is reset.           |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | STBY            | Input  |                                                                                                                                                         |                                                                                  | n this pin i<br>andby mod | s driven low, a transition is made le.          |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | BREQ            | Input  |                                                                                                                                                         |                                                                                  |                           | n external bus master to issue a 245 Series.    |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | BREQO           | Output | <b>Bus request output:</b> The external bus request signal used when an internal bus master accesses external space in the external bus-released state. |                                                                                  |                           |                                                 |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                      | BACK            | Output |                                                                                                                                                         | _                                                                                |                           | ge: Indicates that the bus has rnal bus master. |  |  |  |  |  |  |  |  |  |

**Table 1.3 Pin Functions (cont)**

| Туре                                 | Symbol                                  | I/O    | Name and Function                                                                                                                                     |

|--------------------------------------|-----------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupts                           | NMI                                     | Input  | Nonmaskable interrupt: Requests a nonmaskable interrupt.                                                                                              |

|                                      | IRQ7 to IRQ0                            | Input  | Interrupt request 7 to 0: These pins request a maskable interrupt.                                                                                    |

| Address bus                          | A <sub>23</sub> to A <sub>0</sub>       | Output | Address bus: These pins output an address.                                                                                                            |

| Data bus                             | D <sub>15</sub> to D <sub>0</sub>       | I/O    | Data bus: These pins constitute a bidirectional data bus.                                                                                             |

| Bus control                          | CS3 to CS0                              | Output | Chip select: Signals for selecting areas 3 to 0.                                                                                                      |

|                                      | ĀS                                      | Output | Address strobe: When this pin is low, it indicates that address output on the address bus is enabled.                                                 |

|                                      | RD                                      | Output | <b>Read:</b> When this pin is low, it indicates that the external address space can be read.                                                          |

|                                      | HWR                                     | Output | <b>High write:</b> A strobe signal that writes to external space and indicates that the upper half ( $D_{15}$ to $D_8$ ) of the data bus is enabled.  |

|                                      | LWR                                     | Output | <b>Low write:</b> A strobe signal that writes to external space and indicates that the lower half $(D_7 \text{ to } D_0)$ of the data bus is enabled. |

|                                      | WAIT                                    | Input  | Wait: Requests insertion of a wait state in the bus cycle when accessing external 3-state address space.                                              |

| 16-bit timer-<br>pulse unit<br>(TPU) | TCLKA to<br>TCLKD                       | Input  | Clock input A to D: These pins input an external clock.                                                                                               |

|                                      | TIOCA0,<br>TIOCB0,<br>TIOCC0,<br>TIOCD0 | I/O    | Input capture/output compare match A0 to D0: The TGR0A to TGR0D input capture input or output compare output, or PWM output pins.                     |

|                                      | TIOCA1,<br>TIOCB1                       | I/O    | Input capture/output compare match A1 and B1: The TGR1A and TGR1B input capture input or output compare output, or PWM output pins.                   |

|                                      | TIOCA2,<br>TIOCB2                       | I/O    | Input capture/output compare match A2 and B2: The TGR2A and TGR2B input capture input or output compare output, or PWM output pins.                   |

| 8-bit timer                          | TMO0, TMO1                              | Output | Compare match output: The compare match output pins.                                                                                                  |

|                                      | TMCI0,<br>TMCI1                         | Input  | Counter external clock input: Input pins for the external clock input to the counter.                                                                 |

|                                      | TMRI0,<br>TMRI1                         | Input  | Counter external reset input: The counter reset input pins.                                                                                           |

**Table 1.3 Pin Functions (cont)**

| Туре                                       | Symbol                             | I/O    | Name and Function                                                                                                                        |

|--------------------------------------------|------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| Watchdog<br>timer (WDT)                    | WDTOVF                             | Output | <b>Watchdog timer overflows:</b> The counter overflows signal output pin in watchdog timer mode.                                         |

| Serial communication                       | TxD2, TxD1,<br>TxD0                | Output | Transmit data (channel 2, 1, 0): Data output pins.                                                                                       |

| interface (SCI)<br>Smart Card<br>interface | RxD2, RxD1,<br>RxD0                | Input  | Receive data (channel 2, 1, 0): Data input pins.                                                                                         |

| interrace                                  | SCK2, SCK1,<br>SCK0                | I/O    | Serial clock (channel 2, 1, 0): Clock I/O pins.                                                                                          |

| A/D converter                              | AN3 to AN0                         | Input  | Analog 3 to 0: Analog input pins.                                                                                                        |

|                                            | ADTRG                              | Input  | <b>A/D conversion external trigger input:</b> Pin for input of an external trigger to start A/D conversion.                              |

|                                            | AV <sub>CC</sub>                   | Input  | This is the power supply pin for the A/D converter.                                                                                      |

|                                            | AV <sub>SS</sub>                   | Input  | This is the ground pin for the A/D converter.                                                                                            |

|                                            | V <sub>ref</sub>                   | Input  | This is the reference voltage input pin for the A/D converter.                                                                           |

| I/O ports                                  | P1 <sub>7</sub> to P1 <sub>0</sub> | I/O    | <b>Port 1:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port 1 data direction register (P1DDR). |

|                                            | P2 <sub>7</sub> to P2 <sub>0</sub> | I/O    | <b>Port 2:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port 2 data direction register (P2DDR). |

|                                            | P3 <sub>5</sub> to P3 <sub>0</sub> | I/O    | <b>Port 3:</b> A 6-bit I/O port. Input or output can be designated for each bit by means of the port 3 data direction register (P3DDR).  |

|                                            | P4 <sub>3</sub> to P4 <sub>0</sub> | Input  | Port 4: A 4-bit input port.                                                                                                              |

|                                            | P5 <sub>3</sub> to P5 <sub>0</sub> | I/O    | <b>Port 5:</b> A 4-bit I/O port. Input or output can be designated for each bit by means of the port 5 data direction register (P5DDR).  |

|                                            | PA <sub>3</sub> to PA <sub>0</sub> | I/O    | <b>Port A:</b> A 4-bit I/O port. Input or output can be designated for each bit by means of the port A data direction register (PADDR).  |

|                                            | PB <sub>7</sub> to PB <sub>0</sub> | I/O    | <b>Port B:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port B data direction register (PBDDR). |

|                                            | PC <sub>7</sub> to PC <sub>0</sub> | I/O    | <b>Port C:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port C data direction register (PCDDR). |

**Table 1.3 Pin Functions (cont)**

| Type             | Symbol                               | I/O | Name and Function                                                                                                                        |

|------------------|--------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| I/O ports (cont) | ) PD <sub>7</sub> to PD <sub>0</sub> | I/O | <b>Port D:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port D data direction register (PDDDR). |

|                  | PE <sub>7</sub> to PE <sub>0</sub>   | I/O | <b>Port E:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port E data direction register (PEDDR). |

|                  | PF <sub>7</sub> to PF <sub>0</sub>   | I/O | <b>Port F:</b> An 8-bit I/O port. Input or output can be designated for each bit by means of the port F data direction register (PFDDR). |

|                  | PG <sub>4</sub> to PG <sub>0</sub>   | I/O | <b>Port G:</b> A 5-bit I/O port. Input or output can be designated for each bit by means of the port G data direction register (PGDDR).  |

# 1.3 Block Diagram

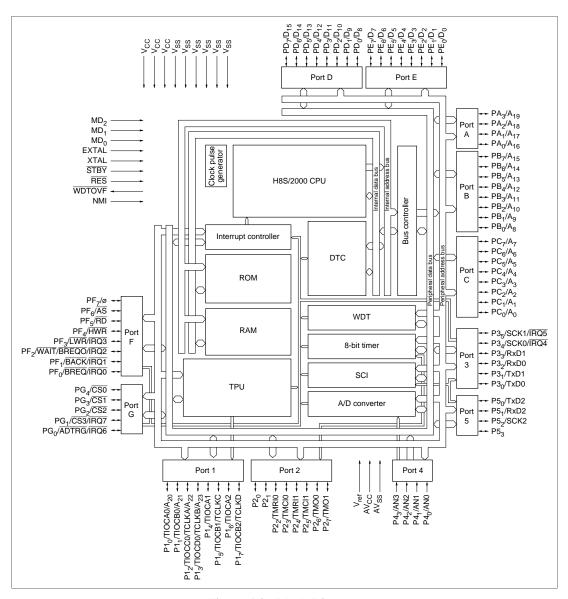

Figure 1.2 shows the block diagram.

Figure 1.2 Block Diagram

10

# Section 2 CPU

#### 2.1 Features

The H8S/2000 CPU is a high-speed central processing unit with an internal 32-bit architecture, and is upward compatible with the H8/300 and H8/300H CPUs.

The H8S/2000 CPU has sixteen 16-bit general registers, can address a 16-Mbyte (architecturally 4-Gbyte) linear access space, and is ideal for realtime control.

The features are as follows:

- Upward-compatible with H8/300 and H8/300H CPUs

- Can execute H8/300 and H8/300H object programs

- · General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- Sixty-five basic instructions

- 8/16/32-bit arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct (Rn)

- Register indirect (@ERn)

- Register indirect with displacement (@(d:16,ERn) or @(d:32,ERn))

- Register indirect with post-increment or pre-decrement (@ERn+ or @-ERn)

- Absolute address (@aa:8, @aa:16, @aa:24, or @aa:32)

- Immediate (#xx:8, #xx:16, or #xx:32)

- Program-counter relative (@(d:8,PC) or @(d:16,PC))

- Memory indirect (@@aa:8)

- 16-Mbyte access space

- Program: 16 Mbytes

- Data: 16 Mbytes (architecturally 4 Gbytes)

- High-speed operation

- All frequently-used instructions execute in one or two states

- Maximum clock frequency: 20 MHz

8/16-32-bit register-register add/subtract: 50 ns

8 × 8-bit register-register multiply: 600 ns

- 16/8-bit register-register divide: 600 ns

16 × 16-bit register-register multiply: 1000 ns

32/16-bit register-register divide: 1000 ns

- Two CPU operating modes

- Normal mode/advanced mode

- Low-power state

- Transition to power-down state by SLEEP instruction

- CPU clock speed selectable

#### Differences between the H8S/2600 CPU and the H8S/2000 CPU

- Register configuration

- The MAC register is supported only by the H8S/2600 CPU.

- Basic instructions

- The MAC, CLRMAC, LDMAC, and STMAC instructions are supported only by the H8S/2600 CPU.

- Number of states required for execution

- The number of states required for execution of the MULXU and MULXS instructions

- · Other differences

- In addition, there may be differences in address spaces, EXR register functions, power-down states, and so on. For details, refer to the relevant microcontroller hardware manual.

#### Differences from H8/300 CPU

In comparison with the H8/300 CPU, the H8S/2000 CPU has the following enhancements.

- More general registers and control registers

- Eight 16-bit registers and one 8-bit control registers added

- Expanded address space

- Normal mode supports the same 64-kbyte address space as the H8/300 CPU

- Advanced mode supports a maximum 16-Mbyte address space

- Enhanced addressing

- For effective use of the 16-Mbyte address space

- Enhanced instructions

- Addressing modes of bit-manipulation instructions enhanced

- Signed multiply and divide instructions added

- Two-bit shift instructions added

- Instructions for saving and restoring multiple registers added

- Test-and-set instruction added

- · Higher speed

— Basic instructions execute twice as fast

# Differences from H8/300H CPU

In comparison with the H8/300H CPU, the H8S/2000 CPU has the following enhancements.

- Additional control register

- One 8-bit control registers added

- Enhanced instructions

- Addressing modes of bit-manipulation instructions enhanced

- Two-bit shift instructions added

- Instructions for saving and restoring multiple registers added

- Test-and-set instruction added

- Higher speed

- Basic instructions execute twice as fast

# 2.2 Register Configuration

The H8S/2000 CPU has general registers and control registers.

The eight 32-bit general registers all have identical functions and can be used as either address registers or data registers. The control registers are the 24-bit program counter (PC), 8-bit extend register (EXR), and 8-bit condition code register (CCR).

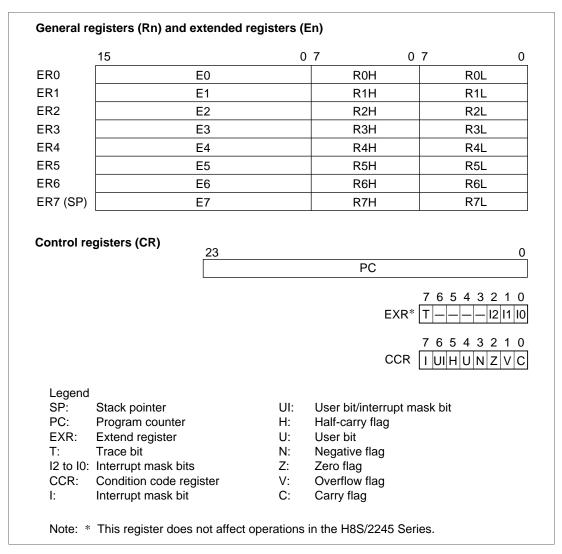

Figure 2.1 CPU Internal Register Configuration

#### 2.2.1 General Registers

The CPU has eight 32-bit general registers. These general registers are all functionally alike and can be used as either address registers or data registers.

When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register.

When the general registers are used as 32-bit registers or address registers, they are designated by the letters ER (ER0 to ER7).

The ER registers divide into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

The R registers divide into 8-bit general registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum sixteen 8-bit registers.

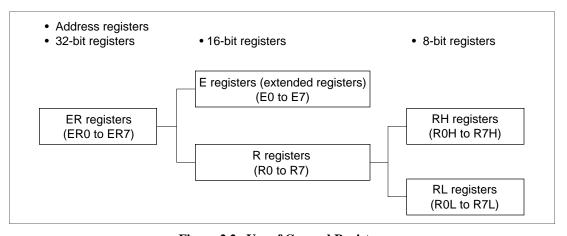

The figure below illustrates the usage of the general registers. The usage of each register can be selected independently.

Figure 2.2 Use of General Registers

# 2.2.2 Control Registers

The control registers are the 24-bit program counter (PC), 8-bit extend register (EXR), and 8-bit condition code register (CCR).

**Program Counter (PC):** This 24-bit counter indicates the address of the next instruction the CPU will execute. The length of all CPU instructions is 2 bytes (one word) or a multiple of 2 bytes, so

the least significant PC bit is ignored. When an instruction is fetched, the least significant PC bit is regarded as 0.

Extend Register (EXR): This 8-bit register does not affect operations in the H8S/2245 Series.

• Bit 7—Trace Bit (T)

This bit is reserved. It does not affect operations in the H8S/2245 Series.

- Bits 6 to 3—Reserved

- Bits 2 to 0—Interrupt Mask Bits (I2 to I0)

These bits are reserved. They do not affect operations in the H8S/2245 Series.

Condition Code Register (CCR): This 8-bit register contains internal CPU status information, including the interrupt mask bit (I), and the half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags.

• Bit 7—Interrupt Mask Bit (I)

Masks interrupts other than NMI when set to 1. NMI is accepted regardless of the I bit setting. The I bit is set to 1 at the start of an exception-handling sequence. See section 2.9, Interrupts for details.

Bit 6—User Bit or Interrupt Mask Bit (UI)

Can be written or read by software using the LDC, STC, ANDC, ORC, and XORC instructions. This bit can also be used as an interrupt mask bit. See section 2.9, Interrupts, for details.

• Bit 5—Half-Carry Flag (H)

When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and cleared to 0 otherwise. When the ADD.W, SUB.W, CMP.W, or NEG.W instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 11, and cleared to 0 otherwise. When the ADD.L, SUB.L, CMP.L, or NEG.L instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 27, and cleared to 0 otherwise.

• Bit 4—User Bit (U)

Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.

• Bit 3—Negative Flag (N)

Stores the value of the most significant bit (sign bit) of data.

• Bit 2—Zero Flag (Z)

Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.

• Bit 1—Overflow Flag (V)

Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

• • Bit 0—Carry Flag (C)

Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

- Add instructions, to indicate a carry

- Subtract instructions, to indicate a borrow

- Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit-manipulation instructions.

# 2.3 Data Formats

The CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data.

Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data.

The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

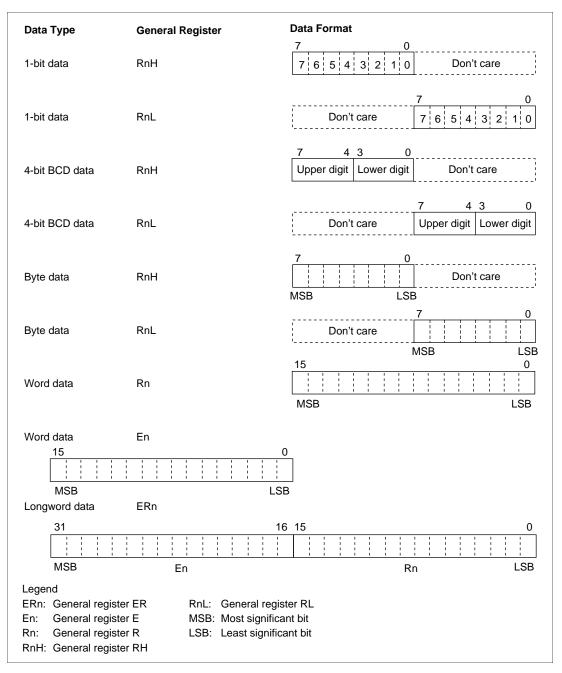

Figure 2.3 General Register Data Formats

**Figure 2.4 Memory Data Formats**

# 2.4 Addressing Modes

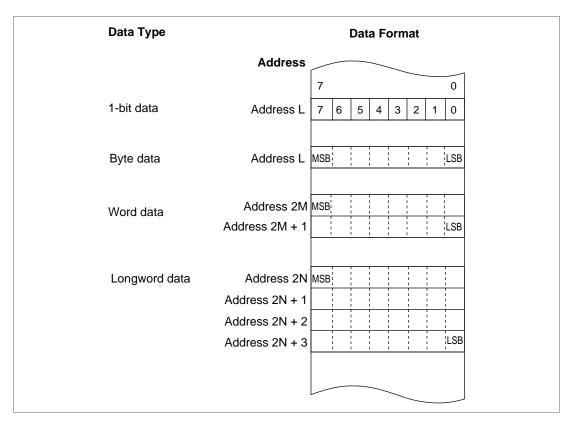

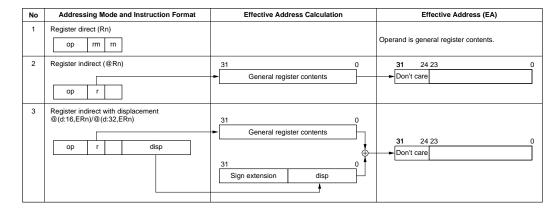

The H8S/2000 CPU supports eight addressing modes (table 2.1).

**Table 2.1 Addressing Modes**

| No. | Addressing Mode                       | Symbol                     |

|-----|---------------------------------------|----------------------------|

| 1   | Register direct                       | Rn                         |

| 2   | Register indirect                     | @ERn                       |

| 3   | Register indirect with displacement   | @(d:16,ERn)/@(d:32,ERn)    |

| 4   | Register indirect with post-increment | @ERn+                      |

|     | Register indirect with pre-decrement  | @-ERn                      |

| 5   | Absolute address                      | @aa:8/@aa:16/@aa:24/@aa:32 |

| 6   | Immediate                             | #xx:8/#xx:16/#xx:32        |

| 7   | Program-counter relative              | @(d:8,PC)/@(d:16,PC)       |

| 8   | Memory indirect                       | @@aa:8                     |

# 2.4.1 Effective Address (EA) Calculation

In normal mode, the upper 8 bits of the effective address are ignored in order to generate a 16-bit effective address.

# 2.5 Instruction Set

The H8S/2000 CPU has 65 types of instructions.

#### 2.5.1 Features

- Upward-compatible at object level with H8/300H and H8/300 CPUs.

- General register architecture

- 8/16/32-bit transfer instructions and arithmetic and logic instructions

- Byte (B), word (W), and longword (L) formats for transfer instructions and basic arithmetic and logic instructions

- Unsigned and signed multiply and divide instructions

- Powerful bit-manipulation instructions

- Instructions for saving and restoring multiple registers

# 2.5.2 Assembler Format

The ADD instruction format is shown below as an example.

# 2.5.3 Instruction Set Tables

**Table 2.2 Data Transfer Instructions**

|     | Mnemonic                |   |     | Addı |      | ing<br>.eng |             |     |         | ction  | 1 |                                 |   | Con | ditio | on C | ode |   | No<br>Sta | o. of<br>tes <sup>* 1</sup> |

|-----|-------------------------|---|-----|------|------|-------------|-------------|-----|---------|--------|---|---------------------------------|---|-----|-------|------|-----|---|-----------|-----------------------------|

|     |                         |   | *x# | Rn   | @ERn | @(d,ERn)    | @-ERn/@ERn+ | @aa | @(d,PC) | @ @ aa | I | Operation                       | ı | Н   | N     | z    | ٧   | С | Normal    | Advanced                    |

| MOV | MOV.B #xx:8,Rd          | В | 2   |      |      |             |             |     |         |        |   | #xx:8 → Rd8                     | _ | _   | Δ     | Δ    | 0   |   |           | 1                           |

|     | MOV.B Rs,Rd             | В |     | 2    |      |             |             |     |         |        |   | Rs8→Rd8                         | _ | _   | Δ     | Δ    | 0   | _ |           | 1                           |

|     | MOV.B @ERs,Rd           | В |     |      | 2    |             |             |     |         |        |   | @ERs→Rd8                        | _ | _   | Δ     | Δ    | 0   | _ | :         | 2                           |

|     | MOV.B<br>@(d:16,ERs),Rd | В |     |      |      | 4           |             |     |         |        |   | @(d:16,ERs) →<br>Rd8            | _ | _   | Δ     | Δ    | 0   | _ | ;         | 3                           |

|     | MOV.B<br>@(d:32,ERs),Rd | В |     |      |      | 8           |             |     |         |        |   | @(d:32,ERs)→<br>Rd8             | _ | _   | Δ     | Δ    | 0   | _ |           | 5                           |

|     | MOV.B @ERs+,Rd          | В |     |      |      |             | 2           |     |         |        |   | @ERs→Rd8,<br>ERs32+1 →<br>ERs32 |   | _   | Δ     | Δ    | 0   | _ | ;         | 3                           |

|     | MOV.B @aa:8,Rd          | В |     |      |      |             |             | 2   |         |        |   | @aa:8 →Rd8                      | _ | _   | Δ     | Δ    | 0   | _ | 2         |                             |

|     | MOV.B @aa:16,Rd         | В |     |      |      |             |             | 4   |         |        |   | @aa:16 → Rd8                    | _ | _   | Δ     | Δ    | 0   | _ | ;         | 3                           |

|     | MOV.B @aa:32,Rd         | В |     |      |      |             |             | 6   |         |        |   | @aa:32 → Rd8                    | _ | _   | Δ     | Δ    | 0   | _ | 4         |                             |

|     | MOV.B Rs,@ERd           | В |     |      | 2    |             |             |     |         |        |   | Rs8→@ERd                        | _ | _   | Δ     | Δ    | 0   | _ | 2         |                             |

|     | MOV.B<br>Rs,@(d:16,ERd) | В |     |      |      | 4           |             |     |         |        |   | Rd8→@(d:16,<br>ERd)             | _ | _   | Δ     | Δ    | 0   | _ | 3         |                             |

|     | MOV.B<br>Rs,@(d:32,ERd) | В |     |      |      | 8           |             |     |         |        |   | Rd8→@(d:32,<br>ERd)             | _ | _   | Δ     | Δ    | 0   | _ |           | 5                           |

|     | MOV.B Rs,@-ERd          | В |     |      |      |             | 2           |     |         |        |   | Erd32–<br>1→ERd32,<br>Rs8→@ERd  |   |     | Δ     | Δ    | 0   | _ | ;         | 3                           |

|     | MOV.B Rs,@aa:8          | В |     |      |      |             |             | 2   |         |        |   | Rs8→@aa:8                       | _ | _   | Δ     | Δ    | 0   | _ | :         | 2                           |

|     | MOV.B Rs,@aa:16         | В |     |      |      |             |             | 4   |         |        |   | Rs8→@aa:16                      | _ | _   | Δ     | Δ    | 0   | _ | ;         | 3                           |

|     | MOV.B Rs,@aa:32         | В |     |      |      |             |             | 6   |         |        |   | Rs8→@aa:32                      | _ | _   | Δ     | Δ    | 0   | _ |           | 4                           |

|     | MOV.W #xx:16,Rd         | W | 4   |      |      |             |             |     |         |        |   | #xx:16 →Rd16                    | _ | _   | Δ     | Δ    | 0   | _ | :         | 2                           |

|     | MOV.W Rs,Rd             | W |     | 2    |      |             |             |     |         |        |   | Rs16→Rd16                       | _ | _   | Δ     | Δ    | 0   | _ |           | 1                           |

|     | MOV.W @ERs,Rd           | W |     |      | 2    |             |             |     |         |        |   | @ERs→Rd16                       | _ | _   | Δ     | Δ    | 0   | _ | :         | 2                           |

|     | MOV.W<br>@(d:16,ERs),Rd | W |     |      |      | 4           |             |     |         |        |   | @(d:16,ERs)→<br>Rd16            | _ | _   | Δ     | Δ    | 0   | _ | 3         |                             |

|     | MOV.W<br>@(d:32,ERs),Rd | W |     |      |      | 8           |             |     |         |        |   | @(d:32,ERs)→<br>Rd16            | _ | _   | Δ     | Δ    | 0   | _ | 5         |                             |

|     | MOV.W @ERs+,Rd          | W |     |      |      |             | 2           |     |         |        |   | ERs→Rd16,ERs<br>32+2→@ERd32     | _ | _   | Δ     | Δ    | 0   | _ | 3         |                             |

|     | MOV.W @aa:16,Rd         | W |     |      |      |             |             | 4   |         |        |   | @aa:16 →Rd16                    |   | _   | Δ     | Δ    | 0   | _ |           | 3                           |

|     | MOV.W @aa:32,Rd         | W |     |      |      |             |             | 6   |         |        |   | @aa:32 → Rd16                   | _ | _   | Δ     | Δ    | 0   | _ | 4         |                             |

|     | MOV.W Rs,@ERd           | W |     |      | 2    |             |             |     |         |        |   | Rs16→@ERd                       | _ | _   | Δ     | Δ    | 0   | _ | :         | 2                           |

|                          |   |     | Add |      | ing l<br>eng | th (E       |     |         | ction  | 1 |                                                  |   | Cor | No. of States*1 |   |   |   |        |          |

|--------------------------|---|-----|-----|------|--------------|-------------|-----|---------|--------|---|--------------------------------------------------|---|-----|-----------------|---|---|---|--------|----------|

| Mnemonic                 |   | #xx | Rn  | @ERn | @(d,ERn)     | @-ERn/@ERn+ | @аа | @(d,PC) | @ @ aa | 1 | Operation                                        | ı | Н   | N               | z | v | C | Normal | Advanced |

| MOV.W<br>Rs,@(d:16,ERd)  | W |     |     |      | 4            |             |     |         |        |   | Rs16→@(d:16,<br>ERd)                             | _ | _   | Δ               | Δ | 0 | _ |        | 3        |

| MOV.W<br>Rs,@(d:32,ERd)  | W |     |     |      | 8            |             |     |         |        |   | Rs16→@(d:32,<br>ERd)                             | _ | _   | Δ               | Δ | 0 | _ |        | 5        |

| MOV.W Rs,<br>@-ERd       | W |     |     |      |              | 2           |     |         |        |   | ERd32–<br>2→ERd32,<br>Rs16→@ERd                  | _ |     | Δ               | Δ | 0 |   |        | 3        |

| MOV.W Rs,@aa:16          | W |     |     |      |              |             | 4   |         |        |   | Rs16→@aa:16                                      | _ | _   | Δ               | Δ | 0 | _ |        | 3        |

| MOV.W Rs,@aa:32          | W |     |     |      |              |             | 6   |         |        |   | Rs16→@aa:32                                      | _ | _   | Δ               | Δ | 0 | _ |        | 4        |

| MOV.L #xx:32,Rd          | L | 6   |     |      |              |             |     |         |        |   | #xx:32 →Rd32                                     | _ | _   | Δ               | Δ | 0 | _ |        | 3        |

| MOV.L ERs,ERd            | L |     | 2   |      |              |             |     |         |        |   | ERs32→ERd32                                      | _ | _   | Δ               | Δ | 0 |   |        | 1        |

| MOV.L @ERs,ERd           | L |     |     | 4    |              |             |     |         |        |   | @ERs→ERd32                                       | _ | _   | Δ               | Δ | 0 | _ |        | 4        |

| MOV.L<br>@(d:16,ERs),ERd | L |     |     |      | 6            |             |     |         |        |   | @(d:16,ERs) →<br>ERd32                           | _ | _   | Δ               | Δ | 0 | - |        | 5        |

| MOV.L<br>@(d:32,ERs),ERd | L |     |     |      | 10           |             |     |         |        |   | @(d:32,ERs) →<br>ERd32                           | _ |     | Δ               | Δ | 0 |   |        | 7        |

| MOV.L<br>@ERs+,ERd       | L |     |     |      |              | 4           |     |         |        |   | <pre>@ERs→ERd32,<br/>ERs32 +4 →<br/>@ERs32</pre> |   |     | Δ               | Δ | 0 |   |        | 5        |

| MOV.L<br>@aa:16,ERd      | L |     |     |      |              |             | 6   |         |        |   | @aa:16 →ERd32                                    | _ | _   | Δ               | Δ | 0 |   |        | 5        |

| MOV.L<br>@aa:32,ERd      | L |     |     |      |              |             | 8   |         |        |   | @aa:32 →ERd32                                    | _ | _   | Δ               | Δ | 0 | _ |        | 6        |

|            |                          |    |      | Add  |      | ing l<br>eng |             |      |         | tion   | 1  |                                                                       |   | Cor | No. of<br>States <sup>*1</sup> |   |   |   |            |          |

|------------|--------------------------|----|------|------|------|--------------|-------------|------|---------|--------|----|-----------------------------------------------------------------------|---|-----|--------------------------------|---|---|---|------------|----------|

|            | Mnemonic                 |    | *x#  | Rn   | @ERn | @(d,ERn)     | @-ERn/@ERn+ | @aa  | @(d,PC) | @ @ aa | I  | Operation                                                             | ı | н   | N                              | Z | v | С | Normal     | Advanced |

|            | MOV.L ERs,@ERd           | L  |      |      | 4    |              |             |      |         |        |    | ERs32→@ERd                                                            | _ | _   | Δ                              | Δ | 0 | _ |            | 4        |

|            | MOV.L<br>ERs,@(d:16,ERd) | L  |      |      |      | 6            |             |      |         |        |    | ERs32→@(d:16,<br>ERd)                                                 | _ | _   | Δ                              | Δ | 0 |   |            | 5        |

|            | MOV.L<br>ERs,@(d:32,ERd) | L  |      |      |      | 10           |             |      |         |        |    | ERs32→ @ (d:32,<br>ERd)                                               | _ | _   | Δ                              | Δ | 0 | _ | -          | 7        |

|            | MOV.L ERs,<br>@-ERd      | L  |      |      |      |              | 4           |      |         |        |    | ERd32–4→<br>ERd32,ERs32→<br>@ERd                                      | _ |     | Δ                              | Δ | 0 | _ | ;          | 5        |

|            | MOV.L<br>ERs,@aa:16      | L  |      |      |      |              |             | 6    |         |        |    | ERs32→ @aa:16                                                         | _ | _   | Δ                              | Δ | 0 | _ | 5          |          |

|            | MOV.L<br>ERs,@aa:32      | L  |      |      |      |              |             | 8    |         |        |    | ERs32→ @aa:32                                                         | _ | _   | Δ                              | Δ | 0 | _ | (          | 6        |

| POP        | POP.W Rn                 | W  |      |      |      |              |             |      |         |        | 2  | @SP→Rn16,SP<br>+2→SP                                                  | _ | _   | Δ                              | Δ | 0 | _ | ;          | 3        |

|            | POP.L ERn                | L  |      |      |      |              |             |      |         |        | 4  | @SP→ERn32,<br>SP+4→SP                                                 | _ | _   | Δ                              | Δ | 0 | _ |            | 5        |

| PUSH       | PUSH.W Rn                | W  |      |      |      |              |             |      |         |        | 2  | SP–2→SP,<br>Rn16→@SP                                                  | _ | _   | Δ                              | Δ | 0 | _ | ;          | 3        |

|            | PUSH.L ERn               | L  |      |      |      |              |             |      |         |        | 4  | SP–4→SP,<br>ERn32→@SP                                                 | _ | _   | Δ                              | Δ | 0 | _ | ;          | 5        |

| LDM        | LDM @SP+,<br>(ERm–ERn)   | L  |      |      |      |              |             |      |         |        | 4  | (@SP →ERn32,<br>SP+4→SP)<br>Repeated for<br>each register<br>restored | _ | _   | _                              | _ | _ | _ | 7/9/11 [1] |          |

| STM        | STM (ERm-<br>ERn),@-SP   | L  |      |      |      |              |             |      |         |        | 4  | (SP–4→SP,<br>ERn32→@SP)<br>Repeated for<br>each register<br>saved     | _ |     | _                              | _ | _ | _ | 7/9/       | 11 [1]   |

| MOV<br>FPE | MOVFPE<br>@aa:16,Rd      | Ca | nnot | be u | ısed | in th        | ie H8       | 3S/2 | 245     | Serie  | es |                                                                       |   |     |                                |   |   |   | [2]        |          |

| MOV<br>TPE | MOVTPE<br>Rs,@aa:16      |    |      |      |      |              |             |      |         |        |    |                                                                       |   |     |                                |   |   |   | [2         | 2]       |

**Table 2.3** Arithmetic Instructions

|      |                  |              | ,    | Addı |       |          | Mod<br>th (E |      |         | ctior  | 1 |                             |   | Cor | nditio | on C | ode |   |        | o. of<br>ites <sup>* 1</sup> |

|------|------------------|--------------|------|------|-------|----------|--------------|------|---------|--------|---|-----------------------------|---|-----|--------|------|-----|---|--------|------------------------------|

|      | Mnemonic         | Operand Size | #xx# | Rn   | @ ERn | @(d,ERn) | @-ERn/@ERn+  | @ аа | @(d,PC) | @ @ aa | 1 | Operation                   | ı | н   | N      | Z    | v   | ၀ | Normal | Advanced                     |

| ADD  | ADD.B #xx:8,Rd   | В            | 2    |      |       |          |              |      |         |        |   | Rd8+#xx:8→Rd<br>8           |   | Δ   | Δ      | Δ    | Δ   | Δ |        | 1                            |

|      | ADD.B Rs,Rd      | В            |      | 2    |       |          |              |      |         |        |   | Rd8+Rs8→Rd8                 | _ | Δ   | Δ      | Δ    | Δ   | Δ |        | 1                            |

|      | ADD.W #xx:16,Rd  | W            | 4    |      |       |          |              |      |         |        |   | Rd16+#xx:16→<br>Rd16        | _ | [3] | Δ      | Δ    | Δ   | Δ |        | 2                            |

|      | ADD.W Rs,Rd      | W            |      | 2    |       |          |              |      |         |        |   | Rd16+Rs16→<br>Rd16          |   | [3] | Δ      | Δ    | Δ   | Δ |        | 1                            |

|      | ADD.L #xx:32,ERd | L            | 6    |      |       |          |              |      |         |        |   | ERd32+#xx:32<br>→ERd32      | _ | [4] | Δ      | Δ    | Δ   | Δ |        | 3                            |

|      | ADD.L ERs,ERd    | L            |      | 2    |       |          |              |      |         |        |   | ERd32+ERs32<br>→ERd32       | _ | [4] | Δ      | Δ    | Δ   | Δ |        | 1                            |

| ADDX | ADDX #xx:8,Rd    | В            | 2    |      |       |          |              |      |         |        |   | Rd8+#xx:8+C → Rd8           | _ | Δ   | Δ      | [5]  | Δ   | Δ |        | 1                            |

|      | ADDX Rs,Rd       | В            |      | 2    |       |          |              |      |         |        |   | $Rd8+Rs8+C \rightarrow Rd8$ |   | Δ   | Δ      | [5]  | Δ   | Δ |        | 1                            |

| ADDS | ADDS #1,ERd      | L            |      | 2    |       |          |              |      |         |        |   | ERd32+1→<br>ERd32           | _ | _   | _      | _    | _   | _ |        | 1                            |

|      | ADDS #2,ERd      | L            |      | 2    |       |          |              |      |         |        |   | ERd32+2→<br>ERd32           | _ | _   | _      | _    | _   | _ |        | 1                            |

|      | ADDS #4,ERd      | L            |      | 2    |       |          |              |      |         |        |   | ERd32+4→<br>ERd32           | _ | _   | _      | _    | _   | _ |        | 1                            |

| INC  | INC.B Rd         | В            |      | 2    |       |          |              |      |         |        |   | Rd8+1 → Rd8                 | _ | _   | Δ      | Δ    | Δ   | _ |        | 1                            |

|      | INC.W #1,Rd      | W            |      | 2    |       |          |              |      |         |        |   | Rd16+1 →Rd16                | _ | _   | Δ      | Δ    | Δ   | _ |        | 1                            |

|      | INC.W #2,Rd      | W            |      | 2    |       |          |              |      |         |        |   | Rd16+2→Rd16                 | _ | _   | Δ      | Δ    | Δ   | _ |        | 1                            |

|      | INC.L #1,ERd     | L            |      | 2    |       |          |              |      |         |        |   | ERd32+1→<br>ERd32           | _ | _   | Δ      | Δ    | Δ   | _ |        | 1                            |

|      | INC.L #2,ERd     | L            |      | 2    |       |          |              |      |         |        |   | ERd32+2→<br>ERd32           | _ | _   | Δ      | Δ    | Δ   | _ |        | 1                            |

| DAA  | DAA Rd           | В            |      | 2    |       |          |              |      |         |        |   | Rd8 decimal adjust → Rd8    | _ | *   | Δ      | Δ    | *   | Δ |        | 1                            |

| SUB  | SUB.B Rs,Rd      | В            |      | 2    |       |          |              |      |         |        |   | Rd8-Rs8→Rd8                 | _ | Δ   | Δ      | Δ    | Δ   | Δ |        | 1                            |

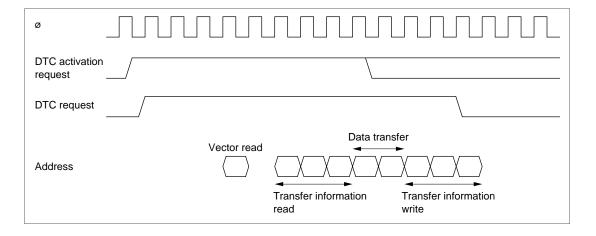

|      | SUB.W #xx:16,Rd  | W            | 4    |      |       |          |              |      |         |        |   | Rd16–<br>#xx:16 →Rd16       |   | [3] | Δ      | Δ    | Δ   | Δ |        | 2                            |