# HY5U2A6C(L)F

#### DESCRIPTION

The Hynix Low Power SDRAM is suited for non-PC application which use the batteries such as PDAs, 2.5G and 3G cellular phones with internet access and multimedia capabilities, mini-notebook, handheld PCs.

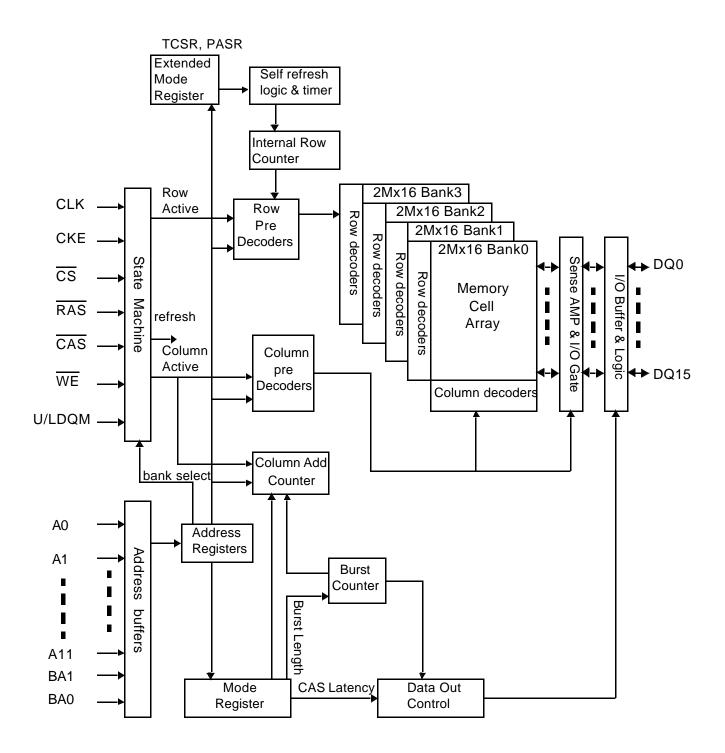

The Hynix HY5U2A6CF is a 134,217,728bit CMOS Synchronous Dynamic Random Access Memory. It is organized as 4banks of 2,097,152x16.

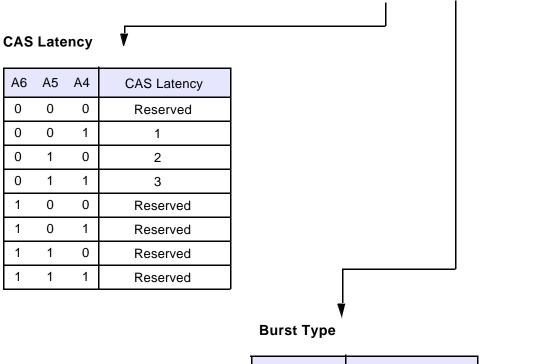

The Low Power SDRAM provides for programmable options including CAS latency of 1, 2, or 3, READ or WRITE burst length of 1, 2, 4, 8, or full page, and the burst count sequence(sequential or interleave). And the Low Power SDRAM also provides for special programmable options including Partial Array Self Refresh of a quarter bank, a half bank, 1bank, 2banks, or all banks, Temperature Compensated Self Refresh of 15, 45, 70, or 85 degrees C. A burst of Read or Write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst Read or Write command on any cycle(This pipelined design is not restricted by a 2N rule).

Deep Power Down Mode is a additional operating mode for Low Power SDRAM. This mode can achieve maximum power reduction by removing power to the memory array within each SDRAM. By using this feature, the system can cut off alomost all DRAM power without adding the cost of a power switch and giving up mother-board power-line layout flexibility.

### **FEATURES**

- Standard SDRAM Protocol

- Internal 4bank operation

- Voltage: VDD = 2.5V, VDDQ = 2.5V

- LVTTL compatible I/O Interface

- Low Voltage interface to reduce I/O power

- Special Low Power Features (JEDEC standard)

- PASR(Partial Array Self Refresh)

- TCSR(Temperature Compensated Self Refresh)

- Deep Power Down Mode

- CAS latency of 1, 2, or 3

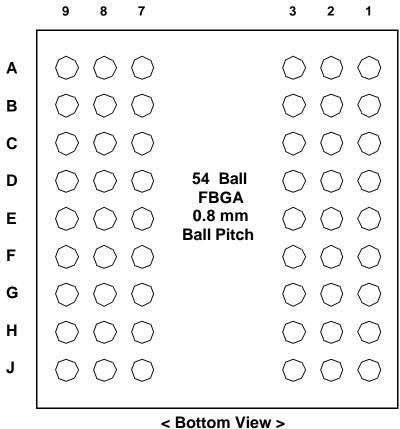

- Packages: 54ball, 0.8mm pitch FBGA / 54pin, TSOP

### 128M SDRAM ODERING INFORMATION

| Part Number         | Clock<br>Frequency | CAS<br>Latency | Organization      | Interface | Package       |

|---------------------|--------------------|----------------|-------------------|-----------|---------------|

| HY57U2A1620HC(L)T-H | 133MHz             | 3              | 4banks x 2Mb x 16 | LVTTL     | 54pin TSOP-II |

| HY57U2A1620HC(L)T-P | 100MHz             | 2              | 4banks x 2Mb x 16 | LVTTL     | 54pin TSOP-II |

| HY57U2A1620HC(L)T-S | 100MHz             | 3              | 4banks x 2Mb x 16 | LVTTL     | 54pin TSOP-II |

| HY5U2A6C(L)F-H      | 133MHz             | 3              | 4banks x 2Mb x 16 | LVTTL     | 54ball FBGA   |

| HY5U2A6C(L)F-P      | 100MHz             | 2              | 4banks x 2Mb x 16 | LVTTL     | 54ball FBGA   |

| HY5U2A6C(L)F-S      | 100MHz             | 3              | 4banks x 2Mb x 16 | LVTTL     | 54ball FBGA   |

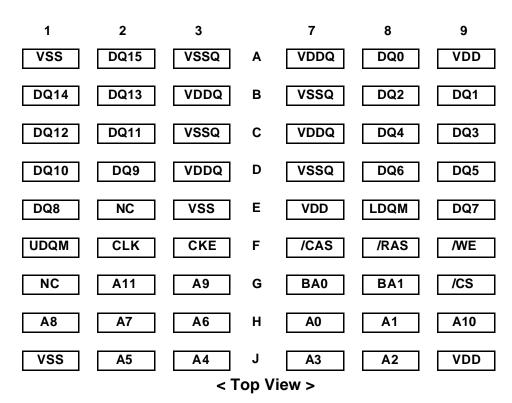

### **BALL CONFIGURATION**

#### BALL DESCRIPTION

| BALL OUT                                                                | SYMBOL          | TYPE   | DESCRIPTION                                                                                                                                      |

|-------------------------------------------------------------------------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| F2                                                                      | CLK             | INPUT  | Clock : The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLK                                           |

| F3                                                                      | CKE             | INPUT  | Clock Enable: Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refresh |

| G9                                                                      | CS              | INPUT  | Chip Select : Enables or disables all inputs except CLK, CKE, UDQM and LDQM                                                                      |

| G7,G8                                                                   | BA0, BA1        | INPUT  | Bank Address : Selects bank to be activated during RAS activity Selects bank to be read/written during CAS activity                              |

| H7, H8, J8, J7,<br>J3, J2, H3, H2,<br>H1, G3, H9, G2                    | A0 ~ A11        | INPUT  | Row Address : RA0 ~ RA11, Column Address : CA0 ~ CA8<br>Auto-precharge flag : A10                                                                |

| F8, F7, F9                                                              | RAS, CAS,<br>WE | INPUT  | Command Inputs: RAS, CAS and WE define the operation Refer function truth table for details                                                      |

| F1, E8                                                                  | UDQM,<br>LDQM   | INPUT  | Data Mask:Controls output buffers in read mode and masks input data in write mode                                                                |

| A8, B9, B8, C9,<br>C8, D9, D8, E9,<br>E1, D2, D1, C2,<br>C1, B2, B1, A2 | DQ0 ~<br>DQ15   | I/O    | Data Input/Output:Multiplexed data input/output pin                                                                                              |

| A9, E7, J9, A1,<br>E3, J1                                               | VDD/VSS         | SUPPLY | Power supply for internal circuits                                                                                                               |

| A7, B3, C7, D3,<br>A3, B7, C3, D7                                       | VDDQ/<br>VSSQ   | SUPPLY | Power supply for output buffers                                                                                                                  |

| E2, G1                                                                  | NC              | -      | No connection                                                                                                                                    |

Note. Please find HY57U2A1620 series for TSOP pin configuration & description.

### FUNCTIONAL BLOCK DIAGRAM

2Mbit x 4banks x 16 I/O Low Power Synchronous DRAM

### **BASIC FUNCTIONAL DESCRIPTION**

### **Mode Register**

| BA1 | BA0 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5     | A4   | А3 | A2  | A1     | Α0  |

|-----|-----|-----|-----|-----|----|----|----|----|--------|------|----|-----|--------|-----|

| 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | C/ | AS Lat | ency | BT | Bur | st Len | gth |

| А3 | Burst Type |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

**Burst Length**

| ۸۵ | ۸ 1   | ^^ | Burst I   | Length   |

|----|-------|----|-----------|----------|

| AZ | A2 A1 |    | A3 = 0    | A3=1     |

| 0  | 0     | 0  | 1         | 1        |

| 0  | 0     | 1  | 2         | 2        |

| 0  | 1     | 0  | 4         | 4        |

| 0  | 1     | 1  | 8         | 8        |

| 1  | 0     | 0  | Reserved  | Reserved |

| 1  | 0     | 1  | Reserved  | Reserved |

| 1  | 1     | 0  | Reserved  | Reserved |

| 1  | 1     | 1  | Full Page | Reserved |

# **BASIC FUNCTIONAL DESCRIPTION (Continued)**

# **Extended Mode Register**

PASR (Partial Array Self Refresh)

| A2 | A1 | A0 | Self Refresh Coverage                              |

|----|----|----|----------------------------------------------------|

| 0  | 0  | 0  | All Banks                                          |

| 0  | 0  | 1  | Half of Total Bank (BA1=0)                         |

| 0  | 1  | 0  | Quarter of Total Bank (BA1=BA0=0)                  |

| 0  | 1  | 1  | Reserved                                           |

| 1  | 0  | 0  | Reserved                                           |

| 1  | 0  | 1  | One Eighth of Total Bank (Row Address MSB=0)       |

| 1  | 1  | 0  | One Sixteenth of Total Bank (Row Address 2 MSBs=0) |

| 1  | 1  | 1  | Reserved                                           |

### Power Up and Initialization

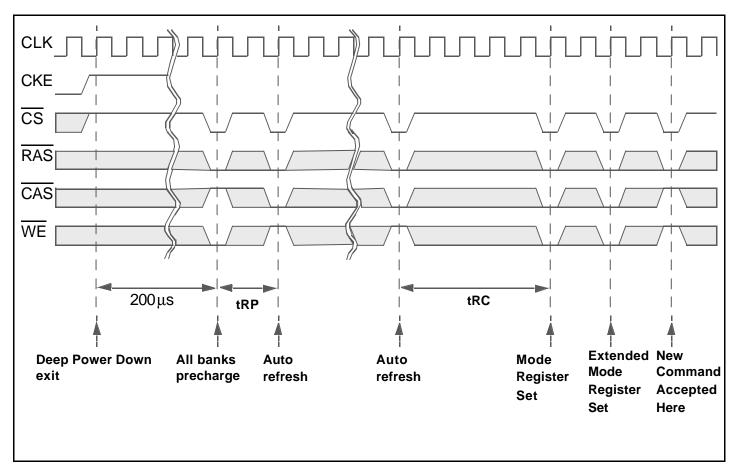

Like a Synchronous DRAM, Low Power SDRAM must be powered up and initialized in a predefined manner. Power must be applied to VDD and VDDQ(simultaneously). The clock signal must be started at the same time. After power up, an initial pause of 200 µsec is required. And a precharge all command will be issued to the LP SDRAM. Then, 8 or more Auto refresh cycles will be provided. After the Auto refresh cycles are completed, a mode register set(MRS) command will be issued to program the specific mode of operation (Cas Latency, Burst length, etc.) And a extended mode register set command will be issued to program specific mode of self refresh operation(PASR & TCSR). The following these cycles, the LP SDRAM is ready for normal opeartion.

### Programming the registers

### Mode Register

The mode register contains the specific mode of operation of the LP SDRAM. This register includes the selection of a burst length(1, 2, 4, 8, Full Page), a cas latency(1, 2, or 3), a burst type, an opearting mode to differentiate between normal mode and a special burst read and single write mode. The mode register set must be done before any activate command after the power up sequence. Any contents of the mode register be altered by re-programming the mode register through the execution of mode register set command.

### Extended Mode Register

The extended mode register contains the specific features of self refresh opeartion of the LP SDRAM. This register includes the selection of partial arrays to be refreshed(half array, quarter array, etc.), tempearture range of the device(85, 70, 45, 15) for reducing current consumption during self refresh. The extended mode register set must be done before any activate command after the power up sequence. Any contents of the mode register be altered by re-programming the mode register through the execution of extended mode register set command.

### Bank(Row) Active

The Bank Active command is used to activate a row in a specified bank of the device. This command is initiated by activating CS, RAS and deasserting CAS, WE at the positive edge of the clock. The value on the BA1 and BA0 selects the bank, and the value on the A0-A11 selects the row. This row remains active for column access until a precharge command is issued to that bank. Read and write opeartions can only be initiated on this activated bank after the minimum tRCD time is passed from the activate command.

### Read

The READ command is used to initiate the burst read of data. This command is initiated by activating  $\overline{\text{CS}}$ ,  $\overline{\text{CAS}}$ , and deasserting WE, RAS at the positive edge of the clock. BA1 and BA0 inputs select the bank, A8-A0 address inputs select the sarting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge is selected the row being accessed will be precharged at the end of the READ burst; if Auto Precharge is not selected, the row will remain active for subsequent accesses. The length of burst and the CAS latency will be determined by the values programmed during the MRS command.

### Write

The WRITE command is used to initiate the burst write of data. This command is initiated by activating  $\overline{\text{CS}}$ ,  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$  and deasserting RAS at the positive edge of the clock. BA1 and BA0 inputs select the bank, A8-A0 address inputs select the starting column location. The value on input A10 determines whether or not Auto Precharge is used. If Auto Precharge is selected the row being accessed will be precharged at the end of the WRITE burst; if Auto Precharge is not selected, the row will remain active for subsequent accesses.

### Precharge

The Precharge command is used to close the open row in a particular bank or the open row in all banks. When the precharge command is issued with address A10, high, then all banks will be precharged, and If A10 is low, the open row in a particular bank will be precharged. The bank(s) will be available when the minimum tRP time is met after the precharge command is issued.

### Auto Precharge

The Auto Precharge command is issued to close the open row in a particular bank after READ or WRITE operation. If A10 is high when a READ or WRITE command is issued, the READ or WRITE with Auto Precharge is initiated.

### **Burst Termination**

The Burst Termination is used to terminate the burst operation. This function can be accomplished by asserting a Burst Stop command or a Precharge command during a burst READ or WRITE operation. The Precharge command interrupts a burst cycle and close the active bank, and the Burst Stop command terminates the existing burst operation leave the bank open.

### Data Mask

The Data Mask comamnd is used to mask READ or WRITE data. During a READ operation, When this command is issued, data ouputs are disabled and become high impedance after two clock delay. During a WRITE operation, When this command is issued, data inputs can't be written with no clock delay.

### Clock Suspend

The Clock Suspend command is used to suspend the internal clock of DRAM. During normal access mode, CKE is keeping High. When CKE is low, it freezes the internal clock and extends data Read and Write operations.

### Power Down

The Power Down command is used to reduce standby current. Before this command is issued, all banks must be precharged and tRP must be passed after a precharge command. Once the Power Down command is initiated by keeping CKE low, all of the input buffer except CKE are gated off.

### Auto Refresh

The Auto Refresh command is used during normal operation and is similar to CBR refresh in Coventional DRAMs. This command must be issued each time a refresh is required. When an Auto Refresh command is issued, the address bits is "Don' t care", because the specific address bits is generated by internal refresh address counter.

### Self Refresh

The Self Refresh command is used to retain cell data in the Low Power SDRAM. In the Self Refresh mode, the Low Power SDRAM operates refresh cycle asynchronously. The Self Refresh command is initiated like an Auto Refresh command except CKE is disabled(Low). The Low Power SDRAM can accomplish an special Self Refresh operation by the specific modes(TCSR, PASR) programmed in extended mode registers. The Low Power SDRAM can control the refresh rate by the temperature value of TCSR (Temperature Compensated Self Refresh) and select the memory array to be refreshed by the value of PASR(Partial Array Self Refresh). The Low Power SDRAM can reduce the self refresh current(IDD6) by using these two modes.

### Deep Power Down

The Deep Power Down Mode is used to achieve maximum power reduction by cutting the power of the whole memory array of the devices. For more information, see the special operation for Low Power consumption of this data sheet.

# **COMMAND TRUTH TABLE**

| Function                   | CKEn-1 | CKEn | CS | RAS | CAS | WE | DQM | ADDR           | A10/<br>AP | ВА | Note |

|----------------------------|--------|------|----|-----|-----|----|-----|----------------|------------|----|------|

| Mode Register Set          | Н      | Χ    | L  | L   | L   | L  | Χ   | Ор (           | Code       |    | 2    |

| Extended Mode Register Set | Н      | Х    | L  | L   | L   | L  | Χ   | Ор (           | Code       |    | 2    |

| No Operation               | Н      | Х    | L  | Н   | Н   | Н  | Χ   |                | Χ          |    |      |

| Device Deselect            | Н      | Х    | Н  | Х   | Х   | Х  | Χ   |                | Χ          |    |      |

| Bank Active                | Н      | Х    | L  | L   | Н   | Н  | Х   | Row<br>Address |            | V  |      |

| Read                       | Н      | Х    | L  | Н   | L   | Н  |     | Column         | L          | V  |      |

| Read with Autoprecharge    | Н      | Χ    | L  | Н   | L   | Н  | Χ   | Column         | Н          | V  |      |

| Write                      | Н      | Χ    | L  | Н   | L   | L  | Χ   | Column         | L          | V  |      |

| Write with Autoprecharge   | Н      | Χ    | L  | Н   | L   | L  | Χ   | Column         | Н          | V  |      |

| Precharge All Banks        | Н      | Χ    | L  | L   | Н   | L  | Χ   | Χ              | Н          | Х  |      |

| Precharge selected Bank    | Н      | Χ    | L  | L   | Н   | L  | Χ   | Χ              | L          | V  |      |

| Burst stop                 | Н      | Х    | L  | Н   | Н   | L  | Х   |                | Χ          |    |      |

| Data Write/Output Enable   | Н      | Х    |    | Х   |     |    | Х   |                | Χ          |    |      |

| Data Mask/Output Disable   | Н      | Х    |    | Х   |     |    | V   |                | Χ          |    |      |

| Auto Refresh               | Н      | Н    | L  | L   | L   | Н  | Χ   |                | Χ          |    |      |

| Self Refresh Entry         | Н      | L    | L  | L   | L   | Н  | Χ   |                | Χ          |    |      |

| Self Refresh Exit          | L      | Н    | Н  | Χ   | Χ   | Х  | Χ   |                | Χ          |    | 1    |

|                            |        |      | L  | Н   | Н   | Н  |     |                |            |    |      |

| Precharge Power Down       | Н      | L    | Н  | Х   | Х   | Х  | Х   |                | Χ          |    |      |

| Entry                      |        |      | L  | Н   | Н   | Н  |     |                |            |    |      |

| Precharge Power Down Exit  | L      | Н    | Н  | Χ   | Χ   | Х  | Χ   |                | Χ          |    |      |

|                            |        |      | L  | Н   | Н   | Н  |     |                |            |    |      |

| Clock Suspend Entry        | Н      | L    | Н  | Х   | Х   | Х  | Χ   |                | Χ          |    |      |

|                            |        |      | L  | V   | V   | V  |     |                |            |    |      |

| Clock Suspend Exit         | L      | Н    |    | Х   |     |    | Χ   |                | Χ          |    |      |

| Deep Power Down Entry      | Н      | L    | L  | Н   | Н   | L  | Χ   |                | Х          |    |      |

| Deep Power Down Exit       | L      | Н    |    | Х   |     |    | Χ   |                | Χ          |    |      |

Note: 1. Exiting Self Refresh occurs by asynchronously bringing CKE from low to high.

2. BA1/BA0 must be issued 0/0 in the mode register set, and 1/0 in the extended mode register set.

# CURRENT STATE TRUTH TABLE (Sheet 1 of 3)

| Current State |    |     |     |    | Comma   | nd              |                      | Action                                         | Notes |

|---------------|----|-----|-----|----|---------|-----------------|----------------------|------------------------------------------------|-------|

| Current State | CS | RAS | CAS | WE | BA0,BA1 | A11-A0          | Description          | Action                                         | Notes |

|               | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | Set the Mode Register                          | 14    |

|               | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh | Start Auto or Self Refresh                     | 5     |

|               | L  | L   | Н   | L  | BA      | Х               | Precharge            | No Operation                                   |       |

| idle          | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | Activate the specified bank and row            |       |

|               | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                                        | 4     |

|               | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | ILLEGAL                                        | 4     |

|               | L  | Н   | Н   | Н  | Χ       | Х               | No Operation         | No Operation                                   | 3     |

|               | Н  | Х   | Х   | Χ  | Х       | Х               | Device Deselect      | No Operation or Power Down                     | 3     |

|               | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | ILLEGAL                                        | 13,14 |

|               | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh | ILLEGAL                                        | 13    |

|               | L  | L   | Н   | L  | BA      | Х               | Precharge            | Precharge                                      | 7     |

|               | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | ILLEGAL                                        | 4     |

| Row<br>Active | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | Start Write : optional<br>AP(A10=H)            | 6     |

|               | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | Start Read : optional<br>AP(A10=H)             | 6     |

|               | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | No Operation                                   |       |

|               | Н  | Χ   | Χ   | Χ  | Х       | Х               | Device Deselect      | No Operation                                   |       |

|               | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | ILLEGAL                                        | 13,14 |

|               | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh | ILLEGAL                                        | 13    |

|               | L  | L   | Н   | L  | BA      | Х               | Precharge            | Termination Burst: Start the<br>Precharge      |       |

| Read          | L  | L   | Н   | Η  | BA      |                 | Bank Activate        | ILLEGAL                                        | 4     |

| . 1000        | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | Termination Burst: Start Write(optional AP)    | 8,9   |

|               | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | Termination Burst: Start<br>Read(optional AP)  | 8     |

|               | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | Continue the Burst                             |       |

|               | Н  | Χ   | Χ   | Χ  | Х       | Х               | Device Deselect      | Continue the Burst                             |       |

|               | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | ILLEGAL                                        | 13,14 |

|               | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh | ILLEGAL                                        | 13    |

|               | L  | L   | Н   | L  | BA      | Х               | Precharge            | Termination Burst: Start the<br>Precharge      | 10    |

| Write         | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | ILLEGAL                                        | 4     |

|               | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | Termination Burst: Start<br>Write(optional AP) | 8     |

|               | L  | Н   | L   | Н  | BA      |                 | Read/ReadAP          | Termination Burst: Start<br>Read(optional AP)  | 8,9   |

|               | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | Continue the Burst                             |       |

|               | Н  | Χ   | Χ   | Χ  | Х       | Х               | Device Deselect      | Continue the Burst                             |       |

# CURRENT STATE TRUTH TABLE (Sheet 2 of 3)

| 0 1011            |    |     |     |    | Comma   | ınd             |                      | A -4:                                | Nistas  |

|-------------------|----|-----|-----|----|---------|-----------------|----------------------|--------------------------------------|---------|

| Current State     | CS | RAS | CAS | WE | BA0,BA1 | A11-A0          | Description          | Action                               | Notes   |

|                   | L  | L   | L   | L  | OP (    | L<br>Code       | Mode Register Set    | ILLEGAL                              | 13,14   |

|                   | L  | L   | L   | Н  | X       | Х               | Auto or Self Refresh | ILLEGAL                              | 13      |

|                   | L  | L   | Н   | L  | ВА      | X               | Precharge            | ILLEGAL                              | 4,12    |

| Read with         | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | ILLEGAL                              | 4,12    |

| Auto              | L  | Н   | L   | L  | ВА      | Col Add.        | Write/WriteAP        | ILLEGAL                              | 12      |

| Precharge         |    |     |     |    |         | A10             |                      |                                      |         |

|                   | L  | Н   | L   | Н  | BA      | Col Add.        | Read/ReadAP          | ILLEGAL                              | 12      |

|                   |    |     |     |    |         | A10             |                      |                                      |         |

|                   | L  | Н   | Η   | Η  | Х       | Х               | No Operation         | Continue the Burst                   |         |

|                   | Н  | Χ   | Χ   | Χ  | Χ       | X               | Device Deselect      | Continue the Burst                   |         |

|                   | L  | L   | L   | L  | OP (    |                 | Mode Register Set    | ILLEGAL                              | 13,14   |

|                   | L  | L   | L   | Η  | Х       | Х               | Auto or Self Refresh | ILLEGAL                              | 13      |

|                   | L  | L   | Η   | L  | BA      | Х               | Precharge            | ILLEGAL                              | 4,12    |

| Write with        | L  | L   | Н   | Η  | BA      |                 | Bank Activate        | ILLEGAL                              | 4,12    |

| Auto              | L  | Н   | Г   | L  | BA      |                 | Write/WriteAP        | ILLEGAL                              | 12      |

| Precharge         |    |     |     |    |         | A10             |                      |                                      |         |

|                   | L  | Н   | L   | Н  | BA      |                 | Read/ReadAP          | ILLEGAL                              | 12      |

|                   |    |     |     |    |         | A10             |                      |                                      |         |

|                   | L  | Н   | Н   | Η  | Χ       | X               | No Operation         | Continue the Burst                   |         |

|                   | Н  | Х   | Χ   | Χ  | Х       | X               | Device Deselect      | Continue the Burst                   |         |

|                   | L  | L   | L   | L  | OP (    | -               | Mode Register Set    | ILLEGAL                              | 13,14   |

|                   | L  | L   | L   | Н  | Х       | X               |                      | ILLEGAL                              | 13      |

|                   | L  | L   | Н   | L  | BA      | Х               | Precharge            | No Operation: Bank(s) idle after tRP |         |

| Precharging       | L  | L   | Η   | Н  | BA      |                 | Bank Activate        | ILLEGAL                              | 4,12    |

|                   | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                              | 4,12    |

|                   | L  | Н   | L   | Н  | BA      | Col Add.        | Read/ReadAP          | ILLEGAL                              | 4,12    |

|                   |    |     |     |    |         | A10             |                      |                                      |         |

|                   | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | No Operation: Bank(s) idle after tRP |         |

|                   | Η  | Х   | Х   | Х  | Х       | Х               | Device Deselect      | No Operation: Bank(s) idle after tRP |         |

|                   | L  | L   | L   | L  | OP (    | -               | Mode Register Set    | ILLEGAL                              | 13,14   |

|                   | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh |                                      | 13      |

|                   | L  | L   | Н   | L  | BA      | X               | Precharge            | ILLEGAL                              | 4,12    |

|                   | L  | L   | Н   | Н  | BA      |                 | Bank Activate        | ILLEGAL                              | 4,11,12 |

| Row<br>Activating | L  | Н   | ┙   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                              | 4,12    |

|                   | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | ILLEGAL                              | 4,12    |

|                   | L  | Н   | Н   | Н  | Х       | X               | No Operation         | No Operation: Row Active after tRCD  |         |

|                   | Н  | Х   | Х   | Х  | Х       | Х               | Device Deselect      | No Operation: Row Active after tRCD  |         |

# CURRENT STATE TRUTH TABLE (Sheet 3 of 3)

| Current State      |    |     |     |    | Comma   | nd              |                      | Astion                                  | Natas  |

|--------------------|----|-----|-----|----|---------|-----------------|----------------------|-----------------------------------------|--------|

| Current State      | CS | RAS | CAS | WE | BA0,BA1 | A11-A0          | Description          | Action                                  | Notes  |

|                    | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | ILLEGAL                                 | 13,14  |

|                    | L  | L   | L   | Н  | Х       | Х               | Auto or Self Refresh | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | L  | BA      | Х               | Precharge            | ILLEGAL                                 | 4,13   |

| Write              | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | ILLEGAL                                 | 4,12   |

| Recovering         | L  | Н   | L   | L  | ВА      | Col Add.        | Write/WriteAP        | Start Write: Optional                   |        |

|                    |    |     |     |    |         | A10             |                      | AP(A10=H)                               |        |

|                    | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | Start Read: Optional<br>AP(A10=H)       | 9      |

|                    | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | No Operation: Row Active after tDPL     |        |

|                    | Н  | Х   | Х   | Х  | Х       | Х               | Device Deselect      | No Operation: Row Active after tDPL     |        |

|                    | L  | L   | L   | L  | OP (    |                 | Mode Register Set    | ILLEGAL                                 | 13,14  |

|                    | L  | L   | L   | Н  | X       | Х               | Auto or Self Refresh | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | L  | BA      | X               | Precharge            | ILLEGAL                                 | 4,13   |

| Write              | L  | L   | Н   | Ħ. | BA      |                 | Bank Activate        | ILLEGAL                                 | 4,12   |

| Recovering<br>with | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                                 | 4,12   |

| Auto<br>Precharge  | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | ILLEGAL                                 | 4,9,12 |

|                    | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | No Operation: Precharge after tDPL      |        |

|                    | Η  | Х   | Χ   | Х  | Х       | Х               | Device Deselect      | No Operation: Precharge after tDPL      |        |

|                    | L  | L   | L   | L  | OP (    |                 | Mode Register Set    | ILLEGAL                                 | 13,14  |

|                    | L  | L   | L   | Н  | Х       | X               | Auto or Self Refresh | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | L  | BA      | Х               | Precharge            | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | Н  | BA      |                 | Bank Activate        | ILLEGAL                                 | 13     |

| Refreshing         | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                                 | 13     |

|                    | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | ILLEGAL                                 | 13     |

|                    | L  | Н   | Н   | Н  | Х       | Х               | No Operation         | No Operation: idle after tRC            |        |

|                    | Н  | Х   | Χ   | Х  | Х       | Х               | Device Deselect      | No Operation: idle after tRC            |        |

|                    | L  | L   | L   | L  | OP (    | Code            | Mode Register Set    | ILLEGAL                                 | 13,14  |

|                    | L  | L   | L   | Н  | Χ       | Х               | Auto or Self Refresh | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | L  | BA      | Х               | Precharge            | ILLEGAL                                 | 13     |

|                    | L  | L   | Н   | Н  | BA      | Row Add.        | Bank Activate        | ILLEGAL                                 | 13     |

| Mode<br>Register   | L  | Н   | L   | L  | BA      | Col Add.<br>A10 | Write/WriteAP        | ILLEGAL                                 | 13     |

| Accessing          | L  | Н   | L   | Н  | BA      | Col Add.<br>A10 | Read/ReadAP          | ILLEGAL                                 | 13     |

|                    | L  | Н   | Н   | Н  | Х       | X               | No Operation         | No Operation: idle after 2 clock cycles |        |

|                    | Н  | Х   | Х   | X  | Х       | Х               | Device Deselect      | No Operation: idle after 2 clock cycles |        |

#### Note:

- 1. H: Logic High, L: Logic Low, X: Don't care, BA: Bank Address, AP: Auto Precharge.

- 2. All entries assume that CKE was active during the preceding clock cycle.

- 3. If both banks are idle and CKE is inactive, then in power down cycle

- 4. Illegal to bank in specified states. Function may be legal in the bank indicated by Bank Address, depending on the state of that bank.

- 5. If both banks are idle and CKE is inactive, then Self Refresh mode.

- 6. Illegal if tRCD is not satisfied.

- 7. Illegal if tRAS is not satisfied.

- 8. Must satisfy burst interrupt condition.

- 9. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 10. Must mask preceding data which don't satisfy tDPL.

- 11. Illegal if tRRD is not satisfied

- 12. Illegal for single bank, but legal for other banks in multi-bank devices.

- 13. Illegal for all banks.

- 14. Mode Register Set and Extended Mode Register Set is same command truth table except BA1.

### **CKE Enable(CKE) Truth TABLE**

|                | СК                |                  |    |     | Comr | nand |             |            |                                                           |       |

|----------------|-------------------|------------------|----|-----|------|------|-------------|------------|-----------------------------------------------------------|-------|

| Current State  | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS  | WE   | BA0,<br>BA1 | A11-<br>A0 | Action                                                    | Notes |

|                | Н                 | Х                | Х  | Х   | Х    | Х    | Х           | Х          | INVALID                                                   | 1     |

|                | L                 | Н                | Н  | Х   | Х    | Х    | Х           | Х          | Exit Self Refresh with Device<br>Deselect                 | 2     |

| Self Refresh   | L                 | Н                | L  | Н   | Н    | Н    | Х           | Х          | Exit Self Refresh with No Operation                       | 2     |

|                | L                 | Н                | L  | Н   | Н    | L    | Х           | Χ          | ILLEGAL                                                   | 2     |

| 1              | L                 | Н                | L  | Н   | L    | Χ    | Х           | Χ          | ILLEGAL                                                   | 2     |

| ]              | L                 | Н                | L  | L   | Χ    | Χ    | Х           | Χ          | ILLEGAL                                                   | 2     |

|                | L                 | L                | Х  | Χ   | Χ    | Χ    | Χ           | Χ          | Maintain Self Refresh                                     |       |

|                | Н                 | Х                | Х  | Х   | Χ    | Χ    | Х           | Χ          | INVALID                                                   | 1     |

| Power<br>Down  | L                 | Н                | Н  | Х   | Х    | Х    | Х           | Х          | Power Down mode exit, all<br>banks idle                   | 2     |

|                | L                 | Н                | L  | Χ   | Χ    | Χ    | Х           | Χ          | ILLEGAL                                                   | 2     |

| ]              | L                 | L                | Χ  | Χ   | Χ    | Χ    | Χ           | Χ          | Maintain Power Down Mode                                  |       |

| Deep           | Н                 | Х                | Х  | Χ   | Χ    | Χ    | Χ           | Χ          | INVALID                                                   | 1     |

| Power          | L                 | Н                | Х  | Х   | Χ    | Χ    | Х           |            | Deep Power Down mode exit                                 | 5     |

| Down           | L                 | L                | Χ  | Х   | Х    | Х    | Х           | Х          | Maintain Deep Power Down<br>Mode                          |       |

|                | Н                 | Н                | Н  | Х   | Χ    | Χ    |             |            | Refer to the idle State section                           | 3     |

| ·              | Н                 | Н                | L  | Н   | Χ    | Χ    |             |            | of the Current State Truth Table                          | 3     |

| 1              | Н                 | Н                | L  | L   | Н    | Χ    |             |            |                                                           | 3     |

| •              | Н                 | Н                | L  | L   | L    | Н    | Χ           | Χ          | Auto Refresh                                              |       |

| All Banks Idle | Н                 | Н                | L  | L   | L    | L    | Op (        | Code       | Mode Register Set                                         | 4     |

| •              | Н                 | L                | Н  | Χ   | Χ    | Χ    |             |            | Refer to the idle State section                           | 3     |

| ·              | Н                 | L                | L  | Н   | Χ    | Χ    |             |            | of the Current State Truth Table                          | 3     |

| ·              | Н                 | L                | L  | L   | Н    | Х    |             |            | •                                                         | 3     |

| •              | Н                 | L                | L  | L   | L    | Н    | Х           | Χ          | Entry Self Refresh                                        | 4     |

| •              | Н                 | L                | L  | L   | L    | L    | Op (        | Code       | Mode Register Set                                         |       |

|                | L                 | Х                | Χ  | Х   | Χ    | Х    | X           | Χ          | Power Down                                                | 4     |

| Any State      | Н                 | Н                | Χ  | Х   | Х    | Х    | Х           | Х          | Refer to operations of the Cur-<br>rent State Truth Table |       |

| other than     | Н                 | L                | Χ  | Χ   | Χ    | Χ    | Х           | Χ          | Begin Clock Suspend next cycle                            |       |

| listed above   | L                 | Н                | Χ  | Х   | Χ    | Χ    | Х           | Х          | Exit Clock Suspend next cycle                             |       |

| 1              | L                 | L                | Χ  | Х   | Χ    | Χ    | Х           | Χ          | Maintain Clock Suspend                                    |       |

**Note:** 1. For the given current state CKE must be low in the previous cycle.

- 2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high.

- 3. The address inputs depend on the command that is issued.

- 4. The Precharge Power Down mode, the Self Refresh mode, and the Mode Register Set can only be entered from the all banks idle state.

- 5. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. When exiting deep power down mode, a NOP (or Device Deselect) command is required on the first positive edge of clock after CKE goes high and is maintained for a minimum 200µsec.

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Symbol    | Rating     | Unit     |

|------------------------------------|-----------|------------|----------|

| Ambient Temperature                | ТА        | TBD        | °C       |

| Storage Temperature                | TSTG      | -55 ~ 125  | °С       |

| Voltage on Any Pin relative to VSS | VIN, VOUT | -1.0 ~ 4.6 | V        |

| Voltage on VDD relative to VSS     | VDD       | -1.0 ~ 4.6 | V        |

| Voltage on VDDQ relative to VSS    | VDDQ      | -1.0 ~ 4.6 | V        |

| Short Circuit Output Current       | los       | 50         | mA       |

| Power Dissipation                  | PD        | 1          | W        |

| Soldering Temperature Time         | TSOLDER   | 260 · 10   | °C · Sec |

Note: Operation at above absolute maximum rating can adversely affect device reliability.

# DC OPERATING CONDITION (TA= 0 to 70)

| Parameter            | Symbol | Min      | Тур | Max      | Unit | Note    |

|----------------------|--------|----------|-----|----------|------|---------|

| Power Supply Voltage | VDD    | 2.3      | 2.5 | 2.7      | V    | 1       |

| Power Supply Voltage | VDDQ   | 2.3      | 2.5 | 2.7      | V    | 1, 2    |

| Input High Voltage   | VIH    | 0.8*VDDQ | -   | VDDQ+0.3 | V    | 1, 2, 3 |

| Input Low Voltage    | VIL    | -0.3     | -   | 0.2*VDDQ | V    | 1, 2, 3 |

Note : 1. All Voltages are referenced to VSS = 0V

2. VDDQ must not exceed the level of VDD

3. Internal VREF = 0.9V

### AC OPERATING TEST CONDITION (TA= 0 to 70, VDD = 2.5V, VSS = 0V) )

| Parameter                                           | Symbol    | Value | Unit | Note |

|-----------------------------------------------------|-----------|-------|------|------|

| AC Input High/Low Level Voltage                     | VIH / VIL | TBD   | V    |      |

| Input Timing Measurement Reference Level Voltage    | Vtrip     | 0.9   | V    |      |

| Input Rise/Fall Time                                | tR/tF     | 1     | ns   |      |

| Output Timing Measurement Reference Level Voltage   | Voutref   | 0.9   | V    |      |

| Output Load Capacitance for Access Time Measurement | CL        | TBD   | pF   |      |

# **CAPACITANCE** (TA=2.5 C, f=1MHz)

| Parameter                     | Pin                                                    | Symbol | -6/H |     | -8/P/S |     | Unit  |  |

|-------------------------------|--------------------------------------------------------|--------|------|-----|--------|-----|-------|--|

| raiametei                     | F III                                                  | Symbol | Min  | Max | Min    | Max | J.iit |  |

| Input capacitance             | CLK                                                    | CI1    | 2.5  | 3.0 | 2.3    | 3.0 | pF    |  |

|                               | A0~A11, BA0, BA1, CKE, CS,<br>RAS, CAS, WE, UDQM, LDQM | CI2    | 1.5  | 3.0 | 1.5    | 3.0 | pF    |  |

| Data input/output capacitance | DQ0 ~ DQ15                                             | CI/O   | 4.0  | 5.2 | 4.0    | 5.5 | pF    |  |

# **DC CHARACTERISTICS I** (TA=0 to 79 C, VDD=2.5V VDDQ=2.5V)

| Parameter              | Symbol | Min        | Max | Unit | Note |

|------------------------|--------|------------|-----|------|------|

| Input Leakage Current  | Ш      | -1         | 1   | μΑ   | 1    |

| Output Leakage Current | ILO    | -1         | 1   | μΑ   | 2    |

| Output High Voltage    | Voн    | VDDQ - 0.2 | -   | V    | 3    |

| Output Low Voltage     | VoL    | -          | 0.2 | V    | 4    |

**Note:** 1. VIN = 0 to 2.5V. All other pins are not tested under VIN = 0V.

2. Dout is disabled. Vout= 0 to 1.95V.

3. IOUT = -0.1mA

4. IOUT = + 0.1mA

# $\textbf{DC CHARACTERISTICS II} \ (\mathsf{TA=0} \ \mathsf{to} \ \mathsf{79} \ \mathsf{C}, \ \mathsf{VDD=2.5V} \ \mathsf{VDDQ=2.5V} \ \mathsf{VSS=0V})$

| Parameter                                        | Symbol                                | Test Condition                                                                                                                                             |             |     | Speed     |          | Unit | Note |   |

|--------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-----------|----------|------|------|---|

| rarameter                                        | Symbol                                | rest Condition                                                                                                                                             | •           | -H  | -P        | -S       | 0    | NOTE |   |

| Operating Current                                | IDD1                                  | Burst length=1, One bank activ<br>tRC ≥ tRC (min), IOL=0mA                                                                                                 | ve          | 120 | 110       | 110      | mA   | 1    |   |

| Precharge Standby Current                        | IDD2P                                 | CKE ≤ VIĽ(max), tCK = 15ns                                                                                                                                 |             |     | 2         | mA       |      |      |   |

| in Power Down Mode                               | IDD2PS                                | CKE ≤ VIĽ(max), tCK = ∞                                                                                                                                    |             |     | 300       |          | μΑ   |      |   |

| Precharge Standby Current in Non Power Down Mode | IDD2N                                 | CKE ≥ VIH(min), CS ≥ VIH(min<br>Input signals are changed one<br>2clks. All other pins ≥ VDD-0.2                                                           | time during | 15  |           |          | mA   |      |   |

| III Noil Fower Down wode                         | IDD2NS                                | CKE ≥ VIH(min), tCK = ∞<br>Input signals are stable.                                                                                                       |             | 15  |           |          |      |      |   |

| Active Standby Current IDD3P                     |                                       | CKE ≤ VIL(max), tCK = 15ns                                                                                                                                 |             |     | 5         |          | mA   |      |   |

| in Power Down Mode                               | IDD3PS                                | CKE ≤ VIĽ(max), tCK = ∞                                                                                                                                    |             | 5   |           |          | mA   |      |   |

| Active Standby Current in Non Power Down Mode    | IDD3N                                 | $CKE \ge VIH(min), \overline{CS} \ge VIH(min), tCK = 15ns$<br>Input signals are changed one time during 2clks. All other pins $\ge VDD-0.2V$ or $\le 0.2V$ |             |     | 30        |          |      |      |   |

| iii Noii Fower Down Mode                         | IDD3NS                                | CKE ≥ VIH(min), tCK = ∞<br>Input signals are stable.                                                                                                       |             | 20  |           |          |      |      |   |

| Burst Mode Operating                             | IDD4                                  | tCK≥tCK(min), IOL=0mA                                                                                                                                      | CL=3        | 130 | 110       | 110      | mA   | 1    |   |

| Current                                          | T T T T T T T T T T T T T T T T T T T | All banks active                                                                                                                                           | CL=2        | 140 | 120       | 120 IIIA |      | ·    |   |

| Auto Refresh Current                             | IDD5                                  | tRRC ≥ tRRC(min), All banks active                                                                                                                         |             | 220 | 200       | 200      | mA   | 2    |   |

| Self Refresh Current                             | IDD6                                  | CKE ≤ 0.2V                                                                                                                                                 |             |     | KE ≤ 0.2V |          |      |      | 3 |

| Standby Current in Deep<br>Power Down Mode       | TBD                                   | TBD 60                                                                                                                                                     |             |     | μΑ        |          |      |      |   |

Note: 1. IDD1 and IDD4 depend on output loading and cycle rates. Specified values are measured with the output open 2. Min. of tRRC (Refresh RAS cycle time) is shown at AC CHARACTERISTICS II.

- 3. See the tables of next page for more specific IDD6 current values.

# DC CHARACTERISTICS III - Normal (IDD6) (VDD=2.5V VDDQ=2.5V VSS=0V)

| Temp. |            |                       | Memory Array             | 1                           |                                |      |

|-------|------------|-----------------------|--------------------------|-----------------------------|--------------------------------|------|

| (°C)  | Total Bank | Half of Total<br>Bank | Quarter of<br>Total Bank | One eighth of<br>Total Bank | One sixteenth of<br>Total Bank | Unit |

| 85    | 600        | 420                   | 340                      | 280                         | 230                            | μΑ   |

| 70    | 400        | 280                   | 230                      | 190                         | 160                            | μΑ   |

| 45    | 300        | 210                   | 170                      | 150                         | 140                            | μΑ   |

| 15    | 200        | 180                   | 160                      | 140                         | 130                            | μΑ   |

# DC CHARACTERISTICS III - Low Power (IDD6) (VDD=2.5V VDDQ=2.5V VSS=0V)

| Temp. |            |                       | 1                        |                             |                                |      |

|-------|------------|-----------------------|--------------------------|-----------------------------|--------------------------------|------|

| (°C)  | Total Bank | Half of Total<br>Bank | Quarter of<br>Total Bank | One eighth of<br>Total Bank | One sixteenth of<br>Total Bank | Unit |

| 85    | 500        | 350                   | 300                      | 240                         | 190                            | μΑ   |

| 70    | 350        | 250                   | 200                      | 160                         | 130                            | μΑ   |

| 45    | 250        | 180                   | 150                      | 130                         | 110                            | μΑ   |

| 15    | 150        | 130                   | 120                      | 110                         | 100                            | μΑ   |

# DC CHARACTERISTICS III - Super Low Power (IDD6) (VDD=2.5V VDDQ=2.5V VSS=0V)

| Temp. |            |                       | Memory Array             | !                           |                                |      |

|-------|------------|-----------------------|--------------------------|-----------------------------|--------------------------------|------|

| (°C)  | Total Bank | Half of Total<br>Bank | Quarter of<br>Total Bank | One eighth of<br>Total Bank | One sixteenth of<br>Total Bank | Unit |

| 85    | TBD        | TBD                   | TBD                      | TBD                         | TBD                            | μΑ   |

| 70    | TBD        | TBD                   | TBD                      | TBD                         | TBD                            | μΑ   |

| 45    | TBD        | TBD                   | TBD                      | TBD                         | TBD                            | μΑ   |

| 15    | TBD        | TBD                   | TBD                      | TBD                         | TBD                            | μΑ   |

# AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)

| Param                | -1                             | Cumbal | ŀ   | 1    | F   | •    |     | 3    | Unit | Note |

|----------------------|--------------------------------|--------|-----|------|-----|------|-----|------|------|------|

| Param                | eter                           | Symbol | Min | Max  | Min | Max  | Min | Max  | Unit | Note |

| System Clock         | CAS Latency=3                  | tCK3   | 7.5 | 1000 | 10  | 1000 | 10  | 1000 | ns   |      |

| Cycle Time           | CAS Latency=2                  | tCK2   | 10  |      | 10  |      | 12  |      | ns   |      |

| Clock High Pulse Wi  | dth                            | tCHW   | 2.5 | -    | 3   | -    | 3   | -    | ns   | 1    |

| Clock Low Pulse Wid  | łth                            | tCLW   | 2.5 | -    | 3   | -    | 3   | -    | ns   | 1    |

| Access Time          | CAS Latency=3                  | tAC3   | -   | 5.4  | -   | 6    | -   | 6    | ns   | 2    |

| From Clock           | CAS Latency=2                  | tAC2   | -   | 6    | -   | 6    | -   | 6    | ns   |      |

| Data-out Hold Time   |                                | tOH    | 2.7 | -    | 3   | -    | 3   | -    | ns   |      |

| Data-Input Setup Tin | Data-Input Setup Time          |        | 1.5 | -    | 2   | -    | 2   | -    | ns   | 1    |

| Data-Input Hold Time | Э                              | tDH    | 0.8 | -    | 1   | -    | 1   | -    | ns   | 1    |

| Address Setup Time   |                                | tAS    | 1.5 | -    | 2   | -    | 2   | -    | ns   | 1    |

| Address Hold Time    |                                | tAH    | 0.8 | -    | 1   | -    | 1   | -    | ns   | 1    |

| CKE Setup Time       |                                | tCKS   | 1.5 | -    | 2   | -    | 2   | -    | ns   | 1    |

| CKE Hold Time        |                                | tCKH   | 0.8 | -    | 1   | -    | 1   | -    | ns   | 1    |

| Command Setup Tin    | ne                             | tCS    | 1.5 | -    | 2   | -    | 2   | -    | ns   | 1    |

| Command Hold Time    | Э                              | tCH    | 0.8 | -    | 1   | -    | 1   | -    | ns   | 1    |

| CLK to Data Output   | K to Data Output in Low-Z Time |        | 1   | -    | 1   | -    | 1   | -    | ns   |      |

| CLK to Data Output   | CAS Latency=3                  | tOHZ3  | 2.7 | 5.4  | 3   | 6    | 3   | 6    | ns   |      |

| in High-Z Time       | CAS Latency=2                  | tOHZ2  | 2.7 | 5.4  | 3   | 6    | 3   | 6    | ns   |      |

Note: 1. Assume tR / tF (input rise and fall time) is 1ns. If tR & tF > 1ns, then [(tR+tF)/2-1]ns should be added to the parameter.

2. Access time to be measured with input signals of 1v/ns edge rate, from 0.8v to 0.2v. If tR > 1ns, then (tR/2-0.5)ns should be added to the parameter.

# AC CHARACTERISTICS II (AC operating conditions unless otherwise noted)

| Dorom                 | oto v                          | Cumbal | ı   | 1    | ı   | P    | 9   | 3    | I Imit | Note |

|-----------------------|--------------------------------|--------|-----|------|-----|------|-----|------|--------|------|

| Param                 | eter                           | Symbol | Min | Max  | Min | Max  | Min | Max  | Unit   | Note |

| RAS Cycle Time        | Operation                      | tRC    | 65  | -    | 70  | -    | 70  | -    | ns     |      |

|                       | Auto Refresh                   | tRRC   | 65  |      | 70  | •    | 70  |      | ns     |      |

| RAS to CAS Delay      |                                | tRCD   | 20  | -    | 20  | -    | 20  | -    | ns     |      |

| RAS Active Time       |                                | tRAS   | 45  | 100K | 50  | 100K | 50  | 100K | ns     |      |

| RAS Precharge Time    | Э                              | tRP    | 20  | -    | 20  | -    | 20  | -    | ns     |      |

| RAS to RAS Bank A     | ctive Delay                    | tRRD   | 15  | -    | 20  | -    | 20  | -    | ns     |      |

| CAS to CAS Delay      | CAS to CAS Delay               |        | 1   | -    | 1   | -    | 1   | -    | tCK    |      |

| Write Command to [    | Write Command to Data-In Delay |        | 0   | -    | 0   | -    | 0   | -    | tCK    |      |

| Data-in to Precharge  | e Command                      | tDPL   | 2   | -    | 1   | -    | 1   | -    | tCK    |      |

| Data-In to Active Co  | mmand                          | tDAL   | 5   | -    | 3   | -    | 3   | -    | tCK    |      |

| DQM to Data-Out Hi    | -Z                             | tDQZ   | 2   | -    | 2   | -    | 2   | -    | tCK    |      |

| DQM to Data-In Mas    | sk                             | tDQM   | 0   | -    | 0   | -    | 0   | -    | tCK    |      |

| MRS to New Comma      | and                            | tMRD   | 2   | -    | 2   | -    | 2   | -    | tCK    |      |

| Precharge to Data     | CAS Latency=3                  | tPROZ3 | 3   | -    | 3   | -    | 3   | -    | tCK    |      |

| Output High-Z         | CAS Latency=2                  | tPROZ2 | 2   |      | 2   |      | 2   |      | tCK    |      |

| Power Down Exit Tir   | Power Down Exit Time           |        | 1   | -    | 1   | -    | 1   | -    | tCK    |      |

| Self Refresh Exit Tin | ne                             | tSRE   | 1   | -    | 1   | -    | 1   | -    | tCK    | 1    |

| Refresh Time          |                                | tREF   | -   | 64   | -   | 64   | -   | 64   | ns     |      |

Note: 1. A new command can be given tRRC after self refresh exit.

# **Special Operation for Low Power Consumption**

### **Deep Power Down Mode**

Deep Power Down Mode is an operating mode to achieve maximum power reduction by cutting the power of the whole memory array of the devices.

Data will not be retained once the device enters Deep Power Down Mode.

Full initialization is required when the device exits from Deep Power Down Mode.

### **Truth Table**

| Current State      | Command                  | CKEn-1 | CKEn | cs | RAS | CAS | WE |

|--------------------|--------------------------|--------|------|----|-----|-----|----|

| Idle               | Deep Power<br>Down Entry | Н      | L    | L  | Н   | Н   | L  |

| Deep Power<br>Down | Deep Power<br>Down Exit  | L      | Н    | Х  | Х   | X   | X  |

### **Deep Power Down Mode Entry**

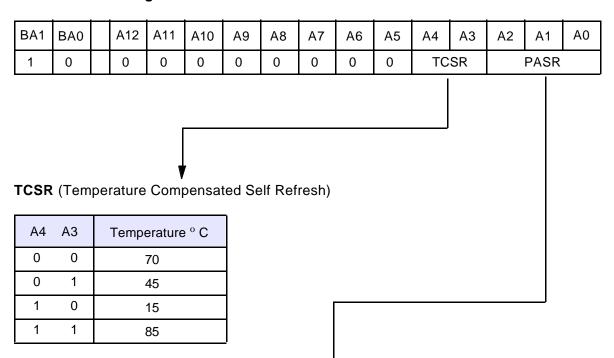

The Deep Power Down Mode is entered by having /CS and /WE held low with /RAS and /CAS high at the rising edge of the clock, while CKE is low. The following diagram illustrates deep power down mode entry.

### **Deep Power Down Mode (Continued)**

### **Deep Power Down Mode Exit Sequence**

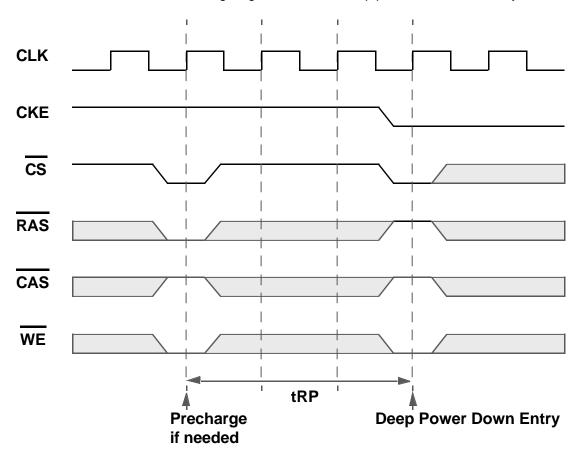

The Deep Power Down mode is exited by asserting CKE high.

After the exit, the following sequence is needed to enter a new command.

- 1. Maintain NOP input conditions for a minimum of 200µsec

- 2. Issue precharge commands for all banks of the device

- 3. Issue 8 or more auto refresh commands

- 4. Issue a mode register set command to initialize the mode register

- 5. Issue an extended mode register set command to initialize the extended mode register

The following timing diagram illustrates deep power down mode exit sequence.

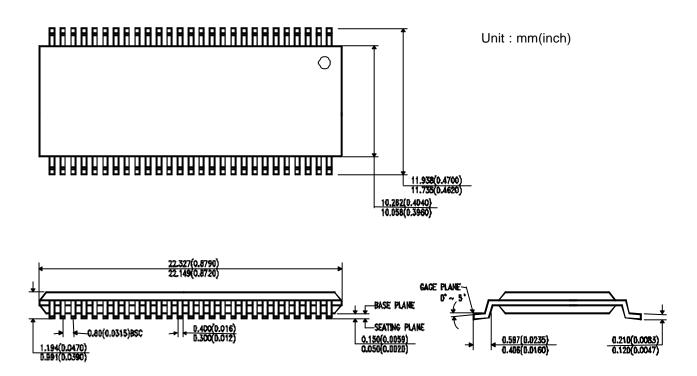

### **PACKAGE INFORMATION**

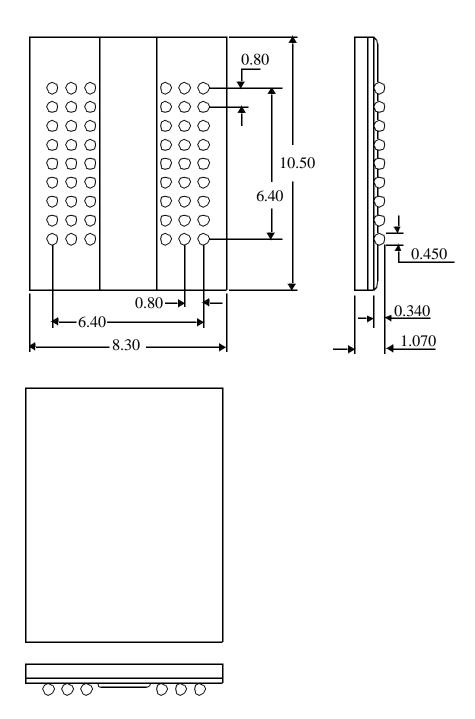

54 Ball 0.8mm pitch 8.3mm x 10.5mm FBGA

### **PACKAGE INFORMATION**

# 400mil 54pin Thin Small Outline Package