### Combo (Spindle & VCM) Driver

# **HITACHI**

ADE-207-246D (Z) Preliminary, 5th Edition Oct. 1, 1998

#### **Description**

This COMBO driver for HDD application consists of sensorless spindle driver and BTL type VCM driver.

"PWM soft switching function" for low power dissipation and less commutation acoustic noise at the same time is implemented by using the IPIC\* process.

Note: Intelligent Power IC

#### **Features**

- · PWM soft switching drive

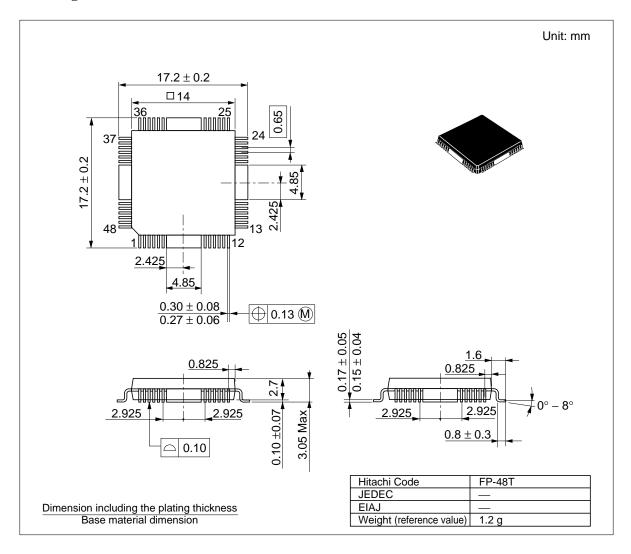

- Small surface mount package: FP-48T

- Low thermal resistance: 30°C/W with 4 layer multi glass-epoxy board

- Low output on resistance

- Spindle  $1.2 \Omega$  Typ

- VCM 1.4 Ω Typ

- TTL compatible input level (with 3.3 V logic interface)

- High precision reference voltage output (for 3.3 V power supply)

#### **Functions**

- 16 bit serial port

- 2.0 A Max/3-phase spindle motor driver with PWM soft switch function

- 1.5 A Max BTL VCM driver with low crossover distortion

- PWMDAC for VCM drive current control

- Power off brake function for spindle motor

- Auto retract with constant output voltage

- Booster

- Internal Protector (OTSD, LVI)

- Precision power monitor

- · OP amplifier

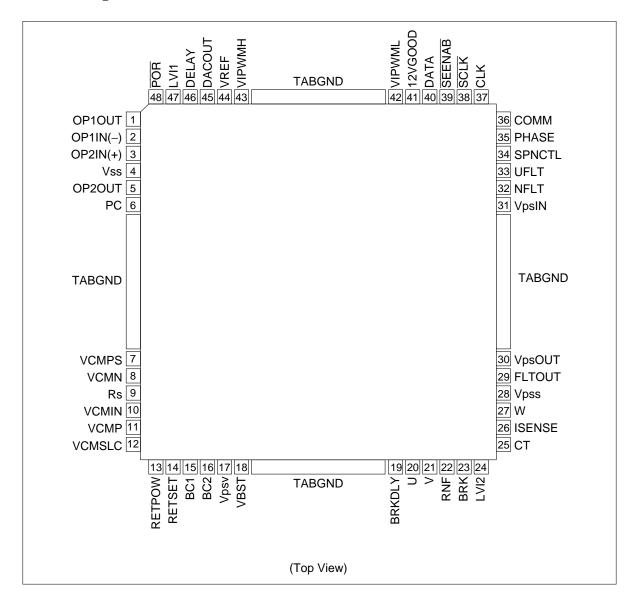

### **Pin Arrangement**

# **Pin Description**

| Pin No. | Pin Name | Function                                                                                        |

|---------|----------|-------------------------------------------------------------------------------------------------|

| 1       | OP1OUT   | Output of OP amp. 1                                                                             |

| 2       | OP1IN(-) | Inverted input of OP amp. 1                                                                     |

| 3       | OP2IN(+) | Non-inverted input of OP amp. 2                                                                 |

| 4       | Vss      | Power supply for +5 V                                                                           |

| 5       | OP2OUT   | Output of OP amp. 2                                                                             |

| 6       | PC       | External time constant connection terminal for phase compensation of VCM driver                 |

| 7       | VCMPS    | Current sensing terminal for VCM driver                                                         |

| 8       | VCMN     | Output of VCM driver (Inverted output of VCMP)                                                  |

| 9       | Rs       | Current sensing terminal for VCM driver (differential input for VCMPS)                          |

| 10      | VCMIN    | Input of VCM driver (differential input for VREF)                                               |

| 11      | VCMP     | Output of VCM driver (inverted output of VCMN)                                                  |

| 12      | VCMSLC   | External capacitor connection terminal for stabilizing internal reference voltage of VCM driver |

| 13      | RETPOW   | Power supply terminal of retract driver                                                         |

| 14      | RETSET   | Output voltage set up terminal of retract driver                                                |

| 15      | BC1      | External capacitor connection terminal for pumping of booster                                   |

| 16      | BC2      |                                                                                                 |

| 17      | Vpsv     | +12 V power supply for VCM driver                                                               |

| 18      | VBST     | Output of booster circuit                                                                       |

| 19      | BRKDLY   | Time constance set up terminal of delayed brake                                                 |

| 20      | U        | U-phase output of spindle motor driver                                                          |

| 21      | V        | V-phase output of spindle motor driver                                                          |

| 22      | RNF      | Current sensing terminal for spindle motor driver                                               |

| 23      | BRK      | External capacitor connection terminal for power off brake                                      |

| 24      | LVI2     | Resistor connection terminal for set up the threshold of +3.3 V power monitor                   |

| 25      | СТ       | Center tap connection terminal for spindle motor                                                |

| 26      | ISENSE   | Input of PWM comparator                                                                         |

| 27      | W        | W-phase output of spindle motor driver                                                          |

| 28      | Vpss     | +12 V power supply for spindle motor driver                                                     |

| 29      | FLTOUT   | PWMDAC output for current control of spindle motor driver                                       |

| 30      | VpsOUT   | Output of power supply switch                                                                   |

| 31      | VpsIN    | Input of power supply switch (+12 V)                                                            |

| 32      | NFLT     | Output of pre-filter for B-EMF sensing (capacitor connection terminal)                          |

| 33      | UFLT     |                                                                                                 |

# Pin Description (cont)

| Pin No. | Pin Name | Function                                                                     |

|---------|----------|------------------------------------------------------------------------------|

| 34      | SPNCTL   | PWMDAC input for current control of spindle motor driver                     |

| 35      | PHASE    | Toggle signal output for zero-crossing timing of B-EMF                       |

| 36      | COMM     | Commutation signal input for spindle motor driver during synchronous driving |

| 37      | CLK      | Master clock input of commutation logic circuit                              |

| 38      | SCLK     | Clock input of serial port for data strobe                                   |

| 39      | SEENAB   | Enable signal input of serial port                                           |

| 40      | DATA     | Data signal input of serial port                                             |

| 41      | 12VGOOD  | Output of power monitor for +12 V power supply (open drain)                  |

| 42      | VIPWML   | PWMDAC input for current control of VCM driver                               |

| 43      | VIPWMH   |                                                                              |

| 44      | VREF     | Output of internal reference voltage                                         |

| 45      | DACOUT   | PWMDAC output for current control of VCM driver                              |

| 46      | DELAY    | Capacitor connection terminal for set up the power on reset time             |

| 47      | LVI1     | Resistor connection terminal for set up the threshold of +12 V power monitor |

| 48      | POR      | Output of power on reset signal                                              |

| TAB     | GND      | Ground of this IC                                                            |

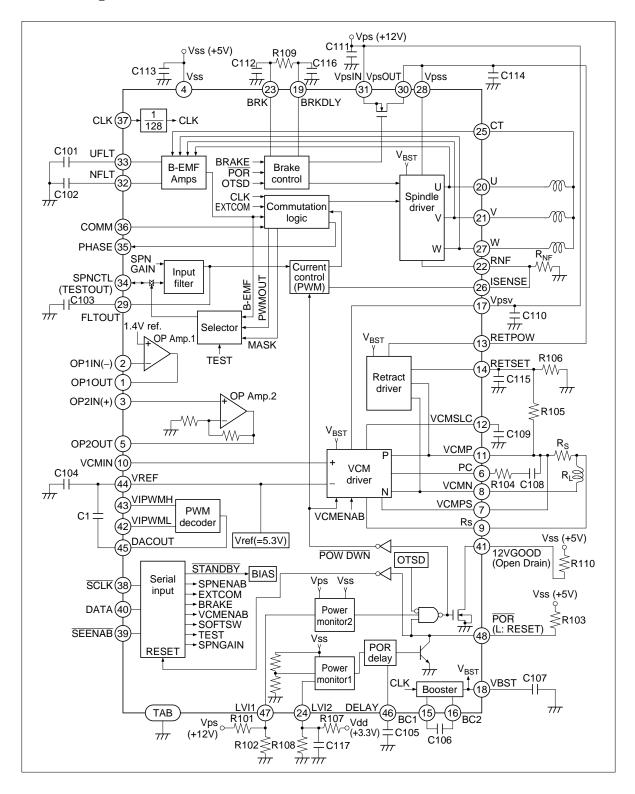

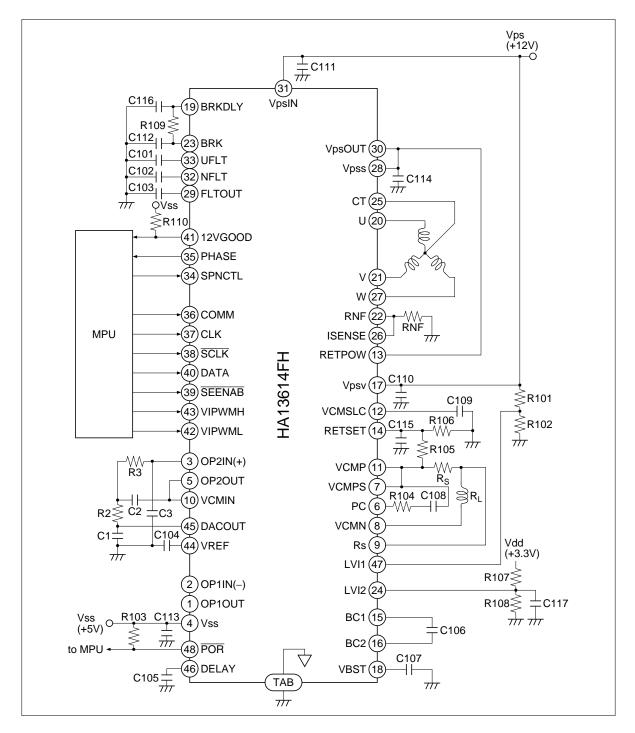

#### **Block Diagram**

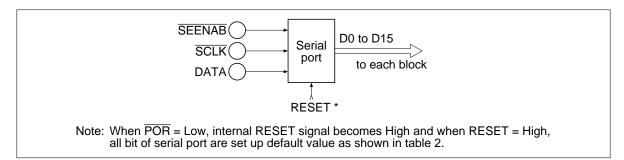

#### **Serial Port**

#### Construction

Figure 1 Construction of Serial Port

Table 1 Truth Table of Internal RESET Signal

| Input | Output | Note |

|-------|--------|------|

| POR   | RESET  |      |

| Low   | High   | 1    |

| Open  | Low    | 1    |

Note: 1. When +5 V or +3.3 V power supply goes to Low, then  $\overline{POR}$  = Low.  $\overline{POR}$  output is able to construct the wired logic with external signal.

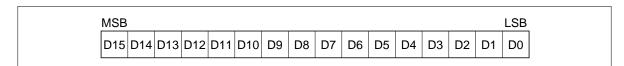

#### **Input Data**

Figure 2 Input Data

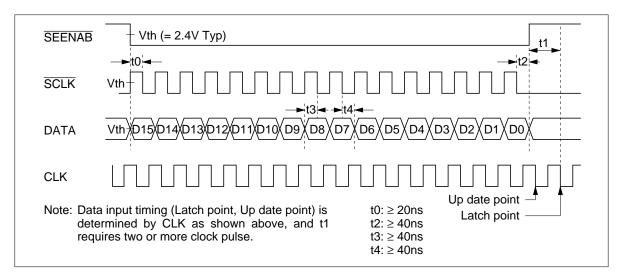

The serial port is required the 16 bits data (D0 to D15). When the data length is less than 16 bits, the internal register will not be up dated. And when the data length is more than 16 bits, this register will take later 16 bits and ignore the faster bit.

#### **Bit Assignment**

Table 2 Bit Assignment of Serial Port

| Bit | Symbol   | 1 (= High)               | 0 (= Low)            | Default | Note |

|-----|----------|--------------------------|----------------------|---------|------|

| D0  | STANDBY  | Active                   | Stand by             | 0       | 1    |

| D1  | VCMENAB  | VCM enable               | VCM disable          | 0       | 1    |

| D2  | SPNENAB  | Spindle enable           | Spindle disable      | 0       | 1    |

| D3  | BRAKE    | Brake enable             | Brake disable        | 0       | 1    |

| D4  | SENSEN   | B-EMF sense enable       | B-EMF sense disable  | 0       | 2    |

| D5  | VARCNT   | Variable count           | Normal count         | 0       | 2    |

| D6  | EXTCOM   | External commutation     | Internal commutation | 0       | 2    |

| D7  | SRCTL1   | High slew rate           | Low slew rate        | 0       | 3    |

| D8  | SRCTL2   | Commutation time select  | (See table 4)        | 0       | 4    |

| D9  | SRCTL3   | -                        |                      | 0       | 4    |

| D10 | OFFTIME1 | Off time select of PWM d | rive (See table 5)   | 0       | 5    |

| D11 | OFFTIME2 | _                        |                      | 0       | 5    |

| D12 | SPNGAIN  | High gain                | Low gain             | 0       | 6    |

| D13 | RETRACT  | Retract                  | Not retract          | 0       | 1    |

| D14 | TEST1    | For testing              |                      | 0       | 7    |

| D15 | TEST2    |                          |                      | 0       | 7    |

Note: 1. The priority of operation for each bit is as shown in table 3.

- 2. This bit is using for start up of spindle motor. Please refer to the application note explained about start up of spindle motor.

- 3. The slew rate during every commutation of spindle motor is selectable by using this bit. Please select the suitable value of this bit for your motor.

- 4. This bit is used for setting up the commutation time (refer to figure 9) of spindle motor as shown in table 4.

- 5. This bit is used for setting up the off time at PWM driving of spindle motor as shown in table 5.

- 6. The gain of current control for spindle motor is selectable by using this bit. Please select the suitable value of this bit for your motor.

- 7. This bit will be used in fabrication test. Please set up D15 = "0" normally.

SPNCTL terminal (pin 35) is using for output terminal in the case of "1" for testing. Then please do not input signal into pin 35 from outside.

**Table 3** Truth Table

| Input   |               |         |         |       |         |         | Driver Output     |               |                   |                 |

|---------|---------------|---------|---------|-------|---------|---------|-------------------|---------------|-------------------|-----------------|

| OTSD    | 12/GOOD<br>*1 | STANDBY | SPNENAB | BRAKE | RETRACT | VOMENAB | Spindle<br>Driver | VCM<br>Driver | Retract<br>Driver | Power<br>Switch |

| Enable  | Low           | X*2     | ×       | ×     | ×       | ×       | Braking           | Cut off       | On                | Cut off         |

| Disable | Low           | ×       | ×       | ×     | ×       | ×       | Braking           | Cut off       | On                | Cut off         |

| Disable | High          | Low     | ×       | ×     | ×       | ×       | Braking           | Cut off       | Cut off           | Cut off         |

| Disable | High          | High    | 0       | 0     | 0       | 0       | Cut off           | Cut off       | Cut off           | On              |

| Disable | High          | High    | 0       | 1     | 0       | 0       | Braking           | Cut off       | Cut off           | On              |

| Disable | High          | High    | 1       | ×     | 0       | 0       | On                | Cut off       | Cut off           | On              |

| Disable | High          | High    | 0       | 0     | 0       | 1       | Cut off           | On            | Cut off           | On              |

| Disable | High          | High    | 0       | 1     | 0       | 1       | Braking           | On            | Cut off           | On              |

| Disable | High          | High    | 1       | ×     | 0       | 1       | On                | On            | Cut off           | On              |

| Disable | High          | High    | 0       | 0     | 1       | ×       | Cut off           | Cut off       | On                | On              |

| Disable | High          | High    | 0       | 1     | 1       | ×       | Braking           | Cut off       | On                | On              |

| Disable | High          | High    | 1       | ×     | 1       | ×       | On                | Cut off       | On                | On              |

Note: 1. The 12VGOOD terminal is open drain output type. The 12VGOOD signal output is determined by the power monitor output for 12 V power supply, POR output and OTSD signal as shown in the table below.

| 12 V Supply | POR  | OTSD    | 12VGOOD |

|-------------|------|---------|---------|

| Cut off     | ×    | ×       | Low     |

| ×           | Low  | ×       | Low     |

| ×           | ×    | Enable  | Low     |

| Normal      | High | Disable | High    |

<sup>2.</sup> The symbol "x" means "Don't care".

**Table 4** Commutation Time

| SRCTL2 | SRCTL3 | Commutation Time (s) |

|--------|--------|----------------------|

| 0      | 0      | 24 × (128 / fclk)    |

| 0      | 1      | 16 × (128 / fclk)    |

| 1      | 0      | 12 × (128 / fclk)    |

| 1      | 1      | No slew rate control |

Note: The "fclk" is the frequency on pin "CLK". (Recommendation: 20 MHz)

**Table 5 OFF Time at PWM Drive**

| OFFTIME1 | OFFTIME2 | OFF Time (s)                 |

|----------|----------|------------------------------|

| 0        | 0        | 1 × (32 / fclk) + (4 / fclk) |

| 0        | 1        | 2 × (32 / fclk) + (4 / fclk) |

| 1        | 0        | 3 × (32 / fclk) + (4 / fclk) |

| 1        | 1        | 4 × (32 / fclk) + (4 / fclk) |

#### **Data Input Timing**

**Figure 3 Input Timing of Serial Port**

### **Timing Chart**

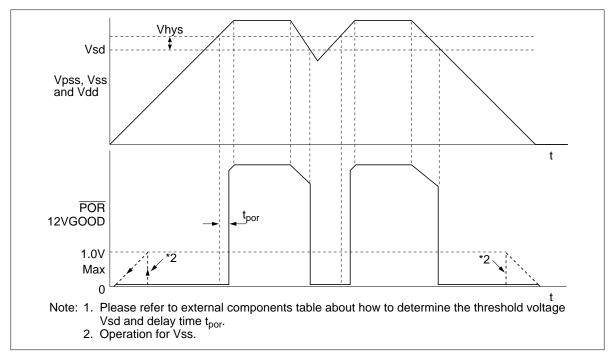

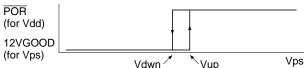

#### Power on Reset (1)

Figure 4 Operation of the Power Monitor (1)

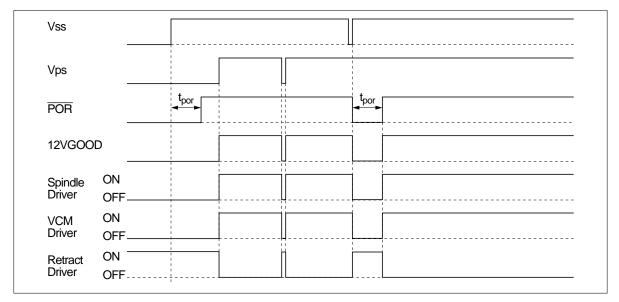

#### Power on Reset (2)

Figure 5 Operation of the Power Monitor (2)

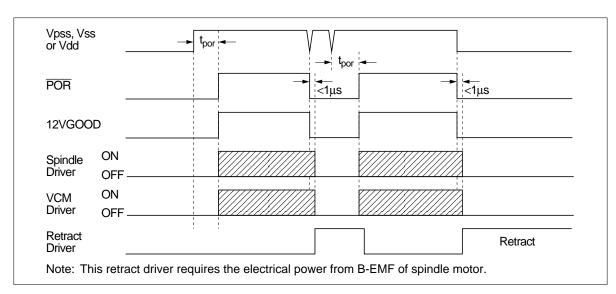

#### Power on Reset (3)

Figure 6 Operation of the Power Monitor (3)

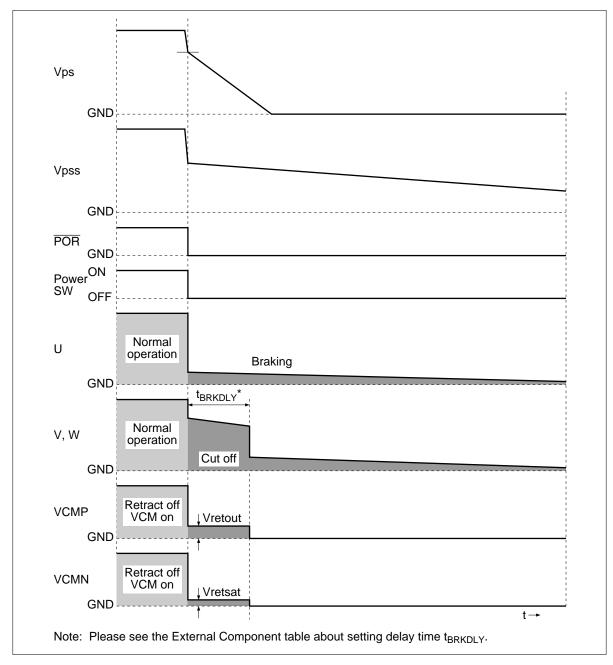

#### **Power Off Retract & Brake**

Figure 7 Operation of Power Off Retract & Brake

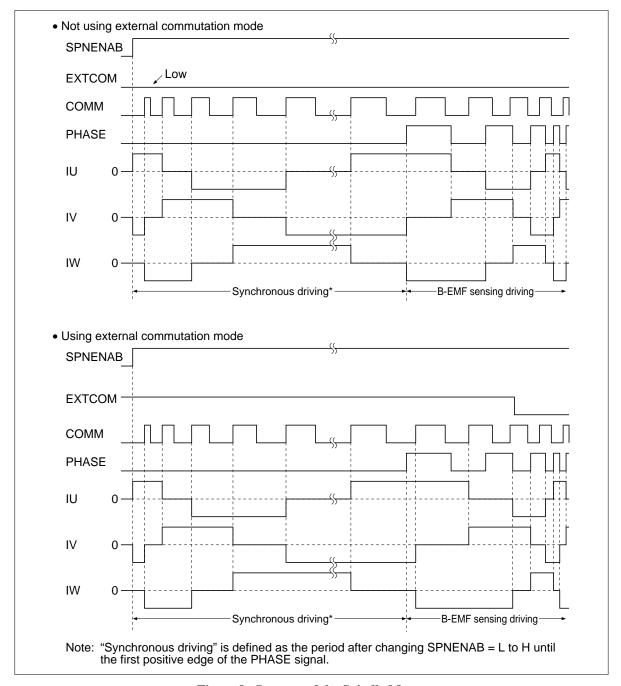

#### Start-up of the Spindle motor

Figure 8 Start-up of the Spindle Motor

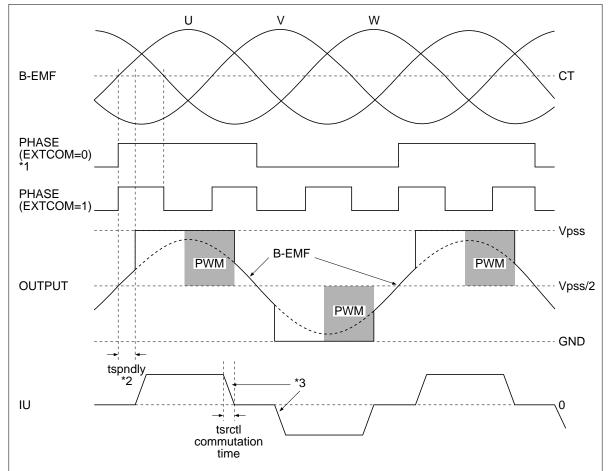

#### **Commutation Timing of the Spindle motor**

Note: 1. In the case of external commutation mode (EXTCOM=1), the signal PHASE will toggle at every B-EMF zero-crossing, and selected the internal commutation mode (EXTCOM=0), the PHASE will have the same period as B-EMF of the spindle motor.

- 2. This is delay time by pre-LPF of the B-EMF amplifier. This delay time can be adjust by the value of external filter capacitor C101, C102. To get the maximum driving efficiency of the spindle motor, these capacitor value should be chosen as equation (17) in the "External components" section.

- 3. The slew rate of every commutation timing is controllable by changing the SRCTL1, SRCTL2 and SRCTL3 in the serial port.

Figure 9 Commutation Timing of the Spindle motor

### **Application**

# **External Components**

| Parts No.      | Recommendation Value | Purpose                                                   | Note |

|----------------|----------------------|-----------------------------------------------------------|------|

| R101 —         |                      | Set up threshold of power monitor for Vps                 | 1    |

| R102           | <del>_</del>         | _                                                         |      |

| R103           | ≥ 5.6 kΩ             | Pull up for POR terminal                                  |      |

| R104           | <del></del>          | Gain dumping for VCM driver                               | 5    |

| R105           | <del>_</del>         | Set up output voltage of retract driver for pin VCMP      | 6    |

| R106           | <del>_</del>         | _                                                         |      |

| R107           | <del></del>          | Set up threshold of power monitor for Vdd                 | 1    |

| R108           | _                    | _                                                         |      |

| R109           | <del>_</del>         | Set up time constance of delayed brake                    | 12   |

| R110           | ≥ 5.6 kΩ             | Pull up for 12VGOOD terminal                              |      |

| R2             | _                    | Filter constant of LPF                                    | 3    |

| R3             | <del></del>          | _                                                         |      |

| Rnf            | 0.33 Ω               | Current sensing for spindle motor                         | 7    |

| R <sub>s</sub> | 0.47 Ω               | Current sensing for VCM                                   | 4    |

| C101, C102     | <del>_</del>         | Pre-filter of B-EMF amplifier                             | 10   |

| C103           | <del></del>          | Filter of PWMDAC for current control of spindle motor     | 9    |

| C104           | 0.1 μF               | Filter of internal reference output                       |      |

| C105           | 0.1 μF               | Set up delay time of POR signal                           | 8    |

| C106           | 0.22 μF              | Boost up of power supply                                  |      |

| C107           | 2.2 μF               | Stabilizing boost up voltage                              |      |

| C108           | <del></del>          | Gain dumping for VCM driver                               | 5    |

| C109           | 0. 1 μF              | Stabilizing reference voltage of VCM driver               |      |

| C110           | 0.1 μF               | By passing of power supply                                |      |

| C111           | 0.1 μF               | _                                                         |      |

| C112           | <del></del>          | Keeping brake function                                    | 12   |

| C113           | 0.1 μF               | By passing of power supply                                |      |

| C114           | 0.1 μF               | _                                                         |      |

| C115           | <del>_</del>         | Stabilizing output voltage of retract driver for pin VCMP | 11   |

| C116           | _                    | Set up time constance of delayed brake                    | 12   |

| C117           | 0.1 μF               | Stabilizing LVI2 terminal                                 |      |

| C1             | _                    | Filter constant of LPF                                    | 3    |

| C2             | _                    | _                                                         |      |

| C3             | _                    | _                                                         |      |

Notes: 1. The operation threshold voltage of Vps or Vdd is determined by resistor R101, R102 or R107, R108 as follows.

• for Vps

Recovery voltage

$$Vup(Vps) = (Vsd1 + Vhys3) \cdot \left(1 + \frac{R101}{R102}\right) \qquad [V]$$

Cut off voltage

$$Vdwn(Vps) = Vsd1 \cdot \left(1 + \frac{R101}{R102}\right) \qquad [V]$$

(2)

where, Vsd1 : Operating voltage of the power monitor [V] (refer to Electrical Characteristics)

Vhys3: Hysteresis voltage of the power monitor [V] (refer to Electrical Characteristics)

• for Vdd

(1)'

(2)'

where, Vhys4 : Hysteresis voltage of the power monitor [V] (refer to Electrical Characteristics)

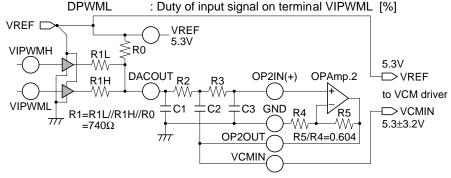

2. The relation between PWMDAC input VIPWMH, VIPWML for VCM driver current control and VCM driver input (VCMIN – VREF) is determined by following equation. (refer to below figure)

$$VCMIN - VREF = \frac{6.4}{6500} \cdot (64 \cdot DPWMH + DPWML) - 3.2$$

(3)

where, VREF : Internal reference voltage [V] (refer to Electrical Characteristics)

DPWMH : Duty of input signal on terminal VIPWMH [%]

DPWML : Duty of input signal on terminal VIPWML [%]

The 3rd order LPF at next stage of PWMDAC is characterized by internal OP amp. and capacitor C1, C2, C3 and resistor R2, R3. These components value are determined by following equations.

C1 =

$$\frac{1}{2 \cdot \pi \cdot \text{fc} \cdot \text{R1}}$$

[F] (4)

C3 =  $220 \cdot 10^{-12}$  [F] (5)

C2 =  $\frac{1}{2} \cdot \frac{4 \cdot k + 1 - \sqrt{8 \cdot k + 1}}{k^2} \cdot \text{C3}$  [F] (6)

R2 =  $\frac{k}{\sqrt{4 \cdot k + 1 - \sqrt{8 \cdot k + 1}}} \cdot \frac{\sqrt{2}}{2 \cdot \pi \cdot \text{fc} \cdot \text{C3}}$  [\Omega] (7)

R3 = R2 [\Omega] (8)

$$k = \frac{R5}{R4} = 0.604$$

(9)

where, fc : Cut off frequency of 3rd order LPF [Hz]

R1 : Output resistance of PWMDAC  $[\Omega]$  (refer to Electrical Characteristics)

4. The driving current of VCM Ivcm is determined by following equation.

$$Ivcm = \frac{Vvcmin - VREF}{R_S} \cdot Gvcm \qquad [A]$$

(10)

where, Vvcmin : Input voltage on terminal VCMIN (pin 10) [V]

Gvcm: Transfer function of VCM driver [dB] (refer to Electrical Characteristics)

5. Capacitor C108 and resistor R104 are useful to dump the gain peaking of VCM driver. These components also determine the gain band width of VCM driver BW1 which should be chosen less than 10 kHz, as follows.

$$R104 = \frac{12\pi \cdot BW1 \cdot Lvcm}{R_S} \qquad [k\Omega]$$

C108 =

$$\frac{\text{Lvcm}}{\text{R}_{\text{S}} + \text{R}_{\text{L}}} \cdot \frac{1}{\text{R104}}$$

[F] (12)

where,  $R_L$ : Coil resistance of VCM [ $\Omega$ ]

Lvcm: Coil inductance of VCM [H]

6. Retract current Iret is determined by following equation.

Iret =

$$\frac{0.7 \times \left(1 + \frac{R105}{R106}\right) - Vretsat}{R_S + R_L}$$

[A] (13)

Vretsat

: Output saturation voltage of retract driver [V] (refer to Electrical Characteristics)

7. The relation between duty of input signal on terminal SPCNTL (pin 34) and output current of spindle motor driver Ispn is as follows.

$$Ispn = \frac{Vref - Voff1}{Rnf} \cdot duty \qquad [A]$$

(14)

Vref : Reference voltage of current control amplifier [V]

Voff1: Offset voltage of current control amplifier [V] (refer to Electrical Characteristics)

8. The delay time of the power monitor for start up is as follows.

tpor =

$$140 \cdot C105$$

[ms] (15)

9. The cut off frequency fcpwm of the filter for current control input of the spindle motor is as follows.

fcpwm =

$$\frac{1}{2\pi \times 20k \cdot C103}$$

[Hz] (16)

10. To get the maximum driving efficiency for spindle motor, the capacitor C101, C102 should be chosen as following equation.

$$C101 = 0.8 \cdot C102_{(17-1)}$$

C102 =

$$\frac{\tan(\pi/6)}{2\pi \cdot 13k} \cdot \frac{1}{\text{fbemf}}$$

[F] (17-2)

fbemf: Back EMF frequency at standard rotation speed of the spindle motor [Hz]

- where, please set the value of C101, C102 so that C101 < C102 can be kept including the accuracy of the absolute value to assure the stability of motor starting and speed lock state.

- 11. To stabilize output voltage od retract driver, the capacitor C115 should be chosen as following equation. Please chose same values for C115.

C115 =

$$\frac{3 \cdot 10^{-6}}{2\pi \cdot (R105 // R106)}$$

[F] (18)

12. Time t<sub>BRKDLY</sub> of the delayed brake of V, W phase for retract is determined by resistor R109 and capacitor C112, C116 as following equation.

$$t_{BRKDLY} = -\frac{C116 \cdot R109}{1 + \frac{C116}{C112}} \cdot ln \left[ 1 - \frac{Vthb}{V_{BRK0}} \cdot \left( 1 + \frac{C116}{C112} \right) \right]$$

[s] (19)

where, Vthb : Threshold voltage that output MOS transistor of spindle motor driver is operated.

$$V_{BRK0} = Vpss - 0.7 [V]$$

Vpss : +12 V power supply for spindle motor driver

and, please select capacitor C112 and C116 that the ratio of C112/C116 is more than 3 times, because the last voltage of BRK and BRKDLY terminals falls if the value of C116 is big for C112, and effect of brake goes down.

#### **Absolute Maximum Ratings**

| Item                 | Symbol         | Rating            | Unit | Note |

|----------------------|----------------|-------------------|------|------|

| Power supply         | Vss            | 6.0               | V    | 1    |

|                      | Vpss           | 15                | V    | 2    |

|                      | Vpsv           | 15                | V    | 2    |

| Spindle current      | Ispn           | 2.0               | А    | 3    |

| VCM current          | lvcm           | 1.5               | А    | 3    |

| Input voltage        | Vin            | -0.33 to Vss +1.0 | V    | 4    |

| Power dissipation    | P <sub>T</sub> | 5.0               | W    | 5    |

| Junction temperature | Tj             | 150               | °C   | 6    |

| Storage temperature  | Tstg           | -55 to +125       | °C   |      |

Notes: 1. Operating voltage range is 4.25 V to 5.5 V. If power supply voltage exceed this operating range in actual application, the reliability of this IC can not be guaranteed.

- 2. Operating voltage range is 10.2 V to 13.8 V.

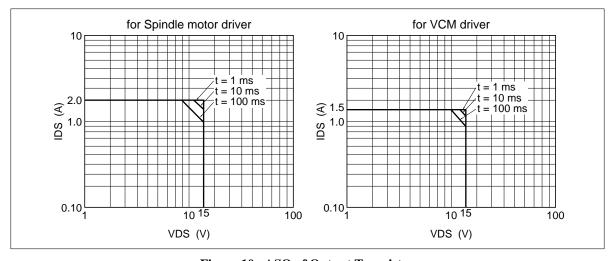

- 3. ASO (Area of Safety Operation) of each output transistor is shown in figure 10. Operating locus must be within the ASO.

- 4. Applied to CLK, COMM, SPNCTL, VIPWMH, VIPWML, SCLK, DATA and SEENAB.

- 5. Thermal resistance θj-a ≤ 30°C/W (Using 4 layer glass epoxy board)

- 6. Operating junction temperature range is 0°C to +125°C.

Figure 10 ASO of Output Transistor

# **Electrical Characteristics** (Ta = 25°C, Vss = 5 V, Vpss = Vpsv = 12 V)

| Item             |                              | Symbol | Min | Тур | Max | Unit | Test Conditions                                     | Applicable<br>Pins | Note |

|------------------|------------------------------|--------|-----|-----|-----|------|-----------------------------------------------------|--------------------|------|

| Supply cu        | Supply current               |        | _   | 2.0 | 3.4 | mA   | Stand by,<br>fclk=20MHz                             | Vss                |      |

|                  |                              | lss1   | _   | 3.2 | 4.2 | mA   | fclk=20MHz                                          |                    |      |

|                  |                              | lps0   | _   | 1.6 | 2.4 | mA   | Stand by                                            | Vpss &<br>Vpsv     | 1    |

|                  |                              | lps1   | _   | 42  | 56  | mA   |                                                     | _                  |      |

| Power switch     | Output on resistance         | Ron0   | _   | 0.2 | 0.3 | Ω    |                                                     | VpsIN<br>VpsOUT    |      |

|                  | Output<br>leacage<br>current | Icer0  | _   | _   | ±10 | μΑ   | VpsOUT=15V,<br>VpsIN=0V,<br>Vss=0V,<br>Vpss=Vpsv=0V |                    |      |

| Logic<br>input   | Input low current            | lil1   | _   | _   | ±10 | μА   | Vil=0V                                              | CLK,<br>COMM,      |      |

|                  | Input high current           | lih1   | _   | _   | ±10 | μА   | Vih1=5V                                             | SCLK,<br>DATA,     |      |

|                  | Input low voltage            | Vil1   |     |     | 0.8 | V    |                                                     | SEENAB,<br>VIPWMH, |      |

|                  | Input high voltage           | Vih1   | 2.0 |     | _   | V    |                                                     | VIPWML,<br>SPNCTL  |      |

|                  | Clock<br>frequency           | fclk   | 19  |     | 21  | MHz  |                                                     | _                  |      |

| Logic<br>output1 | Output high voltage          | Voh1   | 4.6 |     | _   | V    | loh=1mA                                             | PHASE              |      |

|                  | Output low voltage           | Vol1   | _   | _   | 0.4 | V    | Iol=2mA                                             | _                  |      |

| Logic<br>output2 | Output<br>leakage<br>current | lcer1  |     | _   | ±10 | μА   | Vo=5.5V                                             | POR,<br>12VGOOD    | 5    |

|                  | Output low voltage           | Vol2   | _   | _   | 0.4 | V    | Iol=2mA                                             | _                  |      |

**Electrical Characteristics** (Ta = 25°C, Vss = 5 V, Vpss = Vpsv = 12 V) (cont)

| Item                       |                                            | Symbol | Min | Тур | Max  | Unit  | Test Conditions          | Applicable<br>Pins        | Note |

|----------------------------|--------------------------------------------|--------|-----|-----|------|-------|--------------------------|---------------------------|------|

| Spindle<br>motor<br>driver | Output on resistance                       | Ron1   | _   | 1.2 | 1.5  | Ω     | lo≤1.5A                  | U, V, W                   | 2    |

|                            | On resistance during braking               | Ron2   | _   | _   | 3.0  | Ω     | Io=0.4A,<br>BRK=3V       | -                         |      |

|                            | Output<br>leakage<br>current               | lcer3  |     | _   | ±2   | mA    | Vo=15V                   | -                         |      |

|                            | Output clamp diode forward voltage         | Vf     |     | 0.9 | 1.2  | V     | If=0.5A                  | -                         |      |

|                            | Output MOS operating threshold voltage     | Vthb   | _   | 2   | _    | V     | Ron=(Ron/2)×10           | _                         |      |

|                            | Leakage<br>current on<br>brake<br>terminal | Icer4  | _   | _   | 0.6  | μΑ    | Vpsv=GND,<br>Vo=8V       | BRK,<br>BRKDLY            |      |

|                            | Input filter & current control amp.        | Vref2  | _   | 490 | ±10% | mV    | SPNGAIN=1,<br>SPNCTL=Vss | ISENSE,<br>FLTOUT         |      |

|                            |                                            | Vref3  | _   | 250 | ±10% | mV    | SPNGAIN=0,<br>SPNCTL=Vss |                           |      |

|                            | Current control amp. offset voltage        | Voff1  |     | -10 | ±20  | mV    | SPNCTL=GND               | -                         |      |

| B-EMF<br>amp.              | Input offset<br>voltage                    | Voff2  | _   | _   | ±20  | mV    | Synchronous drive        | U, V, W,<br>UFLT,<br>NFLT |      |

|                            |                                            | Voff3  | _   | _   | ±20  | mV    | B-EMF sens drive         | _                         |      |

|                            | Input<br>hysteresis<br>voltage             | Vhys1  | 70  | 90  | 110  | mVp-p | Synchronous drive        | _                         |      |

|                            |                                            | Vhys2  | 35  | 45  | 55   | mVp-p | B-EMF sens drive         | -                         |      |

# **Electrical Characteristics** (Ta = 25°C, Vss = 5 V, Vpss = Vpsv = 12 V) (cont)

| Item              |                                      | Symbol  | Min | Тур    | Max  | Unit | Test Conditions                                                                                                                                                                         | Applicable<br>Pins | Note |

|-------------------|--------------------------------------|---------|-----|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| VCM<br>driver     | Output on resistance                 | Ron2    | _   | 1.4    | 1.8  | Ω    | lo≤1.0A                                                                                                                                                                                 | VCMP,<br>VCMN      | 2    |

|                   | Output<br>leakage<br>current         | Icer5   |     | _      | ±2   | mA   | Vo=15V                                                                                                                                                                                  | -                  |      |

|                   | Output<br>quiescent<br>voltage       | Vq      | _   | Vpsv/2 | ±5%  | V    | $\begin{aligned} &R_{\mathrm{S}}\text{=}0.47\Omega,R_{\mathrm{L}}\text{=}10\Omega,\\ &\text{L=}2\text{mH},\\ &\text{R104=}1.6\text{M}\Omega,\\ &\text{C108=}120\text{pF} \end{aligned}$ | -                  |      |

|                   | Transfer gain                        | Gvcm    | _   | -18    | _    | dB   | -                                                                                                                                                                                       | VCMPS, Rs          | 4    |

|                   | Gain band<br>width                   | BW1     | _   | 10     |      | kHz  |                                                                                                                                                                                         |                    |      |

|                   | Input<br>resistance                  | Rin     | _   | 60     | ±30% | kΩ   | _                                                                                                                                                                                       | VCMIN              |      |

| PWM<br>DAC        | Input<br>minimum<br>pulse width      | Tpwm    | 50  | _      | _    | ns   |                                                                                                                                                                                         | VIPWMH,<br>VIPWML  |      |

|                   | Output resistance                    | R1      |     | 740    | ±30% | Ω    |                                                                                                                                                                                         | FLTOUT             |      |

|                   | Output<br>voltage                    | Vo1     |     | 0.4    | ±10% | V    | VIPWMH=High,<br>VIPWML=High                                                                                                                                                             | VCMPS, Rs          | 3    |

|                   |                                      | Vo2     | _   | 0.4    | ±10% | V    | VIPWMH=Low,<br>VIPWML=Low                                                                                                                                                               | _                  |      |

|                   | Output offset voltage                | Voff4   | _   | _      | ±10  | mV   |                                                                                                                                                                                         |                    | _    |

|                   | Gain ratio                           | Rat     | _   | 64     | ±2%  | _    | Rat=VIPWMH/<br>VIPWML                                                                                                                                                                   |                    | -    |

|                   | Reference voltage                    | Vref    | _   | 5.3    | ±5%  | V    | lo=±1mA                                                                                                                                                                                 | VREF               |      |

| Retract<br>driver | Retract driver<br>output<br>voltage  | Vretout | _   | 1.0    | ±8%  | V    | $ \begin{array}{l} \text{Vpss=6.0V,} \\ \text{R105=13k } \Omega, \\ \text{R106=33k } \Omega, \\ \text{R}_{\text{L}} = 10 \ \Omega, \ \text{R}_{\text{S}} = 0.47 \\ \Omega \end{array} $ | VCMP               |      |

|                   | VCMN output<br>saturation<br>voltage | Vretsat | 0.1 | 0.2    | 0.4  | V    | -                                                                                                                                                                                       | VCMN               | -    |

**Electrical Characteristics** (Ta = 25°C, Vss = 5 V, Vpss = Vpsv = 12 V) (cont)

| Item             |                                | Symbol | Min | Тур   | Max | Unit | Test Conditions                     | Applicable<br>Pins | Note |

|------------------|--------------------------------|--------|-----|-------|-----|------|-------------------------------------|--------------------|------|

| Power<br>monitor | Operating voltage              | Vsd1   | _   | 1.415 | ±3% | V    |                                     | LVI1, LVI2         |      |

|                  | Hysteresis                     | Vhys3  | _   | 60    | _   | mV   |                                     | LVI1               | _    |

|                  |                                | Vhys4  | _   | 30    | _   | mV   |                                     | LVI2               | _    |

|                  | Cut off voltage                | Vsd2   | 4.1 | _     | _   | V    |                                     | Vss                | _    |

|                  | Recovery voltage               | Vrec   |     | _     | 4.4 | V    |                                     | _                  |      |

|                  | POR delay time                 | tpor   | 10  | 14    | 20  | ms   | C105=0.1μF                          | POR                | _    |

| OP<br>amp.1      | Output resistance              | Rout2  |     | _     | 10  | Ω    | Shorted between OP1OUT and OP1IN(-) | OP1OUT             |      |

|                  | Output<br>maximum<br>current   | lomax1 |     | _     | ±1  | mA   | _                                   |                    |      |

|                  | Output<br>voltage<br>deviation | Vdev   |     | 1.415 | ±3% | V    | _                                   |                    |      |

|                  | Input bias current             | IB1    | _   | _     | ±10 | nA   |                                     | OP1IN(-)           |      |

|                  | Gain band width                | BW2    | _   | 1.0   | _   | MHz  |                                     | OP1OUT             | _    |

| OTSD             | Operating temperature          | Tsd    | 125 | 150   | _   | °C   |                                     |                    | 4    |

|                  | Hysteresis                     | Thys   | _   | 25    |     | °C   |                                     | _                  |      |

Note: 1. Specified by sum of supply current to Vpss and Vpsv terminal.

<sup>2.</sup> Specified by sum of saturation voltage and lower saturation voltage.

<sup>3.</sup> Specified by differential voltage on both side of  $R_s$  at shorting between DACOUT and OP2IN(+), and between OP2OUT and VCMIN, respectively.

<sup>4.</sup> Guaranteed by design.

<sup>5.</sup> The 12VGOOD terminal is open drain output type.

### **Package Dimensions**

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# IITACHI

Semiconductor & IC Div.

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

**URL** NorthAmerica http:semiconductor.hitachi.com/ Europe http://www.hitachi-eu.com/hel/ecg

http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKong) http://www.hitachi.com.hk/eng/bo/grp3/index.htm

Japan http://www.hitachi.co.ip/Sicd/indx.htm

#### For further information write to:

Hitachi Semiconductor (America) Inc. 2000 Sierra Point Parkway Brisbane, CA 94005-1897 Tel: <1> (800) 285-1601 Fax: <1> (303) 297-0447

Hitachi Europe GmbH Electronic components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany

Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00 Hitachi Europe Ltd.

Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead

Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 049318 Tel: 535-2100 Fax: 535-1533

Hitachi Asia Ltd. Taipei Branch Office 3F. Hung Kuo Building, No.167 Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180

Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong

Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.