# HFC - S2M ISDN PRI

# ISDN HDLC FIFO controller with Primary Rate Interface

preliminary edition: March 2001

Copyright 1994-2001 Cologne Chip AG All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights. Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

# **Revision History**

| Date                                    | Remarks                                                                           |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Mar. 2001                               | Information added to section: Register description, register bit description.     |  |  |  |

| Oct. 2000                               | Information added to section: Features, block diagram, register bit description.  |  |  |  |

| Feb. 2000                               | Sections added: Register array description, Correspondency between FIFOs,         |  |  |  |

|                                         | CHANNELs and SLOTs, Subchannel processing, PCM interface function, Resets,        |  |  |  |

|                                         | EEPROM, RAM accesses.                                                             |  |  |  |

|                                         | Information added to section: Register description, register bit description.     |  |  |  |

| Nov. 1999                               | Register descriptions added for: CONF_EN, F0_CNT_L, F0_CNT_H register.            |  |  |  |

| Sep. 1999 Section added: Register list. |                                                                                   |  |  |  |

|                                         | Information added to section: Features, PCI buffer signaling and power supply     |  |  |  |

|                                         | environment, PCI access description, register description, FIFO channel operation |  |  |  |

|                                         | receive channels, FIFO reset, FIFO size setup tables, register bit description.   |  |  |  |

| May 1999                                | Added: Multiparty audio conferences description, SLOT_DATA / CONFER register      |  |  |  |

|                                         | bit description.                                                                  |  |  |  |

|                                         | Changes made on: HFC-S2M block diagram, figure of CON_HDLC register bits          |  |  |  |

|                                         | 75 function, SLOT_SEL register bit description.                                   |  |  |  |

| Apr. 1999                               | preliminary edition                                                               |  |  |  |

Cologne Chip AG Eintrachtstrasse 113 D-50668 Köln Germany

Tel.: +49 (0) 221 / 91 24-0 Fax: +49 (0) 221 / 91 24-100 http://www.CologneChip.com http://www.CologneChip.de info@CologneChip.com

# **Contents**

| Features |                                                   | 5  |

|----------|---------------------------------------------------|----|

| 1 Gener  | al descriptional                                  | 6  |

|          | lications                                         |    |

|          | mode description.                                 |    |

| 1.2.1    | ISA Plug and Play mode                            |    |

| 1.2.2    | Processor interface modes                         |    |

| 1.2.3    | PCI mode                                          |    |

| 1.2.4    | PCMCIA mode                                       |    |

| 2 Functi | ional description                                 | q  |

|          | Plug and Play mode                                |    |

| 2.1.1    | ISA-PC bus interface                              |    |

| 2.1.2    | IRQ assignment                                    |    |

| 2.1.3    | ISA Plug and Play control registers               |    |

| 2.1.3.1  |                                                   |    |

| 2.1.3.2  | <u> </u>                                          |    |

| 2.1.4    | ISA Plug and Play configuration registers         |    |

| 2.1.4.1  | e                                                 |    |

| 2.1.4.2  |                                                   |    |

| 2.1.5    | Writing the Plug and Play configuration EEPROM    |    |

|          | cessor mode                                       |    |

|          | interface                                         |    |

| 2.3.1    | PCI access types used by HFC-S2M                  |    |

| 2.3.2    | PCI modes supported                               |    |

| 2.3.3    | PCI buffer signaling and power supply environment |    |

| 2.3.4    | PCI configuration registers                       |    |

| 2.4 PCI  | access description                                |    |

| 2.5 PCN  | MCIA mode                                         | 20 |

| 2.5.1    | Internal HFC-S2M register selection               | 20 |

| 2.5.2    | Attribute memory                                  | 20 |

| 2.5.3    | PCMCIA registers                                  | 20 |

| 2.5.4    | CIS programming                                   | 21 |

| 2.6 Inte | rnal HFC-S2M register description                 | 22 |

| 2.6.1    | Register array description                        | 22 |

| 2.6.2    | FIFO registers                                    | 24 |

| 2.6.3    | Registers of the S2M section                      | 25 |

| 2.6.4    | Registers of the PCM bus section                  | 26 |

| 2.6.5    | Interrupt, status and control registers           | 27 |

| 2.6.6    | Register Reference List                           | 28 |

| 2.7 Tim  | er / watchdog                                     | 30 |

| 2.8 FIF  | Os                                                | 31 |

| 2.8.1    | FIFO channel operation.                           | 32 |

| 2.8.1.1  | ,                                                 |    |

| 2.8.1.2  | i i                                               |    |

| 2.8.1.3  | FIFO full condition in send channels              | 33 |

# preliminary data sheet

| 2.8.1.4                             | Receive Channels (B1, B2 and D receive)                         | 34 |  |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------------|----|--|--|--|--|--|

| 2.8.1.5                             | FIFO full condition in receive channels                         | 35 |  |  |  |  |  |

| 2.8.1.6                             | FIFO reset                                                      | 36 |  |  |  |  |  |

| 2.8.2                               | Transparent mode of HFC-S2M                                     | 36 |  |  |  |  |  |

| 2.8.3                               | FIFO size setup                                                 | 37 |  |  |  |  |  |

| 2.8.3.1                             | 32k x 8 external RAM                                            | 37 |  |  |  |  |  |

| 2.8.3.2                             | 128k x 8 external RAM                                           | 38 |  |  |  |  |  |

| 2.8.3.3                             |                                                                 |    |  |  |  |  |  |

| 2.9 Corr                            | espondency between FIFOs, CHANNELs and SLOTs                    | 40 |  |  |  |  |  |

|                                     | ubchannel Processing                                            |    |  |  |  |  |  |

|                                     | CM Interface Function                                           |    |  |  |  |  |  |

|                                     | Sultiparty audio conferences                                    |    |  |  |  |  |  |

|                                     | esets                                                           |    |  |  |  |  |  |

|                                     | EPROM                                                           |    |  |  |  |  |  |

| 2.15 R.                             | AM accesses                                                     | 47 |  |  |  |  |  |

| 3 Registe                           | er bit description                                              | 45 |  |  |  |  |  |

|                                     | ster bit description of interrupt, status and control registers |    |  |  |  |  |  |

| •                                   | ster bit description of PCM bus section                         |    |  |  |  |  |  |

| $\mathcal{C}$                       | ster bit description of S2M section                             |    |  |  |  |  |  |

| C                                   | •                                                               |    |  |  |  |  |  |

|                                     | structure                                                       |    |  |  |  |  |  |

|                                     | cation of bits 1 to 8 of the frame                              |    |  |  |  |  |  |

| 4.2 CRC                             | 2-4 multiframe structure                                        | 72 |  |  |  |  |  |

| Figures Figure 1: HF                | C-S2M block diagram                                             | 6  |  |  |  |  |  |

|                                     | C-S2M in I/O address mapped mode                                |    |  |  |  |  |  |

|                                     | C-S2M in memory address mapped mode                             |    |  |  |  |  |  |

|                                     | O Organisation (shown for B-channel, similar for D-channel)     |    |  |  |  |  |  |

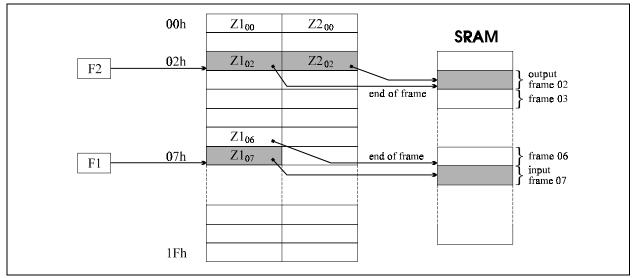

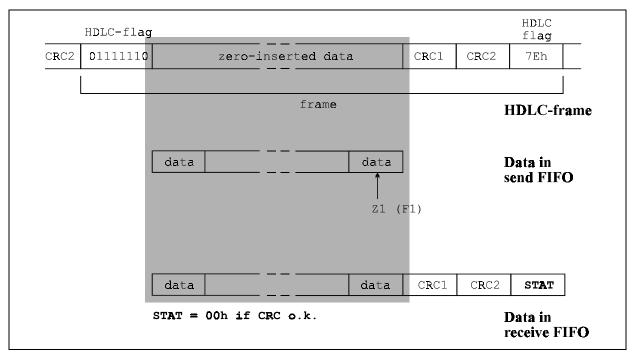

| Figure 5: FIF                       | FO Data Organisation                                            | 34 |  |  |  |  |  |

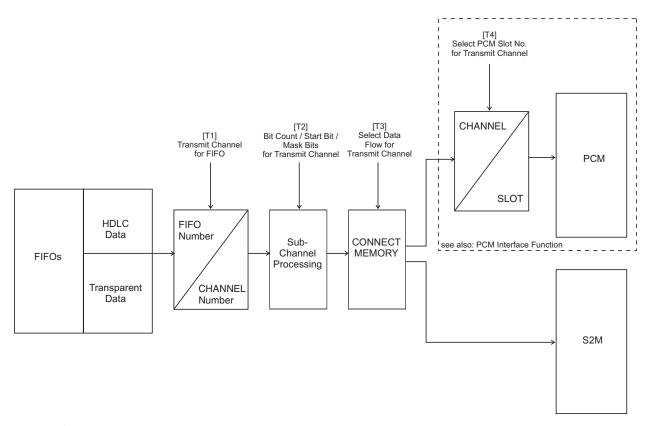

| Figure 6: FIF                       | FOs, CHANNELs and SLOTs in Transmit Direction                   | 41 |  |  |  |  |  |

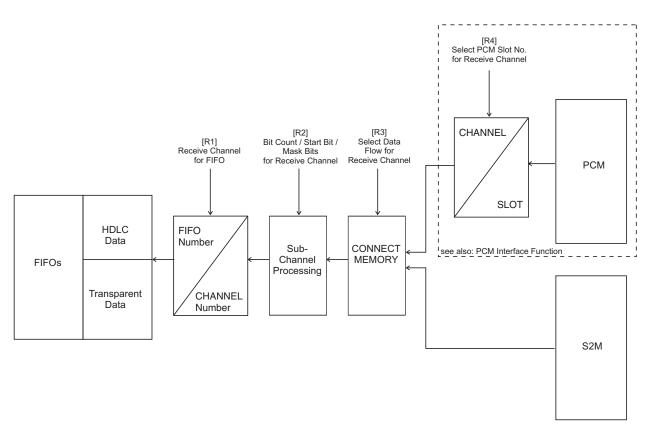

| Figure 7: FIF                       | FOs, CHANNELs and SLOTs in Receive Direction                    | 42 |  |  |  |  |  |

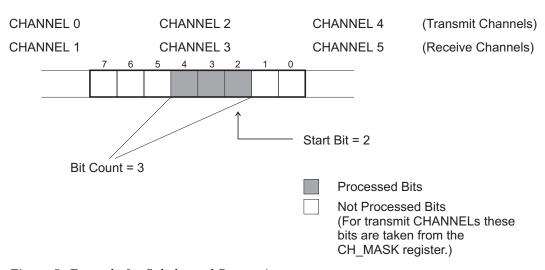

| Figure 8: Exa                       | ample for Subchannel Processing                                 | 43 |  |  |  |  |  |

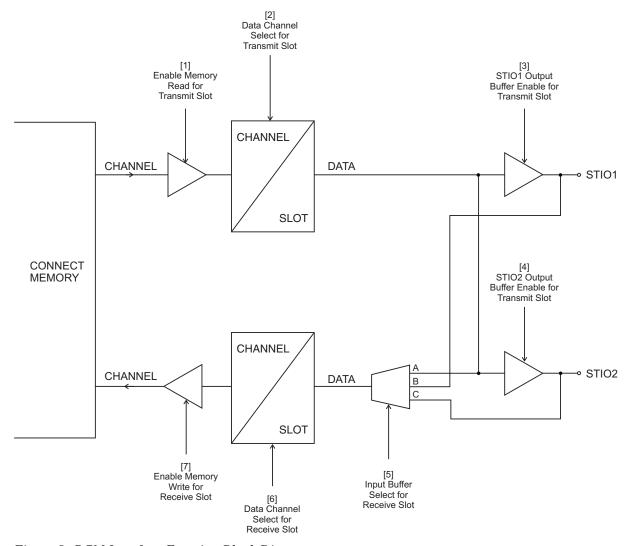

| Figure 9: PC                        | M Interface Function Block Diagram                              | 44 |  |  |  |  |  |

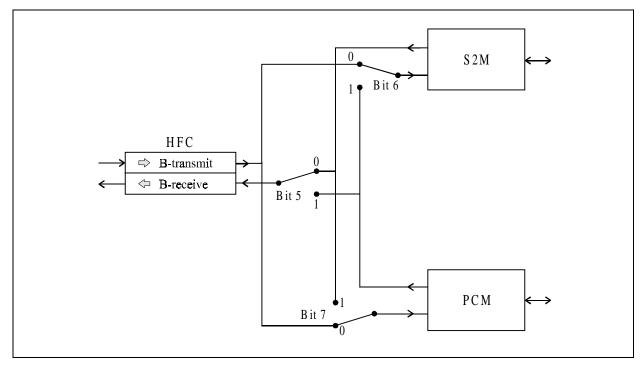

|                                     | unction of CON_HDLC register bits 75                            |    |  |  |  |  |  |

| Figure 11: Co                       | onfiguring CODEC enable signal shapes                           | 63 |  |  |  |  |  |

|                                     |                                                                 |    |  |  |  |  |  |

| Tables                              |                                                                 |    |  |  |  |  |  |

| LUDICS                              |                                                                 |    |  |  |  |  |  |

|                                     | mode selection                                                  |    |  |  |  |  |  |

|                                     | command types                                                   |    |  |  |  |  |  |

|                                     | configuration registers' initial values                         |    |  |  |  |  |  |

|                                     | ets of the HFC-S2M                                              |    |  |  |  |  |  |

|                                     | ocation of bits 1 to 8 of the frame                             |    |  |  |  |  |  |

| Table 6: CRC-4 multiframe structure |                                                                 |    |  |  |  |  |  |

# **Features**

| 9 | single chip ISDN-S2M-controller with B- and D-channel HDLC support                                                              |

|---|---------------------------------------------------------------------------------------------------------------------------------|

| O | integrated S2M interface                                                                                                        |

| O | full I.431 ITU E1/T1 ISDN support in TE and NT mode for 3V - 5V power supply                                                    |

| O | 32 independent read and write HDLC-channels                                                                                     |

|   | for e.g. 30 ISDN B-channels, 1 ISDN D-channel and 1 timeslot on the PCM interface                                               |

| O | B-channel transparent mode independently selectable                                                                             |

| O | up to 64 FIFOs; FIFO-sizes configurable                                                                                         |

| O | each FIFO can be assigned to an arbitrary channel of the S2M or PCM interface                                                   |

| O | max. 31 HDLC frames (with 128k or 512k RAM) and 15 HDLC frames (with 32k RAM)                                                   |

|   | per FIFO                                                                                                                        |

| O | 1 - 8 bit processing for subchannels selectable                                                                                 |

| O | B-channels for higher data rate combinable                                                                                      |

| O | $PCM128  /  PCM64  /  PCM30 \ interface \ configurable \ to \ interface \ MITEL \ ST^{\tiny TM} \ bus \ (MVIP^{\tiny TM}) \ or$ |

|   | Siemens IOM2™ and Motorola GCI™ (bearer slots supported only) for inter chip connection                                         |

|   | (e.g. external CODECs)                                                                                                          |

| O | H.100 data rate supported                                                                                                       |

| O | integrated ISA Plug and Play interface with buffers for ISA-databus                                                             |

| O | integrated PCMCIA interface                                                                                                     |

| O | integrated PCI bus interface (Spec. 2.2) for $3.3V$ and $5V$ bus signals (PCI power management                                  |

|   | supported)                                                                                                                      |

| O | microprocessor interface compatible to Motorala bus and Siemens/Intel bus                                                       |

| O | multiparty audio conferences switchable                                                                                         |

| O | DTMF detection on all B-channels                                                                                                |

| O | Timer and watchdog with interrupt capability                                                                                    |

| O | CMOS technology 3V-5V                                                                                                           |

| O | PQFP 144 case                                                                                                                   |

March 2001 5 of 72

# 1 General description

The HFC-S2M is an ISDN S2M HDLC primary rate controller for all kind of PRI equipment, such like high performance ISDN PC cards, ISDN PABX, ISDN LAN routers, ISDN least cost routers as well as ISDN test equipment. It has an integrated universal bus interface which can be configured into PCI bus, ISA Plug and Play, PCMCIA or microprocessor interface. A PCM128 / PCM64 / PCM30 interface for CODEC or inter chip connection is also integrated.

The very deep FIFOs of the HFC-S2M are realized with an external SRAM.

#### 1.1 Applications

- O ISDN PRI terminal adapters

- O ISDN PABX for PRI

- O ISDN LAN routers for PRI

- O ISDN least cost routers for PRI

- O ISDN test equipment for PRI

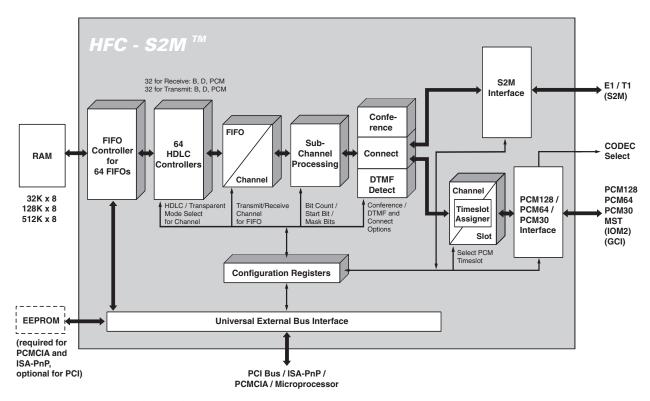

Figure 1: HFC-S2M block diagram

#### 1.2 Bus mode description

The HFC-S2M has an integrated universal external bus interface which can be configured into ISA-PnP, PCI bus, PCMCIA and microprocessor interface.

| BMODE1 | BMODE0 | Bus type          |

|--------|--------|-------------------|

| 0      | 0      | PCI bus           |

| 0      | 1      | Processor mode    |

| 1      | 0      | ISA Plug and Play |

| 1      | 1      | PCMCIA            |

Table 1: Bus mode selection

#### 1.2.1 ISA Plug and Play mode

In ISA PnP mode the HFC-S2M is addressed by eight successive port addresses on the ISA-PC bus. The port address is selected by the lines SA0 - SA15.

The address with SA2='1' is for register selection and the address with SA2='0' is used for data read/write (see also: 2.1).

#### 1.2.2 Processor interface modes

The HFC-S2M has 3 different microprocessor modes:

CPU-Mode 1: Motorola bus with control signals /CS, R/W, /DS

CPU-Mode 2: Siemens/Intel bus with seperated address bus and databus and control signals /CS, /WR, /RD

CPU-Mode 3: Intel bus with multiplexed address and databus with control signals /CS, /WR, /RD, ALE. ALE latches the address. The address lines SA0-SA7 must be connected to the data lines BD0-BD7.

The lines SA0-SA7 are used for direct addressing the internal registers of the HFC-S2M (see also 2.2).

#### **1.2.3 PCI** mode

In PCI mode the HFC-S2M is accessed by PCI bus target mode accesses (see also: 2.3).

March 2001 7 of 72

## 1.2.4 PCMCIA mode

In PCMCIA mode the HFC-S2M is addressed by eight successive port addresses. The port address is selected by the lines SA0 - SA11.

The address with SA2='1' is for register selection and the address with SA2='0' is used for data read/write (see also: 2.5).

# 2 Functional description

The HFC-S2M has an integrated universal external bus interface which can be configured into ISA PnP, PCI bus, PCMCIA and microprocessor interface. The following sections show how to use the HFC-S2M in the different interface modes.

## 2.1 ISA Plug and Play mode

ISA Plug and Play mode is selected by BMODE1=1 and BMODE0=0. The HFC-S2M needs eight consecutive addresses in the I/O map of a PC for operation. Usually also one IRQ line is used. The following section describes how to configure the interrupts of the HFC-S2M.

#### 2.1.1 ISA-PC bus interface

In ISA Plug and Play mode 16 bits SA0 - SA15 are decoded by the address decoder.

| SA2 | /IOR | /IOW | /AEN | Operation     |

|-----|------|------|------|---------------|

| X   | X    | X    | 1    | no access     |

| X   | 1    | 1    | X    | no access     |

| 0   | 0    | 1    | 0    | read data     |

| 0   | 1    | 0    | 0    | write data    |

| 1   | 0    | 1    | 0    | read status   |

| 1   | 1    | 0    | 0    | write control |

X = don't care

The HFC-S2M has no memory or DMA access to any component on the ISA-PC bus.

Because of its power drive characteristic it needs no external driver for the ISA-PC bus data lines.

If necessary an external bus driver can be added. In this case the output BUSDIR determines the driver direction.

BUSDIR = 1 means that data is driven into the HFC-S2M;

BUSDIR = 0 means that the HFC-S2M is read and data is driven to the external bus.

March 2001 9 of 72

# 2.1.2 IRQ assignment

The IRQ lines are disabled after a hardware reset.

The IRQ assigned by the PnP BIOS can be read from register CHIP\_ID (16h), bits [3:0]. Bits [2:0] of the CIRM register have to be set according to the hardware wiring on the PCB and the IRQ number assigned by the PnP BIOS.

## 2.1.3 ISA Plug and Play control registers

#### 2.1.3.1 Card level control regsisters

| Plug and Play control register | Read<br>Write | Accessable in state | Description                                                                                              |

|--------------------------------|---------------|---------------------|----------------------------------------------------------------------------------------------------------|

| address                        |               |                     |                                                                                                          |

| 00h                            | W             | Isolation state     | Set read data port address register. Bits[7:0]                                                           |

|                                |               | Config state *)     | become bits[9:2] of the port's I/O address. Bits[11:10]                                                  |

|                                |               |                     | are hardwired to 00b and bits[1:0] are hardwired to                                                      |

|                                |               |                     | 11b.                                                                                                     |

| 01h                            | r             | Isolation state     | <b>Serial isolation register</b> . Used to read the serial identifier during the card isolation process. |

| 02h                            | W             | Sleep state,        | Configuration control register. Bits[7:3] are                                                            |

|                                |               | Isolation state,    | reserved and must be zero. The defined bits are:                                                         |

|                                |               | Config state        | 0 <b>Reset Bit</b> . When set to one, resets all of the                                                  |

|                                |               | _                   | card's configuration registers to their default                                                          |

|                                |               |                     | state. The CSN is not affected.                                                                          |

|                                |               |                     | 1 Return to wait for key state. When set to one,                                                         |

|                                |               |                     | all cards return to wait for key state.                                                                  |

|                                |               |                     | Their CSNs and configuration registers are not                                                           |

|                                |               |                     | affected. This command is issued after all cards                                                         |

|                                |               |                     | have been configured and activated.                                                                      |

|                                |               |                     | 2 <b>Reset CSN to zero</b> . When set to one, all cards                                                  |

|                                |               |                     | reset their CSN to zero.                                                                                 |

|                                |               |                     | All bits are automatically cleared by the hardware.                                                      |

| Plug and Play control register | <u>R</u> ead<br>Write | Accessable in state                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address                        |                       |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 03h                            | W                     | Sleep state,<br>Isolation state,<br>Config state | <ul> <li>Wake command register. Writing a CSN to this register has the following effects:</li> <li>If the value written is 00h, all cards in the sleep state with a CSN=00h go to the isolation state. Any card in configure state (CSN not 00h) goes to the sleep state.</li> <li>If the value written is not 00h, any card in the sleep state with a matching CSN goes to configure state. Any card in the isolation state goes to sleep state.</li> <li>Any write to a card's wake command register with a match on its CSN causes the pointer to the serial identifier / resource data to be reset to the first byte of</li> </ul> |

|                                |                       |                                                  | the serial identifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

<sup>\*)</sup> This is an extension to the Plug and Play Specification

| Plug and Play<br>control register | Read<br>Write | Accessable in state                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------|---------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04h                               | r             | Config state                                    | Resource data register. This register is used to read the device's recource data. Each time that a read is performed from this register a byte of the resource data is returned and the resource data pointer is incremented. Prior to reading each byte, the programmer must read from the status register to determine if the next byte is available for reading from the resource data register.  The card's serial identifier and checksum must be read prior to accessing the resource requirement list via this register. |

| 05h                               | r             | Config state                                    | <b>Status register.</b> Prior to reading the next byte of the device's resource data, the programmer must read from this register and check bit 0 for a one. This is the resource data byte available bit. Bits[7:1] are reserved.                                                                                                                                                                                                                                                                                              |

| 06h                               | r/w           | Isolation state <sup>*)</sup> ,<br>Config state | Card select number (CSN) register. The configuration software uses the CSN register to assign a unique ID to the card. The CSN is then used to wake up the card's configuration logic whenever the configuration program must access its configuration registers.                                                                                                                                                                                                                                                               |

March 2001 11 of 72

| Plug and Play<br>control register<br>address | Read<br>Write | Accessable in state | Description                                                                                                                                                                                                               |

|----------------------------------------------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07h                                          | r             | C                   | <b>Logical device number register.</b> The number in this register points to the logical device the next commands will operate on. The HFC-S2M only supports one logical device. This register is hardwired to all zeros. |

<sup>\*)</sup> only if the isolation process is finished; the last card remains in isolation state until a CSN is assigned.

# 2.1.3.2 Logical device control registers

| Plug and Play control register | <u>R</u> ead<br>Write | Accessable in state | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|-----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address                        | <u>**</u> 11tc        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30h                            | r/w                   | Config state        | Activate register. Setting bit 0 to a one activates the card on the ISA bus. When cleared, the card cannot respond to any ISA bus transactions (other than accesses to its Plug and Play configuration ports). Reset clears bit 0. Bits[7:1] are reserved and return zeros when read. The HFC-S2M only supports one logical device, so it is not necessary to write the logical device number into the card's logical device number register prior to writing to this register.                  |

| 31h                            | r/w                   | Config state        | I/O range check register.  Bit(s) Description  7:2 Reserved, return zero when read  1 When set to one, enables I/O range checking and disables it when cleared to zero. When enabled, bit 0 is used to select a pattern for the logical device to return.  This bit is only valid if the logical device is deactivated (see Activate register).  0 When set, the logical device returns 55h in response to any read from the logical device's assigned I/O space. When cleared, AAh is returned. |

## 2.1.4 ISA Plug and Play configuration registers

#### 2.1.4.1 I/O port configuration registers

| Plug and Play    | Read          | Accessable in state | Description                            |

|------------------|---------------|---------------------|----------------------------------------|

| configuration    | <u>W</u> rite |                     |                                        |

| register address |               |                     |                                        |

| 60h              | r/w           | Config state        | I/O decoder 0 base address upper byte. |

|                  |               |                     | I/O port base address bits[15:8].      |

| 61h              | r/w           | Config state        | I/O decoder 0 base address lower byte. |

|                  |               |                     | I/O port base address bits[7:0].       |

## 2.1.4.2 Interrupt configuration registers

| Plug and Play                  | Read          | Accessable in state | Description                                |  |  |

|--------------------------------|---------------|---------------------|--------------------------------------------|--|--|

| configuration register address | <u>W</u> rite |                     |                                            |  |  |

| 70h                            | r/w           | Config state        | IRQ select configuration register 0.       |  |  |

|                                |               |                     | Bits[3:0] specify the sleceted IRQ number. |  |  |

|                                |               |                     | Bits[7:4] are reserved.                    |  |  |

| 71h                            | r/w           | Config state        | IRQ type configuration register 0.         |  |  |

|                                |               |                     | Bits[1:0] are ignored.                     |  |  |

|                                |               |                     | Bits[7:2] are reserved.                    |  |  |

#### d important!

All registers not implemented return 00h when read except the DMA configuration registers 74h and 75h. These two registers return 04h when read. This means no DMA channel has been selected.

#### 2.1.5 Writing the Plug and Play configuration EEPROM

The EEPROM Writing Spec. is only available on special request to avoid destruction of configuration information by not authorized programs or software viruses.

March 2001 13 of 72

#### 2.2 Processor mode

Processor mode is selected by BMODE1=0 and BMODE0=1.

In the microprocessor mode the HFC-S2M uses 256 I/O addresses (SA0 - SA7).

| /IOR<br>/DS | /IOW<br>R/W | /CS | ALE      | Operation  | CPU-Mode |

|-------------|-------------|-----|----------|------------|----------|

| X           | X           | 1   | X        | no access  | all      |

| 1           | 1           | X   | X        | no access  | all      |

| 0           | 1           | 0   | 1        | read data  | 1        |

| 0           | 0           | 0   | 1        | write data | 1        |

| 0           | 1           | 0   | 0        | read data  | 2        |

| 1           | 0           | 0   | 0        | write data | 2        |

| 0           | 1           | 0   | $0_{*)}$ | read data  | 3        |

| 1           | 0           | 0   | $0^{*)}$ | write data | 3        |

X = don't care

All registers are directly accessable by their I/O address (see register description).

Except in CPU-mode 3 ALE is assumed to be stable after a RESET.

The HFC-S2M has 3 different microprocessor modes:

CPU-Mode 1: Motorola bus with control signals /CS, R/W, /DS

CPU-Mode 2: Siemens/Intel bus with seperated address bus and databus and control signals /CS, /WR, /RD

CPU-Mode 3: Intel bus with multiplexed address and databus with control signals /CS, /WR, /RD, ALE. ALE latches the address. The address lines SA0-SA7 must be connected to the data lines BD0-BD7.

The lines SA0-SA7 are used for direct addressing the internal registers of the HFC-S2M (see also 2.2).

<sup>\*) 1-</sup>pulse latches register address.

#### 2.3 PCI interface

PCI mode is selected by BMODE1=0 and BMODE0=0.

#### 2.3.1 PCI access types used by HFC-S2M

| C/BE3# | C/BE2# | C/BE1# | C/BE0# | <b>Command Type</b> | HFC-S2M mode |

|--------|--------|--------|--------|---------------------|--------------|

| 0      | 0      | 1      | 0      | I/O Read            | target mode  |

| 0      | 0      | 1      | 1      | I/O Write           | target mode  |

| 0      | 1      | 1      | 0      | Memory Read         | target mode  |

| 1      | 1      | 0      | 0      | Memory Read         | target mode  |

|        |        |        |        | Multiple            |              |

| 1      | 1      | 1      | 0      | Memory Read Line    | target mode  |

| 0      | 1      | 1      | 1      | Memory Write        | target mode  |

| 1      | 1      | 1      | 1      | Memory Write and    | target mode  |

|        |        |        |        | Invalidate          |              |

| 1      | 0      | 1      | 0      | Configuration Read  | target mode  |

| 1      | 0      | 1      | 1      | Configuration Write | target mode  |

Table 2: PCI command types

Memory Read Line and Memory Read Multiple commands are aliased to Memory Read. Memory Write and Invalidate is aliased to Memory Write.

#### 2.3.2 PCI modes supported

The HFC-S2M only supports target mode PCI accesses.

#### 2.3.3 PCI buffer signaling and power supply environment

The HFC-S2M supports 5V and 3.3V PCI bus environments. The environment mode is set during RESET (RST# low) by the input value of /V\_SEL (see also: CHIP\_ID register bit decription).

| PCI bus<br>power and signaling<br>environment | /V_SEL<br>during RST# low |

|-----------------------------------------------|---------------------------|

| 3.3V                                          | high *)                   |

| 5V                                            | low                       |

<sup>\*)</sup> external pull-up resistor required (10k)

March 2001 15 of 72

# 2.3.4 PCI configuration registers

| 3        | 2                | 1 0              |                    | Hex Address |  |  |  |

|----------|------------------|------------------|--------------------|-------------|--|--|--|

| Devi     | ce ID            | Vend             | lor ID             | 00h         |  |  |  |

| Status I | Register         | Command          | d Register         | 04h         |  |  |  |

|          | Class Code       |                  | Revision<br>ID     | 08h         |  |  |  |

| BIST     | Header<br>Type   | Latency<br>Timer | Cache Line<br>Size | 0Ch         |  |  |  |

|          | I/O Base Address |                  |                    |             |  |  |  |

|          | Memory Ba        | se Address       |                    | 14h         |  |  |  |

|          | Base Ad          | ddress 2         |                    | 18h         |  |  |  |

|          | Base Address 3   |                  |                    |             |  |  |  |

|          | Base Ad          | ddress 4         |                    | 20h         |  |  |  |

|          | Base Ad          | ddress 5         |                    | 24h         |  |  |  |

|          | CardBus C        | CIS Pointer      |                    | 28h         |  |  |  |

| Subsy    | stem ID          | Subsysten        | n Vendor ID        | 2Ch         |  |  |  |

| Ex       | pansion RON      | /I Base Addre    | ess                | 30h         |  |  |  |

|          | Reserved         |                  | Cap_Ptr            | 34h         |  |  |  |

|          | Reserved         |                  |                    |             |  |  |  |

| Max_Lat  | Min_Gnt          | Interrupt<br>Pin | Interrupt<br>Line  | 3Ch         |  |  |  |

| PI       | лС               | Next Item<br>Ptr | Cap_ID             | 40h         |  |  |  |

| Data     | PMCSR<br>BSE     | PMC              | CSR                | 44h         |  |  |  |

Register is implemented, value can be read from EEPROM

Register is implemented

Register is not implemented and returns all 0's when read

The external EEPROM is optional. If no EEPROM is available, EE\_SCL/EN must be connected to GND. Without EEPROM the PCI configuration registers will be loaded with the default values shown in Table 3.

All registers which can be read from EEPROM can also be written by configuration write accesses. The addresses for configuration write are shown in the table below.

| Register Name       | Default Value | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|---------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Vendor ID           | 1397h         | Value can be read from EEPROM. Base address for                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | configuration write is C0h.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Device ID           | 30BDh         | configuration write is C0h.  Value can be read from EEPROM. Base address for configuration write is C0h.  Bits Function  0 Enables/disables I/O space accesses.  1 Enables/disables memory space accesses.  52 fixed to '0'  6 PERR# enable/disable  7 fixed to '0'  8 SERR# enable/disable  159 fixed to '0'  Bits[7:0] can be read from EEPROM. Base address for configuration write is C4h.  Bits Function  30 reserved  4 fixed to '1'  5 66MHz capable  6 User definable features supported |  |  |  |

|                     |               | configuration write is C0h.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Command Register    |               | Bits Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                     |               | 0 Enables/disables I/O space accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                     |               | 7 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | 7 fixed to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Status Register     | 0210h         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | 7 fast Back-to-Back capable                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                     |               | 8 data parity error detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                     |               | 109 fixed to '01': timing of DEVSEL# is medium                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                     |               | signaled target abort (fixed to '0')                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                     |               | 1312 fixed to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                     |               | signaled system error (Addr. parity error)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| D ID                | 011           | 15 detected partity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Revision ID         | 01h           | HFC-S2M Revision 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Class Code          | 02 80 00h     | Value can be read from EEPROM. Base address for                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| II. 1 m             | 001           | configuration write is C8h.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Header Type         | 00h           | Header Type 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| BIST                | 00h           | No build in self test supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| I/O Base Address    |               | Bits[31:3] are r/w by configuration accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Memory Base Address | 100-          | Bits[31:8] are r/w by configuration accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Subsystem Vendor ID | 1397h         | Value can be read from EEPROM. Base address for                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | configuration write is ECh.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Subsystem ID        | 30BDh         | Value can be read from EEPROM. Base address for                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     |               | configuration write is ECh.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Cap_Ptr             | 40h           | Offset to Power Management register block.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Interrupt Line      | FFh           | This register must be configured by configuration write.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Interrupt Pin       | 01h           | INTA supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

March 2001 17 of 72

| Register Name | Default Value | Remarks                                                                 |  |  |  |

|---------------|---------------|-------------------------------------------------------------------------|--|--|--|

| Cap_ID        | 01h           | Capability ID. 01h identifies the linked list item as PCI               |  |  |  |

|               |               | Power Management registers. There are no next items in the linked list. |  |  |  |

| Next Ptr      | 00h           | There are no next items in the linked list.                             |  |  |  |

| PMC           | 7E21h         | Power Management Capabilities. See also PCI Bus                         |  |  |  |

|               |               | Power Management Interface Specification. This                          |  |  |  |

|               |               | register's value can be read from EEPROM. Base                          |  |  |  |

|               |               | address for configuration write is E0h.                                 |  |  |  |

|               |               | <b>PME</b> # can be asserted from D0, D1, D2 and D3 <sub>hot</sub> .    |  |  |  |

|               |               | Device specific initialisation is required.                             |  |  |  |

|               |               | The HFC-S2M does not require PCI-clock to generate                      |  |  |  |

|               |               | PME#.                                                                   |  |  |  |

|               |               | This function complies with the PCI Power                               |  |  |  |

|               |               | Management Spec. Version 1.0.                                           |  |  |  |

| PMCSR         | 0000h         | Power Management Control/Status                                         |  |  |  |

|               |               | Bits Function                                                           |  |  |  |

|               |               | PME_Status - This bit is set when the function                          |  |  |  |

|               |               | would normally assert the <b>PME</b> # signal                           |  |  |  |

|               |               | independent of the state of the <b>PME_En</b> bit.                      |  |  |  |

|               |               | Writing a '1' to this bit will clear it and cause                       |  |  |  |

|               |               | the function to stop asserting a PME# (if                               |  |  |  |

|               |               | enabled).                                                               |  |  |  |

|               |               | Writing a '0' has no effect.                                            |  |  |  |

|               |               | 149 fixed to '0'                                                        |  |  |  |

|               |               | 8 <b>PME_En</b> - A '1' enables the function to assert                  |  |  |  |

|               |               | PME#.                                                                   |  |  |  |

|               |               | When '0', <b>PME</b> # assertion is disabled.                           |  |  |  |

|               |               | 72 fixed to '0'                                                         |  |  |  |

|               |               | 10 <b>PowerState</b> - This 2-bit field is used both to                 |  |  |  |

|               |               | determine the current power state of a function                         |  |  |  |

|               |               | and to set the function into a new power state.                         |  |  |  |

|               |               | 00b - <b>D0</b>                                                         |  |  |  |

|               |               | 01b - <b>D1</b>                                                         |  |  |  |

|               |               | 10b - <b>D2</b>                                                         |  |  |  |

|               |               | 11b - <b>D3</b> <sub>hot</sub>                                          |  |  |  |

Table 3: PCI configuration registers' initial values

Unimplemented registers return all 0's when read.

### 2.4 PCI access description

If the HFC-S2M is used in memory mapped mode all register can directly be accessed by adding their CIP address to the configured Memory Base Address.

In I/O address mapped mode the HFC-S2M occupies 8 bytes in the I/O address space. Byte 0 is for data read/write, byte 4 for register selection. The AUX-port address is selected by byte 3, AUX-port data is read/written by byte 1.

|               | Byte 3 | Byte 2 | Byte 1 | Byte 0             |

|---------------|--------|--------|--------|--------------------|

| I/O-Address   | DATA 3 | DATA 2 | DATA 1 | DATA 0             |

|               | Byte 7 | Byte 6 | Byte 5 | Byte 4             |

| I/O-Address+4 |        |        |        | Register<br>Select |

Figure 2: HFC-S2M in I/O address mapped mode

|                    | Byte 3 | Byte 2 | Byte 1 | Byte 0 |

|--------------------|--------|--------|--------|--------|

| Memory-<br>Address | DATA 3 | DATA 2 | DATA 1 | DATA 0 |

Figure 3: HFC-S2M in memory address mapped mode

March 2001 19 of 72

#### 2.5 PCMCIA mode

#### 2.5.1 Internal HFC-S2M register selection

The HFC-S2M occupies eight consecutive addresses in the I/O map. The base I/O address must be 8 byte aligned so the lower of both addresses is the one with SA2 = 0 and the higher address is the one with SA2 = 1. The lines SA3 to SA15 are don't care. The registers of the HFC-S2M are selected by writing the registers' address to the higher I/O address (SA2=1). Registers are read/written by reading/writing the base I/O address (SA2=0).

#### 2.5.2 Attribute memory

After hardware reset the card's information structure (CIS) is copied from the EEPROM to even numbered addresses of the SRAM starting with 0000h (512 byte are occupied for the CIS). To avoid accesses in this phase the /WAIT signal is active.

#### 2.5.3 PCMCIA registers

#### **Configuration Option Register (COR):**

#### Register address: 400h in Configuration Memory

| D7     | D6      | D5                  | D4 | D3 | D2 | D1 | D0 |

|--------|---------|---------------------|----|----|----|----|----|

| SRESET | LevIREQ | Configuration Index |    |    |    |    |    |

|        | 1       |                     |    |    |    |    |    |

The fields are as follows:

| SRESET              | SRESET card. Setting this bit to one places the card in the reset state. This bit |

|---------------------|-----------------------------------------------------------------------------------|

|                     | must be cleared to zero by the user.                                              |

| LevIREQ             | This bit is not implemented and returns always 1 when read to indicate usage of   |

|                     | level mode interrupts.                                                            |

| Configuration Index | Configuration Index.                                                              |

|                     | Bit 0 must be set to 1 to enable I/O accesses to the HFC-S2M.                     |

|                     | Bit 5 must be set to 1 to write data to the EEPROM.                               |

# Card Configuration and Status Register (CSR): Register address: 402h in Configuration Memory

| D7      | D6     | D5    | D4   | D3    | D2     | D1   | D0   |

|---------|--------|-------|------|-------|--------|------|------|

| Changed | SigChg | IOis8 | Rsvd | Audio | PwrDwn | Intr | Rsvd |

| 0       | 0      | 1     | 0    | 0     | 0      |      | 0    |

The fields are as follows:

| Changed | Unimplemented and return 0 when read.                                |

|---------|----------------------------------------------------------------------|

| SigChg  |                                                                      |

| Rsvd    |                                                                      |

| Audio   |                                                                      |

| PwrDwn  |                                                                      |

| IOis8   | Unimplemented and return 1 when read to indicate an 8 bit data path. |

| Intr    | Internal state of interrupt request (IREQ).                          |

# 2.5.4 CIS programming

The EEPROM Programming Spec. is only available on special request to avoid destruction of configuration information by not authorized programs or software viruses.

March 2001 21 of 72

#### 2.6 Internal HFC-S2M register description

In ISA Plug and Play mode, PCI mode and PCMCIA mode all registers are selected by writing the register address into the Control Internal Pointer (CIP) register. This is done by writing the HFC-S2M on the higher I/O address (SA2 = 1).

All consecutive read or write data accesses (SA2 = 0) are done with the selected register until the CIP register is changed.

In processor mode all internal registers can be directly accessed. The registers are selected by SA0 - SA7. In PCI mode SA0 and SA1 are generated from the byte enable lines.

#### 2.6.1 Register array description

As you will see in the register list on the following pages some registers are listed like follows:

REGISTER\_NAME [INDEX\_REGISTER\_NAME]

e.g.: FIF\_DATA [FIFO#]

This means that the register with the name REGISTER\_NAME is available n times (register array). For example: The HFC-S2M can handle up to 64 FIFOs so each of the FIFO control/configuration registers is available 64 times. 6 registers are required to control one FIFO. Additionally there are 6 registers for configuration. The register FIFO# indexes 1 of 64 blocks of 12 registers for the desired FIFO.

REGISTER NAME [INDEX REGISTER NAME]

REGISTER\_NAME is the name of the register to access

INDEX\_REGISTER\_NAME is the name of the index register which makes the corresponding register for REGISTER\_NAME accessible.

| Index Register Name | Depending Registers |

|---------------------|---------------------|

| FIFO#               | FIF_DATA            |

|                     | FIF_F1              |

|                     | FIF_F2              |

|                     | FIF_Z1H             |

|                     | FIF_Z1L             |

|                     | FIF_Z2H             |

|                     | FIF_Z2L             |

|                     | CH_MASK             |

|                     | CON_HDLC            |

|                     | HDLC_PAR            |

|                     | CHANNEL#            |

|                     | F_SEQ               |

|                     | INT_MASK            |

| SLOT#               | CONFER              |

|                     | SLOT_CFG            |

#### **Examples:**

To access register HDLC\_PAR for FIFO number 12 do the following:

- 1) write 12 to register FIFO# (register address is 0Fh)

- 2) register HDLC\_PAR can be read/written (register address is FBh)

To access register SLOT\_CFG for PCM time slot 20 do the following:

- 1) write 20 to register SLOT# (register address is 10h)

- 2) register SLOT\_CFG can be read/written (register address is D0h)

March 2001 23 of 72

#### 2.6.2 FIFO registers

The FIFO control registers are used to select and control the FIFOs of the HFC-S2M. The FIFO register selection is independent of the B- or D-channel FIFO number. The FIFO is selected by the FIFO select register (FIFO#).