## Processing Signals At Increased Sample Rates With Multiple HSP45116's

Technical Brief April 1998 TB315.1

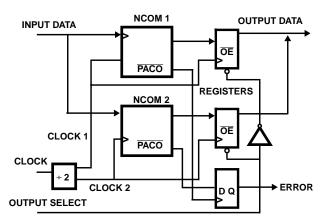

It is possible to generate signals with sample rates higher than the rated speed of the HSP45116 Numerically Controlled Oscillator/Modulator by using two parts. Each NCOM is clocked at half the sample rate of the signal to be generated, and the frequency of each is set to half the desired frequency. The phase register of one NCOM is then set to offset the phase of its output by one half of a sample period. The vector inputs and outputs of the two parts are then multiplexed together to form a signal at twice the frequency that would normally be possible; see Figure 1.

FIGURE 1. CIRCUIT BLOCK DIAGRAM

The value to be put into the phase register is one half of the sum of the center and offset frequency registers. This means that the phase offset between the two NCOMs is limited to the 16 bit resolution of the phase register, which limits the frequency resolution of the complete circuit to 15 bits.

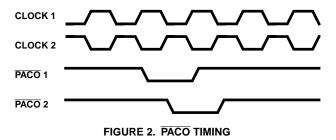

The proper operation of this circuit can be verified by observing the  $\overline{PACO}$  outputs of the two NCOMs. Since  $\overline{PACO}$  is the inverted output of the phase accumulator and the phase offset is added to the output of the phase accumulator register, the alignment of the  $\overline{PACO}$  pulses out of the two parts will not be affected by phase offsets (see HSP45116 Data Sheet, Figure 1). The timing of the  $\overline{PACO}$  pulses is shown in Figure 2. The flip flop connected to the  $\overline{PACO}$  outputs of NCOM 1 and NCOM 2 as shown in Figure 1 will detect an error in this alignment. Note that the only causes for  $\overline{PACO}$  misalignment are improper configuration of the NCOMs or circuit noise which is severe enough to cause the parts to false trigger. Should the error signal go active, there will most likely be a problem with the entire circuit.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## Sales Office Headquarters

**NORTH AMERICA**

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 734 7000

TEL: (407) 724-7000 FAX: (407) 724-7240 **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 **ASIA**

Intersil (Taiwan) Ltd.

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029