# SK70704/SK70707 or SK70708

1168 Kbps HSDL Data Pump Chip Set

## **Datasheet**

The HDSL Data Pump is a chip set consisting of the following two devices:

- SK70704 Analog Core Chip (ACC)

- SK70707 (68-pin PLCC) or SK70708 (44-pin PLCC) HDSL Digital Transceiver (HDX)

The HDSL Data Pump is a 2-wire transceiver which provides echo-cancelling and 2B1Q line coding. It incorporates transmit pulse shaping, filtering, line drivers, receive equalization, timing and data recovery to provide 1168 kbps, clear-channel, "data pipe" transmission. The Data Pump provides Near-End Cross-Talk (NEXT) performance in excess of that required over all ETSI test loops. Typical transmission range on 0.4 mm cable exceeds 3.6 km in a noise-free environment or 2.8 km with a 0 dB margin over  $10\,\mu\text{V}/\sqrt{\text{Hz}}$  ETSI noise.

The Data Pump meets the requirements of ETSI ETR-152. It provides one end of a single-channel HDSL transmission system from the twisted pair interface back to the Data Pump/HDSL data interface. The Data Pump can be used at either the NTU or the LTU end of the interface.

# **Applications**

- E1 (2-pair) and fractional E1 transport

- N-channel digital pair-gain

- Wireless base station to switch interface

- Campus and private networking

- High-Speed digital modems

# **Product Features**

- Fully integrated, 2-chip set for interfacing to 2-wire HDSL lines at 1168 kbps

- Single +5 V supply

- Integrated line drivers, filters and hybrid circuits result in greatly reduced external logic and simplified support circuitry requirements

- Simple line interface circuitry, via transformer coupling, to twisted pair line

- Internal ACC voltage reference

- Integrated VCO circuitry

- Converts serial binary data to scrambled 2B1Q encoded data

- Self-contained activation/start-up state machine for simplified single loop designs

- Programmable for either line termination (LTU) or network termination (NTU) applications

- Compliant with ETSI ETR-152 (1995)

- Compliant with ITU G.991.1

- Design allows for operation in either Software Control or stand alone Hardware Control mode

- Typical power consumption less than 1.2 W allowing remote power feeding for repeater and NTU equipment

- Input or Output Reference Clock of 18.688 MHz

- Digital representation of receive signal level and noise margin values available for SNR controlled activation

Order Number: 249193-001

January 2001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SK70704/SK70707 or SK70708 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0          | Pin A                                         | Assignments and Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0          | Fund                                          | etional Description19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

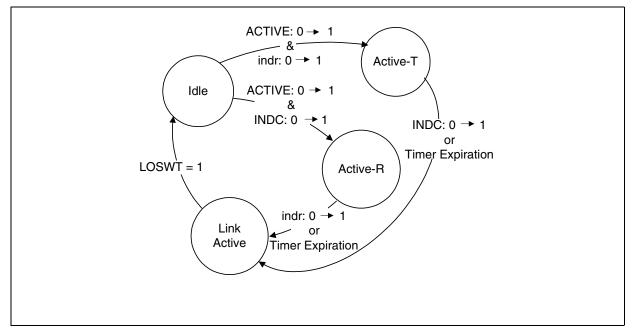

|              | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Transmit       15         Receive       15         Control       15         ACC and HDX Overview       15         2.4.1 Analog Core Chip (ACC)       15         2.4.2 HDSL Digital Transceiver (HDX)       16         2.4.3 HDX/ACC Interface       17         Line Interface       17         HDSL Data Interface       18         Microprocessor Interface (HDX)       20         2.7.1 Control Pins       20         2.7.2 Register Access       22         2.7.3 Registers       22         Activation State Machines       25         2.8.1 LTU Data Pump Activation       29         2.8.2 LTU Framer Activation       30         2.8.3 NTU Data Pump Activation       30         2.8.4 NTU Framer Activation       30         2.8.5 HDSL Synchronization State Machine       30          2.8.5 HDSL Synchronization State Machine       30          3.5       30 |

| 3.0          | App                                           | ication Information3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | 3.1<br>3.2                                    | HDSL Framer State Machine Design 37 PCB Layout 37 3.2.1 User Interface 37 3.2.2 Digital Section 38 3.2.3 Analog Section 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.0          | Test                                          | Specifications44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.0          |                                               | nanical Specifications5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <del>-</del> |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Figures 1

**Tables**

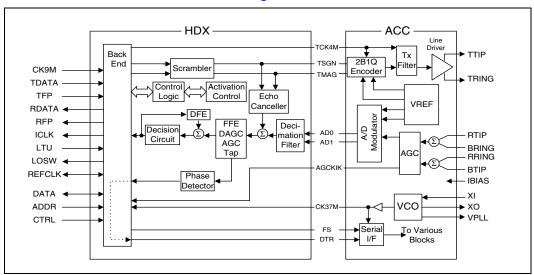

| 1  | SK/0/04/SK/0/0/ or SK/0/08 Block Diagram                             |     |

|----|----------------------------------------------------------------------|-----|

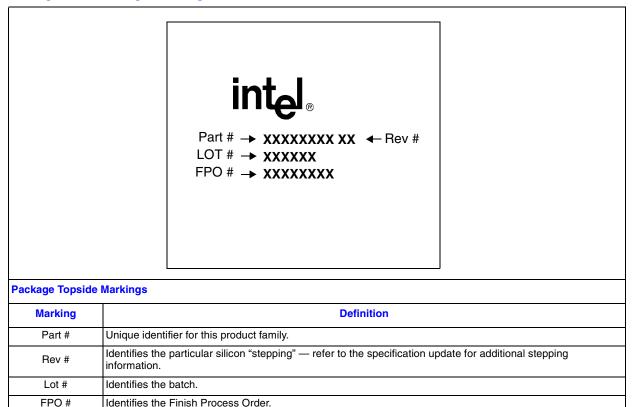

| 2  | Package Markings                                                     | 7   |

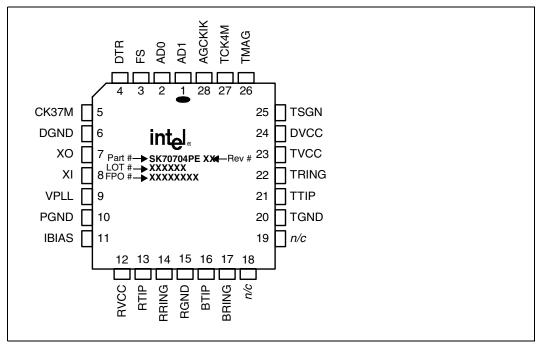

| 3  | SK70704 ACC Pin Locations                                            | 8   |

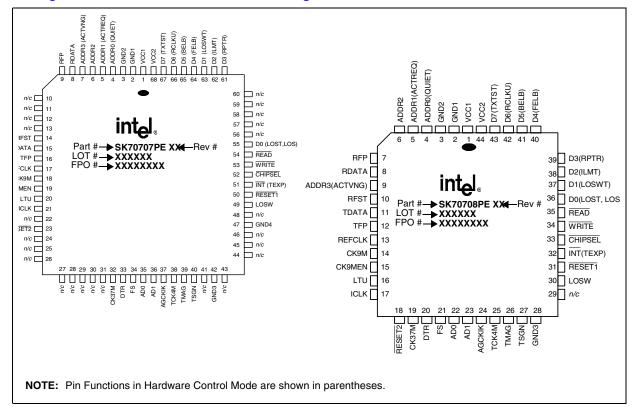

| 4  | SK70707/SK70708 HDX Pin Assignments                                  | 9   |

| 5  | HDX/ACC Interface – Relative Timing                                  |     |

| 6  | HDX/ACC Framer Interface – Relative Timing                           |     |

| 7  | Model for HDSL Data Pump and HDSL Framer Applications                |     |

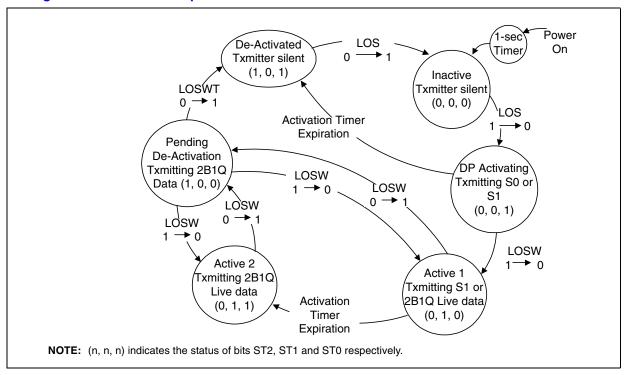

| 8  | LTU Data Pump Activation State Machine                               |     |

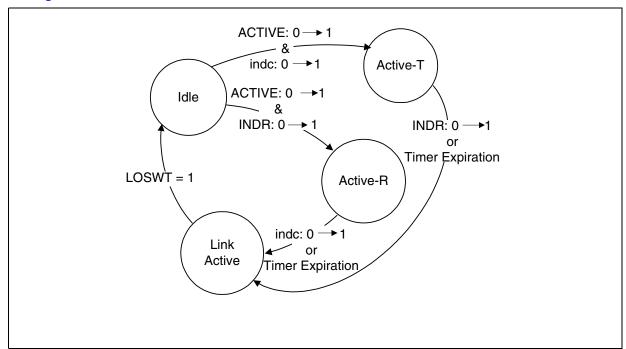

| 9  | LTU HDSL Framer Activation State Machine                             |     |

| 10 | NTU Data Pump Activation State Machine                               |     |

| 11 | NTU HDSL Framer Activation State Machine                             |     |

| 12 |                                                                      |     |

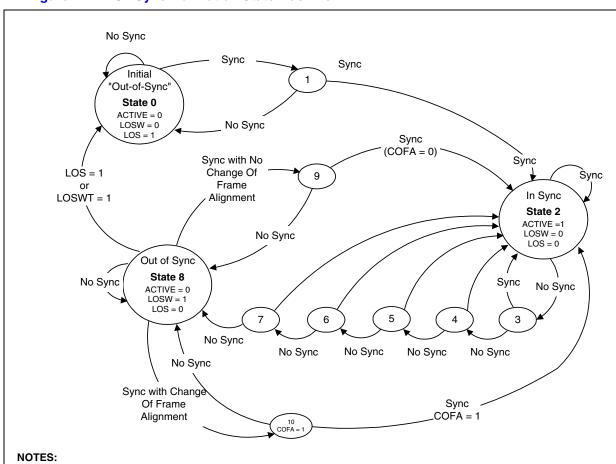

|    | HDSL Synchronization State Machine                                   |     |

| 13 | PCB Layout Guidelines                                                |     |

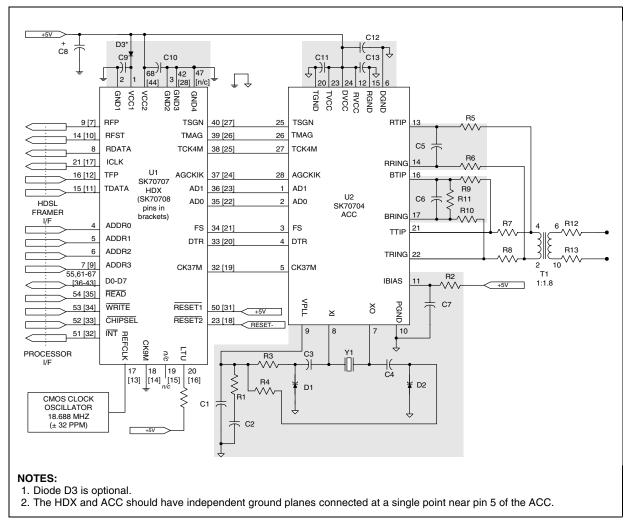

| 14 | Typical Support Circuitry for LTU Applications                       |     |

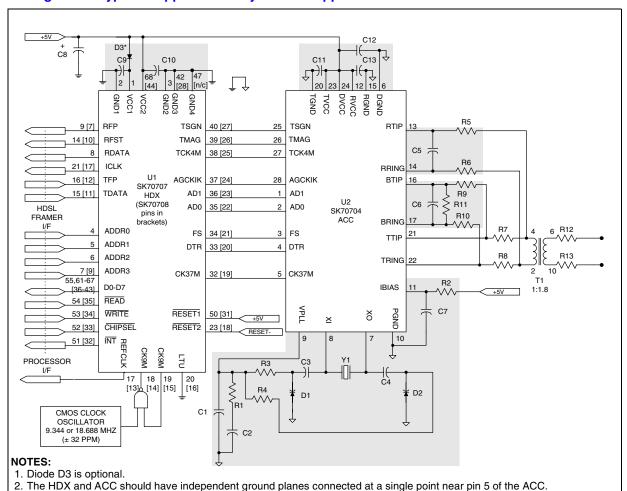

| 15 | Typical Support Circuitry for NTU Applications                       |     |

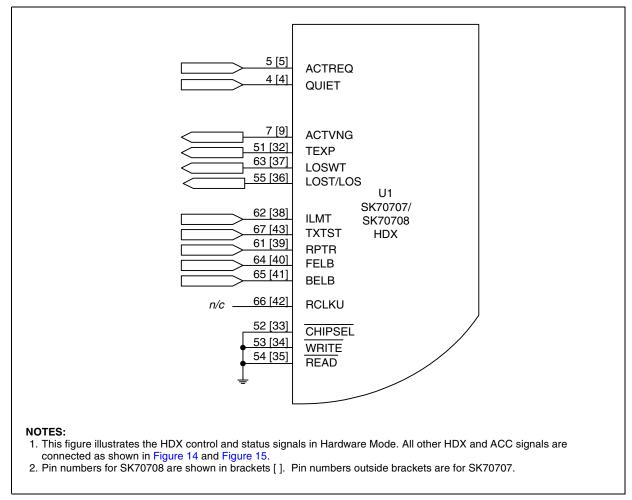

| 16 | SK70707/SK70708 HDX Control and Status Signals (Hardware Mode)       | 43  |

| 17 | ACC Normalized Pulse Amplitude Transmit Template                     |     |

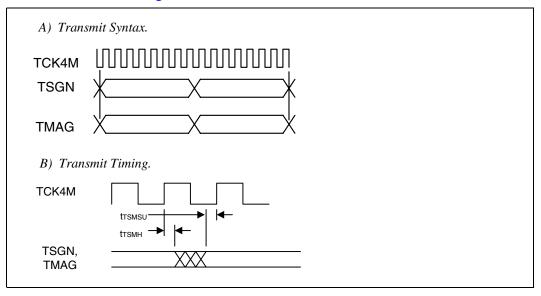

| 18 | ACC Transmitter Timing                                               |     |

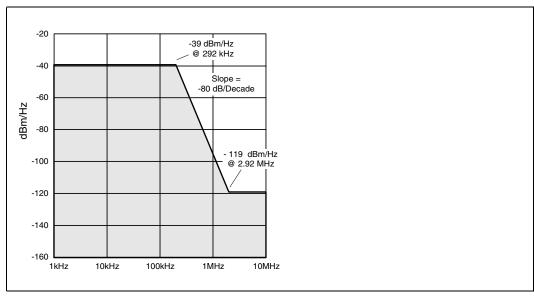

| 19 | Upper Bound of Transmit Power Spectral Density                       |     |

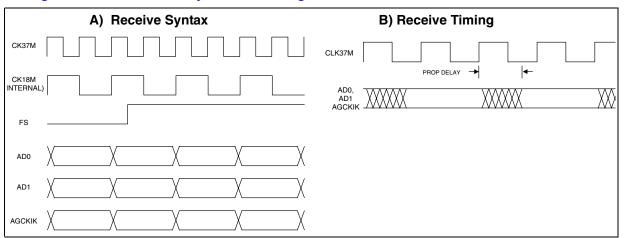

| 20 | ACC Receiver Syntax and Timing                                       | 47  |

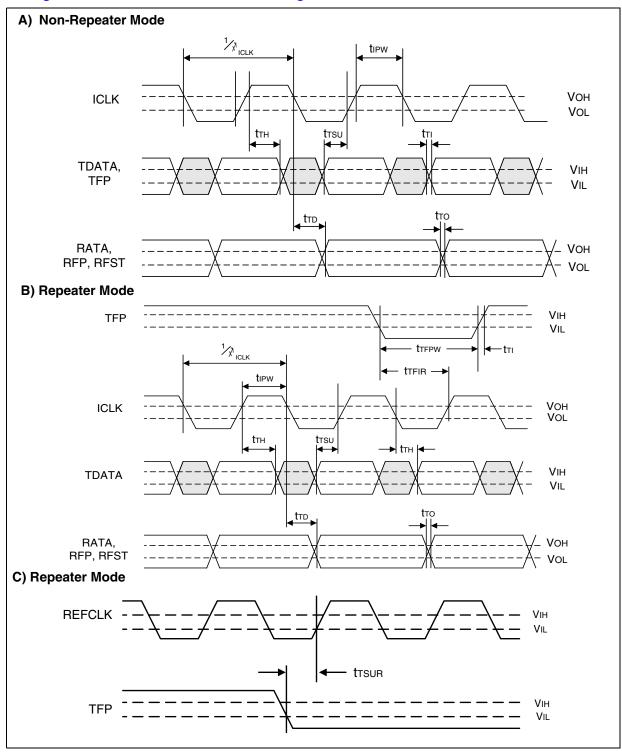

| 21 | HDX/HDSL Data Interface Timing                                       | 49  |

| 22 | Reset and Interrupt Timing (mP Control Mode)                         | 51  |

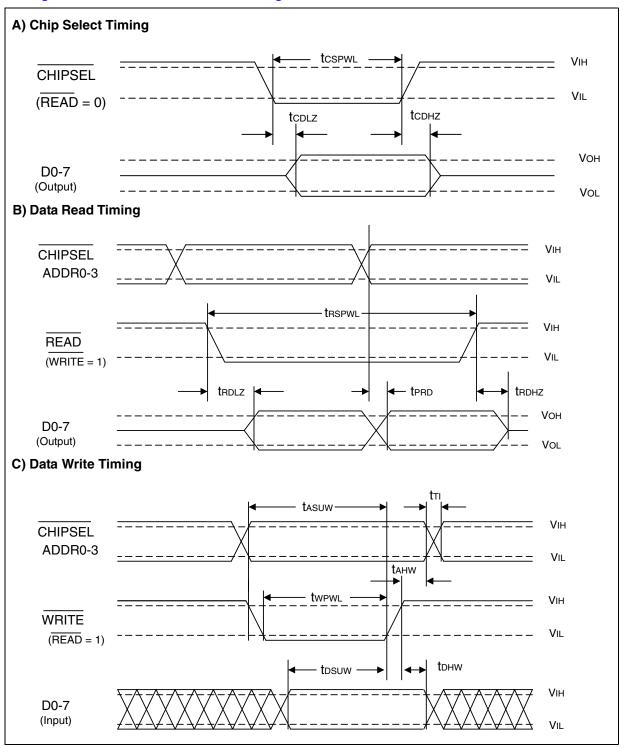

| 23 | Parallel Data Channel Timing                                         | 52  |

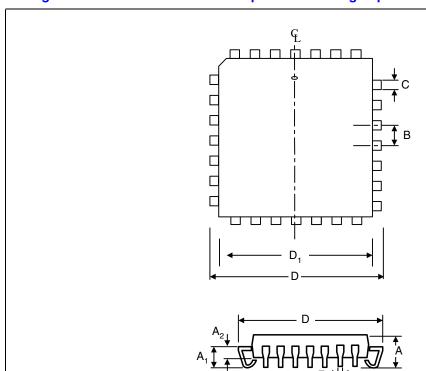

| 24 | ACC Plastic Leaded Chip Carrier Package Specifications               | 53  |

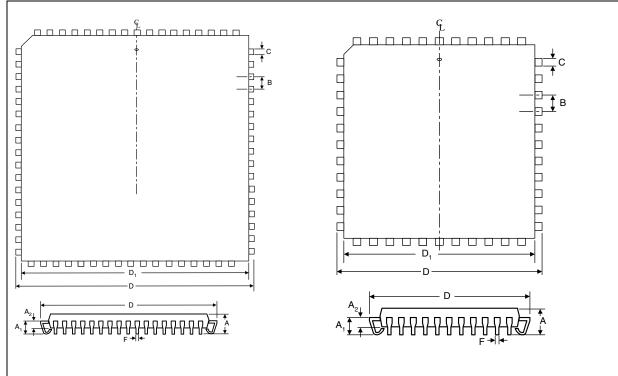

| 25 | HDX Plastic Leaded Chip Carrier Package Specifications               | 54  |

|    |                                                                      |     |

|    |                                                                      |     |

|    |                                                                      |     |

| 4  | CK70704 ACC Bin Assignments/Circus Bosseintions                      | 0   |

| 1  | SK70704 ACC Pin Assignments/Signal Descriptions                      |     |

| 2  | SK70707/SK70708 HDX Pin Assignments/Signal Descriptions              |     |

| 3  | ACC Transmit Control                                                 |     |

| 4  | HDX/ACC Serial Port Word Bit Definitions ( Figure 5)                 |     |

| 5  | HDSL Framer TDATA Requirements                                       |     |

| 6  | Register Summary                                                     |     |

| 7  | Main Control Register WR0                                            |     |

| 8  | Interrupt Mask Register WR2                                          | 24  |

| 9  | Read Coefficient Select Register WR3                                 | 25  |

| 10 | Main Status Register RD0                                             | 25  |

| 11 | Receiver Gain Word Register                                          | 26  |

| 12 | Noise Margin Register RD2                                            |     |

|    | Noise Margin Coding126                                               |     |

| 13 | Coefficient Read Register                                            | 28  |

| 14 | Activation Status Register RD5                                       |     |

| 15 | Receiver AGC and FFE Step Gain Register RD6                          |     |

| 16 | Data Pump/Framer Activation State Machine Correspondences            |     |

| 17 | Activation – Synchronization                                         |     |

| 18 | Components for Suggested Circuitry (Figure 14 and Figure 15)         |     |

|    |                                                                      | 411 |

| 10 | , , , , , , , , , , , , , , , , , , , ,                              | 40  |

| 19 | Transformer Specifications (Figure 14 and Figure 15, Reference T1)41 | 40  |

# 1168 Kbps HSDL Data Pump Chip Set — SK70704/SK70707 or SK70708

| 20 | Crystal Specifications                                                       |           |

|----|------------------------------------------------------------------------------|-----------|

|    | (Figure 14 and Figure 15, Reference Y1)41                                    |           |

| 21 | ACC Absolute Maximum Ratings                                                 | 44        |

| 22 | ACC Recommended Operating Conditions                                         | 44        |

| 23 | ACC DC Electrical Characteristics (Over Recommended Range)                   | 44        |

| 24 | ACC Transmitter Electrical Parameters (Over Recommended Range)               | 45        |

| 25 | ACC Receiver Electrical Parameters (Over Recommended Range)                  | 46        |

| 26 | HDX Absolute Maximum Ratings                                                 | 47        |

| 27 | HDX Recommended Operating Conditions                                         | 47        |

| 28 | HDX DC Electrical Characteristics (Over Recommended Range)                   | 48        |

| 29 | HDX/HDSL Data Interface Timing (Figure 21)                                   | 48        |

| 30 | HDX/Microprocessor Interface Timing Specifications1 (Figure 22 and Figure 50 | ure 23) . |

| 31 | General System and Hardware Mode Timing                                      | 50        |

# **Revision History**

| Revision | Date | Description |

|----------|------|-------------|

|          |      |             |

|          |      |             |

|          |      |             |

Figure 1. SK70704/SK70707 or SK70708 Block Diagram

Figure 2. Package Markings

# 1.0 Pin Assignments and Signal Description

The ACC is packaged in a 28-pin PLCC. Figure 3 shows the ACC pin locations. Table 1 lists signal descriptions for each pin, except pins 18 and 19 which are not connected.

The HDX is available in two packages: 68-pin PLCC (SK70707) and 44-pin PLCC (SK70708). Figure 4 shows the HDX pin assignments. Table 2 lists signal descriptions for each pin, corresponding to the specific package.

Figure 3. SK70704 ACC Pin Locations

| Package Topside Markings |                                                                                                                       |  |  |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Marking Definition       |                                                                                                                       |  |  |  |  |  |  |  |

| Part #                   | Unique identifier for this product family.                                                                            |  |  |  |  |  |  |  |

| Rev #                    | Identifies the particular silicon "stepping" — refer to the specification update for additional stepping information. |  |  |  |  |  |  |  |

| Lot #                    | Identifies the batch.                                                                                                 |  |  |  |  |  |  |  |

| FPO #                    | FPO # Identifies the Finish Process Order.                                                                            |  |  |  |  |  |  |  |

Figure 4. SK70707/SK70708 HDX Pin Assignments

Table 1. SK70704 ACC Pin Assignments/Signal Descriptions

| Group                            | Pin #                 | Symbol | I/O | Description                                                                         |  |

|----------------------------------|-----------------------|--------|-----|-------------------------------------------------------------------------------------|--|

|                                  | 13                    | RTIP   | I   | Receive Tip and Ring. Connected these input pins to the line transformer per        |  |

| 14 RRING I network requirements. | network requirements. |        |     |                                                                                     |  |

| Line                             | 16                    | BTIP   | I   | Bias Tip and Ring. Inputs provide a bias setting for the receiver. Provide balanced |  |

| Line                             | 17                    | BRING  | I   | network inputs.                                                                     |  |

|                                  | 21                    | TTIP   | 0   | Transmit Tip and Ring. Line driver outputs.                                         |  |

|                                  | 22                    | TRING  | 0   | Transmit Tip and Timg. Line driver outputs.                                         |  |

|                                  | 7                     | XO     | 0   | Crystal Oscillator. Connect a 37.376 MHz crystal across these two pins.             |  |

| PLL                              | 8                     | ΧI     | I   | Crystal Oscillator. Conflict a 37.370 for 12 crystal across these two pins.         |  |

|                                  | 9                     | VPLL   | 0   | PLL Voltage Control. Supplies control voltage to the VCO.                           |  |

# SK70704/SK70707 or SK70708 — 1168 Kbps HSDL Data Pump Chip Set

Table 1. SK70704 ACC Pin Assignments/Signal Descriptions (Continued)

| Group           | Pin # | Symbol | I/O | Description                                                                                                 |

|-----------------|-------|--------|-----|-------------------------------------------------------------------------------------------------------------|

|                 | 10    | PGND   | I   | PLL Ground. 0 V.                                                                                            |

|                 | 12    | RVCC   | I   | Power supply. + 5 V (± 5%).                                                                                 |

|                 | 23    | TVCC   | I   | Power supply. + 5V (± 5%).                                                                                  |

| Power           | 24    | DVCC   | I   | Digital Power Supply. +5 V (± 5%).                                                                          |

|                 | 6     | DGND   | I   | DVCC Ground. 0V.                                                                                            |

|                 | 15    | RGND   | I   | RVCC Ground. 0V.                                                                                            |

|                 | 20    | TGND   | I   | TVCC Ground. 0V.                                                                                            |

|                 | 3     | FS     | I   | 584 kHz clock. Input from HDX FS.                                                                           |

| Clock and       | 4     | DTR    | I   | Serial control data. Input from the HDX at 18.688 Mbps.                                                     |

| Control         | 5     | CK37M  | 0   | <b>37.376 MHz HDSL Reference Clock.</b> Used as the receive timing reference for the HDX. Tie to HDX CK37M. |

|                 | 27    | TCK4M  | I   | 4.672 MHz Clock. Input from HDX TCK4M.                                                                      |

|                 | 28    | AGCKIK | 0   | AGC adjust signal. Output to HDX AGCKIK.                                                                    |

| Data Input      | 1     | AD1    | 0   | A-to-D converter data line 1. Connect to HDX AD1.                                                           |

| and             | 2     | AD0    | 0   | A-to-D converter data line 0. Connect to HDX AD0.                                                           |

| Output          | 25    | TSGN   | I   | Transmit quat sign. Input from HDX.                                                                         |

|                 | 26    | TMAG   | I   | Transmit quat magnitude. Input from HDX.                                                                    |

| Analog<br>Input | 11    | IBIAS  | I   | Input BIAS. Provides input bias current.                                                                    |

SK70707/SK70708 HDX Pin Assignments/Signal Descriptions

| Group     | 707<br>Pin # | 708<br>Pin # | Symbol | I/O                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----------|--------------|--------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | 14           | 10           | RFST   | 0                   | Receive Frame and Stuff Bit Indicator. Goes High for 18 consecutive ICLK periods to indicate four stuffing bits (b7007 - 7010) and 14 frame bits (b1-14) on RDATA.                                                                                                                                                                                                                                                               |  |

|           | 17           | 13           | REFCLK | I <sup>1</sup><br>O | <b>18.688 MHz HDSL Reference Clock.</b> In LTU Mode, this clock generates transmit and receive timing and must have ±32 ppm accuracy. In NTU Mode, this output is derived by dividing CK37M by two.                                                                                                                                                                                                                              |  |

|           | 20           | 16           | LTU    | I                   | Operation Mode Select. When LTU is High, the Data Pump operates in LTU mode; when LTU is Low, the Data Pump operates in NTU mode. Tied to internal pull-up device.                                                                                                                                                                                                                                                               |  |

|           | 21           | 17           | ICLK   | 0                   | Bit Rate Clock. Nominally 1168 kHz, REFCLK is the source of ICLK in LTU Mode. CK37M is the source of ICLK in NTU Mode.                                                                                                                                                                                                                                                                                                           |  |

|           | 49           | 30           | LOSW   | 0                   | Loss of Sync Word Indicator. Normally Low in Active States, goes High to indicate receipt of six consecutive mismatched frame synch words. LOSW is logic High in all states except Active States.                                                                                                                                                                                                                                |  |

| User Port | 8            | 8            | RDATA  | 0                   | Receive HDSL Data Stream. Output data to HDSL framer at 1168 kbps: HDSL payload of Loop 1 or Loop 2 bytes plus the Z-bits, eoc, crc, losd, febe, ps, bpv, hrp, indc/indr and uib bits, Sync bits for frame positions b1-14, Stuff bits for frame positions b7007 - 7010. RDATA bits are forced high in all states except the Active State.                                                                                       |  |

|           | 9            | 7            | RFP    | 0                   | <b>Receive Frame Pulse</b> . Low for one ICLK cycle during the last bit of the current HDSL receive frame on RDATA, either b7006 or b7010. Period is within one baud time of 6 ms. <sup>2</sup> RFP is valid when LOSW transitions Low.                                                                                                                                                                                          |  |

|           | 15           | 11           | TDATA  | I1                  | Transmit HDSL Data Stream. Input data from HDSL framer at 1168 kbps: HDSL payload of Loop 1 or Loop 2 bytes plus the Z-bits, eoc, crc, losd, febe, ps, bpv, hrp, indc/indr and uib bits, Sync bits for frame positions b1-14, Stuff dummy bits; may be 1s or 0s. Tied to internal pull-up device. When ACTIVE, the Data Pump is transparent and the HDSL framer must generate the appropriate bits on TDATA as shown in Table 5. |  |

| User Port | 16           | 12           | TFP    | l <sub>1</sub>      | <b>Transmit Frame Pulse.</b> Must be Low for one ICLK cycle during the last bit of the current HDSL frame on TDATA, either b7006 or b7010. Period is within one baud time of 6 ms. <sup>2</sup> If TFP is pulled Low and is Low again three ICLK cycles later, RDATA, RFP, RFST, ICLK, CK9MEN and LOSW go to tri-state. Tied to internal pull-up device.                                                                         |  |

<sup>1.</sup> This input is a Schmidt Triggered circuit and includes an internal pull-up device.

The period is 6 ms ±<sup>1</sup>/<sub>584</sub> ms.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

# SK70704/SK70707 or SK70708 — 1168 Kbps HSDL Data Pump Chip Set

Table 2. SK70707/SK70708 HDX Pin Assignments/Signal Descriptions (Continued)

| Group                | 707<br>Pin # | 708<br>Pin # | Symbol        | I/O            |                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------|--------------|--------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      | 4            | 4            | QUIET         | l <sup>3</sup> |                                                                                                                                              | Quiet Mode Enable. Pull High to force HDX into Deactivated State. Any later transition to Low will not return HDX to Active State. See ACTREQ.                                                                                                                                                                                                                                       |  |  |

|                      | 5            | 5            | ACTREQ        | l <sup>3</sup> | pin Low in NTl                                                                                                                               | Activation Request (LTU mode) or no function (NTU mode). Tie this pin Low in NTU mode. If QUIET is Low, a rising edge on this pin initiates activation, but the signal is ignored after activation. See QUIET.                                                                                                                                                                       |  |  |

|                      | 6            | 6            | reserved      | _              | Pull Low in LT                                                                                                                               | U mode, leave open in NTU mode.                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                      | 7            | 9            | ACTVNG        | 0              | Activating State.                                                                                                                            | Activating State Indication. High when the HDX is in the Activating State.                                                                                                                                                                                                                                                                                                           |  |  |

|                      | 23           | 18           | RESET2        | l <sup>1</sup> | Reset Pulse. Pull Low on power up to initialize circuits and stop all clocks.                                                                |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Hardware             | 50           | 31           | RESET1        | l <sup>1</sup> | Reset Pulse. Pull Low to initialize internal circuits.                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Interface            | 51           | 32           | TEXP          | 0              | <b>Timer Expiry.</b> Goes High to indicate 30 second timer expiration i states.                                                              |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| (Hardware<br>Control | 52           | 33           | CHIPSEL       | l <sup>3</sup> | Chip Select                                                                                                                                  | Assert these three pins Low to activate Hardware                                                                                                                                                                                                                                                                                                                                     |  |  |

| Mode)                | 53           | 34           | WRITE         | l <sup>3</sup> | Write Pulse                                                                                                                                  | Control Mode. When any of them goes High, the HDX                                                                                                                                                                                                                                                                                                                                    |  |  |

|                      | 54           | 35           | READ          | l <sup>3</sup> | Read Pulse                                                                                                                                   | reverts immediately to Software Control Mode.                                                                                                                                                                                                                                                                                                                                        |  |  |

|                      | 55 36        |              | LOST<br>(LTU) | 0              | the Data Pump<br>Deactivated to<br>transmission b<br>Active-1 or Activating State                                                            | Il Timer Expiration. In LTU mode, LOST goes High when be enters the Inactive State. The transition from the the Inactive State occurs 1 second after the end of by the NTU when deactivation began from either the tive-2 State. When the Data Pump transitions from the e to the Deactivated State it may immediately enter the without waiting for NTU transmission to cease. (See |  |  |

|                      |              |              | LOS<br>(NTU)  | 0              | Loss of Signal Energy Indicator. In NTU mode LOS goes High to indicate loss of signal energy on entering the Inactive State (See Figure 10). |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

This input is a Schmidt Triggered circuit and includes an internal pull-up device.

The period is 6 ms ±<sup>1</sup>/<sub>584</sub> ms.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

Table 2. SK70707/SK70708 HDX Pin Assignments/Signal Descriptions (Continued)

| Group                                    | 707   | 708   | Symbol  | I/O               | Description                                                                                                                                                                                                                                                                                                                                     |  |  |

|------------------------------------------|-------|-------|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Group                                    | Pin # | Pin # | Cymbol  | .,,               | Description                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                          | 63    | 37    | LOSWT   | 0                 | <b>Loss of Sync Word Timer.</b> LOSWT goes High when LOSW is sustained for longer than 2 sec.                                                                                                                                                                                                                                                   |  |  |

|                                          | 62    | 38    | ILMT    | l <sup>1</sup>    | Insertion Loss Measurement Test. Set High to transmit a framed & scrambled, "all 1s", 2B1Q pulse sequence. Pulse sequence will have a valid sync word. In the NTU configuration, when the ILMT mode is selected, the Data Pump may begin activation.                                                                                            |  |  |

|                                          | 61    | 39    | RPTR    | l <sup>1</sup>    | Repeater Mode Enable. When in LTU mode, ICLK output phase is aligned to the TFP input pulse width. Ignored in NTU mode.                                                                                                                                                                                                                         |  |  |

| Hardware<br>Interface                    | 64    | 40    | FELB    | l <sup>1</sup>    | Front-End Loopback (LTU only). In Inactive State, set High to cause the ACC to loopback. The returned signal activates the HDX which receives its own transmitted data. The system ignores incoming data from NTU during loopback irrespective of status.                                                                                       |  |  |

| (Hardware<br>Control<br>Mode)<br>-cont'd | 65    | 41    | BELB    | l <sup>1</sup>    | Back-End Loopback. In Active State a High forces an internal, transparent loopback with RDATA connected to TDATA and RFP connected to TFP.                                                                                                                                                                                                      |  |  |

| -com a                                   | 66    | 42    | RCLKU   | 0                 | Receive Baud Rate (584 kHz) Clock. Aligned with ICLK in NTU mode, phase synchronous with receive pulse stream, However, during Activating State, the clocks may not be aligned. In the LTU mode RCLKU has a constant, arbitrary, phase relationship with ICLK in Active State.                                                                  |  |  |

|                                          | 67    | 43    | TXTST   | l <sup>1</sup>    | Transmit Test. Set high to enable isolated transmit pulse generation. The time between pulses is approximately 6 ms. TDATA controls the sign and TFP controls the magnitude of the transmitted quat pulses according to the 2B1Q encoding rules. In the NTU configuration, when the TXTST mode is selected, the Data Pump may begin activation. |  |  |

|                                          | 55    | 36    | D0      | I <sup>1</sup> /O | Data bit 0. Eight-bit, parallel data bus.                                                                                                                                                                                                                                                                                                       |  |  |

|                                          | 63    | 37    | D1      | I <sup>1</sup> /O | Data bit 1                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                          | 62    | 38    | D2      | I <sup>1</sup> /O | Data bit 2                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                          | 61    | 39    | D3      | I <sup>1</sup> /O | Data bit 3                                                                                                                                                                                                                                                                                                                                      |  |  |

| Processor                                | 64    | 40    | D4      | I <sup>1</sup> /O | Data bit 4                                                                                                                                                                                                                                                                                                                                      |  |  |

| Interface                                | 65    | 41    | D5      | I <sup>1</sup> /O | Data bit 5                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                          | 66    | 42    | D6      | I <sup>1</sup> /O | Data bit 6                                                                                                                                                                                                                                                                                                                                      |  |  |

| (Software                                | 67    | 43    | D7      | I <sup>1</sup> /O | Data bit 7                                                                                                                                                                                                                                                                                                                                      |  |  |

| Control                                  | 4     | 4     | ADDR0   | l <sup>3</sup>    | Address bit 0. Four-bit address, selects read or write register.                                                                                                                                                                                                                                                                                |  |  |

| Mode)                                    | 5     | 5     | ADDR1   | l <sup>3</sup>    | Address bit 1                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                          | 6     | 6     | ADDR2   | l <sup>3</sup>    | Address bit 2                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                          | 7     | 9     | ADDR3   | l <sup>3</sup>    | Address bit 3                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                          | 23    | 18    | RESET2  | l1                | Reset Pulse. Pull Low on power up to initialize circuits and stop all clocks.                                                                                                                                                                                                                                                                   |  |  |

|                                          | 50    | 31    | RESET1  | l <sup>1</sup>    | Reset Pulse. Pull Low to initialize internal circuits. ICLK continues.                                                                                                                                                                                                                                                                          |  |  |

| Processor<br>Interface                   | 51    | 32    | INT     | 0                 | Interrupt Output. Open drain output. Requires an external 10 k $\Omega$ pull up resistor. Goes Low on interrupt.                                                                                                                                                                                                                                |  |  |

| (Software                                | 52    | 33    | CHIPSEL | I <sup>3</sup>    | Chip Select. Pull Low to read or write to registers.                                                                                                                                                                                                                                                                                            |  |  |

| Control                                  | 53    | 34    | WRITE   | l <sup>3</sup>    | Write Pulse. Pull Low to write to registers.                                                                                                                                                                                                                                                                                                    |  |  |

| Mode)                                    | 54    | 35    | READ    | l <sup>3</sup>    | Read Pulse. Pull Low to read from registers.                                                                                                                                                                                                                                                                                                    |  |  |

|                                          |       | I     | I       |                   |                                                                                                                                                                                                                                                                                                                                                 |  |  |

This input is a Schmidt Triggered circuit and includes an internal pull-up device.

The period is 6 ms ±<sup>1</sup>/<sub>584</sub> ms.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

# SK70704/SK70707 or SK70708 — 1168 Kbps HSDL Data Pump Chip Set

Table 2. SK70707/SK70708 HDX Pin Assignments/Signal Descriptions (Continued)

| Group     | 707<br>Pin #                                                                                             | 708<br>Pin # | Symbol | I/O            | Description                                                                                                                                                           |  |

|-----------|----------------------------------------------------------------------------------------------------------|--------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | 18                                                                                                       | 14           | СК9М   | l <sup>3</sup> | 9.344 or 18.688 MHz Reference Clock. Mandatory in NTU mode. Tie High or Low in LTU Mode. Clock input requires ± 32 ppm accuracy.                                      |  |

|           | 19                                                                                                       | 15           | CK9MEN | 0              | <b>CK9M Enable.</b> Active High enable for CK9M clock. In NTU mode, this pin goes Low to indicate the PLL is tracking the input signal from the LTU. Not used in LTU. |  |

|           | 32                                                                                                       | 19           | CK37M  | I              | Receive Timing Clock (37.376 MHz). Tie to CK37M on ACC.                                                                                                               |  |

| Clock and | 33                                                                                                       | 20           | DTR    | 0              | Serial Control Data Link. Transfers data at 18.688 Mbps. Tie to DTR on ACC.                                                                                           |  |

| Control   | 34                                                                                                       | 21           | FS     | 0              | 584 kHz Clock. Derived from CK37M. Tie to FS on ACC.                                                                                                                  |  |

|           | 35                                                                                                       | 22           | AD0    | I              | Analog to Digital Converter input pin. Tie to AD0 on ACC.                                                                                                             |  |

|           | 36                                                                                                       | 23           | AD1    | I              | Analog to Digital Converter input pin. Tie to AD1 on ACC.                                                                                                             |  |

|           | 37                                                                                                       | 24           | AGCKIK | I              | AGC Adjust. Controls analog gain circuit. Tie to AGCKIK on ACC.                                                                                                       |  |

|           | 38                                                                                                       | 25           | TCK4M  | 0              | Transmit Clock. Tie to TCK4M on ACC.                                                                                                                                  |  |

|           | 39                                                                                                       | 26           | TMAG   | 0              | Transmit Magnitude Bit. Tie to TMAG on ACC.                                                                                                                           |  |

|           | 40                                                                                                       | 27           | TSGN   | 0              | Transmit Sign Bit. Tie to TSGN on ACC.                                                                                                                                |  |

|           | 1                                                                                                        | 1            | VCC1   | I              | Logic supply input (Refer to Table Table 27).                                                                                                                         |  |

|           | 68                                                                                                       | 44           | VCC2   | I              | I/O supply input.                                                                                                                                                     |  |

| Power     | 2                                                                                                        | 2            | GND1   | I              | Ground.                                                                                                                                                               |  |

| rowei     | 3                                                                                                        | 3            | GND2   | I              | Ground.                                                                                                                                                               |  |

|           | 42                                                                                                       | 28           | GND3   | I              | Ground.                                                                                                                                                               |  |

|           | 47                                                                                                       | _            | GND4   | I              | Ground.                                                                                                                                                               |  |

| Misc      | 10 11<br>12 13<br>22 24<br>25 26<br>27 28<br>29 30<br>31 41<br>43 44<br>45 46<br>48 56<br>57 58<br>59 60 | 29           | _      | _              | No internal connection.                                                                                                                                               |  |

This input is a Schmidt Triggered circuit and includes an internal pull-up device.

The period is 6 ms ±<sup>1</sup>/<sub>584</sub> ms.

This input is a Schmidt Triggered circuit and includes an internal pull-down device.

# 2.0 Functional Description

The HDSL Data Pump is a fully-integrated, two-chip solution (see front page block diagram) which includes an SK70704 Analog Core Chip (ACC) and an SK70707/SK70708 HDSL Digital Transceiver (HDX).

# 2.1 Transmit

The transmit data stream is supplied to the HDX at the TDATA input in a binary fashion. The HDX scrambles and 2B1Q encodes the data and adds the sync word and stuff quats based on the TFP frame pulse position. The injected stuff quats in a frame are equal to the last scrambled data symbol in that frame. The 2B1Q encoded transmit quat data stream (TSGN/TMAG) is then passed to the ACC which filters and drives it onto the line.

# 2.2 Receive

The composite waveform of the receive signal plus trans-hybrid echo is filtered and converted to digital words at a rate of 584 k-words/second in the ACC. The ACC passes the digitized receive quat stream (AD0 and AD1) to the HDX. The HDX performs digital filtering, linear echo cancellation, frame recovery and descrambling. The HDX uses the transmit quat stream to generate the echo estimates and estimate error values. Using this error and the delayed transmit quat stream, the echo canceller coefficients are updated. The recovered, decoded and descrambled data is then output to the framer-mux from the HDX RDATA pin.

# 2.3 Control

The Data Pump offers two control modes - Hardware Mode and Software Mode. In Hardware mode the HDX receives control inputs via individually designated pins. In Software mode the HDX control data is supplied via an 8-bit parallel port. In either mode, the HDX and the ACC communicate via a unidirectional serial port (DTR).

#### 2.4 ACC and HDX Overview

The following paragraphs describe the chip set components individually with reference to internal functions and the interfaces between Data Pump components.

# 2.4.1 Analog Core Chip (ACC)

The ACC incorporates the following analog functions:

- the transmit line driver

- · transmit and receive filters

- Phase-Locked Loop (PLL), including VCO

- hybrid circuitry analog-to-digital converter

The ACC provides the complete analog front end for the HDSL Data Pump. It performs transmit pulse shaping, line driving, receive A/D, and the VCO portion of the receiver PLL function. Transmit and receive controls are implemented through the serial port. The ACC line interface uses a single twisted pair line for both transmit and receive. Table 2 lists the ACC pin descriptions. Refer to Test Specifications section for ACC electrical and timing specifications.

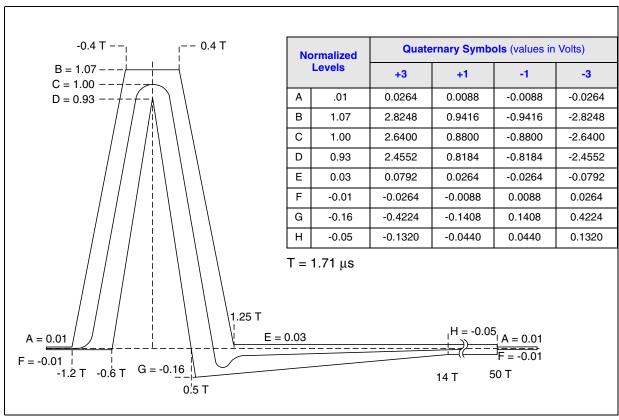

#### 2.4.1.1 ACC Transmitter

The ACC performs the pulse shaping and driving functions. The ACC transmitter generates a 4-level output of 1/(8\*f(TCK4M)) defined by TMAG and TSGN. Table 3 lists 2B1Q pulse coding parameters. Refer to Test Specifications for frequency and voltage templates.

#### 2.4.1.2 ACC Receiver

The ACC receiver is a sophisticated sigma-delta converter. It sums the differential signal at RTIP/RRING minus the signal at BTIP/BRING. The first A/D signal comes out of AD0 at a bit stream rate of 18.688 MHz. The second stage of the A/D samples the noise of the first and generates the AD1 bit stream at 18.688 MHz.

Receiver gain is controlled by the HDX via the AGC2-0 bits in the DTR serial control stream. The AGCKIK output from the ACC is normally Low. It goes High when the signal level in the sigmadelta A/D is approaching its clipping level, signaling the HDX to lower the gain.

The VCO is part of a phase-locked loop (PLL) locked to the receive data baud rate using an external phase detector. The VCO frequency is varied by pulling an external crystal with external varactor diodes that are controlled by the VPLL output. The VPLL output is, in turn, controlled by the serial port VCO and PLL bits.

# 2.4.2 HDSL Digital Transceiver (HDX)

The HDX incorporates the following digital functions:

- bit-rate transmit and receive signal-processing

- adaptive echo-cancelling (EC)

- adaptive decision feedback-equalization (DFE) using the receive quat stream and the internal error signal

- fixed and adaptive digital-filtering functions

- activation/start-up control and the microprocessor interface to the HDSL framer

The HDX also provides the Data Pump Back-End interface for the customer defined/developed HDSL framer via serial data channels and clock signals. A simple, parallel 8-bit microprocessor interface on the HDX allows high-speed access to control, status and filter coefficient words. Table 2 lists the HDX pin descriptions. Refer to Test Specifications section for HDX electrical and timing specifications.

The microprocessor interface on the HDX provides bit flags for signal presence, synchronization, activation completion, and loss of synchronization for a time greater than two seconds. Single-byte words representing receive signal level and the noise margin of the transceiver are also available on the microprocessor interface. One control byte allows the user to start the Data Pump activation sequence. The HDX controls the complete activation/start-up sequence, allowing flexible, single-loop, fractional applications.

| Table 3. A | CC Transmi | t Control |

|------------|------------|-----------|

|------------|------------|-----------|

| TSGN | TMAG | Output Symbol (quat) |  |  |

|------|------|----------------------|--|--|

| 1    | 0    | +3                   |  |  |

| 1    | 1    | +1                   |  |  |

| 0    | 1    | -1                   |  |  |

| 0    | 0    | -3                   |  |  |

#### 2.4.3 HDX/ACC Interface

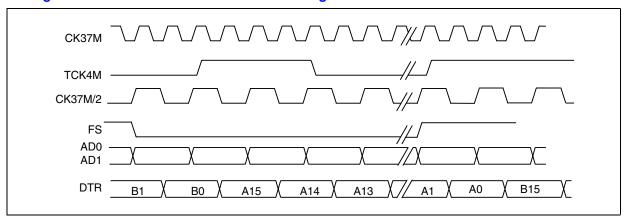

The ACC provides the 37.376 MHz master clock, CK37M, to the HDX. The serial control stream framing signal FS is sampled inside the ACC with the CK37M rising edge. The serial control stream, DTR, is sampled inside the ACC by the rising edge of an internally-generated clock at f(CK37M)/2. This ACC internal clock has the same phase relationship with a similar clock inside the HDX, as established by the FS signal. In the HDX, the half-rate clock CK37M/2 and FS transition on the rising edge of CK37M, and DTR transitions come on the falling edge of CK37M/2. The output REFCLK in NTU Mode equals CK37M/2.

The A/D converter outputs, AD0 and AD1, are clocked out of the ACC with CK37M, having transitions coincidental with the rising edge of CK37M/2. The HDX samples AD0 and AD1 with the falling edge of its internal CK37M/2.

Transmit data, represented by TSGN and TMAG, is clocked from the HDX using the falling edge of TCK4M, the 4.672 MHz (f(REFCLK)/4) transmit time base clock. The ACC uses the rising edge of TCK4M to sample TSGN and TMAG. TSGN and TMAG change state at the baud rate, or every 8 cycles of TCK4M. Figure 5 shows relative timing for the HDX/ACC interface.

#### 2.4.3.1 HDX/ACC Serial Port

The HDX continually writes to the ACC serial port. This serial stream consists of two 16-bit words as shown in Table 4. The data flows from the HDX to the ACC at a rate of f(CK37M)/2. Refer to the Test Specifications section for serial port timing relationships and electrical parameters.

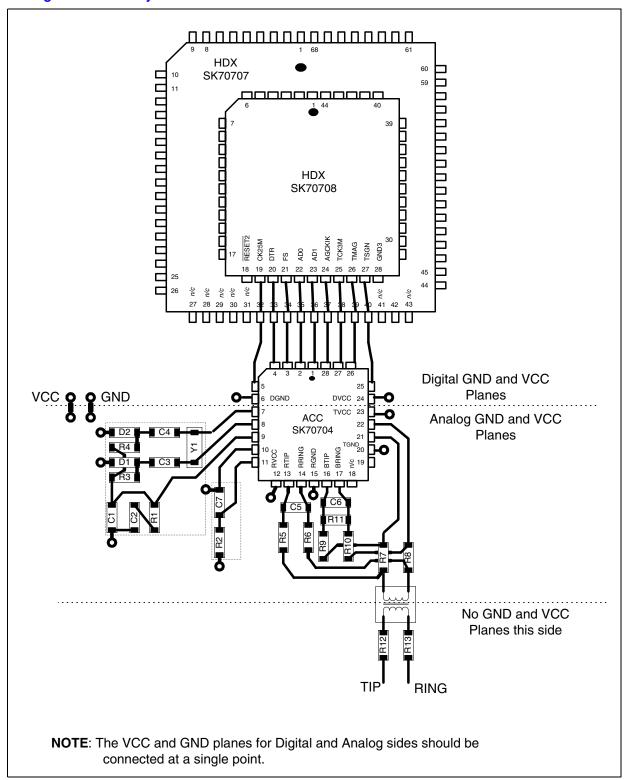

#### 2.5 Line Interface

The Data Pump line interface consists of three differential pairs. The transmit outputs TTIP and TRING, receive inputs RTIP and RRING, and the balance inputs BTIP and BRING, all connect through a common transformer to a single twisted-pair line (see Figure 14 and Figure 16). The transmit outputs require resistors in series with the transformer. A passive prefilter is required for the receive inputs. The balance inputs feed the transmit signals back to the Data Pump providing passive echo cancellation. Protection circuitry should be inserted between all Data Pump line interface pins and the transformer. Refer to the Applications section for typical schematics.

Table 4. HDX/ACC Serial Port Word Bit Definitions ( Figure 5)

| Bit | Word A (on DTR) | Word B (on DTR) |  |  |

|-----|-----------------|-----------------|--|--|

| 15  | INIT            | COR4            |  |  |

| 14  | n/a             | COR3            |  |  |

| 13  | n/a             | COR2            |  |  |

| 12  | TXOFF           | COR1            |  |  |

| 11  | TXDIS           | COR0            |  |  |

| 10  | TXTST           | VCO2            |  |  |

| 9   | AGC2            | VCO1            |  |  |

| 8   | AGC1            | VCO0            |  |  |

| 7   | AGC0            | PLL7            |  |  |

| 6   | FELB            | PLL6            |  |  |

| 5   | n/a             | PLL5            |  |  |

| 4   | PTR4            | PLL4            |  |  |

| 3   | PTR3            | PLL3            |  |  |

| 2   | PTR2            | PLL2            |  |  |

| 1   | PTR1            | PLL1            |  |  |

| 0   | PTR0            | PLL0            |  |  |

Figure 5. HDX/ACC Interface – Relative Timing

# 2.6 HDSL Data Interface

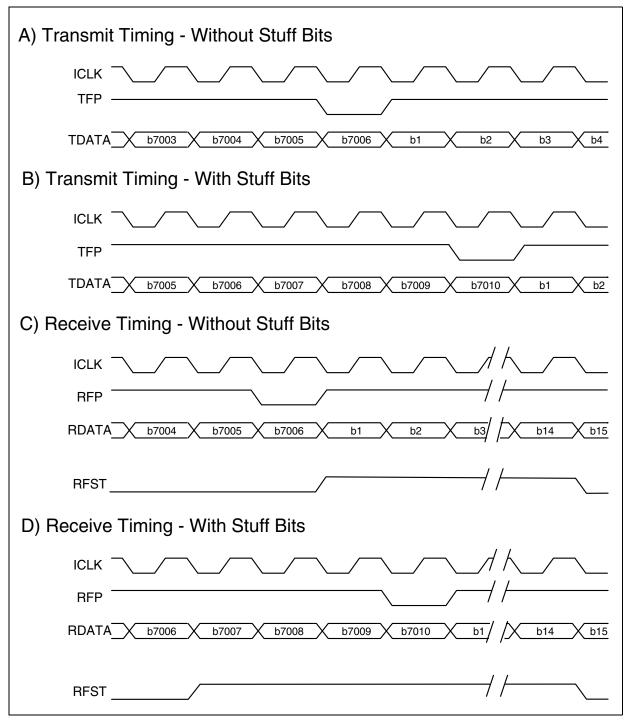

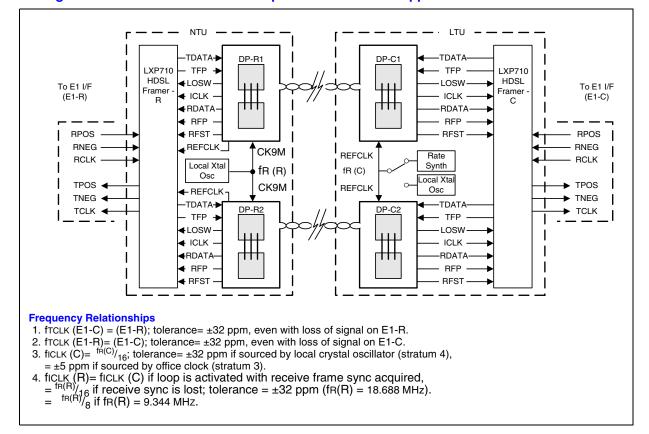

The HDSL data interface includes the transmit and receive binary data streams, transmit and receive frame pulses, the 1168 kHz clock (ICLK) and the receive frame and stuff quat indicator (RFST). Figure 6 shows relative timing for the framer interface. Refer to Test Specifications section for details on the Data Pump/framer interface. Figure 8 shows a complete HDSL system with both the remote NTU and central office LTU HDSL framer interfaces illustrated. Table Table

# 1168 Kbps HSDL Data Pump Chip Set — SK70704/SK70707 or SK70708

5 shows the TDATA requirements for the framer interface through the activation sequence. Once the ACTIVE Low-to-High transition occurs, the Data Pump becomes transparent. Therefore, the HDSL framer must supply appropriate data to TDATA. Table 5 summarizes this requirement.

The HDSL framer interface is subject to the following rules:

- 1. When frame sync is not present (LOSW is High), all RDATA bits are set to 1.

- 2. If frame sync is lost on both Data Pump-R1 and Data Pump-R2, both units will fall back on the local reference frequency with ±32 ppm tolerance, and stuff bits will be injected in their RDATA streams on every other frame.

| Table 5. | HDSL | Framer | <b>TDATA</b> | Rec | uirements |

|----------|------|--------|--------------|-----|-----------|

|----------|------|--------|--------------|-----|-----------|

| Activation           | Process    | TDATA      |            |  |

|----------------------|------------|------------|------------|--|

| Framer               | Data Pump  | Overhead   | Data       |  |

| Idle                 | Activating | don't care | don't care |  |

| Idle                 | Active 1   | live       | all 1s     |  |

| Active-R             | Active 1   | live       | all 1s     |  |

| Active-T             | Active 1   | live       | live       |  |

| Link Active Active 1 |            | live       | live       |  |

| Link Active          | Active 2   | live       | live       |  |

- 1. If frame sync is lost on either Data Pump-R1 or Data Pump-R2, that unit can be made to fall back on the REFCLK from the Data Pump-R which is still in frame sync, and stuff bits will be injected in the RDATA stream on every other frame of the out-of-frame Data Pump-R.

- 2. If frame sync is lost on either Data Pump-C1 or Data Pump-C2, the receiver in each unit will fall back on the reference clock with ±32 ppm or ±5 ppm tolerance, and inject stuff bits in the RDATA stream on every other frame.

- 3. If either E1-R or E1-C loses sync or signal, it is assumed that the corresponding T1 receiver will fall back on a local reference with ±32 ppm tolerance, and that transmit bit-stuffing control will still be applied through the TFP signal from the HDSL framer.

- 4. The HDSL framer should provide TFP signal with a period of 6 ms  $\pm 1/584$  ms prior to an activation request for the LTU Data Pump(s). The framer should provide a valid TFP after power-up, before or immediately after LOS goes Low for the NTU Data Pump(s).

If the TFP signal from the HDSL framer is inactive (always High or unconnected), the Data Pump will inject stuff bits in the TDATA stream in every other frame, although the Data Pump will not be synchronized to the HDSL framer. When a new TFP is provided, the Data Pump will immediately reset the transmit frame alignment, typically causing loss of alignment at the other end.

5. A simultaneous RESET2 to all LTU Data Pumps which use a common REFCLK eliminates phase shift between the ICLK outputs which may exist after power-up.

The ICLK outputs of all NTU Data Pumps may have an arbitrary phase difference even using a common CK9M reference.

Figure 6. HDX/ACC Framer Interface – Relative Timing

Figure 7. Model for HDSL Data Pump and HDSL Framer Applications

# 2.7 Microprocessor Interface (HDX)

Three primary control pins, CHIPSEL (Chip Select), READ and WRITE, execute the Software Mode which also uses an interrupt output pin to report status changes. Four additional pins are used for the parallel bus addressing and eight pins for data I/O. Refer to Test Specifications for microprocessor interface timing in Software Mode. The following control pins are used during register access.

#### 2.7.1 Control Pins

**Chip Select:** The Chip Select (CHIPSEL) pin requires an active Low signal to enable Data Pump read or write transfers over the data bus. To enable Hardware Mode hold this pin Low, along with READ and WRITE.

**Data Read:** The Data Read pin (READ) requires an active Low pulse to enable a read transfer on the data bus. When READ is pulled Low, the Data Pump data bus lines go from tristate to active and output the data from the register addressed by ADDR0-ADDR3. To avoid reading data during register updates, reads should be synchronized to the falling edge of FS. Alternatively, each read should be repeated until the same data is read twice within one baud time.

#### SK70704/SK70707 or SK70708 — 1168 Kbps HSDL Data Pump Chip Set

**Data Write:** The Data Write pin (WRITE) requires an active Low pulse to enable a write transfer on the data bus. Data transfer is triggered by the rising edge of the WRITE pulse. To ensure data is written to the register addressed by ADDR0-ADDR3, valid data must be present on the HDX data bus lines before WRITE goes High.

Interrupt: The Interrupt pin (INT) is an open drain output requiring an external pull-up resistor. The INT output is pulled active Low when an internal interrupt condition occurs. INT is latched and held until Main Status Register RD0 is read. An internal interruption results from a Low-to-High transition in any of four status indicators: ACTIVE, LOSW, LOSWT or TEXP. Any transition on LOS will also generate an interrupt. If an interrupt mask bit in register WR2 is set, any transition of the corresponding status bit will not trigger the INT output.

# 2.7.2 Register Access

Write: To write to an HDX register, proceed as follows:

- 1. Drive CHIPSEL Low.

- 2. Drive an address (0000, 0010, or 0011) onto ADDR0-ADDR3.

- 3. Observe address setup time.

- 4. Set 8-bit input data word on D0-D7.

- 5. Pull WRITE Low, observing minimum pulse width.

- 6. Pull WRITE High, observing hold time for data and address lines.

Read: Procedures for reading the HDX registers vary according to which register is being read. Accessing registers RD0, RD1, RD2, RD5 and RD6 is relatively simple. Reading registers RD3 and RD4 is more complex. *Unless parallel port reads are synchronized with the falling edge of FS, all read operations should be repeated until the same data is read twice within one baud time*. To read register RD0, RD1, RD2, RD5 or RD6 proceed as follows:

- 1. Drive CHIPSEL Low.

- 2. Drive the desired address onto ADDR0-ADDR3.

- 3. Pull READ Low, observing minimum pulse width.

- 4. Pull READ High to complete the read cycle.

Registers RD3 and RD4 hold the coefficient values from the DFE, EC, FFE and AGC as shown in Table 9. Register RD3 holds the lower byte value and register RD4 holds the upper byte value. To reconstruct the complete 16-bit word, concatenate the least significant and most significant bytes.

To read registers RD3 and RD4 proceed as follows:

- 1. Select the desired coefficient by writing the appropriate code from Table 9 to register WR3.

- 2. Enable the Coefficient Read Register by writing a 1 to bit b0 (CRD1) in register WR2.

- 3. Perform standard register read procedure listed in steps 1 through 6 above to read the lower byte from RD3 and the upper byte from RD4.

- 4. Concatenate the RD3 and RD4 to obtain the complete 16-bit word.

# 2.7.3 Registers

Three write registers and seven read registers are available to the user. Table 6 lists these registers and the following paragraphs describe them in more detail.

Some of the registers contain *reserved* bits. Software must deal correctly with *reserved* fields. For reads, software must use appropriate masks to extract the defined bits and not rely on *reserved* bits being any particular value. In some cases, software must program *reserved* bit positions to a particular value. This value is defined in the individual bit descriptions.

After asserting the  $\overline{RESET1}$  and  $\overline{RESET2}$  signals, the Data Pump initializes its registers to the **default** value.

Table 6. Register Summary

| ADDR      | Write Registers |                         |       | Read Registers                             |                    |       |  |

|-----------|-----------------|-------------------------|-------|--------------------------------------------|--------------------|-------|--|

| A3-A0     | WR#             | Name                    | Table | RD# Name                                   |                    | Table |  |

| 0000      | WR0             | Main Control            | 7     | RD0 Main Status                            |                    | 10    |  |

| 0001      |                 | reserved                |       | RD1                                        | Receiver Gain Word | 11    |  |

| 0010      | WR2             | Interrupt Mask          | 8     | RD2                                        | Noise Margin       | 12    |  |